вторые выводы через соответствующие аналоговые ключи первой группы соединены с выходом буферного усилителя, первые выводы резисторов второй группы подключены к второму выводу пятого резистора, их вторые выводы через соответствующие аналоговые ключи второй группы соединены с выходом усилителя мощности, первые выводы третьей группы резисторов подключены к инвертирующему входу усилителя обратной связи,их вторые выводы через соответствующие аналоговые ключи третьей группы соединены с выходом буферного усилителя первые выводы резисторов второй группы подключены второму выводу, пятого резистора, их вторые выводы через соответствующие аналоговые ключи второй группы соединены с выходом усилителя мощности, первые выводы третьей группы резисторов подключены к инвертирующему входу усилителя обратной связи, их вторые выводы через соответствующие аналоговые ключи третьей группы соединены с выходом усилителя обратной связи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Электрометрический преобразователь заряда | 1986 |

|

SU1499242A1 |

| Устройство для измерения малых токов | 1988 |

|

SU1638647A1 |

| Устройство для измерения температуры | 1985 |

|

SU1315831A1 |

| Электрометрический преобразователь заряда | 1986 |

|

SU1420537A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО ТОКА | 1991 |

|

RU2024917C1 |

| Устройство для считывания графической информации | 1987 |

|

SU1506460A1 |

| Стабилизированный источник тока с изменяющейся полярностью | 1982 |

|

SU1065843A1 |

| Устройство для измерения температуры | 1984 |

|

SU1276924A1 |

| Цифроаналоговый преобразователь | 1989 |

|

SU1817244A1 |

CTABHJTliSATOP ПОСТОЯННОГО ТОКА, содержащий М-разрядный управляемый кодом по входным цепям цифроаналоговый преобразователь, выход которого подключен к инвертирующему входу буферного усилителя и через первый резистор - к выходу буферного усилителя, который через второй резистор подключен к инвертирующему входу суммирующего усилителя, соединенному через третий резистор с выходом усилителя обратной связи, а через четвертый резистор - с выходом усилителя мощности, вход кото- роге подключен к выходу суммирующего усилителя, и первым выводом пятого резистора, второй вывод которого соединен с выводом для подключения резистора нагрузки, свободным выводом подключенного к ишне нулевого потенциала, а через шестой резистор - с инвертирующим входом усилителя обратной и с первьм выводом седьмого резистора, второй выход которого подключен.к выходу усилителя обратной связи, при этом неинвертирующие входы всех усили1163314 А 4

Изобретение относится к электротехнике, в частности к стабилизированным источникам Тока, управляемым кодом.

Цель изобретения - повыщение точ ности стабилизации и расширение диапазона регулирования .тока.

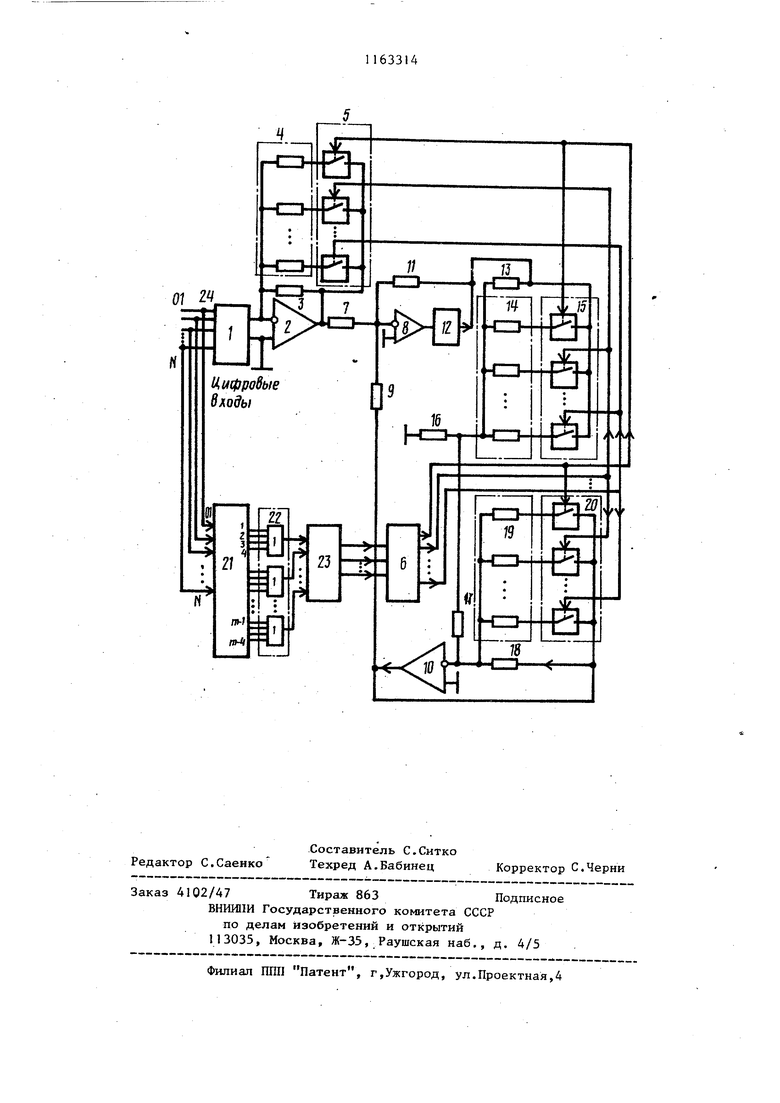

На чертеже изображена функциональная схема стабилизатора постояннего тока.

Стабилизатор содержит цифроаналоговый преобразователь (ЦАП) 1, буферный усилитель (БУ) 2, первый резистор 3, первую группу дополнительно введенных резисторов 4 со своими ключами 5 коммутатора 6, второй резистор 7, суммирующий -усилитель СУ 8, третий резистор 9, усилитель обратной связи (УОС) 10, четвертый резистор 11, усилитель мощности (УМ 12, пятый резистор 13, вторую группу дополнительно введенных резисторов 14 со своими ключами 15 коммутаторов, резистор 16 нагрузки, шестой резистор 17, седьмой резистор 18, третью группу дополнительно введенных резисторов 19 со своими ключами 20 коммутатора 6, а также дополнительно введенные преобразователь 2 двоичный код - двоично-десятичный код, элементы ИЛИ 22, дешифратор 23 На схеме так же изображены цифровые входы ЦАП 1 и преобразователя 21 (I - N) , а также выходы преобразователя 21 (1 - м).

Устройство работает следующим образом.

Сигналы кодовой комбинации, соответствующие заданному току, поступают на входы 24 ЦАП 1, который преобразует их в ток и выдает его на инвертирующий вход БУ 2, коэффициент усиления которого определяется величиной сопротивления отрицательной обратной связи БУ 2 (суммарным сопротивлением первого резистора 3 и подключаемыми параллельно ему дополнительными резисторами первой группы) . Выходное напряжение БУ 2 через (масщтабный резистор) второй резистор 7 поступает на вход СУ 8, который осуществляет сложение аналогового выходного напряжения от БУ 2 с падением напряжения на резисторе 16 нагрузки, которое через щестой резистор 17 поступает на инвертирующий вход УОС 10, усиливается ним с коэффициентом усиления, определяемым, величиной сопротивления отрицательной обратной связи УОС 10 (сумманым сопротивлением седьмого резистора 18 и подключаемыми параллельно ему дополнительными резисторами третьей группы) и подается через третий резистор 9 на инвертирующий вход СУ 8, который управляя УМ 12, создает на его выходе напряжение V , а следовательно, и в нагрузке ток, величина которого определяется из выражения

н Ueb,«/R. ,

вых значение выходного напряжения БУ 2; R - суммарная величина сопро тивления пятого резистора 13 и подключаемых параллельно ему дополнител ных резисторов второй группы. Сигналы кодовой комбинации, пост пающие на вход ДАЛ I, поступают так же на входы преобразователя 21, ко,торый преобразует двоичный код, обы но используемьп для управления ЦАП 1 в двоично-десятичный. Выходы преобразователя 21, сгруппированные в М групп (каждая группа может иметь кодовую комбинацию, соответствующую числам от О до 9). Выходы каждой группы, за исключением первой, содержащей четыре младщих разряда, подключены к входам сво их элементов ИЛИ 22, При задании на,входах ДАЛ 1 и пре образователя 21 кодовой комбинации, соответствующей значениям чисел от О до 9, появляются сигналы кодовой комбинации (логической 1) на выходах первой группы преобразователя 21 (четырех младших разрядах), а на всех остальных выходах присутствуют сигналы логического О. При задании на входах ЦЛП 1 кода, соответствующего числам от О до 99, от О до 999, от О до N,появляются сигналы логической 1 соответственно н§ входах первого, второго и М-го элементах ИЛИ 22, подключенных соответственно к второй (5 и 8 разряды), третьей (9-12 разряды) и М-й группе выходов преобразователя 21, которые приводят к сраб тыванию элементов ИЛИ 22. Логические сигналы с элементов ИЛИ 22 преобразуюд-ся дешифратором 23 в сигналы переключения коммутатором 6 поддиапазонов работы 1 до К устройства, опеределяемых допустимым динамическим диапазоном работы применяемых активных элементов . Это переключение синхронно осуществляется одним из ключей 5, 15 и 20 соответственно в первой, второй и третьей группах резисторов 4, 14 и 19. Пусть при переходе на новый поддиапазон работы в (X раз уменьшается выходной сигнал ЦАП 1. По командам блока 6 синхронно срабатывают соответствующие ключи 5, 15 и 20 в первой, второй и третьей группах резисторов 4, 14 и 19. При этом одновременно в / раз увеличиваются коэффициенты усиления БУ 2 и суммарная величина пятого резистора 13, который ограничивает выходной ток УМ 12, и в Л раз уменьшается коэффициент усиления УОС 10. Величина коэффициента определяется числом (R + l) поддиапазонов, на которое разбит весь диапазон работы устройства. Таким образом, в предлагаемом устройстве при управлении током с помощью ЦАП 1 (кодом) устраняется ограничение на разрядность ЦА.П 1 вследствие того, что управляюощй сигнал при разрядности больше 10 и работе в начале диапазона не соизмерим за счет перехода на соответствующий поддиапазон работы с U и dUpy/dT операционного усилителя что уменьшает погрешность задания тока и расширяет диапазон регулирования (разрядность ЦАП 1). Дополнительное введение новых лементов позволяет уменьшить погрешость задания тока и расширить диаазон регулирования.

| Стахов А.Ф | |||

| Автоматизированные измерительные комплексы | |||

| М., Энергоиздат, 1982, с | |||

| Способ получения жидкой протравы для основных красителей | 1923 |

|

SU344A1 |

| Аналоговые интегральные схемы | |||

| Под ред | |||

| Коннели Дж | |||

| М.,Мир, 1977, с | |||

| Способ получения жидкой протравы для основных красителей | 1923 |

|

SU344A1 |

Авторы

Даты

1985-06-23—Публикация

1983-11-21—Подача