Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении прецизионных цифроаналоговых преоб- разователей в составе контрольно-измерительной аппаратуры, системах уп равления и передачи информации.

Цель изобретения - повышение точности и быстродействия преобразо- . вания,

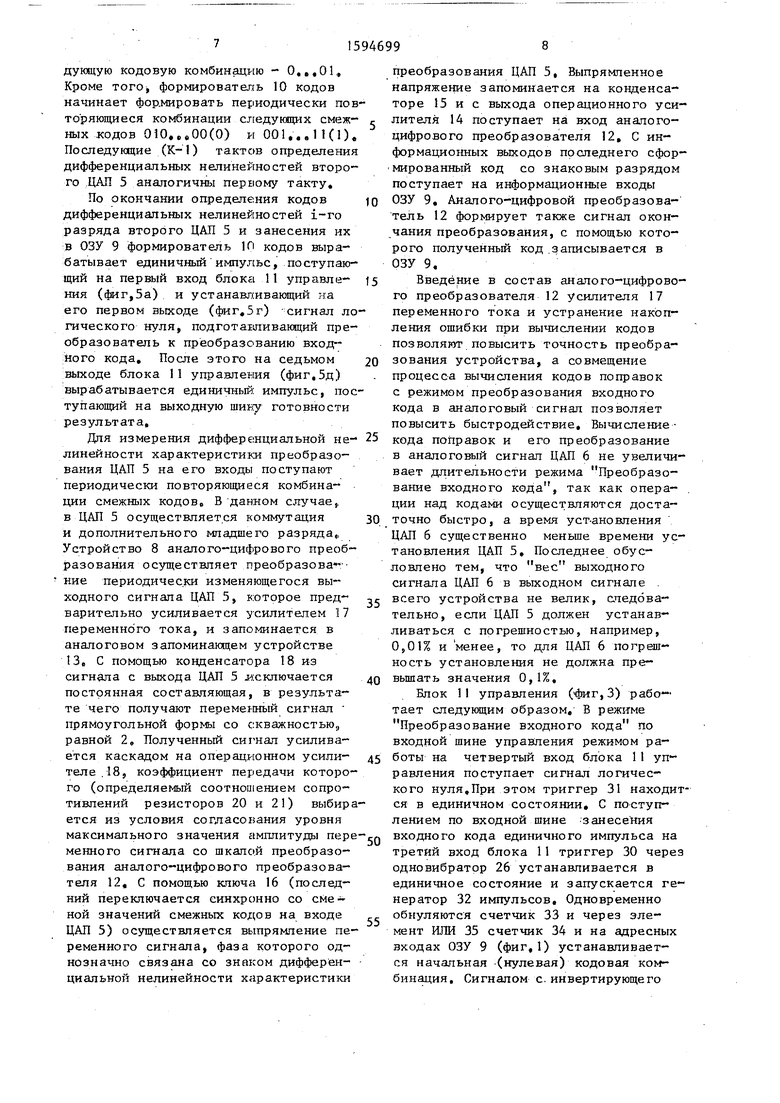

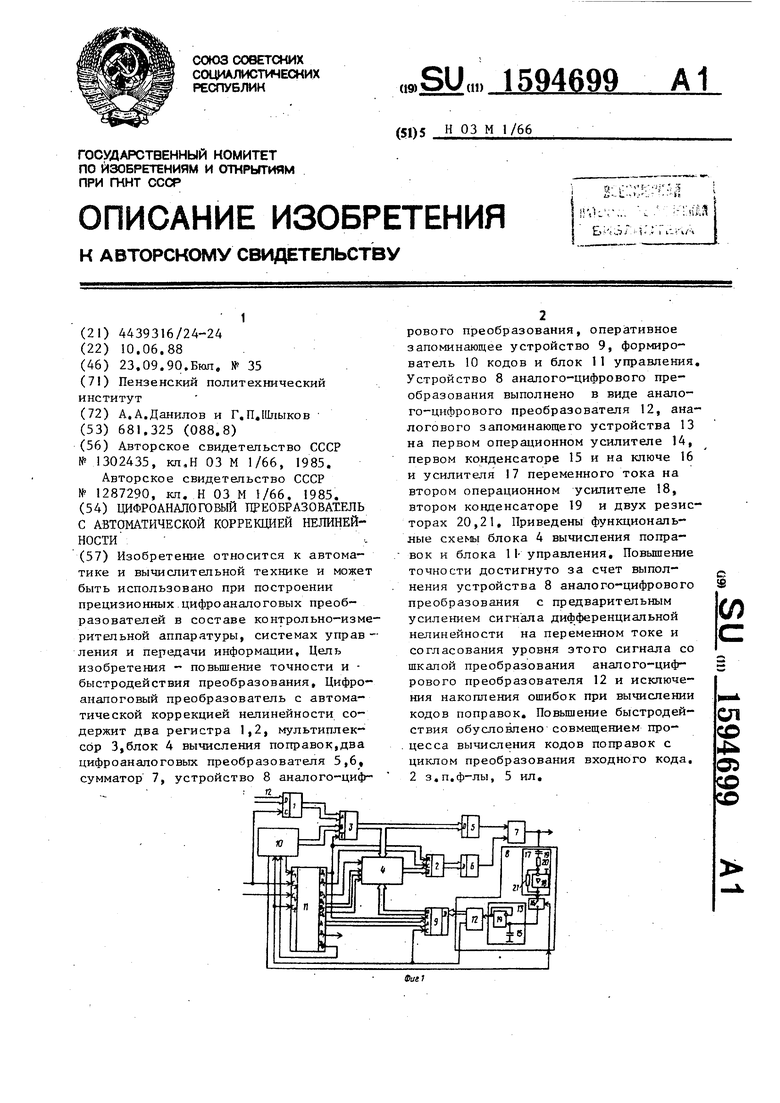

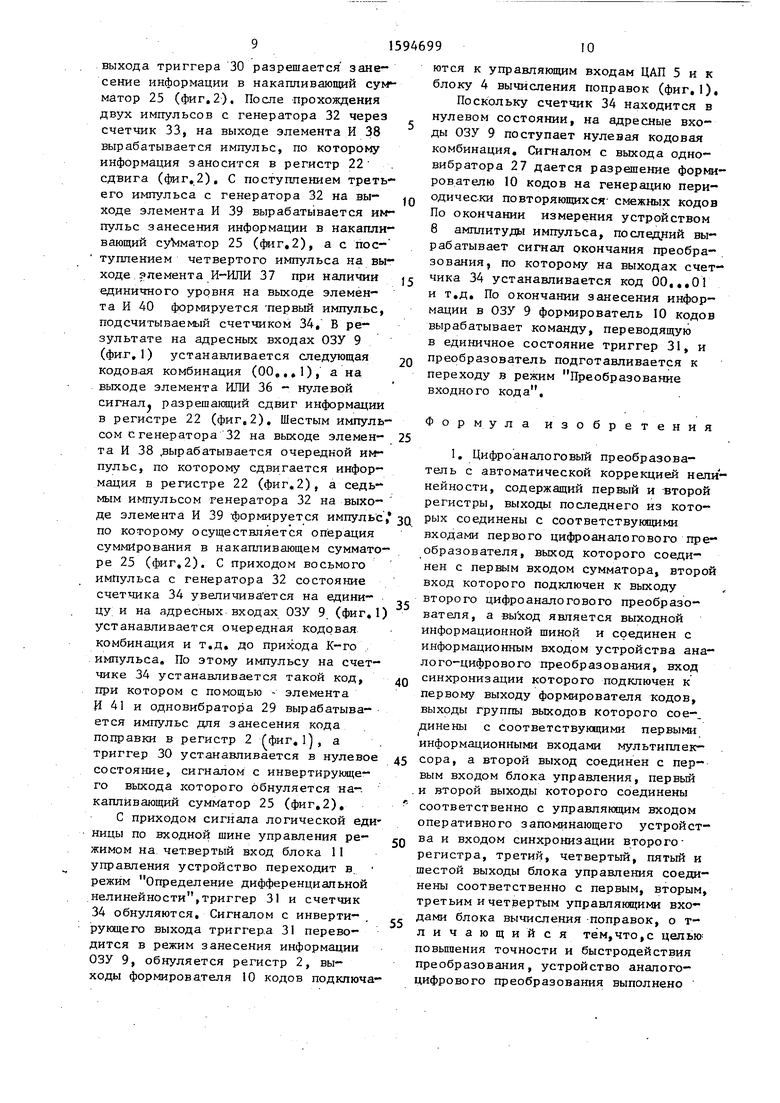

; На фиг,1 представлена функционапь- |ная схема цифроаналогового преоб-- Фазователя с автоматической коррекцией нелинейности; на фиг„2 - функцио- нальная схема блока вычисления поправок; на фиг.З - функциональная схема блока управления; на фиг,4 и 5 - временные диаграммы работы блока управления в режимах Преобразование вход- ного кода и Определение дифференци- :апьных нелинейностей соответственно,

Цифроаналоговый преобразователь с автоматической коррекцией нелинейности (фиг,1) содержит первый 1 и второй 2 регистры, мультиплексор 3, блок 4 вычисления поправок, второй 5 и первый 6 цифроаналоговые преобразователи, сумматор 7, устройство 8 аналого-цифрового преобразования, оперативное запоминающее устройство (ОЗУ) 9, формирователь 10 кодов и блок 11 управления. Устройство 8 аналого-цифрового ..преобразования выполнено в виде аналого-цифрового преоб- разователя 12, аналогового запоминающего устройства 13 на первом операционном усилителе 14, первом конден саторе 15 и на ключе 16 и усилителя 17 переменного тока на-втором опера- ционном усилителе 1й, втором конденсаторе 19 и двух резисторах 20 и 21, Блок 4 вычисления поправок (фиг,2) выполнен на регистре 22 сдвига, суммторе 23, умножителе 24 и накапливаю- тем сумматоре 25, Блок 11 управления (фиг.З) выполнен на четырех од- новибраторах 26 - 29, двух КЗ-триггерах 30 и 31, генераторе 32 импульсов, двух счетчиках 33 н 34 импуль- сов, двух элементах ИЛИ 35 и 36, элементе И-ИЛИ 37 и четырех элементах; И 38 - 41,

ности работает в двух режимах: Преобразование входного кода и Определение дифференциальных нелинейнос- тей. Второй цифроанапоговый преобразователь (ЦАП| 5 является основным а первый ЦАП 6 предназначен для компенсации погрешностей, вносимых вторым ЦАП 5,

Работа преобразователя в режиме Преобразование входного кода. По шине управления режимом работы на четвертый вход блока 11 управления поступает сигнал логического нуля, разрешакждий преобразование входного кода. При этом на первом выходе блок 1 1 управления (фиг,46) устанавливается сигнал логического нуля, В результате выходы мультиплексора 3 соединяются с его первыми входами, подключенными к выходам первого регистра 1, а ОЗУ 9 переводится в режим считывания информации,- Преобразуемый входной код поступает на информационные входы первого регистра 1 и заносится в последний с приходом управляющего единичного импульса по шине занесения входного кода (фиг,4а) на вход занесения первого регистра 1 и -на третий вход блока 11 управления С приходом этого импульса блок 11 управления устанавливает на адресных вкодах ОЗУ 9 нулевую кодовую комбинацию (фиг,4и,ок,л), Б результате на выходах ОЗУ 9 устанавливается код Кг дифференциальной нелинейности старшего п-го разряда второго ЦАП 5, поступающий на первые входы умножителя 24 блока 4 вычисления поправок (фиг,2), Кроме того, на третьем выходе блока I1 управления устанавливается сигнал логической единицы (фиг,4г), переводящий регистр сдвига 22 в режим занесения входного кода. Затем на четвертом выходе блока -11 управления вырабатывается импульс (фиг,4д), по которому входной код, хранящийся в. первом регистре 1, заносится в регистр сдвига 22, В сумматоре 23 определяется сумма двух ко до в

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1287290A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1559405A2 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1319279A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| ТАНКОВЫЙ БАЛЛИСТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 1979 |

|

SU1840108A1 |

| СПОСОБ КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2399156C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении прецизионных цифроаналоговых преобразователей в составе контрольно-измерительной аппаратуры, системах управления и передачи информации. Цель изобретения - повышение точности и быстродействия преобразования. Цифроаналоговый преобразователь с автоматической коррекцией нелинейности содержит два регистра 1, 2, мультиплексор 3, блок 4 вычисления поправок, два цифроаналоговых преобразователя 5, 6, сумматор 7, устройство 8 аналого-цифрового преобразования, оперативное запоминающее устройство 9. Формирователь 10 кодов и блок 11 управления. Устройство 8 аналого-цифрового преобразования выполнено в виде аналого-цифрового преобразователя 12, аналогового запоминающего устройства 13 на первом операционном усилителе 14, первом конденсаторе 15 и на ключе 16 и усилителя 17 переменного тока на втором операционном усилителе 18, втором конденсаторе 19 и двух резисторах 20, 21. Приведеные функциональные схемы блока 4 вычисления поправок и блока 11 управления. Повышение точности достигнуто за счет выполнения устройства 8 аналого-цифрового преобразования с предварителным усилением сигнала дифференциальной нелинейности на переменном токе и согласования уровня этого сигнала со шкалой преобразования аналого-цифрового преобразователя 12 и исключения накопления ошибок при вычислении кодов поправок. Повышение быстродействия обусловлено совмещением процесса вычисления кодов поправок с циклом преобразования входного кода. 2 з.п. ф-лы, 5 ил.

Цифроаналогевый преобразователь с автоматической коррекцией нелинейности работает следукяцим образом,

Цифроаналоговый преобразователь с . автоматической коррекцией нелиней-

8„соОа ОО...ОО +10 а„, а,,, .а j,a,, эквивалентная разности

/

-гтг- а:,

.П-1

h-1 2J

ТГ П - 9

2J., 2

в результате на выходе умножителя 24 устанавливается код М, эквивалентный произведению

SnN«,

,-f

а;)-Д

Аи(у. п

который с появлением импульса на пятом выходе блока 11 управления (фиг.4е) заносится в накапливающий сумматор 25,

После этого на третьем выходе блока I I управления (фи.г,4г) устанавливается Гсигнал логического нуля, переводящий регистр сдвига 22 в режим сдвига кода. Одновременно блок 11 управления устанавливает на адресных входах ОЗУ 9 следующую кодовую комбинацию - О,,,01,.в результате чего, на информационных выходах ОЗУ 9 устанавливается код К„., дифференциальной нелинейности ,(пм(п-О-го разряда второго ЦАП 5, С появлением импульса на четвертом выходе блока 11 управления осуществляется сдвиг кода, хранящегося в регистре сдвига 22, В сумматоре 23 определяется сумма двух кодов

, 050 а,, 00,,,00 +

о

+ 10 а. а,.,, ,,,а,0,

эквивалентная разности „п-гh-z

а,., -Z.

Н этом на выходе умножителя устанавливается код М „., Sn,,N., , эквивалентный произведению

П-2

2 п-{

п-г

1J

n-i

aj) X

Л,и рЛп-11 который с появлением импульса на пятом выходе блока 11 управления (фиг,4е) заносится -в накапливающий сумматор 25,

Дальнейшие (К-2) тактов определения кода поправки к выходному сигналу второго ЦАП 5 где К - число его корректируемых старших разрядов аналогичны второму такту.

После окончания последнего такта на втором выходе блока 1 управления (фиг,4в) вырабатывается единичный импульс, по которому код поправки

1594699

20

25

30

5

с выхода накапливающего сумматора 25 заносится во второй регистр 2, преобразуется в аналоговый сигнал в пер- ном ЦАП 6 и суммируется в аналоговом сумматоре 7 с выходным сигналом второго ЦАП 5, компенсируя тем самым дифференциальную нелинейность последнего, Установка накапливающего сумматора Q 25 в нулевое состояние осуществляется сигналом логической единицы на шестом выходе блока I1 управления (фиг.4ж)„

Работа преобразователя в режиме 15 Определение дифференциальных нелинейно ст ей. По шине управления мом работы преобразователя на чет- вертый вход блока II управления . (фиг,56) поступает сигнал логической единицы, по которому на первом выходе блока 11 управления (фиг,5г) устанавливается сигнал логической t единицы. При этом выходы мультиплексора 3 соединяются с его вторыми входами, подключенными к информационным выходам формирователя 10 кодов, ОЗУ 9 переводится в режим занесения . информации, а второй регистр 2 и первый ЦАП 6 устанавливается в нулевое состояние. Одновременно блок 11 управления на адресных входах ОЗУ 9 устанавливает нулевую кодовую комби- - нацию (фиг,5ж,з,и), а на восьмом вы- .ходе блока 11 управления (фиг,5е) 5 вырабатывается единичный импульс, по которому формирователь 10 кодов начинает формирователь периодически повторяющиеся комбинации смежных кодов 100,,,00 (0) и 011,,,11 (1)(в- скобках указан управляющий сигнал допол штельного младшего разряда ЦАП 5 и ЦАП 6). В результате, на вы- ходе аналогового сумматора 7 образуется периодически повторяющийся сигнал прямоугольной формы, аьяшитуда которого из;меряется устройством 8 аналого-цифрового преобразования. На синхронизирующий вход устройства поступает сигнал с первого выхода формирователя 10 кодов, позволяющий определить знак амштнтуды импульса. По окончании измерения амплитуды импульса устройство 8 вырабатывает единичный импульс Конец преобразования, по которому осуществляется занесение ко- да Nj дифференциальной нелинейности п-го разряда второго ЦАП 5 в ОЗУ 9, а блок II управления устанавливает на адресных входах ОЗУ 9 сле0

5

0

дующую кодовую комбинацию - 0,,,01, Кроме того, формирователь 10 кодов начинает формировать периодически повторяющиеся комбинации следукщих смеж- ных кодов 010,,,00(0) и 001,.в11(1), Последующие (К-1) тактов определения дифференциальных нелинейностей второго ЦАП 5 аналогичны первому такту.

По окончании определения кодов

дифференциальных нелинейностей i-ro разряда второго ЦАП 5 и занесения их в ОЗУ 9 формирователь 10 кодов вырабатывает единичньш импульс, поступающий на первый вход блока 11 управле- кия (фиг,5а) и устанавл:ивающий на его первом выходе (фиг,5г) -сигнал логического нуля, подготавливающий преобразователь к преобразованию входного кода. После этого на седьмом выходе блока 11 управления (фиг,5д) вырабатывается единичньй импульс, поступающий на выходную шику готовности результата.

Для измерения дифференциальной не- линейности характеристики преобразования ЦАП 5 на его входы поступают периодически повторяющиеся комбинации смежных кодов, В данном случае,, в ЦАП 5 осуществляется коммутация

и дополнительного младшего разряда,, Устройство 8 аналого-цифрового преобразования осуществляет преобразова кие периодически изменяющегося выходного сигнала ЦАП 5, которое пред- варительно усиливается усилителем 17 переменного тока, и запоминается в аналоговом запоминающем устройстве 13, С помощью конденсатора 18 из сигнала с выхода ЦАП 5 л:сключается

постоянная составляющая, в результате чего получают переменный сигнал прямоугольной формы со скважностью., равной 2, Полученный сигнал усиливается каскадом на операционном усили- теле. 18, коэффициент передачи которого (определяемый соотношением сопротивлений резисторов 20 и 21) выбирается из условия согласования уровня максимального значения амплитуды пере менного сигнала со шкалой преобразования аналого-цифрового преобразователя 12, С помощью ключа 16 (последний переключается синхронно со сме ной значений смежных кодов на входе ЦАП 5) осуществляется выпрямление переменного сигнала, фаза которого однозначно связана со знаком дифференциальной нелинейности характеристи:ки

0

5 О

е д

з л

5

преобразования ЦАП 5, Выпрямленное напряжение запоминается на конденсаторе 15 и с выхода операционного усилителя 14 поступает на вход аналого- цифрового преобразователя 12, С ин- формацио1шых выходов последнего сфор- Мированный код со знаковым разрядом поступает на информационные входы ОЗУ 9, Аналого-цифровой преобразователь 12 формирует также сигнал окончания преобразования, с помощью которого полученный код .записывается в ОЗУ 9,

Введение в состав аналого-цифрового преобразователя 12 усилителя 17 переменного тока и устранение накопления ошибки при вычислении кодов позволяют повысить точность преобразования устройства, а совмещение процесса вычисления кодов поправок с режимом преобразования входного кода в аналоговый сигнал позволяет повысить быстродействие. Вычисление- кода поправок и его преобразование в аналоговый сигнал ЦАП 6 не увеличивает длительности режима Преобразование входного кода, так как операции над кодами осуществляются достаточно быстро, а время уст-ановления ЦАП 6 существенно меньше времени установления ЦАП 5, Последнее обусловлено тем, что вес выходного сигнала ЦАП 6 в выходном сигнале . всего устройства не велик, следовательно, если ЦАП 5 должен устанавливаться с погрешностью, например, 0,01% и менее, то для ЦАП 6 погрешность установления не должна превышать значения 0,1%,

Блок 11 управления (, 3) тает следующим образом,- В режиме Преобразование входного кода по входной шине управления режимом работы на четвертый вход блока 11 управления поступает сигнал логического нуля,При зтом триггер 31 находится в единичном состоянии, С поступлением по входной шине Занесе ния входного кода единичного импульса на третий вход блока 1I триггер 30 через одновибратор 26 устанавливается в единичное состояние и запускается генератор 32 импульсов. Одновременно обнуляются счетчик 33 и через элемент ИЛИ 35 счетчик 34 и на адресных входах ОЗУ 9 (фиг,1) устанавливается начальная (нулевая) кодовая комбинация. Сигналом с. инвертирующего

выхода триггера 30 разрешается занесение информации в накапливающий cyi матор 25 (фиг, 2), После -прохождения двух импульсов с генератора 32 через счетчик 33, на выходе элемента И 38 вырабатывается импульс, по которому информация заносится в регистр 22 сдвига (фиг,2), С поступлением третьего импульса с генератора 32 на вы- ходе элемента И 39 вырабатывается импульс занесения информации в накапливающий cyViMaTop 25 (фиг,2), а с поступлением четвертого импульса на выходе элемента И-ИЛИ 37 при наличии единичного уровня на выходе элемента И 40 формируется первый импульс, подсчитываемый счетчиком 34, В результате на адресных входах ОЗУ 9 (фиг, 1) устанавливается следующая кодов.ая комбинация (00,,, 1), а на выходе элемента ИЛИ 36 - нулевой сигнал разрешагаций сдвиг информации в регистре 22 (фиг,2), Шестым импульсом с генератора 32 на выходе элемен- та И 38 Jвыpaбaтывaeтcя очередной импульс, по которому сдвигается информация в регистре 22 (фиг,2), а седьмым импульсом генератора 32 на выходе элемента И 39 -формируется импульс по которому осуществляется операция суммирования в накапливающем сумматоре 25 (фиг,2). С приходом восьмого импульса с генератора 32 состояние счетчика 34 увеличивается на едини- цу; и на адресных входах ОЗУ 9 (фиг, 1) устанавливается очередная кодовая комбинация и т,д, до прихода К-го , импульса. По этому импульсу на счетчике 34 устанавливается такой код, при котором с помощью - элемента И 41 и одновибратора 29 вырабатыва- ется импульс для занесения кода поправки в регистр 2 /фиг, 1 , а триггер 30 устанавливается в нулевое состояние, сигналом с инвертируклце- го выхода которого обнуляется на-. каплйвающий сумматор 25 (фиг,2),С приходом сигнала логической единицы по входной шине управления режимом на четвертый вход блока 11 управления устройство переходит в. режим Определение дифференциальной нелинейности,триггер 31 и счетчик 34 обнуляются. Сигналом с инвертирующего выхода триггер.а 31 переводится в режим занесения информации ОЗУ 9, обнуляется регистр 2, выходы формирователя 10 кодов подключа

ются к управляющим входам ЦАП 5 и к блоку 4 вычисления поправок (фиг,1), Поскольку счетчик 34 находится в нулевом состоянии, на адресные входы ОЗУ 9 поступает нулевая кодовая комбинация. Сигналом с выхода одно- вибратора 27 дается разрешение формирователю 10 кодов на генерацию периодически повторяющихся- смежных кодов По окончании измерения устройством 8 амплитуды импульса, последний вырабатывает сигнал окончания преобразования, по которому на выходах счетчика 34 устанавливается код 00,,,О Г и т,д. По окончании занесения информации в ОЗУ 9 формирователь 10 кодов вырабатывает команду, переводящую в единичное состояние триггер 31, и преобразователь подготавливается к переходу в режим Преобразование входного кода.

Формул

изобретения

-|,, jj-,,, 253Q4045 35

55

в виде аналого-цифрового преобразозза-- теля,-аналогового запоминающего устройства на первом операционном усилителе, первом конденсаторе и на ключе и усилителя переменного тока на втором операционном усилителе, втором конденсаторе, первом и втором резисторах, первые выводы которых объединены и подключены к инвертирую- 1дему входу второго операционного усилителя, неинвертиругадий вход которого подключен к шине нулевого потенциала, а выход соединен с вторым выводом первого резистора и информацион- ным входом ключа, выход которого соединен с первым выводом первого конденсатора и неинвертирукщим входом первого операционного усилителя, выход которого соединен со своим инвер- тирующим входом и подключен к информационному входу аналого-цифрового преобразователя, второй вывод первого ковденсатора соединен с шиной нулевого потенциала, второй вывод второго резистора соединен с первым выводом второго конд енсатора, второй вывод ко которого является информационным входом устройства аналого-цифрового преобразования, управлякщий вход ключа является входом синхронизации устройства аналого-цифрового преобразования, выходы аналого-цифрового преобразователя соединены с соответствующими информационными входами оператив но го. запоминанщего устройства, а выход готовности, результата преобраг зования соединен с входом разрешен1;1я записи оперативного запоминающего устройства, с первым входом формиро- вателя кодов и вторым входом блока управления, третий вход которого является входной шиной занесения информации и объединен с входом синхронизации первого регистра, информа- ционные входы которого являются входной шиной преобразуемого кода, а выходы соединены с соответствукяцими вторыми информационными входами мультиплексора, выходы которого под- ключены к соответствукщим входам это- рого цифроаналогового преобразователя и к соответствугацим первым информационным входам блока вычисления поправок, выходы которого соединены с соответствукщими . информационными входами второго регистра, вход обнуления которого объединен с входом управления мультиплексора и соединен.с первым выходом, блока управления, четвертый вход и седьмой .выход которого являются соответственно входной шиной управления режимом и выходной шиной готовности- результата преобразования, восьмой выход блока управления соединен с вторым входом формирователя кодов, а вы ходы группы выходов соединены с соответствукщими адресными входами оперативного запоминающего устройства, выходы которого соединены с соответствукщими вторыми информационными входами блока вычисления поправок,

2, Преобразователь по п, 1 , отличающий ся тем, что блок управления выполнен в виде четырех одновибраторов, двух RS-триггеров, генератора импульсов, двух счетчиков импулвсов, элемента И-ИЛИ, двух элементов ИЛИ и четырех элементов И выходы первого и второго из которых являются соответственно четвертым и пятым выходами блока, неин- .вертирующий вход первого элемента И объединен с инвертирующим входом второго элемента И, первым входом третьего элемента И и подключен к первому выходу первого счетчика импульсов, вход синхронизации которого подключен к выходу генератора импулсов, управляняций вход которого соединен с прямым выходом первого RS-триггера, инвертирующий выход которого является шестым выходом блока, а S-вход соединен с входом обнуления первого счетчика импульсов, с первым входом первого элемента ИЛИ и соединен с выходом первого одновибратора, вход которого является третьим входом блока,вход второ го одновибратора является четвер- ,тым входом блока, выход второго одновибратора является восьмым выходом блока и соединен с вторым входом первого элемента ИЛИ и с R-входом второго RS-триггера, неинвертирующий вькод которого подключен к первому входу первой групп входов элемента И-ИЛИ и к входу третьего одновибратора, выход которого является седьмым выходом блока, второй вход первой группы входов элемента И-ИЛИ соединен с выходом третьего элемента И, второй вход которого объединен с неинвертирующим

входом второго и инвертирующим входом первого элементов И и подключен к второму выходу первого счетчика импульсов, выход элемента И-ИЛИ соединен с входом синхронизации второго счетчика импульсов, вход обнуления которого подключен к выходу первого элемента ИЛИ, а выходы соединены с соответствующими входами второго элемента ИЛИ и с соответствующими входами четвертого элемента И и являютч:я группой выходов блока, инвертирующий выход второго элемента ИЛИ является, третьим выходом блока, инв,ертйрующий выход четвертого эле мента И соединен с входом четвертого одновибратора, выход которого явля- ётся вторым выходом блока и соединен с R-входом первого RS-триггера, S-вход второго RS-триггера является первым входом блока, инвертирующий выход второго RS-триггера соединен с первым входом второй группы входов элемента И-ИЛИ и является первым выходом блока, второй вход второй группы входов элемента И-ИЛИ являет-; ся вторым входом блока,

ра, выходы которого являются выходами блока, а входы синхронизации и обнуления яйляются соответственно

третьим и четвертым управлякщими входами блока, информационные входы накапливающего сумматора подключены к соответствукщим выходам умножителя, первые входы которого являются

вторыми информационными входами блока,а вторые входы подключены к соответствующим выходам сумматора, 1-2 первых входов которого соединены с соответствующими выходами

регистра сдвига (1-1 )-й и 1-й первые входы соединены соответственно с шинами логического нуля и шиной Логической единицы, вторые входы сумь5атора, кроме (l-l)-ro подключены к шине логического нуля, а (1-1 )-й второй вход сумматора подключен к дополнительному выходу регистра сдвига, информационные входы параллельного ввода данных которого являются первыми информационными входами блока, информационный вход последовательного ввода данных ре- гистра сдвига подключен к шине ло- гичеСКОРО нуля, входы управления режимом занесения-сдвига и разрешением занесения-сдвига регистра сдвига являются соответственно первым и вто- рым управляющими входами блока.

Фи&2

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1287290A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1990-09-23—Публикация

1988-06-10—Подача