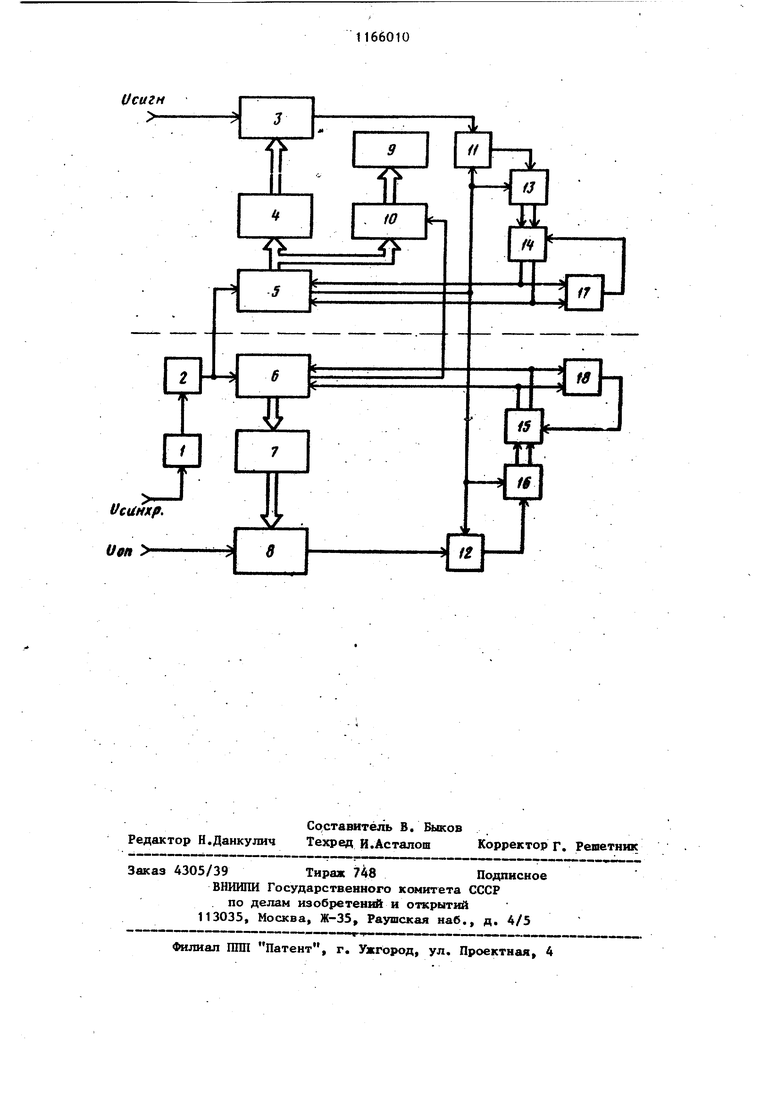

11 Изобретение относится к электроизмерительной технике и предназначено для точного цифрового измерения фазовых сдвигов между двумя исследуе мыми напряжениями искаженной формы в условиях действия шумовых помех. Цель изобретения - уменьшение погрешности измерения фазовых сдвигов при нелинейных искажениях исследуемых сигналов, а также при воздействии шумов и помех. Предлагаемое изобретение позволяет определять истинную фазу основной гармоники каждого из исследуемых сигналов, а затем осуществлять их сравнение. Высокая точность измерения фазовых сдвигов между основными гармониками зашумленных и искаженных сигналов достигается за счет формирования высокоточных сигналов копий, имеющих тот же период, что и исследуемыеСигналы, и непрерывного отслеживания этих сигналов по фазе. На чертеже представлена структурйая схема цифрового автокомпенсацион ного фазометра. Фазометр содержит два идентичных канала корреляционно-фазовой обработки, а также блок 1 умножения частоты генератор 2 импульсов, перемно жаюи|ий цифроаналоговый преобразователь 3, постоянньй запоминакяций элемент 4, пересчетные элементы 5 и 6, постоянньй запоминакядий элемент 7, перемножающий цифроаналоговьн преобразователь 8, цифровой отсчетный блок 9, регистр 10 памяти, интеграторы 11 и 12, компарагор 13, реверсивные счетчики 14 и 15, компаратор 16, элементы ИЛИ 17 и 18. Каждый канал содержит перемножающий цифройналоговьй преобразователь 3 (8), аналоговый вход которого является входом канала, цифровые входь соединены с выходами постоянного запоминающего элемента 4 (7), а выход подключен к входу интегратора 11 (12). В свою очередь выход интегратора 11 (12) соединен с входо компаратора 13 (16). Интеграторы 11 и 12 и компараторы 13 и 16 своими входами синхронизации подключены к одному из пересчетных элементов, например 5. К управлягацим входим пересчетного элемента 5 (6) подсоединены выходы реверсивного счетчика 14 (15) 1,0 подключенного своими входами к выходам компаратора 13 (16), Входы элемента ИЛИ 17 (18) соединены с выходами реверсивного счетчика 14 (15), а выход элемента ИЛИ 17 (18) подключен к установочному входу реверсивного счетчика 14 (15). К тактовым входам пересчетных элементов 5 и 6 .подсоединен генератор 2 импульсов, соединенный с блоком 1 умножения частоты. Блок 1 и генератор 2 являются общими для обоих каналов фазометра. Информационные выходы одного из пересчетных элементов, например 5, и выход заполнения другого, например 6, подключены к регистру 10 памяти, соединенному с цифровым отсчетным блоком 9, Блоки 9 и 10 также являются общими для обоих каканалов фазометра. Фазометр работает следующим образом. Исследуемые сигналы искаженной формы вместе с аддитивными шумами и помехами поступают на аналоговые входы перемножающих цифроаналоговых преобразователей 3 и 8. На цифровые входы последних подается периодически изменяющийся во времени параллельный цифровой код, значения которого соответствуют выборкам сигнала строго гармонической формы, следующего с той же частотой, что и исследуемьй сигнал. Период изменения цифрового кода TO где Tj. - длительность периода исследуемого сигнала; m - целое число тактов изменения цифрового кода. Перемножающие цифроаналоговые преобразователи 3 и 8 осуществляют непрерьшное корреляционное преобразование, т.е. непрерывное перемножение исследуемого сигнала на его квазигармоническую копию. Постоянная составляющая выходного напряжения перемножающего цифроаналогового преобразователя 3 и 8 зависит от фазового сдвига между основ-, ными гармоническими составлянидими перемножаемых исследуемого сигнала и сигнала копии. Эта зависимость имеет гармонический (косинусоидальный) характер. Постоянная составляющая выходного напряжения преобразователя обращается в нуль при 90°-о или 270-ом фазовом сдвиге перемножаемых сигналов. Выходные напряжения перемножающих цифроаналоговых преобразователей 3 и 8 усредняются при помощи интеграторов 11 и 12 в течение интервалов времени, кратны полупериоду исследуемых сигналов, . с целью исключения влияния высших гармонических составляющих, попадаю щих на входы интеграторов 11 и 12. Время интегрирования задается одним из пересчетных элементов 5 и 6. Ком параторы 13 и 16 формируют импульсы накапливаемые в реверсивных счетчиках 14 и 13. Если выходные напряжения интеграторов 11 и 12 оказываю ся положительными, компараторы 13 и 16 формируют импуйьсы, поступшощие на входы сложения реверсивных счетчиков 14 и 15. При отрицательной полярности выходных напряжений интеграторов 11 и 12 формируемые компараторами 13 и 16 импульсы поступают на входы вычитания. Емкость N реверсивных счетчиков 14 и 15 выбирается в зависимости от соотношения сигнал/шум исследуемых сигналов и заданной дисперсии результата отсчета фазового сдвига. Чем меньше соотношение сигнал/шум и меньше требуемая дисперсия отсчета фазового сдвига, тем больше требуется емкость N реверсивных счетчиков 14 и 15. В исходном состоянии на реверсив ных счетчиках 14 и 15 устанавливается код - , Такое же значение кода устанавливается при помощи эле ментов ИЛИ 17 и 18 в те моменты времени, когда в реверсивные счетчики 14 и 15 будет записано суммарное приращение или При этом импульсные cигнaJПll переполнения и обнуления реверсивньк счетчиков 14 и 15 управляют моментами заиолнения пересчетных элементов 5 и 6 смещая их в сторону достижения компенсации основных гармоник исследуе мого сигнала основными гармониками сигналов копий, при которой постоян ные составляющие выходных напряжений перемножающих аналогоцифровых преобразователей 3 и В обратятся в нуль. Коэффициент деления частоты обоих пересчетных элементов 5 и 6 или их емкость п выбирается в зависимости от требуемого минимально104го дискрета по фазе , т.е. в зависимости от заданной разрешакицей способности измерения фазовых сдвигов:При лЧд О, Г п - 3600. Код пересчетных элементов 5 и 6 изменяется циклически через интервалы времени, равные периоду следования импульсов с генератора 2 импульсов . Значения кодов пересчетных элементовNnc(t) выражают текущее значение фазы С( (t) выходных напряжений пересчетных элементов 5 и 6, Постоянные запоминающие элементы 4 и 7 преобразуют значения кодов фазы, формируемые пересчетньми элементами 5 и 6, в весовые значения кодов строго гармонической функции - синуса или косинуса с нормированной амплитудой NMOIKC соответствующей максимальному значению положительной полуволны колебания. Количество ячеек постоянных запоминающих элементов 4 и 7 должно соответствовать количеству устойчивых состояний пересчетных элементов 5 и 6 п. С учетом свойств симметрии гармоничеЬкой функции это количество может быть уменьшено в два либо в четыре раза. Выходной код постоянных запоминающих элементов 4 и 7, будучи поданным на перемножающие цифроаналоговые преобразователи 3 и 8, изменяет их коэффициенты передачи по строго гармоническому закону.При подаче на входы перемножшощих цифроаналоговых преобразователей 3 и В исследуемых сигналов на их выходах образуется напряжение, пропорциональное фазовому сдвигу между основными гармониками сигналов копий и основными гармониками зашумленньк искаженных исследуемых сигналов. Процесс уравновешивания фазовых сдвигов происходит следующим образом. Выходные напряжения перемноающих цифроаналоговых преобразователей 3 и 8, пропорциональные начальному рассогласованию фазо5. вых сдвигов исследуемых сигналов и весовых коэффициентов копий (с учетом сдвига на 90 или 270), усредняются в интеграторах 11 и 12 и сравниваются с нулевым значением на входах компараторов 13 и 16. Зна рассогласований определяет полярность выходных напряжений интеграторов 13 и 16 и входы реверсивных счетчиков 14 и 15, на которые подается периодическая последователь.-ность импульсов с компараторов 13и 16. В реверсивных счетчиках 14 и 15 происходит накопление кода нарастаю щим или убывающим итогом соответственно. При суммарных цриращениях ко дов реверсивных счетчиков 14 и 15 или -Y, что соответствует результируняцему коду N или О, на выходных шинах реверсивных счетчиков 14и 15 формируются импульсы, изменяющие значения кода пересчетных элементов 5 и 6 в сторону уменьшения фазового рассогласования сравниваеьшх в перемножителе сигналов относительно значения ±90. После этого посредством элементов ИЛИ 17 и 18 устанавливается начальньгй код реверсивных счетчиков 14 и 15 и цикл .накопления повторяется до тех 10Ь пор, пока не наступит равновесие, характеризующееся уменьшением до нуля составляющих выходных напряжений перемножающих цифроаналоговых преобразователей 3 и 8 и выходных напряжений интеграторов 11 и 12. В этом случае сдвиг фаз основных Еаргармоник исследуемого сигнала и сигнала копии приобретает значение 90, а выходные импульсы компараторов 13 и 16 равновероятно проходят на суммирующий и вычитающ1й входы реверсивных счетчиков 14 и 15, в результате чего импульсы на их выходах будут отсутствовать. Разность кодов пересчетньк элементов 5 и 6, фиксируемая регистром 10 памяти, приобретает установившееся значение и показания цифрового отсчетного блока 9 застабилизируются. Блок 1 у.1Ножения частоты предназначен для синхронизации работы автокомпенсационного фазометра. Его коэффициент умножения выбирается равным коэффициенту деления п частоты пересчетных элементов 5 и . 6. При этом периоду исследуемых сигналов всегда будет соответствовать целое число тактов изменения цифрового кода на выходе постоянных . запоминакяцих элементов 4 и 7.

UcuZH

| название | год | авторы | номер документа |

|---|---|---|---|

| Радиоимпульсный фазометр | 1985 |

|

SU1257558A1 |

| Анализатор частотного спектра | 1980 |

|

SU900209A1 |

| Двухканальный цифровой следящий фазометр | 1974 |

|

SU492826A1 |

| Двухканальный цифровой следящий фазометр | 1976 |

|

SU655987A1 |

| Цифровой компенсационный фазометр | 1980 |

|

SU920563A1 |

| Цифровой компенсационный фазометр | 1980 |

|

SU924611A1 |

| Цифровой коммутационный фазометр | 1978 |

|

SU765749A1 |

| Аналого-цифровой низкочастотный фазометр | 1990 |

|

SU1780042A1 |

| Цифровой фазометр | 1976 |

|

SU664120A1 |

| Цифровой автокомпенсационный фазометр | 1984 |

|

SU1196777A1 |

ЦИФРОВОЙ АВТОКОМПЕНСАЩЮННШ ФАЗОШТР, содержащий цифровой оТсчетн блок, регистр памяти, импульсный генератор, два реверсивных счетчика, два элемента ИЛИ и два пересчетных элемента, которые подключены своими входами управления вместе с входами элементов ШШ к выходам реверсивных счетчиков, причем выходы элементов ИЛИ соединены с установочными входами реверсивных счетчиков, а импульсный генератор подключен к такткруняцим входам пере-, счетных элементов, информационные выходы одного из которых соединены с регистром памяти, подключенным к цифровому отсчетному блоку, отличающийся тем, что, с целью уменьшения погрешности измерения фазовых сдвигов при нелинейных искажениях исследуемых сигналов, а также при воздействии шумов и помех, в него введены блок умножения частоты, два интегратора, два компаратора и два перемножающих цифроаналоговых преобразователя, аналоговые входы которых соединены с входами фазометра , а цифровые входы их - с информационными выходами пересчетных элементов через постоянные запоминающие элементы, выходы перемножающих цифро(Л а1налоговых преобразователей соединены с соединенными последовательно интеграторами и компараторами,входы синхронизации которых соединены с одним пересчетным элементом,другой пересчетный элемент выходом заполнения соединен с регистре памяти,выходы компара9) Од торов подключены к реверсивным счетчикам, вход импульсного генератора соединен с блоком умножения частоты, вход которого соединен с одню иэ входов фазометра либо со специальным входом синхронизации.

| ЦИФРОВОЙ АВТОКОМПЕНСАЦИОННЫЙ ФАЗОМЕТР | 0 |

|

SU245913A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Висячий замок с кольцевой поворотной дужкой | 1923 |

|

SU808A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-07-07—Публикация

1983-11-25—Подача