2. Детектор по п. 1, о т л ич а ю щ и и t я тем, что в него дрполнительно введены два транзисторных эмиттерных повторителя, истоковый повторитель на полевом транзисторе с изолированным затвором и второй диод, причем средний вьгеод делителя напряжения соединен с другим выводом первого диода через первый транзисторный эмиттерный повторитель и с выходом первого операционного неинвертирукндего усилителя через второй диод, на входе второго операционного инвертирующего усилителя включен истоковый поторитель на полевом транзисторе с изолированным затвором, на выходе второго операционного инвертирующего усилителя включен второй тран зисторный эмиттерный повторитель, а траизисторы обоих эмиттерных повторителей имеют Проводимости различного типА.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пиковый детектор | 1976 |

|

SU592011A1 |

| УСТРОЙСТВО ЗАЩИТНОГО ОТКЛЮЧЕНИЯ ЭЛЕКТРОТЕХНИЧЕСКИХ ПРИБОРОВ И АППАРАТОВ | 2007 |

|

RU2321125C1 |

| Выпрямитель для дуговой сварки с комбинированными внешними характеристиками | 1988 |

|

SU1637969A1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ПИКОВЫЙ ДЕТЕКТОР | 2019 |

|

RU2708687C1 |

| ПИКОВЫЙ ДЕТЕКТОР С ДИФФЕРЕНЦИАЛЬНЫМ ВХОДОМ | 2018 |

|

RU2700327C1 |

| Пиковый детектор | 1984 |

|

SU1325370A1 |

| Преобразователь электрического напряжения в ток | 1990 |

|

SU1817030A1 |

| Пиковый детектор импульсов | 1985 |

|

SU1272259A1 |

| Пиковый детектор | 1979 |

|

SU815648A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

1. ПИКОВЫЙ ДЕТЕКТОР, содержащий первьш операционный неинвертиру ощий fcилитeль,. вход которого 13 Б1БЛИОТВ{ соединен через резистор с источником, входных импульсов и с одним из выводов резистора обратной связи, последовательно включенные первый диод и конденсатор, общий вьгаод которых соединен с входом второго операционного инвертирующего усилителя, выход которого соединен с другим выводом конденсатора и с другим выводом резистора обратной связи, отличающийся тем, что, с целью повышения точности измерений, в него введен делитель напряжения,, включенный на выходе первого i операционного неинвертирукщего усилителя, а средний вывод делителя сл с напряжения соединен с другим вьгаодом диода. САд о: (:

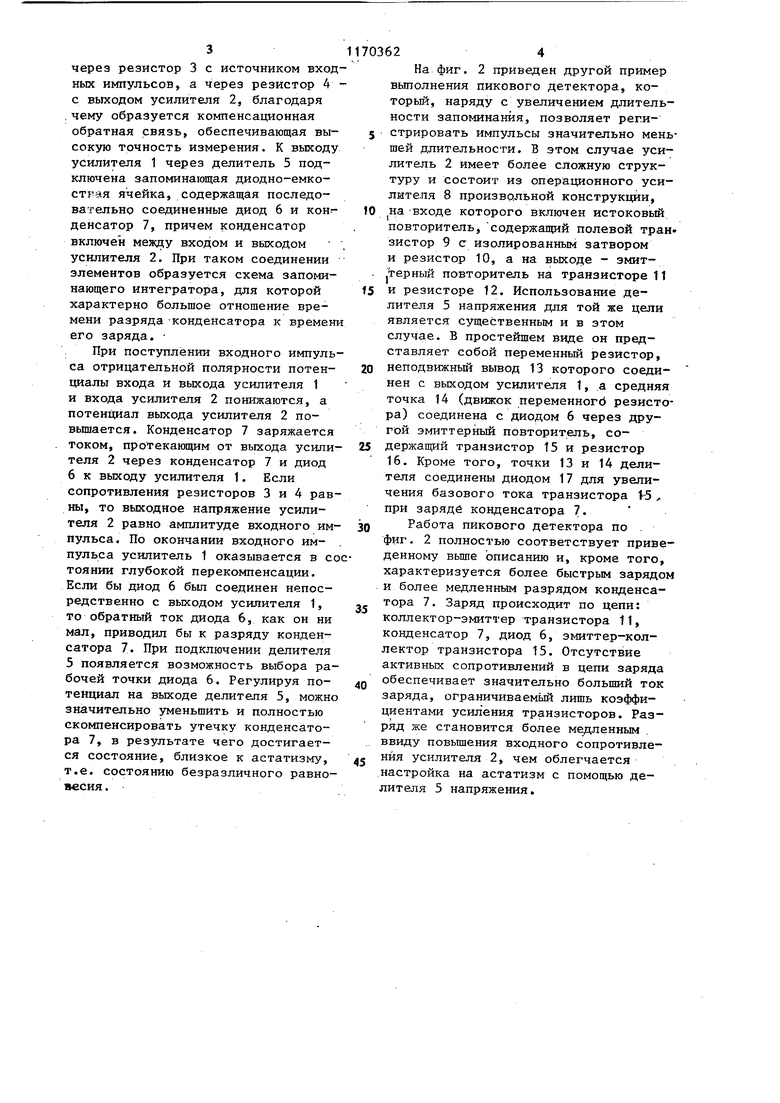

Изобретение относится к измерительной технике и может быть использовано в устройствах для аналогового запоминания экстремально го значения импульсного напряжения Известен пиковый детектор, содержащий диодно-емкостную ячейку, операционные усилители и цепь обратной связи СОНедостатком детектора является низкая точность измерения, а также то, что он не позволяет увеличить длительность запоминания без сущес венного увеличения емкости конденсатора. Наиболее близким к предлагаемом является пиковьй детектор с запоми нающим интегратором, в котором . диодно-емкостная ячейка включена между первым и вторым операционными усилителями, охваченными компен сационной обратной связью t 3Недостатком данного пикового детектора является малая длительнос запоминания выходного напряжения j обусловленная утечкой конденсатора и обратным током диода, Целью изобретения является повы шение точности измерения. Поставленная цель достигается тем, что в пиковый детектор, содержащий первый операционньй неинвертирующий усилитель, вход которого соединен через резистор с источником входных импульсов и с одн из вьшодов резистора обратной связ последовательно включенные первый диод и конденсатор, общий вывод ко торых соединен с входом второго оп рационного инвертирующего усилителя, выход которого соединен с другим выводом конденсатора и с другим выводом резистора обратной связи, введен делитель напряжения, включенный на выходе первого операционного неинвертирующего усипителя, а средний вьтод делителя напряжения соединен с другим выводом диода. Кроме того, в детектор дополнительно введены два транзисторных эмит терных повторителя истоковый повторитель на полевом транзисторе с изолированным затвором и второй диод, причем средний вывод делителя напряжения соединен с другим выводом первого диода через первый транзисторный эмиттерный повторитель и с выходом первого операционного неинвертирующего усилителя через второй диод, на входе второго операционного инвертирующего усилителя включен истоковьй повторитель на полевом транзисторе с изолированным затвором на выходе второго операционного инвертирующего усилителя включен второй транзисторный эмиттерный повторитель, а транзисторы обоих эмиттер ных повторителей имеют проводимости различного типа. На фиг. 1 и 2 приведены примеры вьтолнения предлагаемого пикового детектора. Пиковый детектор пофиг. 1 содержит первый усилитель 1 и второй усилитель 2, вьтолненные на операционных усилителях неинвертирукицего и инвертирующего типов соответственно. Вход усилителя 1 соединен

3

через резистор 3 с источником входных импульсов, а через резистор 4 с выходом усилителя 2, благодаря чему образуется компенсационная обратная связь, обеспечивающая высокую точность измерения. К выходу усилителя 1 через делитель 5 подключена запоминающая диодно-емкостгая ячейка, содержащая последовательно соединенные диод 6 и конденсатор 7, причем конденсатор включен между входом и выходом усилителя 2. При таком соединении элементов образуется схема запоминающего интегратора, для которой характерно большое отношение времени разряда -конденсатора к времени его заряда.

При поступлении входного импульса отрицательной полярности потенциалы входа и выхода усилителя 1 и входа усилителя 2 понижаются, а потенциал выхода усилителя 2 повышается. Конденсатор 7 заряжается Током, протекающим от выхода усилителя 2 через конденсатор 7 и диод 6 к выходу усилителя 1. Если сопротивления резисторов 3 и 4 равны, то выходное напряжение усилителя 2 равно амплитуде входного импульса. По окончании входного импульса усилитель 1 оказывается в сотоянии глубокой перекомпенсации. Если бы диод 6 был соединен непосредственно с выходом усилителя 1, то обратный ток диода 6, как он ни мал, приводил бы к разряду конденсатора 7. При подключении делителя 5 появляется возможность выбора рабочей точки диода 6. Регулируя потенциал на выходе делителя 5, можно значительно уменьшить и полностью скомпенсировать утечку конденсатора 7, в результате чего достигается состояние, близкое к астатизму, т.е. состоянию безразличного равновесия.

03624

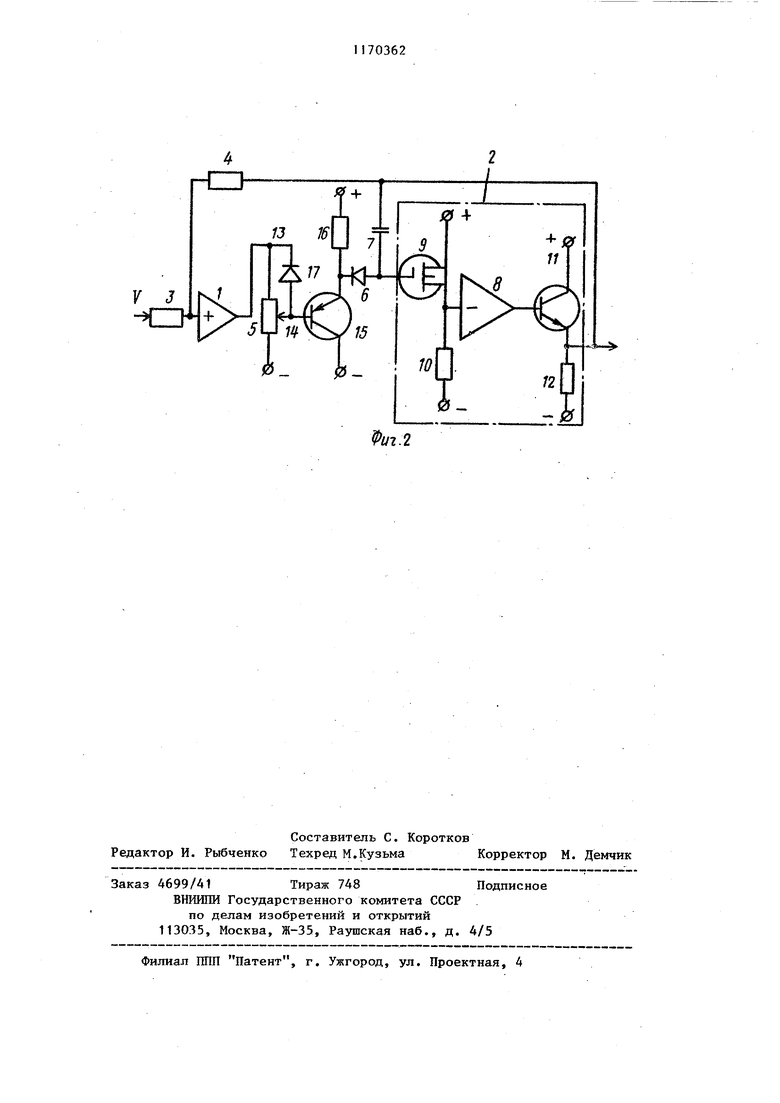

На фиг. 2 приведен другой пример вьтолнения пикового детектора, который, наряду с увеличением длительности запоминания, позволяет регистрировать импульсы значительно меньшей длительности. В этом случае усилитель 2 имеет более сложную структуру и состоит из операционного усилителя 8 произвольной конструкции,

0 на -входе которого включен истоковый повторитель, содержащий полевой транзистор 9 с изолированным затвором и резистор 10, а на выходе - эмит. .терный повторитель на транзисторе 11

S и резисторе 12. Использование делителя 5 напряжения для той же цели является существенным и в этом случае. В простейшем виде он представляет собой переменный резистор,

0 неподвижный вывод 13 которого соединен с выходом усилителя 1, а средняя точка 14 (движок переменногЬ резистора) соединена с диодом 6 через другой эмиттерный повторитель, содержащий транзистор 15 и резистор 16. Кроме того, точки 13 и 14 делителя соединены диодом 17 для увеличения базового тока транзистора V5 , при заряде конденсатора 7.

Q Работа пикового детектора по .

фиг. 2 полностью соответствует приведенному вьше описанию и, кроме того, характеризуется более быстрым зарядом и более медленным разрядом конденсатора 7. Заряд происходит по цепи: коллектор-эмиттер транзистора 11, конденсатор 7, диод 6, эмиттер-коллектор транзистора 15. Отсутствие активных сопротивлений в цепи заряда обеспечивает значительно больший ток заряда, ограничиваемый лишь коэффициентами усиления транзисторов. Разряд же становится более медленным ввиду повьш1ения входного сопротивле, нйя усилителя 2, чем облегчается настройка на астатизм с помощью делителя 5 напряжения.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-07-30—Публикация

1979-04-25—Подача