эо эо а

9д

;о

Изобретение относится к измерительной технике, может быть использовано как для измерения фазовых сдвигов, так и частоты исследуемых сигналов при высокой точности измерений и быстродействии устройства и является дополнительным к авт.св. № 1045155.

Цель изобретения - расширение функциональных возможностей.

Это достигается за счет высокоточного определения частоты сигнала за один измеряемый период путем сравнения измеренного периода сигнала с выбранной мерой времени в виде кода числа N, соответствующей секунде.

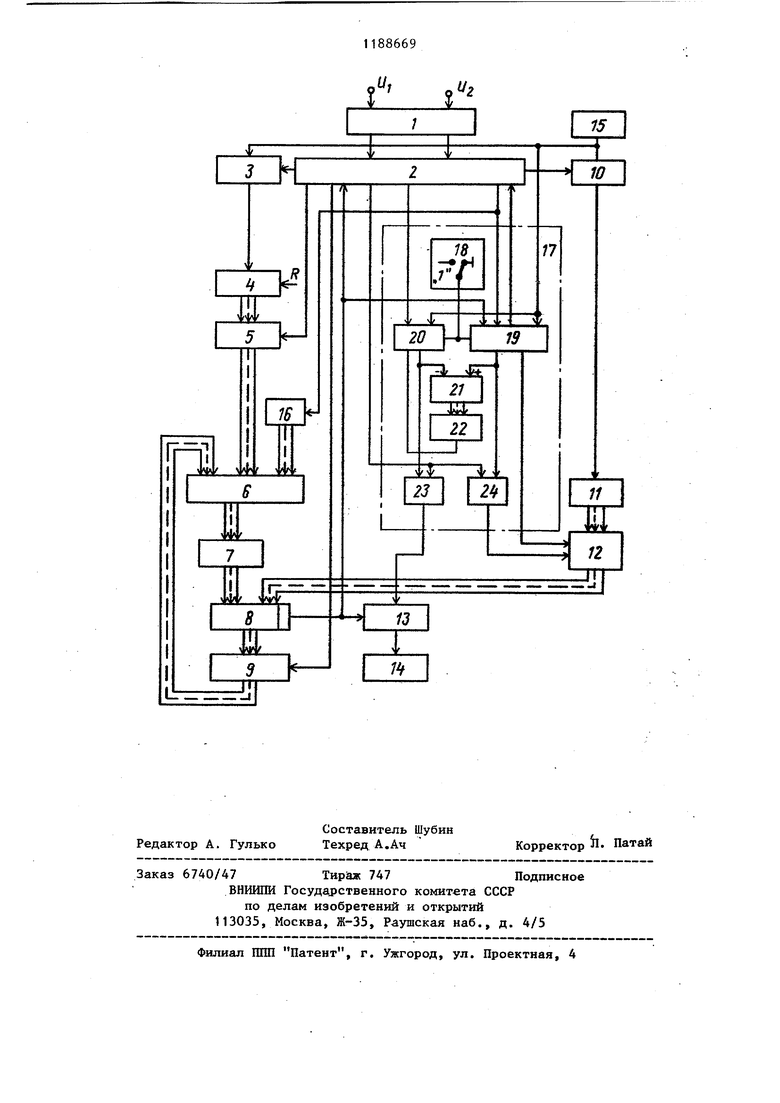

На чертеже представлена блок-схема предлагаемого устройства.

Цифровой фазометр состоит из формирователя 1, первый и второй входы которого подключены соответственно к первой и второй входным шинам устройства, блока 2 управления, первого электронного -ключа 3, первого счетчика 4 импульсов, первого блока 5 вентилей, блока 6 объединения, регистра 7, сумматора 8, второго блока 9 вентилей, второго электронного ключа 10, второго счетчика 11 импульсов первого регистра 12 сдвига, второго регистра 13 сдвига, блока 14 регистрации, генератора 15 импульсов, шифратора 16 кода секунды, синхронизатора 17,

Кроме этого ,синхронизатор 17 состоит из ключа 18, формирователя 19 сигналов сдвига вправо, формирователя 20 сдвига влево, реверсивного счетчика 21 импульсов,дешифратора22, первой схемы ИЛИ 23 и второй схемы ИЛИ 24.

При этом входы фазометра через формирователь 1 подключены к входу блока управления. Генератор 15 подключен к входу синхронизатора 17 и через последовательно включенные ключ 10, счетчик 11, регистр 12 сдвига к второй группе входов сумматора 8, а также через ключ 3, счетчик 4, блок 5 вентилей, блок 6 объединения, регистр 7 к первой группе входов того же сумматора 8. Блок 2 управления подключен выходами к вторым входам ключей 3 и 10, блоку 5 вентилей, шифратору 16 кода секунды, блоку 9 вейтилей, синхронизатору 17 и своими входами подключен к первому и второму выходам синхронизатора. Знаковый регистр сумматора 8 соединен с входом регистра 13 сдвига и первым выходом синхронизатора 17, третий выход которого подключен к второму входу регистра 13 сдвига, подключенного выходами к блоку 14 регистрации. Четвертый и пятый выходы синхронизатора соединены соответственно с управляющими входами регистра 12. Информационные выходы сумматора 8 через блок 8 вентилей подключены к третьим входам блока 6 объединения, вторые входы которого соединены с информационными выходами шифратора 16 кода секунды.

Устройство измеряет (за один период) фазовый сдвиг (fx между двумя синусоидальными сигналами или частоту F одного из них в зависимости от положения ключа 18 и работает следующим образом.

На входы формирователя 1 поступают синусоидальные сигналы U и Uj частотой F. Формирователь 1 преобразует входные синусоидальные сигналы в прямоугольные импульсы, передний фронт которых совпадает с переходами через нуль входных напряжений Эти импульсы поступают на вход блока 2 управления, который формирует одновременно два прямоугольных импульса, имеющих длительности Cf и Ср . Длительность импульса пропорциональна фазовому сдвигу между входными сигналами. Длительность равна период исследуемого напряжения Т (Т 1/F). С помощью генератора 15 импульсов и электронных ключей 3 и 10 длительности импульсов , и с. преобразуются в числоимпульсные коды N соответственно. Код фиксируется в счетчике 4 импульсов и при измерении частоты не используется. Код N фиксируется в счетчике 11 импульсов. При этом

N 1Ы,

где 6 l/f ..„ - период частоты кван

тования .

Измерение частоты исследуемого напряжения с помощью предлагаемого устройства (за один период) основано на определении количества целых периодов исследуемого напряжения и его дробных частей, которое укладьтается во временной базе, равной 1 с. При этом вместо собственно временной баз 1 с используется ее числовой эквивалент N. Величина N определяется значением частоты генератора 15 импульсов N KB- с. Это число N в предлагаемом устрой стве формируется в прямом двоичном коде с помощью шифратора 16 кода секунды . Процесс определения частоты иссле дуемого сигнала F в предлагаемом устройстве состоит из трех этапов: определения числа двоичных разрядов п, необходимых для представления целой части значения измеряемой частоты; формирование т-разрядного двоичного кода измеряемой частоты (т число двоичных разрядов цифровой час ти данного устройства; фиксация запя той между целой и дробной частью кода измеренной частоты, Текущее число п двоичных разрядов необходимых для представления целой части лзмеряемой частоты, определяет ся с помощью неравенства п4-1 Sogj- г) что эквивалентно совместному выполнению неравенств Решение этих неравенств осуществл ется путем последовательного умножения числа N на 2, сравнения этих произведений с числом N, подсчета и фиксации числа п этих сравнений. Эта операция в предлагаемом устройстве осуществляется следующим образом. Из счетчика 11 импульсов код N записывается в регистр 12 сдвига и поступает на входы сумматора 8, который имеет m двоичных разрядов, не считая знакового. Двоичный код секунды N считывается с шифратора 16 кода секунды, записьшается в регистр 7 и поступает на вторые входы сумма- тора Ь. В последнем формируется разность N - NT, знак которой фиксирует ся в знаковом разряде сумматора 8. Если текущая разность N - N-,.0, то синхронизатор 17 формирует сигнал управления сдвига на один разряд вле во (в сторону старших разрядов) содержимого регистра 12 сдвига. При этом код NT сдвигается на один разряд влево,что эквивалентно умножению числа N на 2, а в реверсивный счетчик 21 импульсов, который работает на сложение, поступает один импульсПосле этого в сумматоре 8 формируется знак второй разности N-2 N. Если эта разность положительна, то содержимое регистра 12 сдвига сдвигается на разряд влево, и в реверсивный счетчик 21 импульсов поступает второй импульс. Если сумматор 8 зафиксировал п-ую разность с отрицательным знаком, то содержимое регистра двига 22, равное 2 Nf, больше не сдвигается влево, а в реверсивном счетчике 21 импульсов фиксируется двоичный код числа п. Таким образом, приведенная система из двух неравенств решена и соответственно определено число разрядов п, необходимое для представления в данном измерении целой части значения измеряемой частоты. На этом первый этап работы устройства заканчивается. Отметим, что величина п может принимать значения О, 1, 2,..., тв зависимости от значения величины N. На втором этапе устройство определяется в цифро вой форме какое целое число периодов Т и какая дробная часть его укладывается во временной базе, равной t с. При этом оно формирует соответствующий двоичный код частоты. Для определения разрядных цифр (где Of,- равof, ,« , но О или t) этого кода данное устройство последовательно формирует ш разностей: N - 2 Nf (), а , ,..., ,-„- . а;,..., а„.- N ««„, а, m- « величина, тождественная знаку текущей aj разности, т.е. если aj Отов/J 1, в противном случае ОС J 0. Отметим, что ик, 1 первая значащая цифра кода измеренной частоты. При этом вес зтой единицы равен 2. Из приведенных выражений для разности а следует, что при of, (aj( О) величина 2 N используется для определения разности .. В противном случае используется прет.е. можно записать дыдущая разность, выражение N-NvU(x,... + .,,+ 2Vn + .2-V«,,t.,.)t2- N. Из последнего выражения следует, то с погрешностью ±2 N.-, стремящемся к нулю при увеличении числа т, в числовом эквиваленте временной базы 1 с укладывается 2 +,...,+2 целых числовых эквивалентов периода и определенная дробная его

часть +...+21 . При этом

о h +1 ifi

сумма членов, стоящих в правой части приведенного выражения, представляет собой численное значение кода измеренной частоты. Если последовательно запомнить с помощью регистра сдвига величину W, , то после определения знака т-й разности в регистре сдвига фиксируется параллельный двоичный код измеренного значения частоты.

Предлагаемое устройство выполняет описанные операции следующим образом. После первого сдвига в регистре 12 сдвига в сумматоре 8 всегда формируется положительная разность aj N - 2 N 0. Знак первой разности 1 формируется в знаковом разряде сумматора 8 и записывается в первый (младший) разряд регистра 13 сдвига. При этом текущее значение разности записывается в регистр 7. После этого, производится второй сдвиг содержимого регистра 12 сдвига вправо, и в сумматоре 8 форг мируется вторая разность а N Если вторая разность положительна, то в младший разряд регистра 13 сдвига записывается единица (t ) , При этом единица, записанная в предыдущем цикле ( о;, 1) , сдвигается на разряд влево (в сторону старщих разрядов),а код второй разности а записьшается в регистр 7. Если разность а отрицател7,на, то в младший разряд регистра 13 сдвига записывается нуль ( 0), а в регистре 7 остается npe)SHee значение разности, т.е.

разность а. В остальных т-2 циклах устройство функционирует аналогично. .После проведения m циклов в регистре 13 сдвига фиксируется т-разрядный двоичный код, цифры ос, которого являются значащими цифрами значения частоты исследуемого сигнала.

Рассмотрим третий этап работы устройства. В данном устройстве символическая запятая, отделяющая целую и дробную части результата измеряемой частоты, привязана к т-у разряду регистра 13 сдвига. Это обеспечивается сдвигом содержимого регистра 13 сдвига на п разрядов влево. После этого дробная часть результата измерения всегда будет расположена в ш младших разрядах, а целая часть в п старших разрядах регистра 13 сдвига. Если - максимальное значение измеряемой частоты, то для размещения ее целой части необходимо иметь двоичных разрядов. Величина п д рпределяется с помощью соотношения

Птях

Таким образом, регистр 13 сдвига должен иметь m + п „д двоичных разрядов. Сдвиг кода измеренного значения частоты производится следующим образом. При подаче импульсов сдвига на регистр 13 сдвига его содержимое последовательно сдвигается влево. Одновременно последовательно на единицу уменьшается значение кода п, зафиксированного в реверсивном счетчике 2 импульсов. На третьем этапе этот счечик работает на вычитание импульсов. Сдвиг содержимого регистра 13 сдвига производится до тех пор, пока текуще содержимое реверсивного счетчика 21 импульсов не станет равным нулю.

Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1983 |

|

SU1187100A2 |

| Цифровой фазометр | 1982 |

|

SU1045155A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Цифровой фазометр | 1986 |

|

SU1287037A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| МНОГОКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU384115A1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

ЦИФРОВОЙ ФАЗОМЕТР по авт. св. № 1045155, отличающийс я тем, что, с целью расширения, функциональных возможностей путем обеспечения и измерения частоты ., входного сигнала, в него введены шифратор кода секунды и синхронизатор, причем вход управления шифратора кода секунды соединен с первым входом синхронизатора и с шестьм выходом блока управления, выхода шифратора кода секунды соединены с входами блока объединения, который снабжен третьей группой входовj второй и третий входы синхронизатора соединены соответственно с пятым и седьмым выходами блока управления, четвертый вход синхронизатора соединен с выходом знакового разряда сумматора, первый выход синхронизатора соединен с четвертым входом блока управления, второй и третий выходы синхронизатора соединены соответственно с входами первого и второго ре(Л гистров сдвига, четвертый выход синхронизатора соединен с входом второго регистра сдвига.

| Цифровой фазометр | 1982 |

|

SU1045155A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-10-30—Публикация

1983-11-14—Подача