11283790

Изобретение относится к специалй зированным средствам вычислительной техники, предназначено для определения коэффициентов дискретного преобразования Фурье при работе в реальном масштабе времени.

Цель изобретения - упрощение устройства.

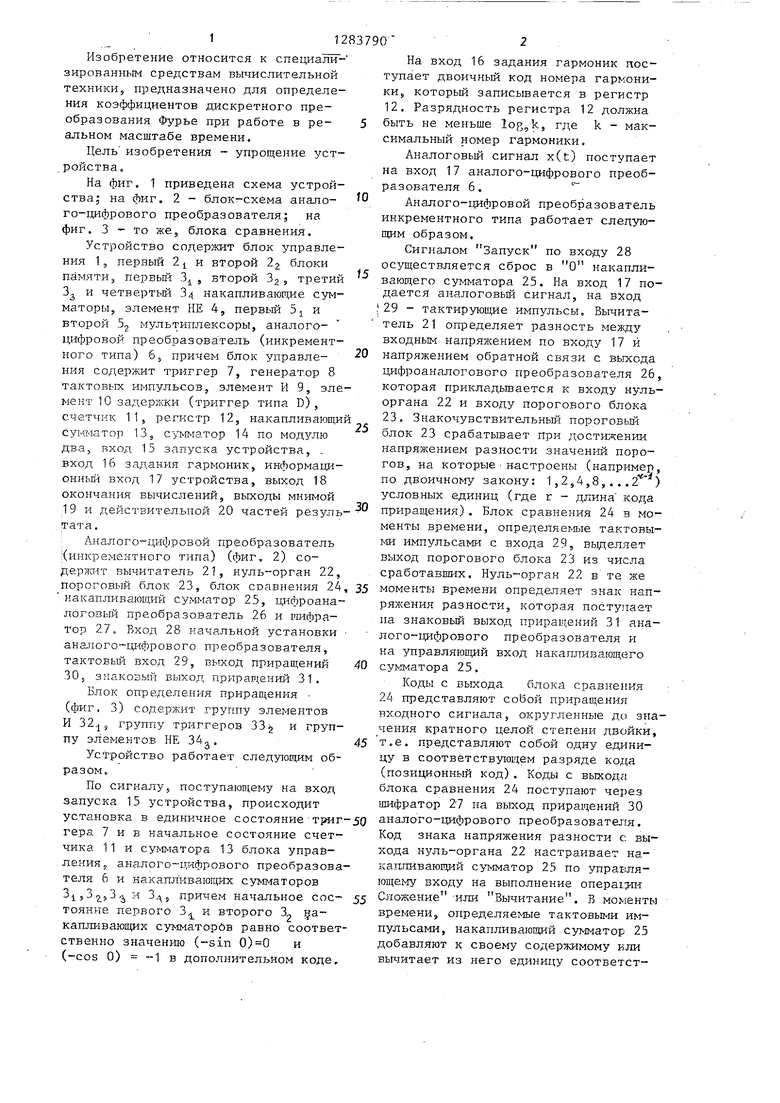

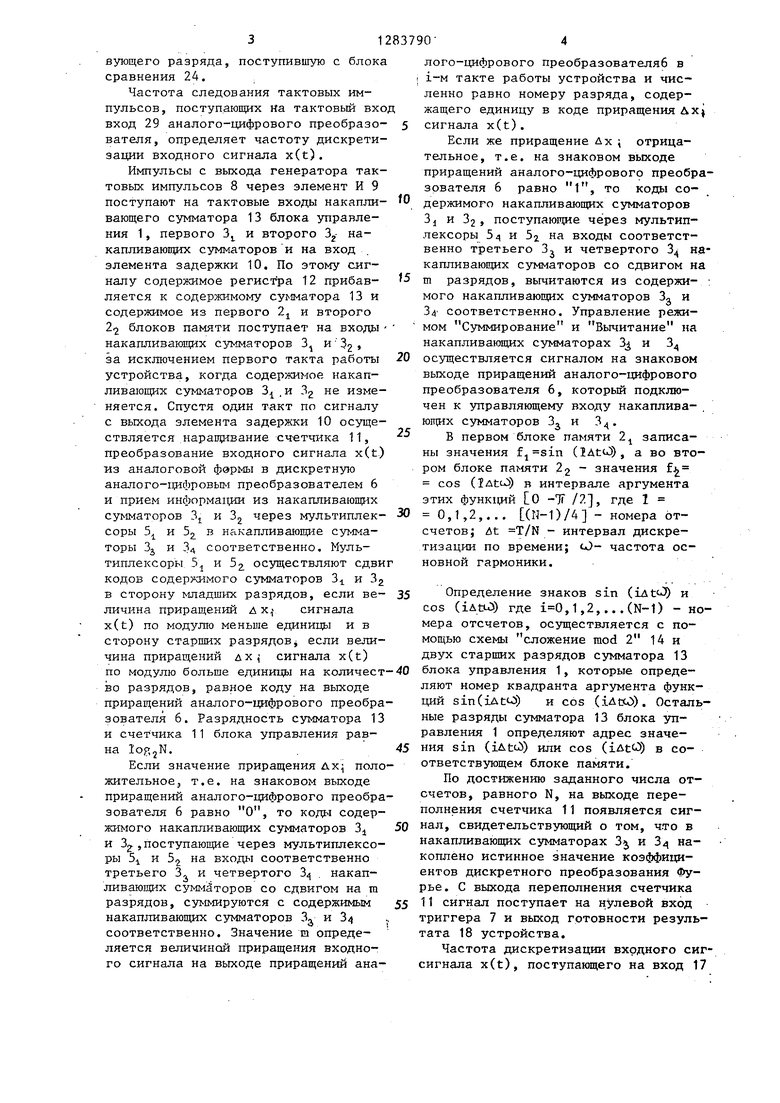

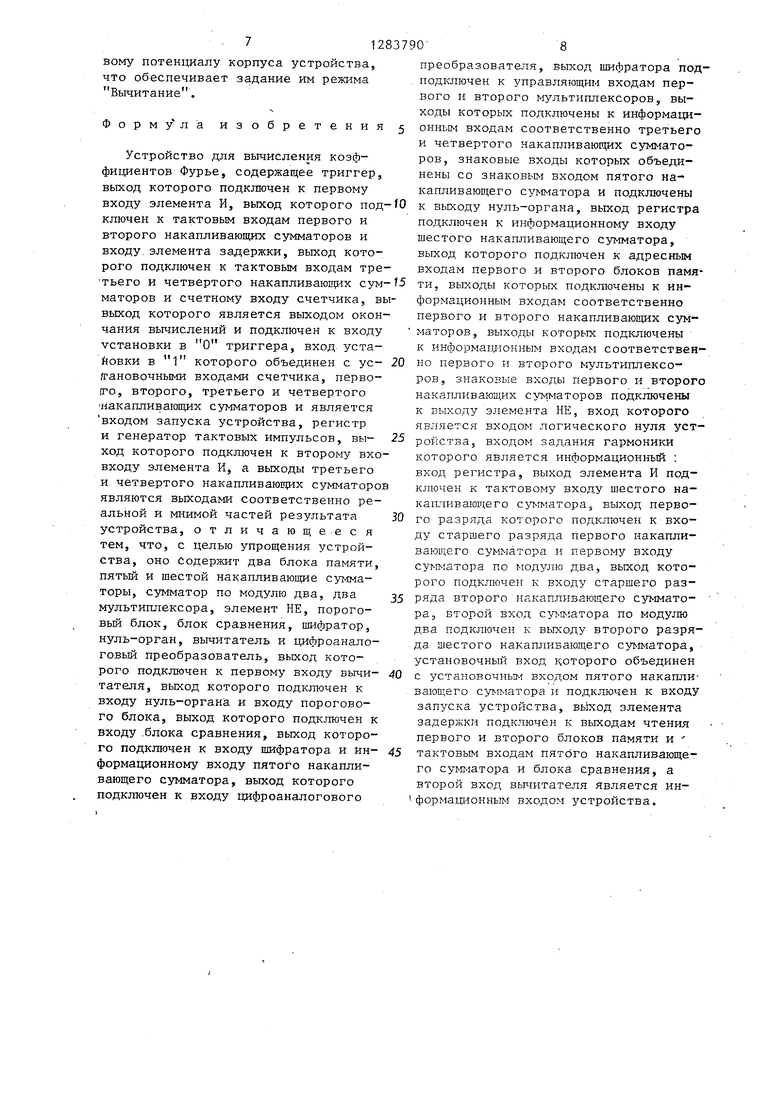

На фиг. 1 приведена схема устройства; на фиг, 2 - блок-схема аналого-цифрового преобразователя; на фиг, 3 - то же, блока сравнения.

Устройство содержит блок управления 1, первый 2j и второй 2 блоки

fO

памяти, первьш 3, , второй 32 э третий 3 и четвертьй 34 накапливаюпще сумматоры, элемент НЕ 4, первый 5 и второй Sg мультиплексоры, аналого- цифровой преобразователь (инкремент- ного типа) 6, причем блок управления содержит триггер 7, генератор 8 тактовых импульсов, элемент И 9, элемент 10 задержки (триггер типа D), счетчик 11, регистр 12, накапливающий сумматор 13, 14 по модулю два, вход 15 запуска устройства, . вход 16 задания гармоник, информационный вход 17 устройства, выход 18 окончания вычислений, выходы мнимой 19 и действительной тата.

Аналого-цифровой преобразователь Кинкрементного типа) (фиг, 2) со- дерлшт вычитатель 21, нуль-орган 22,

5

На вход 16 задания гармоник поступает двоичный код номера гармоники, который записывается в регистр 12. Разрядность регистра 12 должна быть не меньше log,k, где k - максимальный номер гармоники.

Аналоговый сигнал x(t) поступает на вход 17 аналого-цифрового преобразователя 6.

АНгшого-цифровой преобразователь инкрементного типа работает следующим образом.

Сигналом Запуск по входу 28 осуществляется сброс в О накапливающего сумматора 25. На вход 17 подается аналоговый сигнал, на вход 29 - тактирующие импульсы, Вычитатель 21 определяет разность между входным напряжением по входу 17 и напряжением обратной связи с выхода цифроаналогового преобразователя 26, которая прикладьшается к входу нуль- органа 22 и входу порогового блока 23, Знакочувствительный пороговый блок 23 срабатывает при достижении напряжением разности значений порогов, на которые настроены (например, по двоичному закону: 1,2,4,8,.. . ) условных единиц (где г - длина кода

и 20 частей резуль- приращения). Блок сравнения 24 в Моменты времени, определиei-ibie тактовы- ьш импульсами с входа 29, вьщеляет выход порогового блока 23 из числа сработавших. Нуль-орган 22 в те же

20

25

пороговый блок 23, блок сравнения 24, 35 моменты времени определяет знак нап- накапливающий сумматор 25, цифроана- рялсения разности, которая поступает

логовый преобразователь 26 и мифра- ца знаковый выход приращений 31 анатор 27, Вход 28 начальной установки

анапого-цифрового преобразователя,

40

тактовый вход 29, вьгход приращений 30J знакозь й выход прирар1ений 31.

Блок определения прирап;ения . (фиг. 3) содержит группу элементов И 32.,, группу триггеров ЗЗз и группу элементов НЕ 34.

Устройство работает следующим образом „

По сигналу, поступаюп ему на вход запуска 15 устройства, происходит

45

лого-цифрового преобразователя и на управляющий вход накапливающего сумматора 25.

Коды с выхода блока сравнения 24 представляют соВой приращения входного сигнала, округленные до значения кратного целой степени двойки, т.е. представляют собой одну единицу в соответствующем разряде кода (позиционный код). Коды с выхода блока сравнения 24 поступают через шифратор 27 па выход приращений 30

установка в единичное состояние триг-50 аналого-цифрового преобразовател-ш.

Код знака напряжения разности с выхода нуль-органа 22 настраивает накапливающий cyiviMaTop 25 по упраыля- входу на выполнение onepaijtn

гера 7 и в начальное состояние счетчика 11 и сумматора 13 блока упраб- ления,, аналого-цифрового преобразователя 6 и накапл ивалощих сумматоров 3j, , н 3., причем начальное сое- 55 Сложение -или Вычитание. В моменты тояние первого 3, и второго Ъ ga времени, определяемые тактовыми им- капливающих сумматоров равно соответ- пульсами, накапливагощий сумматор 25 ственно значению (sin 0)0 и добавляют к своему содержимому или (-COS 0) -1 в дополнительном коде, вычитает из него единицу соответст

лого-цифрового преобразователя и на управляющий вход накапливающего сумматора 25.

Коды с выхода блока сравнения ; 24 представляют соВой приращения входного сигнала, округленные до значения кратного целой степени двойки, т.е. представляют собой одну единицу в соответствующем разряде кода (позиционный код). Коды с выхода блока сравнения 24 поступают через шифратор 27 па выход приращений 30

Код знака напряжения разности с выхода нуль-органа 22 настраивает накапливающий cyiviMaTop 25 по упраыля- входу на выполнение onepaijtn

Сложение -или Вычитание. В моменты времени, определяемые тактовыми им- пульсами, накапливагощий сумматор 25 добавляют к своему содержимому или вычитает из него единицу соответствующего разряда, поступившую с блока сравнения 24.

Частота следования тактовых импульсов, поступающих На тактовый вход вход 29 аналого-цифрового преобразователя, определяет частоту дискретизации входного сигнала x(t).

Импульсы с выхода генератора тактовых импульсов 8 через элемент И 9 поступают на тактовые входы накапливающего сумматора 13 блока управления 1, первого 3 и второго накапливающих сумматоров и на вход элемента задержки 10, По этому сигналу содержимое регистра 12 прибавляется к содержимому сумматора 13 и содержимое из первого 2j и второго 2 блоков памяти поступает на входы накапливающих сумматоров 3 и 32 за исключением первого такта работы устройства, когда содержимое накапливающих сумматоров 3.и 32 не изменяется. Спустя один такт по сигналу с выхода элемента задержки 10 осуществляется наращивание счетчика 11, преобразование входного сигнала x(t) из аналоговой фермы в дискретную аналого-цифровьм преобразователем 6 и прием информации из накапливающих сумматоров 3j и 3 через мультиплексоры 5 к 5 в накапливающие сумматоры 3j и ЗА соответственно. Мультиплексоры 5.J и 52 осуществляют сдвиг кодов содер чимого сумматоров 3 и З в сторону младших разрядов, если величина приращений д Х{ сигнала x(t) по модулю меньше единицы и в сторону старпмх разрядовj если величина приращений дх, сигнала x(t)

to

лого-цифрового преобразователяб в i-M такте работы устройства и численно равно номеру разряда, содержащего единицу в коде приращения Axj сигнала x(t).

Если же приращение Дх отрицательное, т.е. на знаковом выходе приращений аналого-цифрового преобра- 6 равно 1,

зователя

то коды

20

держимого накапливающих сумматоров 3j и Зз, поступающие через мультиплексоры и 5 на входы соответственно третьего 3j и четвертого 3ц накапливающих сумматоров со сдвигом на m разрядов, вычитаются из содержи- ; мого накапливающих сумматоров 3j и соответственно. Управление режимом Суммирование и Вычитание на накапливающих сумматорах 3 и 3 осуществляется сигналом на знаковом выходе приращений аналого-цифрового преобразователя 6, который подключен к управляющему входу накаплива- .

25

сумматоров 3 и

3,,

30

в первом блоке памяти 2 записаны значения з1п (lAtO), а во втором блоке памяти 22 значения f cos (lutO) в интервале аргумента этих функций о -TfT /2, где 1 0,1,2,... (N-1)74 - номера отсчетов; At T/N - интервал дискретизации по времени; О- частота основной гармоники.

35 Определение знаков sin ( и cos (iAtO) где ,1,2,...(N-1) - номера отсчетов, осуществляется с помощью схемы сложение mod 2 14 и двух старщих разрядов сумматора 13 по модулю больше единицы на количест-40 блока управления 1, которые опреде- во разрядов, равное коду на выходе ляют номер квадранта аргумента функ- приращений аналого-цифрового преобразователя 6. Разрядность сумматора 13 и счетчика 11 блока управления равна log,N.45 ния sin (iAtci) или cos () в соЕсли значение приращения поло- ответствующем блоке памяти, жительноеэ т.е. на знаковом выходе По достижению заданного числа от- приращений аналого-цифрового преобра- счетов, равного N, на выходе пере- 6 равно О.

50

накапливающих сумматорах 3j и 3 накоплено истинное значение коэффициентов дискретного преобразования Фузователя b равно U, то коды содержимого накапливающих сумматоров 3 и 32, поступающие через мультиплексоры 5 и 5 на входы соответственно

ций sin(iAtO) и cos (iAtO). Остальные разряды сумматора 13 блока управления 1 определяют адрес значе-

полнения счетчика 11 появляется сигнал, свидетельствующий о том, что в

третьего 3 и четвертого 3ц . накапливающих сумматоров со сдвигом на m разрядов, сз мируются с содержимым накапливающих сзтФ1аторов 3 и 3 , соответственно. Значение m определяется величиной приращения входного сигнала на выходе приращении анарье. С выхода переполнения счетчика 55 11 сигнал поступает на нулевой вход триггера 7 и выход готовности результата 18 устройства.

Частота дискретизации входного сиг- сигнала x(t), поступающего на вход 17

o

лого-цифрового преобразователяб в i-M такте работы устройства и численно равно номеру разряда, содержащего единицу в коде приращения Axj сигнала x(t).

Если же приращение Дх отрицательное, т.е. на знаковом выходе приращений аналого-цифрового преобра- 6 равно 1,

зователя

то коды со5

0

держимого накапливающих сумматоров 3j и Зз, поступающие через мультиплексоры и 5 на входы соответственно третьего 3j и четвертого 3ц накапливающих сумматоров со сдвигом на m разрядов, вычитаются из содержи- ; мого накапливающих сумматоров 3j и соответственно. Управление режимом Суммирование и Вычитание на накапливающих сумматорах 3 и 3 осуществляется сигналом на знаковом выходе приращений аналого-цифрового преобразователя 6, который подключен к управляющему входу накаплива- .

сумматоров 3 и

3,,

в первом блоке памяти 2 записаны значения з1п (lAtO), а во втором блоке памяти 22 значения f cos (lutO) в интервале аргумента этих функций о -TfT /2, где 1 0,1,2,... (N-1)74 - номера отсчетов; At T/N - интервал дискретизации по времени; О- частота основной гармоники.

Определение знаков sin ( и cos (iAtO) где ,1,2,...(N-1) - номера отсчетов, осуществляется с помощью схемы сложение mod 2 14 и двух старщих разрядов сумматора 13 блока управления 1, которые опреде- ляют номер квадранта аргумента функ- ния sin (iAtci) или cos () в соций sin(iAtO) и cos (iAtO). Остальные разряды сумматора 13 блока управления 1 определяют адрес значе-

ответствующем блоке памяти, По достижению заданного числа от- счетов, равного N, на выходе пере-

полнения счетчика 11 появляется сигнал, свидетельствующий о том, что в

рье. С выхода переполнения счетчика 11 сигнал поступает на нулевой вход триггера 7 и выход готовности результата 18 устройства.

Частота дискретизации входного сиг- сигнала x(t), поступающего на вход 17

5 1283790 6

устройства, р,авна частоте генератора . С соз()д fecol, тактовых импульсов 8.

Алгоритм работы устройства сво причем Йится к следующему. i

Прирас ения Д х.; входного сигнала5 J ,/cos(,m,jAtO;

в каждом такте работы устройства оп- (ш jAtO) ределяются соотношением

cos (га j д t )

- x) x(t) , и C 0

где x;,., xj - отсчеты входного сиг-Проведя аналогичные преобразованала x(t) в ()-M иия и для В (О), получим /

и i-M тактах работы,

устройства; .В(сО)Дх„.5о +Дх,.8, +,...,+

2 единица в т-м разряде15 -

кода приращения А xj 5 +Лх . 8„.5 причем ,r. .

Коэффициенты ДПФ равныгде о YH (m-ut-O)

А (kO) x.cos (iAtOk).,20 s, sin ( u)),

. m,.:.j,

В (ko) x.-sin (iattOk),

, .

где k номер гармоники.

Представив значение A(ko) и B(k(3) S,,,, ; sin (N-1)A ьиз, для в виде:

причем A(0)X(,-cos (Oat-0) + ,, ,+х j-cos())+ n-i

I Sj ) sin (ш; dtO)-sin(m.,At tO)- + ,..+x,,cos(N--1)A tcO . 301 4.H

B(eO)Xo-sin (Oafb:)) + ..,H-xj sin(iutu) - sin (rajAfO).

.,.+X| sin(N-1) Л tto,и S 0

35

и учитываяj чтоВ устройстве вычисления S,. и С ,

N-1 выполняются на накапKj Ахв ,-гз . .. ,+AXJ - AXg ,ливающих сумматорах 3 и Зз соответS-0ственно,

получаем 40 Вычисление &Xj С j идх Sj выполняется согласно выражениям A(i-0)AXc,icos(0 A tO) + ,.. .,-f

. , Сз (t)-xj,.2. (N-1)A t. - ,

. , Xi Sj (t)-Xi il-2-..S;,

4-ДХ.(1 A tU))+,,.+

-bcos (N-1) Д ,.,.,+причем значением sign f x(t)-Xj.t ocyществляется задание операции Сложе- +Лх Icos (N-1)u tO 50 и е или Вычитание на накапливак - - щих сумматорах Зд и 3., , а операция

AY .г -«-AY г + +Av S: и С; осу1чествляется на

-ДХо 1- о t-, . , „ ji-AXfj-j - |ц, , 1 .-

мультиплексорах 5, и З соответствен- где С„ f сов (), путем сдвига Sj и С на m разряmj|o55 ° ° сторону младших разрядов для

С. ) cos (m At-cO),|лх}1 1.

тТоУправляющие входы первого 3; и

второго накапливаюпщх сумматоров через элемент НЕ 4 подключены к нулевому потенциалу корпуса устройства что обеспечивает задание им режима Вычитание.

Форм у л а изобретения 5

преобразователя, выход шифратора под подключен к управляющим входам первого и второго мультиплексоров, выходы которых подключены к информационным входам соответственно третьего и четвертого накапливающих сумматоров, знаковые входы которых объединены со знаковым входом пятого на- капливаю0 ;его сумматора и подключены

Устройство для вычисления коэффициентов Фурье, содержащее триггер, выход которого подключен к первому входу элемента И, выход которого под-fO к выходу нуль-органа, выход регистра ключен к тактовым входам первого и подключен к информационному входу второго накапливающих сз мматоров и шестого накапливающего сумматора, входу, элемента задержки, выход кото- выход которого подключен к адресным рого подключен к тактовым входам тре- входам первого и второго блоков памЯ тьего и четвертого накапливаюших cyM-t5 ти, выходы которых подключены к ин- маторов и счетному входу счетчика, вы- формационнгям входам соответственно выход которого является выходом окончания вычислений и подключен к входу

первого и второго накапливающих сумматоров, выходы которых подключены к информащюнным входам соответственустановки в О триггера, вход устайовки в 1 которого объединен с ус- 20 но первого и второго мультиплексо

/гановочными входами счетчика, первого, второго, третьего и четвертого накапливаюшд х сумматоров и является входом запуска устройства, регистр и генератор тактовых импульсов, выход которого подключен к второму вхо входу элемента И, а выходы третьего и четвертого накапливающих сумматоро являются выходами соответственно реальной и мнимой частей результата устройства, отличающееся тем, что, с целью упрощения устройства, оно Содержит два блока памяти пятый и шестой накапливающие сумматоры, сумматор по модулю два, два мультиплексора, элемент НЕ, порого- вьш блок, блок сравнения, шифратор, нуль-орган, вычитатель и цифроанало- говый преобразователь, выход которого подключен к первому входу вычи- тателя, выход которого подключен к входу нуль-органа и входу порогового блока, выход которого подключен к входу .блока сравнения, выход которого подключен к входу шифратора и ин- формационному входу пятого накапливающего сумматора, выход которого подключен к входу цифроаналогового

я 5

283790 8

преобразователя, выход шифратора под- подключен к управляющим входам первого и второго мультиплексоров, выходы которых подключены к информационным входам соответственно третьего и четвертого накапливающих сумматоров, знаковые входы которых объединены со знаковым входом пятого на- капливаю0 ;его сумматора и подключены

, д-fO к выходу нуль-органа, выход регистра подключен к информационному входу шестого накапливающего сумматора, - выход которого подключен к адресным е- входам первого и второго блоков памЯ M-t5 ти, выходы которых подключены к ин- вы- формационнгям входам соответственно ну

к выходу нуль-органа, выход регистра подключен к информационному входу шестого накапливающего сумматора, выход которого подключен к адресным входам первого и второго блоков памЯ ти, выходы которых подключены к ин- формационнгям входам соответственно

первого и второго накапливающих сумматоров, выходы которых подключены к информащюнным входам соответствен0

5

ров, знаковые входы первого и второго накапливающих сумматоров подключены к выходу элемента НЕ, вход которого является входом логического нуля уст- ройства, входом задания гармоники которого является информацион1-1ЫЙ : вход регистра, выход элемента И подключен к тактовому входу шестого накапливающего ciT-iMaTopaj выход первого разряда которого подключен к входу старшего разряда первого накапливающего сумматора и первом - входу сумматора по модулю два, выход которого подключен к входу старшего разряда второго накапливающего сумматора, второй вход сумматора по модулю два подключен к выходу второго разряда шестого накапливающего сумматора, установочный вход к;оторого объединен с установочным входом пятого накапливающего сумматора и подключен к входу запуска устройства, выход элемента задержки подключен к выходам чтения первого и второго блоков памяти и тактовым входам пятого накапливающего сумг-штора и блока сравнения, а второй вход вычитателя является ин- формащ-юнным входом устройства.

5

0

23

2

-Л

.72

фиеЗ

Составитель А. Баранов Редактор В. Ковтун Техред И,Попович Корректор М. Максимипшнец

Заказ 7444/49 Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

37

Я 29

Р5

25

Н

LZr

77

fff

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1290351A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1273944A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Функциональный преобразователь угла поворота вала в код | 1982 |

|

SU1080174A1 |

| Многоканальный цифровой коррелятор | 1983 |

|

SU1211753A1 |

| Устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1332330A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД ДЛЯ УСТРОЙСТВ ЭЛЕКТРОМЕХАНОТРОНИКИ | 1994 |

|

RU2094945C1 |

| Преобразователь перемещения в код | 1988 |

|

SU1531221A1 |

| Аналого-цифровое устройство для вычисления полиномиальной функции | 1985 |

|

SU1262530A1 |

Изобретение относится к специализированным средствам вычислительной техники, предназначено для определения дискретного преобразования Фурье при работе в реальном масштабе времени. Цель изобретения - упрощение устройства. Поставленная цель достигается за счет того, что устройство содержит блок 1 управления, накапливакицие сумматоры ,, два блока памяти, два мультиплексора аналого-цифровой преобразователь 6, элемент НЕ, сумматор по модулю два 14, регистр 12, триггер 7, элемент 9 И, элемент 10 задержки, счетчик 11. 3 ил. с S (Л tc 00 со ч о о .1 13

| Устройство для вычисления коэффициентов фурье | 1975 |

|

SU537349A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Смирнов Ю.М | |||

| и др | |||

| Проектирова- ниег спехщализированных информационно-вычислительных систем | |||

| М.: Высшая школа, 1984, с | |||

| Приспособление в пере для письма с целью увеличения на нем запаса чернил и уменьшения скорости их высыхания | 1917 |

|

SU96A1 |

Авторы

Даты

1987-01-15—Публикация

1985-07-19—Подача