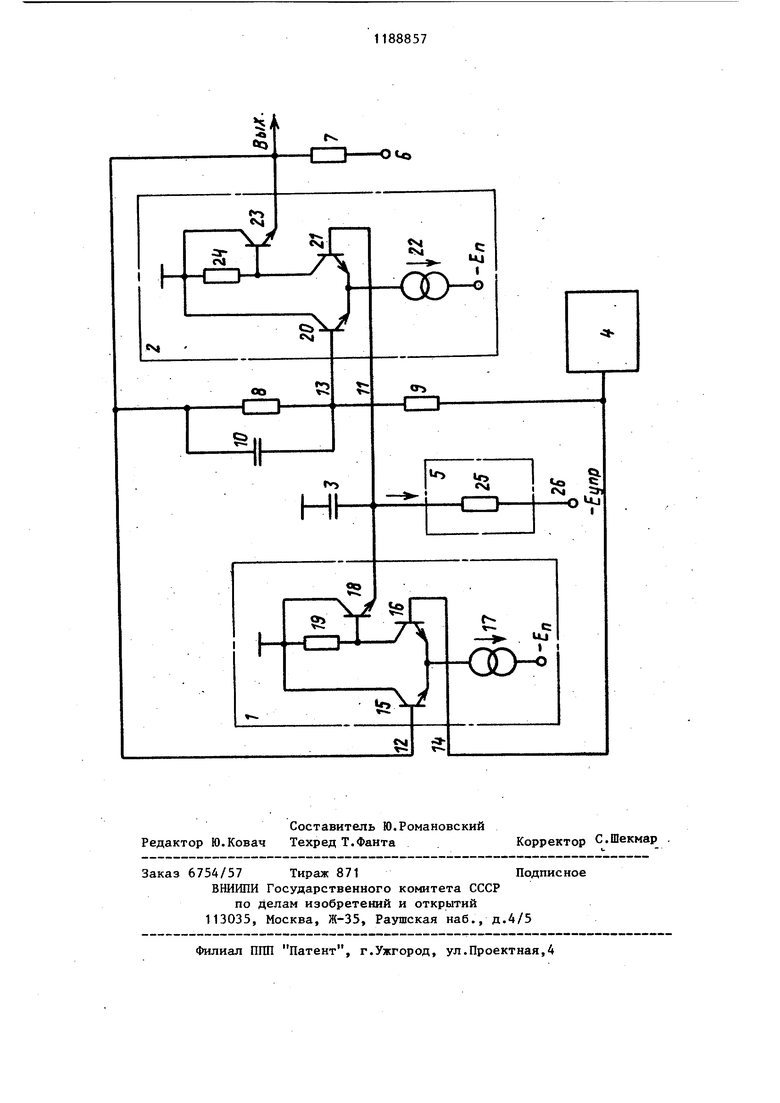

i изобретение относится к импульсной технике и может быть использова но в качестве управляемого напряжением генератора в высокочастотных цифровых системах фазовой автоподстройки частоты, а также генератора синхроимпульсов в устройствах вычис литедьной техники и автоматики. Цель изобретения - расширение диапазона регулирования выходной частоты генератора. На чертеже изобралсена электричес кая схема управляемого генератора импульсов. Схема содержит первый дифференци альный приемник 1 эмиттерно связанной логики, второй дифференциальньп приемник 2 эмиттерно связанной логи ки, времязадающий конденсатор 3, источник 4 опорного напряжения, управляющий генератор 5 тока, источник 6 напряжения, резистор 7 наг рузки, первый резистор 8 резистивного делителя, второй резистор 9 ре зистивного делителя, конденсатор 10 инвертирующий вход 11 дифференциаль ного приемника 2, неинвертйрующий вход 12 дифференциального приемника 1, неинвертирующий вход 13 дифферен циального приемника 2 и инвертирующий вход 14 дифференциального прием ника 1. Выход дифференциального приемника 1 соединен с выходом управляемог генератора 5 тока, инвертирующим вх дом 11 дифференциального приемника и времязадающим конденсатором 3, вт рая обкладка которого соединена с общей шиной. Выход дифференциального приемника 2 соединен с инвертирующим входо 12 дифференциального приемника 1, через резистор 8 - с неинвертирующим входом 13 дифференциального при емника 2 и через нагрузочный резистор 1-е шиной отрицательного источника 6 питания. Выход дифференциального приемника 2 является выходом генератора. Конденсатор 10 подсоединен между выходом дифференциального приемника 2 и его неинвертирующим входом 13. Выход источника 4 опорного напря жения соединен с инвертирующим в ходом 14 дифференциального приемника и через резистор 9 - с неинвертирующим входом 13 дифференциального прИ емника 2. 572 Дифференциальный приемник 1 является стандартным интегральным -дифференциальным приемником эмиттерно связанной логики и содержит переключатель тока, вьшолненный на транзисторах 15 и 16, эмиттеры которых соединены между собой и через генератор 17 тока подключены к шине источника отрицательного напряжения питания. База транзистора 15 соединена с неинвертирующим входом 12 дифференциального приемника 1, а коллектор с общей шиной. База транзистора 16 соединена с инвертирующим входом 14 дифференциального приемника 1, а коллектор подсоединен к базе эмиттерного повторителя,. выполненного на транзисторе 18 и через резистор 19 к общей шине. Коллектор эмиттерного повторителя 18 соединен с общей шиной, а эмиттер - с выходом дифференциального приемника 1. Дифференциальный приемник 2 аналогично дифференциальному приемнику 1 содержит переключатель тока, выполненный на транзисторах 20 и 21, эмиттеры которых соединены между собой и через генератор 22 тока подключены к шине источника 6 отрицательного напряжения питания. База транзистора 20 соединена с неинвертирующим входом 13, а коллектор - с общей шиной. База транзистора 21 соединена с инвертирующм входом 11 дифференциального приемника 2, а коллектор подсоединен к базе эмиттерного повторителя, вьтолненного на транзисторе 23, и через резистор 24 к общей шине. Коллектор эмиттерного повторителя 23 соединен с общей шиной, а эмиттер - с выходом дифференциального приемника 2. На чертеже показан один из возможных вариантов схематического выполнения генератора 5 тока в виде резистора 25, подключенного между выходом генератора тока и входом 26 управляющего напряжения. Дифференциальные приемники 1 и 2 формируют на своем выходе напряжение высокого логического уровня (Ug) или низкого логического уровня (U) в зависимости от напряжения на его входах. Например, если напряжение на неинвертирующем входе 12 дифференциального приемника 1 вьщ1е, чем на инвертирующем входе 14, то ток генератора 17 тока переключается в тран-.

зистор 15. На выходе дифференциального приемника будет высокий логический уровень напряжения, равный сумме падения напряжения на резисторе 19 за счет базового тока транзистора 18 и напряжения эмиттер-база транзистора 18. Если же на неинвертирующем входе 12 напряжение ниже, чем на инвертирующем входе 14, то ток генератора 17 тока переключится в транзистор 16. На выходе дифференциального приемника 1 будет напряжение низкого логического уровня, равное сумме падения напряжения на резисторе 19 за счет тока генератора 17 и напряжения эмиттер-база транзистора 18.

Дифференциальный приемник 2 работает аналогично дифференциальному приемнику 1.

Источник 4 опорного напряжения вырабатывает на выходе напряжение (и. ), равное средней величине логического перепада выходных сигналов дифференциальных приемников.

Напряжения логических уровней Ug и иц и опорное напряжение UQ устанавливаются такой величины, чтобы переключатели токов дифференциальных приемников находились в ненасыщенном режиме, что обеспечивает максимальное быстродействие. Так, для серии К 500 стандартных интегральных схем эмиттерно связанной логики эти напряжения равны Ug --0, 8 В -1, 8 в; Uon -1, 3 В.

Управляемьй генератор импульсов работает следующим образом.

Времязадающий конденсатор 3 заряжается через малое выходное сопротиление эмиттерного повторителя дифференциального приёмника 1 и разряжается током управляемого генератора 5 тока до уровней напряжений порого переключения дифференциального приемника 2 на входе 13.

Если на выходе дифференциального приемника 2 установился высокий логический уровень напряжения, то на неинвертирующем входе 13 установится напряжение, которое заведомо ниже высокого логического уровня Ug , но выше напряжения UOR и равно

Ы iв -JJeLl. + и

(1)

R + R

on 5

где R и R величины сопротивлений резисторов 8 и 9 соответственно.

Поскольку напряжение на входе 12 дифференциального приемника 1 выше, чем на входе 14, на выходе дифференциального приемника произойдет формирование высокого логического уровня и конденсатор 3 будет форсированно заряжаться через малое выходное сопротивление транзистора 18. Как тодько напряжение на конденсаторе 3

0 и, следовательно, на входе 11 дифференциального приемника 2 достигнет уровня напряжения на входе 13, произойдет переключение дифференциального приемника 2. На его выходе

5 и на входе дифференциального приемника 1 установится напряжение низкого логического уровня U. Напряжение на входе 13 диффференциального приемника 2 понизится и станет ниже

0 напряжения и, , но вьше напряжения U(j и равным

) + и (2)

Rg + R, «- 2)

Поскольку напряжение на входе 12 дифференциального приемника 1 стало ниже, чем на входе 14, ток генератора 17 тока переключится в транзистор 16 и эмиттерный повторитель 18 закроется, так как на его базе напряжение будет ниже, чем на эмиттере. Конденсатор 3 начнет линейно разряжаться током генератора 5 тока. Скорость разряда конденсатора 3 определяется током генератора 5 тока и может управляться напряжением Е|,„р, подаваемым на вход 26. Когда напряжение на конденсаторе 3 станет ниже

напряжения на входе 13 дифференциального приемника 2, ток генератора 22 тока переключится в транзистор 20 и на выходе дифференциального приемника 2 установится высокий логический уровень напряжения Up.

Процесс заряда-разряда времязадакнцего конденсатора 3 будет периодически повторяться и на выходе генератора будут вырабатываться положительные импульсы напряжения. Длительность импульсов будет равна сумме времени распространения сигнала в дифференциальных приемниках 1 и 2 и времени форсированного заряда конденсатора 3.

Время паузы между импульсами равно сумме времени распространения сигнала в дифференциальных приемниках

1и 2 и времени разряда конденсатора 3 током генератора 5 тока.

Изменяя ток генератора 5 тока с помощью изменения напряжения Ец. , можно изменить длительность паузы выходных импульсов и тем самым управлять частотой повторения выходных импульсов.

Выходные логические уровни Ug и и дифференциальных приемников 1 и

2зависят от вьрсодного тока нагрузки и определяются следующими известными упрощенными вьфа}кениями:

где и - напряжение высокого уровня на базе транзисторов 18 и 23 за счет базовых токов;

- напряжение низкого уровня на базе транзисторов 18 и 23 за счет тока генераторов 17 и 22 тока, соответственно;

ив itH выходные токи нагрузки соответственно при высоком и низком логическом уровне на выходе;

а и Гд - параметры нелинейной модели и зквивалентное сопротивление змиттерной цепи транзисторов 18 и 23; т - температурный потенциал. Выход дифференциального приемника 2 работает на постоянную токовую нагрузку, определяемую величиной нагрузочного резистора 7, а выход дифференциального приемника 1 работает на переменную токовую нагрузку генератора. 5 тока, которая в процессе регулирования частоты может изменяться в широких пределах.

Как видно из выражений.(3) и (4), если даже пренебречь технологическими разбросами элементов схема приемников, выходные логические уровни дифференциальньк приемников 1 и 2 j могут значительно отличаться друг от друга. Величина сопротивления резисторов 8 и 9 выбирается таким образом, что напряжение. (1) верхнего порога переключения на входе 13 заведо10 МО ниже уровня напряжения высокого логического уровня на выходе дифференциального приемника 1, а напряжение (2) нижнего порога переключения заведомо вьше выходного уровня напряжения низкого логического уровня дифференциального приемника 1 во всем динамическом диапазоне регулирования генератора 5 тока и при всех возможных технологических разбросах элементов схемы дифференциальных приемников.

Конденсатор 10, включенный между выходом дифференциального приемника 2 и его неинвертирующим уходом 13, 5 форсирует переключение напряжения на входе 13, устраняя влияние паразитной емкости входа, и переключение дифференциального приемника 2 из одного логического состояния в 0 Другое. Величина емкости конденсатора 10 выбирается небольшой величины, чтобы постоянная времени перезаряда конденсатора через эквивалентное сопротивление делителя на резисторах 5 8 и 9 было меньше длительности выходных импульсов.

В предлагаемом управляемом генераторе импульсов верхняя граничная частота определяется временем перео ключения дифференциальных приемников. Для современных схем эмиттерно связанной логики это время лежит в области единиц и менее наносекунд. Поэтому верхняя граничная частота 5 данного генератора может достигать величины более сотни мегагерц, что позволяет использовать генератор в самых быстродействукяцих цифровых системах.

| название | год | авторы | номер документа |

|---|---|---|---|

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР НАПРЯЖЕНИЯ | 1991 |

|

RU2007823C1 |

| Коммутатор аналоговых сигналов | 1981 |

|

SU978345A1 |

| Формирователь пилообразного напряжения | 1980 |

|

SU919069A1 |

| Дифференциальный усилитель | 1982 |

|

SU1149380A1 |

| УНИВЕРСАЛЬНОЕ ЗАРЯДНОЕ УСТРОЙСТВО АГАТ-Ц-УЗУ И СПОСОБ ГРАДУИРОВКИ ИЗМЕРИТЕЛЯ НАПРЯЖЕНИЯ, ПОДКЛЮЧАЕМОГО ДЛЯ КОНТРОЛЯ НАПРЯЖЕНИЯ НА ВЫХОДЕ УНИВЕРСАЛЬНОГО ЗАРЯДНОГО УСТРОЙСТВА | 1992 |

|

RU2042247C1 |

| УСИЛИТЕЛЬ МОЩНОСТИ | 1990 |

|

RU1748611C |

| Входное устройство тракта вертикального отклонения осциллографа | 1982 |

|

SU1078340A1 |

| Измерительный преобразователь емкости датчика | 1990 |

|

SU1725160A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Стабилизатор постоянного напряжения | 1988 |

|

SU1539748A1 |

УПРАВЛЯЮНРЙ ГЕНЕРАТОР ИМПУЛЬСОВ, содержащий два дифференциальных приемника эмиттерно связанной логики, причем выход первого дифференциального приемника соединен с управляюпщм генератором тока, времязадающим конденсатором, вторая обкладка которого подключена к общей шине, и инвертирующим входом второго дифференциального приемника, выход которого через резистор нагрузки соединен с источником напряжения и инвертирукицим входом первого дифференциального приемника, инвертирующий вход которого соединен с источником опорного напряжения, о т л и чающийся тем, что, с целью расширения диапазона регулирования выходной частоты генератора, в него введены резистивный делитель и конденсатор, причем первый вывод резистивного делителя и первая, обкладка конденсатора соединены с выходом второго дифференциального приемника, второй вывод резистивного делителя (Л соединен с источником опорного напряжения, а средняя точка резистивного делителя и вторая обкладка конденсатора соединены с неинвертирующим входом второго дифференциального приемника. 00 00 00 ел

| Палм | |||

| Высокочастотный генератор на ЭСЛ-схеме | |||

| - Электроника, 1975, № 11, с.61-62 | |||

| Чулков В.А | |||

| Вьюокочастотный генератор пилообразного напряжения | |||

| Приборы и техника эксперимента, 1980, № 6, с.96-97. |

Авторы

Даты

1985-10-30—Публикация

1984-01-09—Подача