1

Изобретение относится к автоматике и вычислительной технике и может использоваться при построении высоконадежных устройств.

Цель изобретения - повьппение надежности и достоверности контроля устройства.

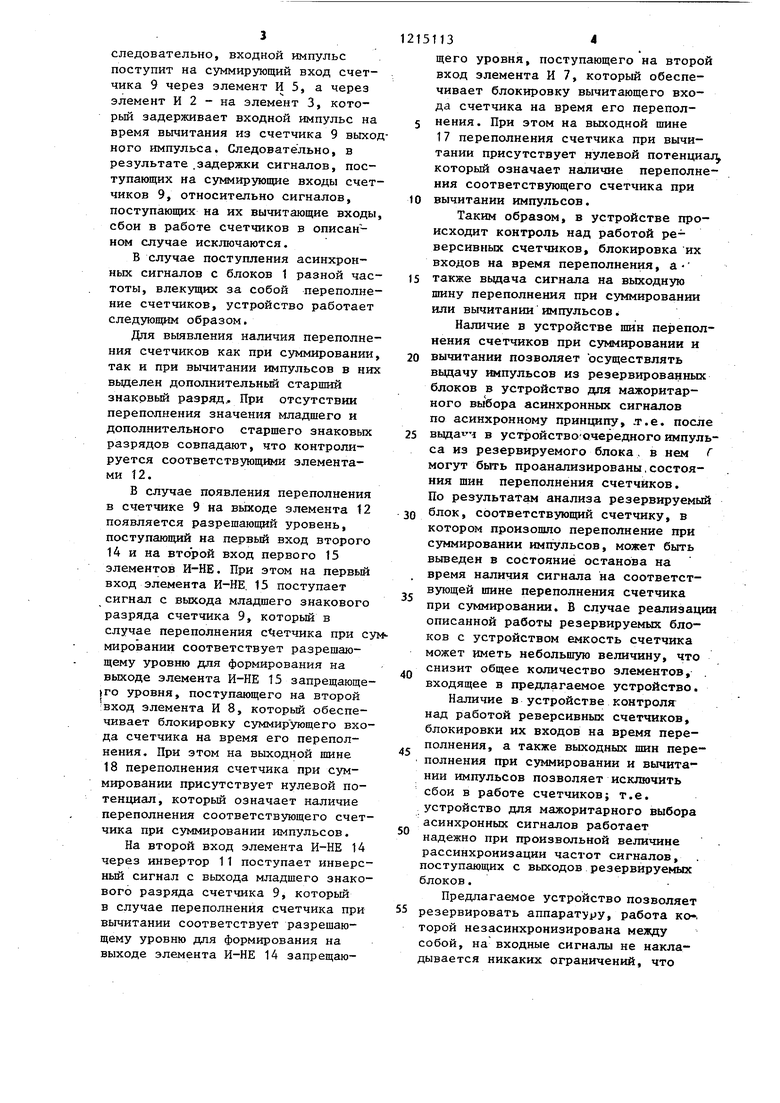

На чертеже приведена функциональная схема устройства для мажоритарного выбора асинхронных сигналов.

Устройство содержит резервируе- мне блоки 1, первые элементы И 2, элементы 3 задержки, первые инверторы 4, вторые элементы И 5, первы элементы ИЛИ 6s пятые элементы И 7 четвертые элементы И 8, реверсивные счетчики 9, вторые элементы ИЛИ 10, вторые инверторы 11,элементы 12 сравнения, третьи элементы И 13, вторые 14 и первые 15 элементы И-НЕ, мажоритарный элемент 1 выходные шины 17 переполнения счетчиков при вычитании, выходные шины 18 переполнения счетчиков при суммировании и выходную шину 19 устройства.

Устройство работает следующим образом.

Импульсы, поступающие с выходов блоков 1, являются асинхронными и могут поступать с различными частотами, в результате чего в устройстве может произойти переполнение реверсивных счетчиков. Рассмотрим вначале случаи поступления асихронных сигналов без переполнения счетчиков.

Принцип работы устройства в исправном состоянии заключается в том, что за определенное время на выход устройства прсЛсодит число импульсов, равное числу поступивших от блоков 1, а в зависимости от вариантов рассинхронизации каналов устройства - число импульсов, равное числу поступивших от блоков 1 двух из трех каналов устройства, или среднее из трех число импульсо

В исходном состоянии значения всех разрядов счетчиков 9 равны нулю.. При одновременном поступлении с блоков 1 импульсных сигналов они через соединенные последователно элементы И 5, элементы ИЛИ 6 и элементы И 8 поступают на сум- мирукйцие входы счетчиков 9 соответствующих каналов, и во всех счетчиках записьшается положитель10

15

20

25

2151132

нов число +1, на вьсходе элементов

И 13 появляются разрешающие уровни и формируется сигнал на выходе элемента 16. Этот сигнал поступает на выходную шину 19 устройства и через элементы И 7 на вычитающие входы всех счетчиков 9, устанавливая их в исходное состояние. При этом этом количество импульсов, прошедших на выход устройстваJ равно количеству импульсов, поступивших от блоков 1 .

Если сигналы с блоков 1, содержащие равные количества импульсов, меньшие или равные емкости счетчиков 9, поступают поочередно друг за другом, например последовательно, в первом, втором и третьем каналах, то устройство работает следующим образом, импульсы с блока 1 первого канала записываются в соответствующий счетчик 9, но на выход не проходят, так как разрешающий уровень присутствует только на выходе элемента И 13 первого канала. Затем импульсы, поступающие с блока 1 второго канала, в темпе поступления проходят на выход устройства, так как разрешающий уровень дополнительно появляется на выходе элемента И 13 второго канала. Поскольку эти импульсы вычитаются из содержимого всех счетчиков, то к концу работы блока 1 второго канала содержимым счетчиков 9 в первом и втором каналах будет ноль, а на счетчике 9 в третьем канале запишется отрицательное число, модуль которого равен количеству прошедших на выход устройства импульсов. Поэтому когда начнут поступать импульсы с блока 1 третьего канала, они на выход , не пройдут, так как во всех трех каналах элементы И 13 имеют на выходе запрещающий уровень, а к концу работы блока. 1 третьего канала на счетчике 9 также будет ноль.

Таким образом, на выход устройства проходит нужное количество импульсов и оно находится в исходном состоянии.

в случае поступления на вход устройства очередного входного импульса с какого-либо блока 1 в момент вычитания из счетчика 9 выходного импульса на втором входе элемента И 5 присутствует запрещающий уровень, а на втором входе элемента И 2 - разрешающий уровень.

30

35

40

45

50

55

следовательно, входной импульс поступит на суммирующий вход счет- чика 9 через элемент И 5, а через элемент И 2 - на элемент 3, кото- рьй задерживает входной импульс на время вычитания из счетчика 9 вьпсод ного импульса. Следовательно, в результате .задержки сигналов, поступающих на суммирующие входы счетчиков 9, относительно сигналов, поступающих на их вычитающие входы сбои в работе счетчиков в описанном случае исключаются.

В случае поступления асинхронных сигналов с блоков 1 разной частоты, влекущих за собой переполнение счетчиков, устройство работает следующим образом.

Для выявления наличия переполнения счетчиков как при суммировании так и при вьтитании импульсов в них выделен дополнительньй старший знаковый разряд. При отсутствии переполнения значения младшего и дополнительного старшего знаковых разрядов совпадают, что контролируется соответствующими элементами 12.

В случае появления переполнения в счетчике 9 на выходе элемента 12 появляется разрешающий уровень, поступакнций на первый вход второго 14 и на второй вход первого 15 элементов И-НЕ. При этом на первый вход элемента И-НЕ, 15 поступает сигнал с выхода младшего знакового разряда счетчика 9, который в случае переполнения с 1етчика при су мировании соответствует разрешающему уровню для формирования на выходе элемента И-НЕ 15 запрещающе- )го уровня, поступающего на второй :вход элемента И 8, который обеспечивает блокировку суммирующего входа счетчика на время его переполнения. При этом на выходной шине 18 переполнения счетчика при суммировании присутствует нулевой потенциал, который означает наличие переполнения соответствующего счетчика при суммировании импульсов.

На второй вход элемента И-НЕ 14 через инвертор 11 поступает инверсный сигнал с выхода младшего знакового разряда счетчика 9, который в случае переполнения счетчика при вычитании соответствует разрешающему уровню для формирования на выходе элемента И-НЕ 14 запрещаю2151134

щего уровня, поступающего на второй вход элемента И 7, который обеспечивает блокировку вычитающего входа счетчика на время его перепол- 5 нения. При этом на выходной шине 17 переполнения счетчика при вычитании присутствует нулевой пoтeнциaJ который означает наличие переполнения соответствующего счетчика при 10 вычитании импульсов.

Таким образом, в устройстве происходит контроль над работой реверсивных счетчиков, блокировка их входов на время переполнения, а 15 также выдача сигнала на выходную шину переполнения при суммировании или вычитании импульсов

Наличие в устройстве шин переполнения счетчиков при суммировании и 20 вычитании позволяет осуществлять вьщачу импульсов из резервированных блоков в устройство для мажоритарного выбора асинхронных сигналов по асинхронному принципу, .т.е. после 25 в устройство-очередного импульса из резервируемого блока , в нем С могут быть проанализированы,состояния шин переполнения счетчиков. По результатам анализа резервируемый 30 блок, соответств5 ющий счетчику, в котором произошло переполнение при суммировании импульсов, может быть выведен в состояние останова на время наличия сигнала на соответствующей шине переполнения счетчика при суммировании. В случае реализации описанной работы резервируемых блоков с устройством емкость счетчика может иметь небольшую величину, что снизит общее количество элементов,- входящее в предлагаемое устройство.

Наличие в устройстве контроля над работой реверсивных счетчиков, блокировки их входов на время переполнения, а также выходных шин переполнения при суммировании и вычитании импульсов позволяет исключить сбои в работе счетчиков; т.е. устройство для мажоритарного выбора асинхронных сигналов работает надежно при произвольной величине рассинхронизации частот сигналов, . поступающих с выходов резервируемых блоков.

Предлагаемое устройство позволяет 55 резервировать аппаратуру, работа ко-, торой незасинхронизирована между собой, на входные сигналы не накладывается никаких ограничений, что

35

40

50

во многих случаях упрощает резервируемые системы в целом.

I

Формула изобретения

Устройство для мажоритарного выбора асинхроиных сигналов, содержащее в каждом из трех каналов резервируемый блок, три элемента И, эле- ,10

меит задержки, первый инвертор, два элемента ИЛИ и реверсивнь счетчик, при этом первые входы первого и второго элементов И соединены с выхо дом соответствующего резервируемого 15 блока, выход первого элемента И через элемент задержки подключен к первому входу первого элемента ШШ, второй вход которого соединен с выходом второго элемента И, а 20 выходы информационных разрядов реверсивного счетчика через второй элемент ИШ подключены к первому входу третьего элемента И, выход которого соединен с соот 25 ветствующим входом мажоритарного элемента, выход которого, явлжопснйся выходом устройства, подключен к объединенньм вторым входам первых элементов Ник входам первых инверторов зо

выходы которых соединены с соответствующими вторыми входами вторых :элементов И, отличающееся тем, что, с целью повышения надежности и достоверности контроля уст- ройства, в него введены в каждый

из трех каналов четвертый и пятый элементы И, элемент сравнения, второй инвертор, два элемента И-НЕ, при этом выход первого элемента ИЛИ подключен к первому входу четвертого элемента И, выход которого соединен с суммирующим входом соответствующего счетчика, выход младшего знакового разряда которого подключен к входу второго инвертора, первому входу элемента сравнения и первому входу первого элемента И-НЕ, а выход дополнительного старшего знакового разряда счетчика соединен е вторым входом элемента сравнения, выход которого подключен к первому входу второго и второму входу первого элементов И-НЕ, выход второго инвертора соединен с объединенньа ш вторыми входами третьего элемента И и вто- рого элемента И-НЕ, выход которого подключен к соответствующей выходной шине переполнения счетчика при вычитании к первому входу пятого элемента И, выход первого элемента И-НЕ соединен с соответствующей выходной шиной переполнения счетчика при суммировании и с вторым входом четвертого элемента И, выход мажоритарного элемента подключен к объединенным вторым входам пятых элементов И,выходы которых содинены с соответствующими вычитающими входами реверсивных счетчиков.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ | 1996 |

|

RU2110835C1 |

| Мажоритарное устройство | 1984 |

|

SU1399905A1 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ | 2008 |

|

RU2396591C1 |

| МАЖОРИТАРНОЕ УСТРОЙСТВО | 1996 |

|

RU2105347C1 |

| Мажоритарное устройство | 1978 |

|

SU744581A1 |

| Устройство для мажоритарного выбора сигналов | 1991 |

|

SU1833876A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием напряжения в частоту импульсов | 1985 |

|

SU1305856A1 |

| Резервированное устройство | 1973 |

|

SU478310A1 |

| Мажоритарное устройство | 1981 |

|

SU1019636A1 |

| Мажоритарно-резервированное устройство | 1980 |

|

SU1032600A1 |

Изобретение относится к облас ти автоматики и вычислительной техники и может использоваться при построении высоконадежных устройств. Цель изобретения - повышение надежности достоверности контроля устройства. Устройство состоит из резервируемых блоков, элементов И, ИЛИ, инверторов, элемен- та И-НЕ, мажоритарного элемента и реверсивных счетчиков. При пос туплении асинхронных сигналов для выявления переполнения счетчиков как при суммировании, так и при вычитании импульсов в них выделен дополнительный старший знаковый разряд, на время переполнения производится блокировка счетчиков, а также вьщача сигнала на выходную шину переполнения. Это позволяет исключить сбои в работе счетчиков при произвольной величине рассин- хронизации частот сигналов, поступающих с вькодов резервируемых блоков. 1 Ш1. (Л сл со

Составитель В. Максимов Редактор А. Лежнина Техред О.Неце Корректор А. Зимокосов

Заказ 907/56 Тираж 673 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ШШ Патент, г. Ужгород, ул. Проектная, А

| Устройство для мажоритарного выбора асинхронных сигналов | 1982 |

|

SU1056489A1 |

| Мажоритарное устройство | 1978 |

|

SU744581A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Мажоритарное устройство | 1981 |

|

SU1019636A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-02-28—Публикация

1984-08-27—Подача