мы входного 1 и нулевого 2 напряжений, управляемый делитель 3 напряжения, цифроаналоговый преобразователь А, преобразователь 3 напряжения в частоту импульсов, первый реверсивный счетчик 6, регистр 7, блок 8 управления реверсом, первый и второй 9 и 10 элементы ИЛИ, первьм и второй элементы И 13, 14, блок 20 управления, с целью повьшения быстродейст1

Изобретение относится к импульсной технике, в частности к преобразователям аналогового сигнала в цифровой код с промежуточным преобразованием в частоту импульсов.

Цель изобретения - повышение быстродействия за счет уменьшения величины шага квантования входного сигнала во времени.

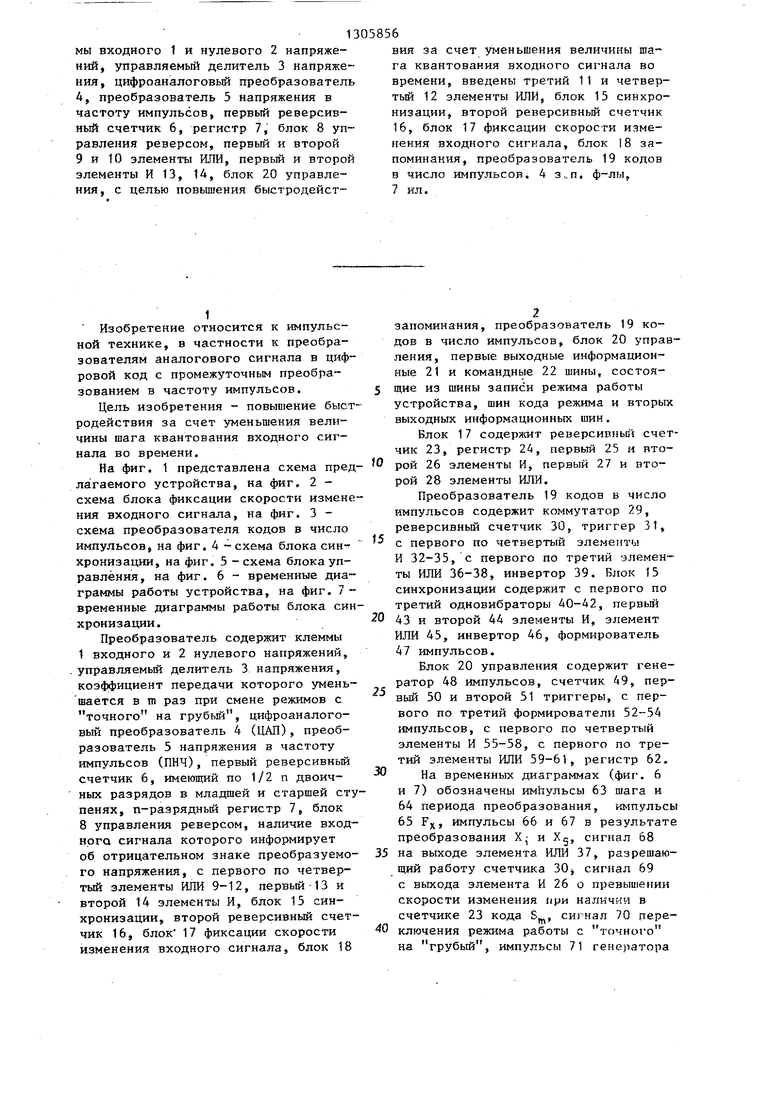

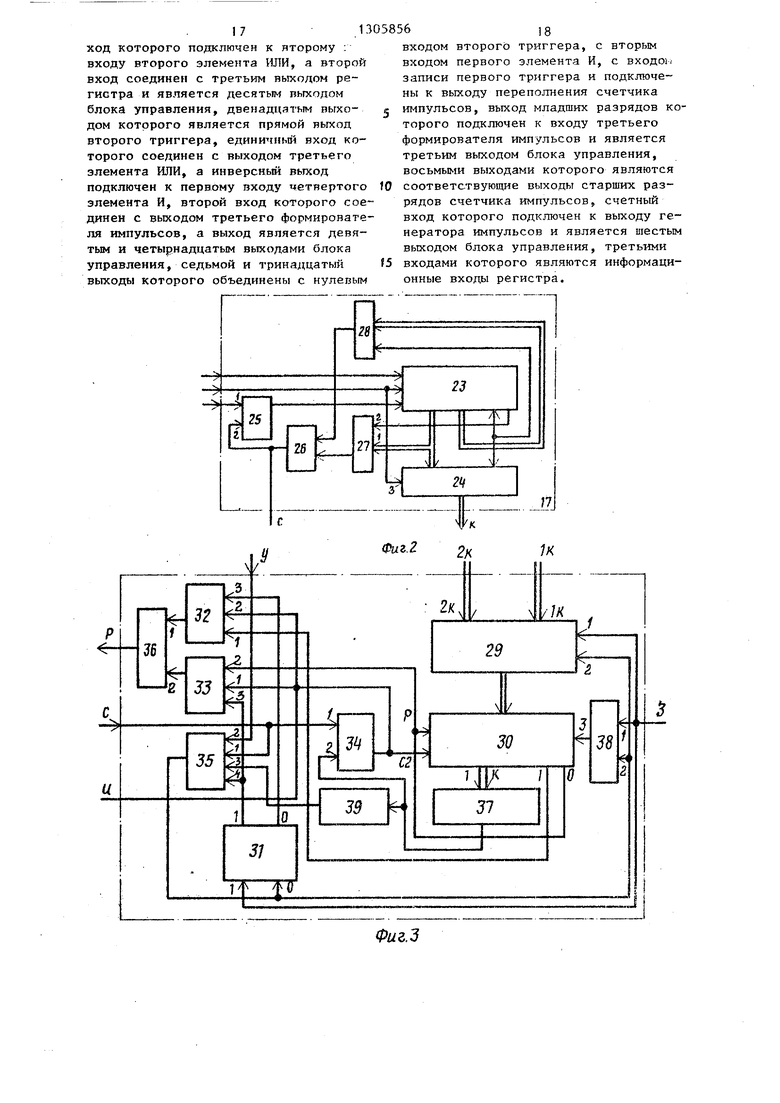

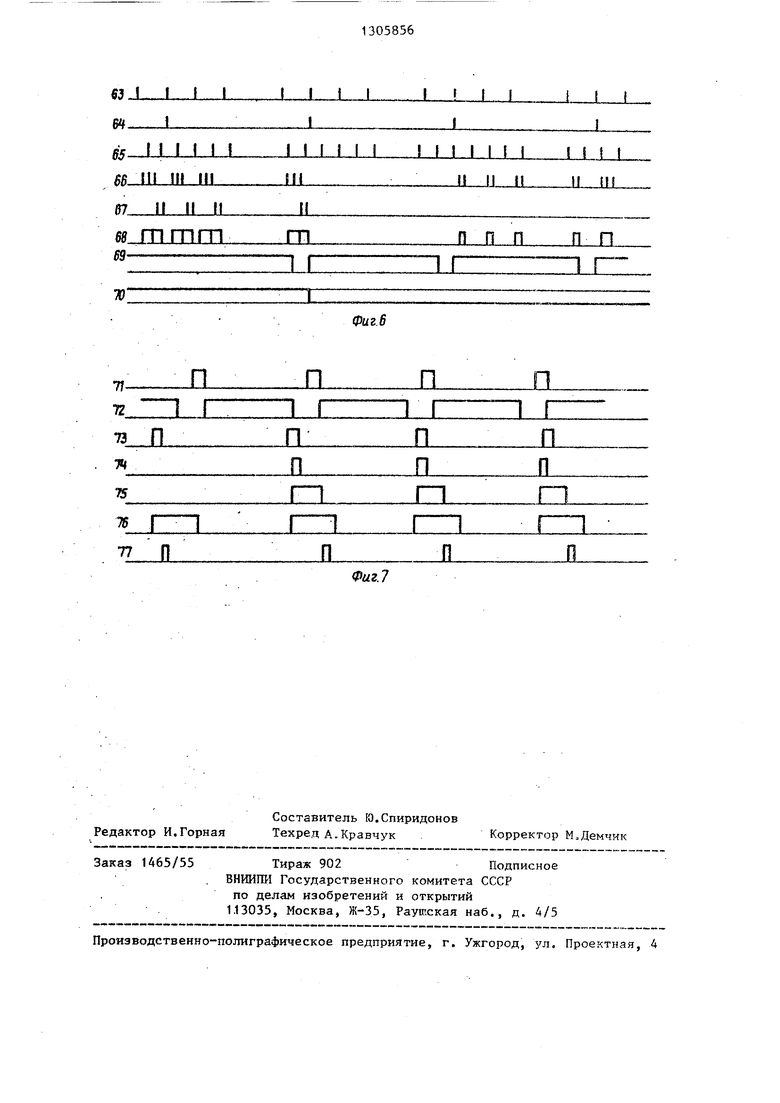

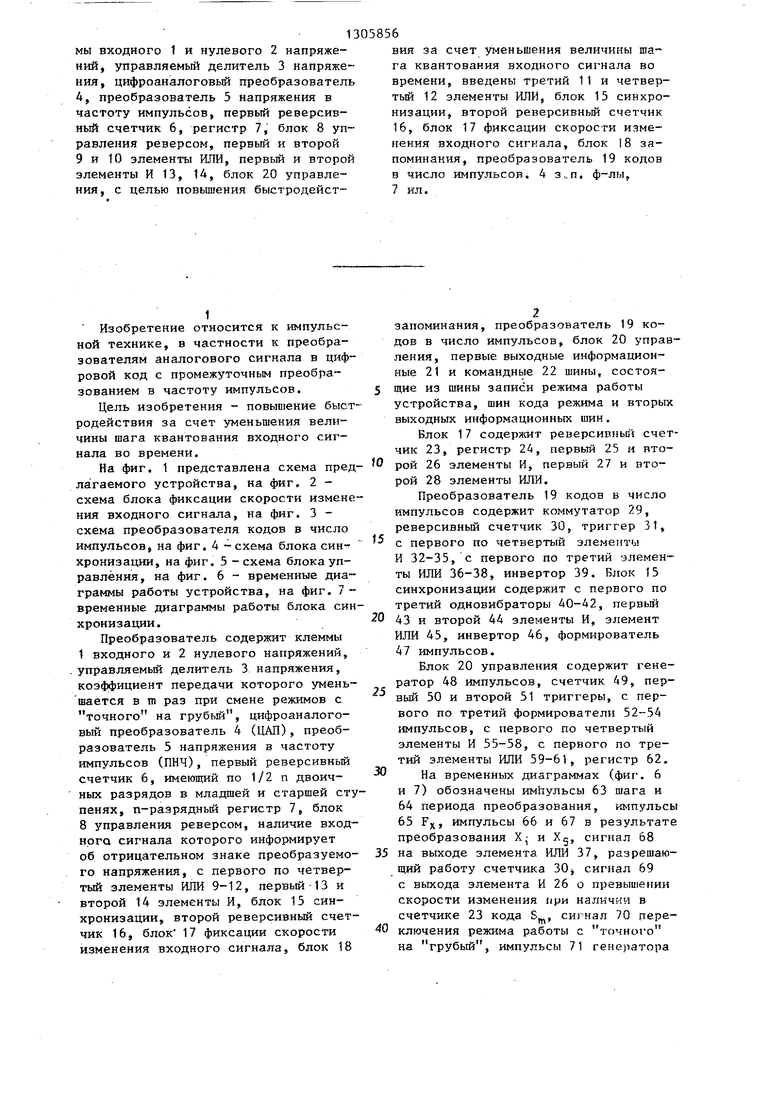

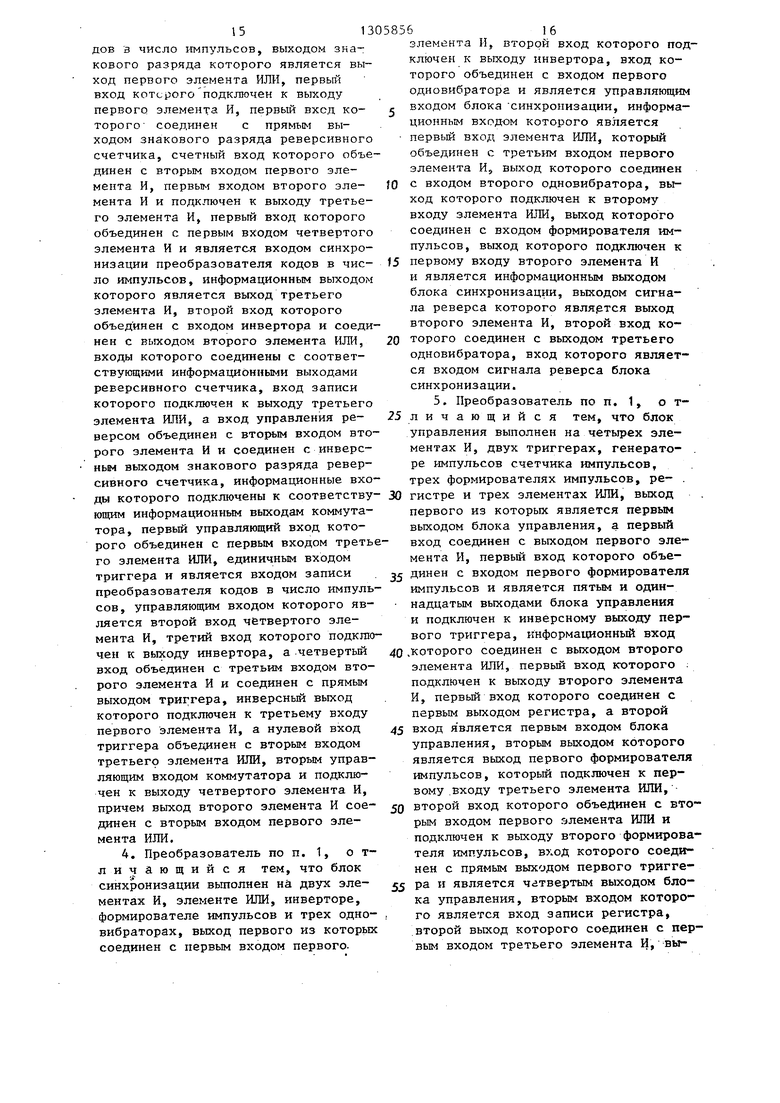

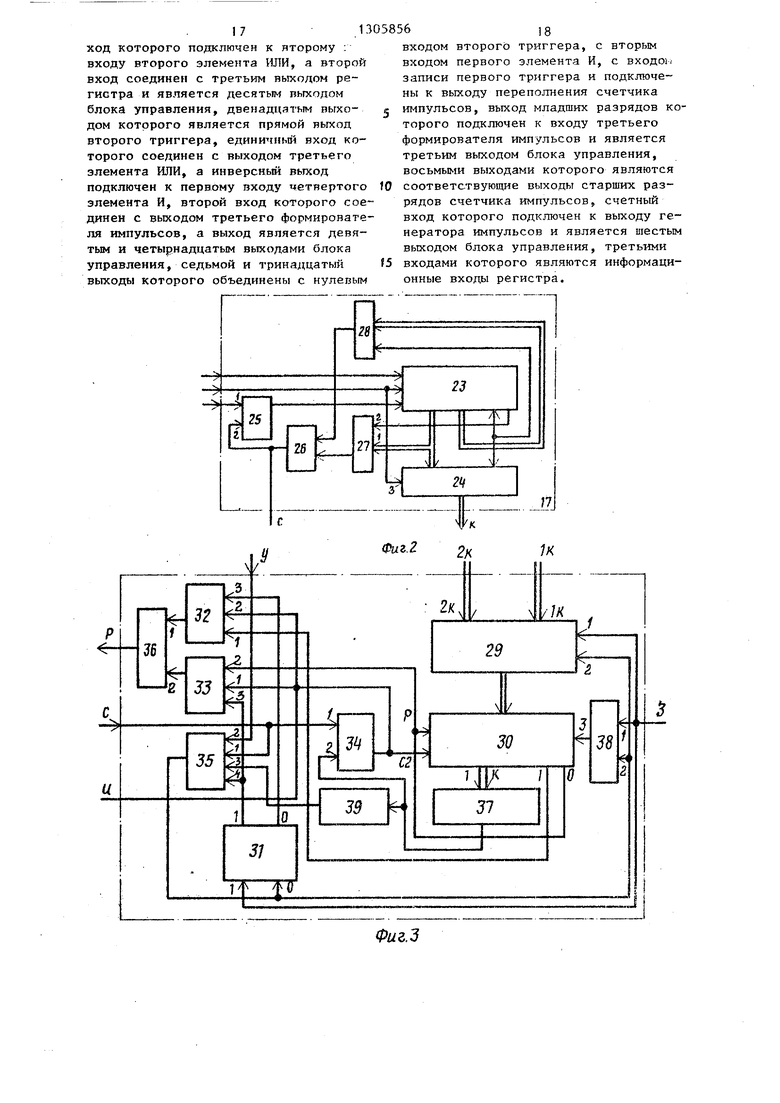

На фиг. 1 представлена схема предлагаемого устройства, на фиг. 2 - схема блока фиксации скорости изменения входного сигнала, на фиг. 3 - схема преобразователя кодов в число импульсов, на фиг. 4 -схема блока синхронизации, на фиг. 5 - схема блока управления , на фиг. 6 - временные диаграммы работы устройства, на фиг. 7- временные диаграммы работы блока синхронизации.

Преобразователь содержит клеммы 1 входного и 2 нулевого напряжений, управляемый делитель 3 напряжения, коэффициент передачи которого уменьшается в m раз при смене режимов с точного на грубый, цифроаналоговый преобразователь 4 (ЦАП), преобразователь 5 напряжения в частоту импульсов (ПНЧ), первый реверсивный счетчик 6, имеющий по 1/2 п двоичных разрядов в младшей и старшей ступенях, п-разрядный регистр 7, блок 8 управления реверсом, наличие входного сигнала которого информирует об отрицательном знаке преобразуемого напряжения, с первого по четвертый элементы ИЛИ 9-12, первый-13 и второй 14 элементы И, блок 15 синхронизации, второй реверсивный счетчик 16, блок 17 фиксации скорости изменения входного сигнала, блок 18

вия за счет уменьшения величины ша га квантования входного сигнала во времени, введены третий 11 и четвертый 12 элементы ИЛИ, блок 15 синхронизации, второй реверсивный счетчик 16, блок 17 фиксации скорости изменения входного сигнала, блок 18 запоминания, преобразователь 19 кодов в число импульсов, 4 3.,п. ф-лы, 7 ил.

запоминания, преобразователь 19 кодов в число импульсов, блок 20 управления, первые выходные информационные 21 и командные 22 шины, состоя- щие из шины записи режима работы

устройства, шин кода режима и вторых выходных информационных шин.

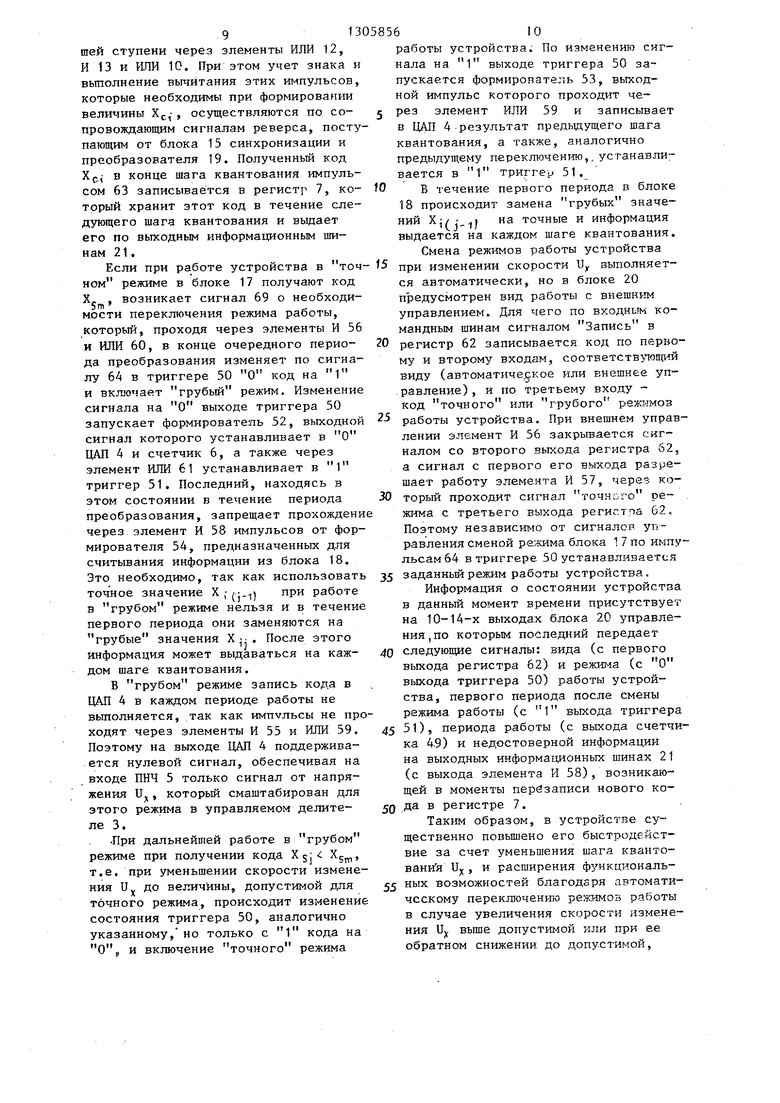

Блок 17 содержит реверсивньгй счетчик 23, регистр 24, первый 25 и вто- рой 26 элементы И, первый 27 и второй 28 элементы ИЛИ.

Преобразователь 19 кодов в число импульсов содержит коммутатор 29, реверсивный счетчик 30, триггер 31, с первого по четвертый элементы

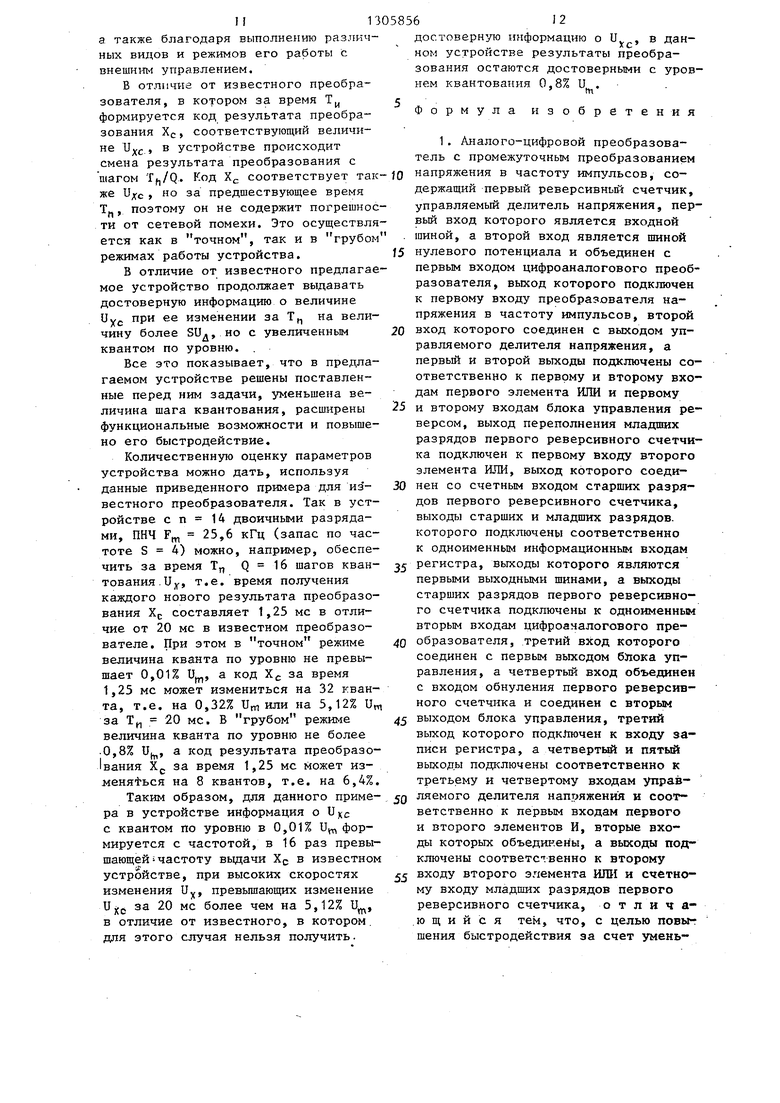

И 32-35, с первого по третий элементы ИЛИ 36-38, инвертор 39. Блок 15 синхронизации содержит с первого по третий одновибраторы 40-42, первый 43 и второй 44 элементы И, элемент ИЛИ 45, инвертор 46, формирователь 47 импульсов.

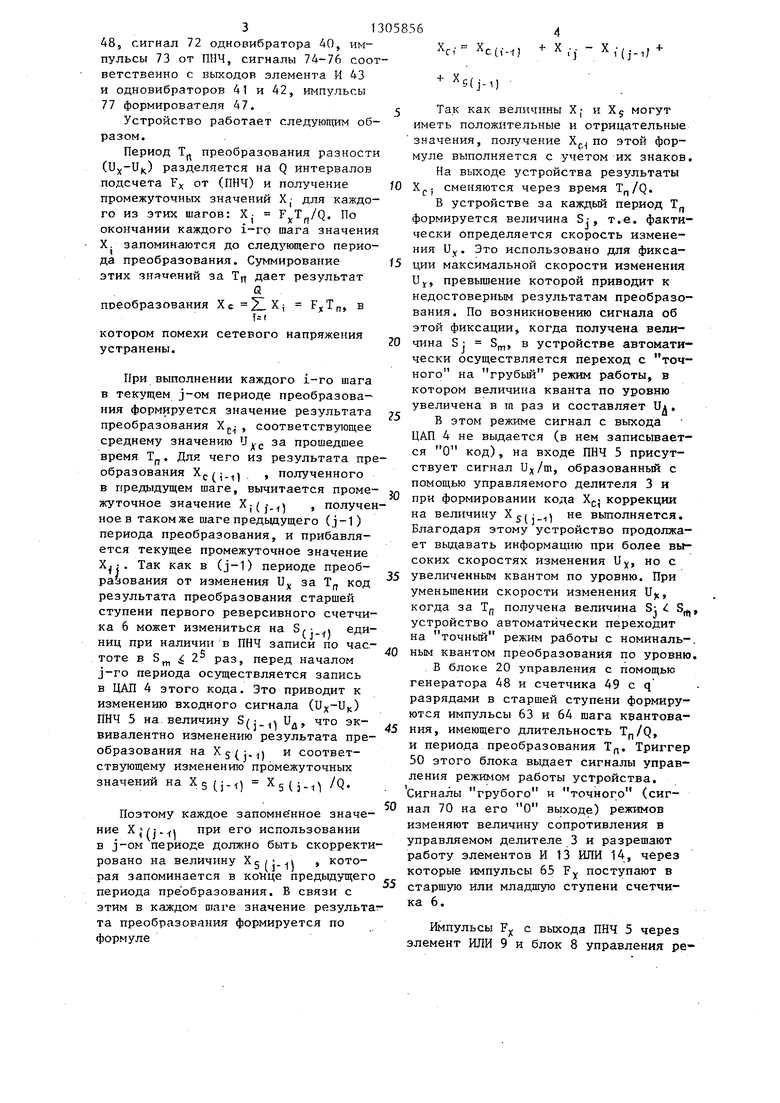

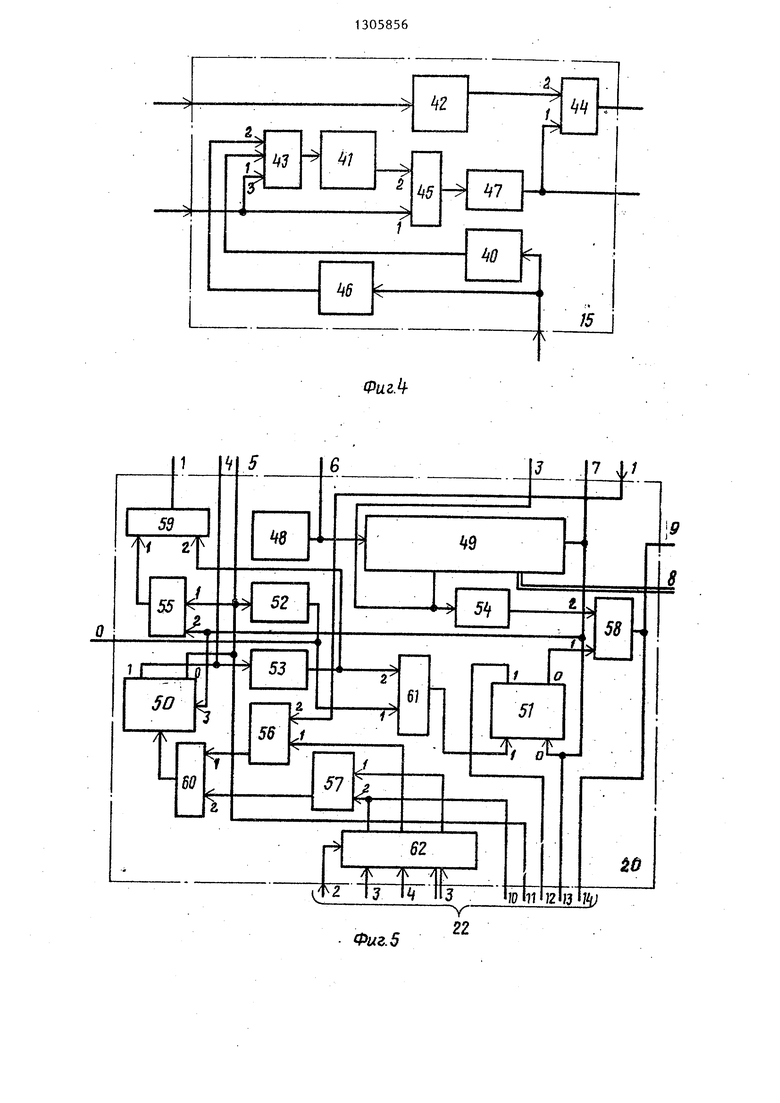

Блок 20 управления содержит генератор 48 импульсов, счетчик 49, первый 50 и второй 51 триггеры, с первого по третий формирователи 52-54 импульсов, с первого по четвертый элементы И 55-58, с первого по третий элементы ИЛИ 59-61, регистр 62. На временных диаграммах (фиг. 6 и 7) обозначены импульсы 63 шага и

64периода преобразования, импульсы

65FX, импульсы 66 и 67 в результате преобразования Х и Хд, сигнал 68

на выходе элемента ИЛИ 37, разрешающий работу счетчика 30, сигнал 69 с выхода элемента И 26 о превышении скорости изменения при наличии в счетчике 23 кода S, сигнал 70 переключения режима работы с точного на грубый, импульсы 71 генератора

31305856

48, сигнал 72 одновибратора 40, импульсы 73 от ПИЧ, сигналы 74-76 соответственно с выходов элемента И 43 и одновибраторов 41 и 42, импульсы 77 формирователя 47.

(1-1)

(j-/+ X

5(J-11

5 Так как величины X; и Ху могут Устройство работает следуюгцим об- иметь положительные и отрицательные разом.

Период Т преобразования разности

значения, nojry4eHHe Х. по этой формуле выполняется с учетом их знаков. На выходе устройства результаты

подсчета 1 от (ПИЧ) и получение /о Х, сменяются через время .

промежуточных значений X,- для каждо- в устройстве за каждый период Т,,

формируется величина S.-, т.е. фактически определяется скорость изменения Uy. Это использовано для фикса- f5 ции максимальной скорости изменения и, превышение которой приводит к недостоверным результатам преобразования. По возникновению сигнала об этой фиксации, когда получена вели(Uv-U) разделяется на Q интервалов

го из этих шагов: Х- , По окончании каждого i-rp шага значения X. запоминаются до следующего периода преобразования. Суммирование этих значений за Тп дает результат

Q поеобразования Хс 21Х; ,, в

|г(

котором помехи сетевого напряжения устранены.

20 чина Sj S, в устройстве автоматически осуществляется переход с точПри выполнении каждого i-ro шага в текущем j-OM периоде преобразования формируется значение результата 5 преобразования Х , соответствующее среднему значению И., за прошедшее время Т. Для чего из результата преобразования Хр/.. , полученного в предыдущем шаге, вычитается проме- ,д жуточное значение Xj(j-. , полученное в такомже ojare предьщущего (j-1) периода преобразования, и прибавляется текущее промежуточное значение

ного на грубьй режим работы, в котором величина кванта по уровню увеличена в тп раз и составляет Ш,

В этом режиме сигнал с выхода ПАП 4 не выдается (в нем записьшает- ся О код), на входе ПНЧ 5 присутствует сигнал , образованный с помощью управляемого делителя 3 и при формировании кода Х. коррекции на величину не вьшолняется,

Благодаря этому устройство продолжает выдавать информацию при более высоких скоростях изменения U, но с 35 увеличенным квантом по уровню. При уменьшении скорости изменения U(,

с туп ени пёрв ого реверсив ного счетчи- ° п величина Sj S, ка 6 может измениться на S, - Устройство автоматически переходит

. Так как в (j-1) периоде преобразования от изменения U за Т, код результата преобразования старшей

(-,} адиниц при наличии в ПНЧ записи по частоте в S ; 2

на точный режим работы с номиналь-. 40 ным квантом преобразования по уровню.

В блоке 20 управления с помощью генератора 48 и счетчика 49 с q разрядами в старшей ступени формируrri.Tt с -. гтютсяимпульсы 63 и 64 шага квантоваПНЧ 5 на. величину S/.- , V.. что эк-... оа lu а

45 ния,имеющего длительность .

вивалентно изменению neчvльтятя ппр- - -П

и периода преобразования Tf,. Триггер 50 этого блока вьщает сигналы управления режимом работы устройства, сигналы грубого и точного (сигПоэтому каждое запомненное значе- ° « ° О режимов

ние Х;п-., при его использованииизменяют величину сопротивления в

в должно быть скорректи-Управляемом делителе 3 и разрешают

ровано на величину Х,,- .. , кото-Р оту элементов И 13 ИЛИ 14, через

рая запоминается в коУ1|е 1редьвдущего ,е импульсы 65 F, поступают в

. ,, ,,5iстаршую или младшую ступени счетчипериода преобразования. В связи сv-idij j t j

КЗ. о

этим в каждом шаге значение результаг т f Рзз, перед началом j-ro периода осуществляется запись в ЦАП 4 этого кода. Это приводит к изменению входного сигнала (Ux-U)

вивалентно изменению результата пре образования на X5(j.i) и соответствующему изменению промежуточных значений на . Хд(.| /Q.

та преобразования формируется по формуле

(1-1)

(j-/+ X

5(J-11

20 чина Sj S, в устройстве автоматически осуществляется переход с точного на грубьй режим работы, в котором величина кванта по уровню увеличена в тп раз и составляет Ш,

В этом режиме сигнал с выхода ПАП 4 не выдается (в нем записьшает- ся О код), на входе ПНЧ 5 присутствует сигнал , образованный с помощью управляемого делителя 3 и при формировании кода Х. коррекции на величину не вьшолняется,

Благодаря этому устройство продолжает выдавать информацию при более высоких скоростях изменения U, но с увеличенным квантом по уровню. При уменьшении скорости изменения U(,

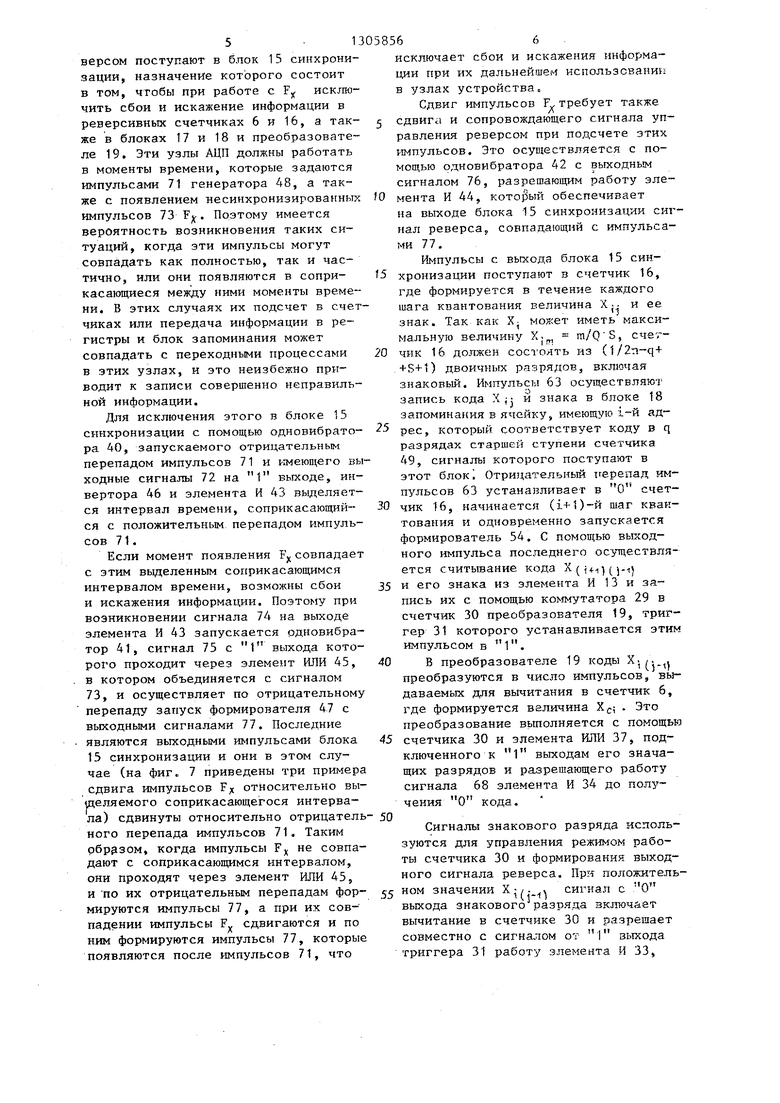

Импульсы Fj( с выхода ПНЧ 5 через элемент ИЛИ 9 и блок 8 управления реверсом поступают в блок 15 синхронизации, назначение которого состоит в том, чтобы при работе с F, исключить сбои и искажение информации в реверсивных счетчиках 6 и 16, а также в блоках 17 и 18 и преобразователе 19, Эти узлы АЦП должны работать в моменты времени, которые задаются импульсами 71 генератора 48, а также с появлением несинхронизированных импульсов 73 7, Поэтому имеется вероятность возникновения таких ситуаций, когда эти импульсы могут совпадать как полностью, так и частично, или они появляются в соприкасающиеся между ними моменты времени. В этих случаях их подсчет в счетчиках или передача информации в регистры и блок запоминания может совпадать с переходными процессами в этих узлах, и это неизбежно приводит к записи совершенно неправильной информации.

Для исключения этого в блоке 15 синхронизации с помощью одновибрато- ра 40, запускаемого отрицательным перепадом импульсов 71 и имеющего выходные сигналы 72 на 1 выходе, инвертора 46 и элемента И 43 выделяется интервал времени, соприкасающийся с положительным перепадом импульсов 71.

Если момент появления F совпадает с этим выделенным соприкасающимся интервалом времени, возможны сбои и искажения информации. Поэтому при возникновении сигнала 74 на выходе элемента И 43 запускается одновибра- тор 41, сигнал 75 с 1 выхода которого проходит через элемент ИЛИ 45, . в котором обьединяется с сигналом 73, и осуществляет по отрицательному перепаду запуск формирователя 47 с выходными сигналами 77. Последние . являются выходными импульсами блока 15 синхронизации и они в этом случае (на фиг. 7 приведены три примера сдвига импульсов F;c относительно вы- щеляемого соприкасающегося интервала) сдвинуты относительно отрицатель- 50 ного перепада импульсов 71. Таким образом, когда импульсы F не совпадают с соприкасающимся интервалом, они проходят через элемент ИЛИ 45,

40

В преобразователе 19 коды Х преобразуются в число импульсо даваемых для вычитания в счетчи где формируется величина Х.; . преобразование вьшолняется с п 45 счетчика 30 и элемента ИЛИ 37, ключенного к 1 выходам его зн щих разрядов и разрешающего ра сигнала 68 элемента И 34 до п 0

чения

кода.

Сигналы знакового разряда ис зуются для управления режимом р ты счетчика 30 и формирования в ного сигнала реверса. При полож

и ПО их отрицательным перепадам фор- 55 значении Х-/.. сигнал с

мируются импульсы 77, а при их совпадении импульсы F. сдвигаются и по

Л

ним формируются импульсы 77, которые появляются после импульсов 71, что

выхода знакового разряда включа вычитание в счетчике 30 и разре совместно с сигналом от 1 вых триггера 31 работу элемента И 3

исключает сбои и искажения информации при их дальнейшем использсванип в узлах устройства

Сдвиг импульсов F, требует также

сдвигг и сопровождающего сигнала управления реверсом при подсчете этих импульсов. Это осуществляется с помощью одновибратора 42 с выходным сигналом 76, разрешающим работу элемента И 44, обеспечивает

на выходе блока 15 синхронизации сигнал реверса, совпадающий с импульсами 77.

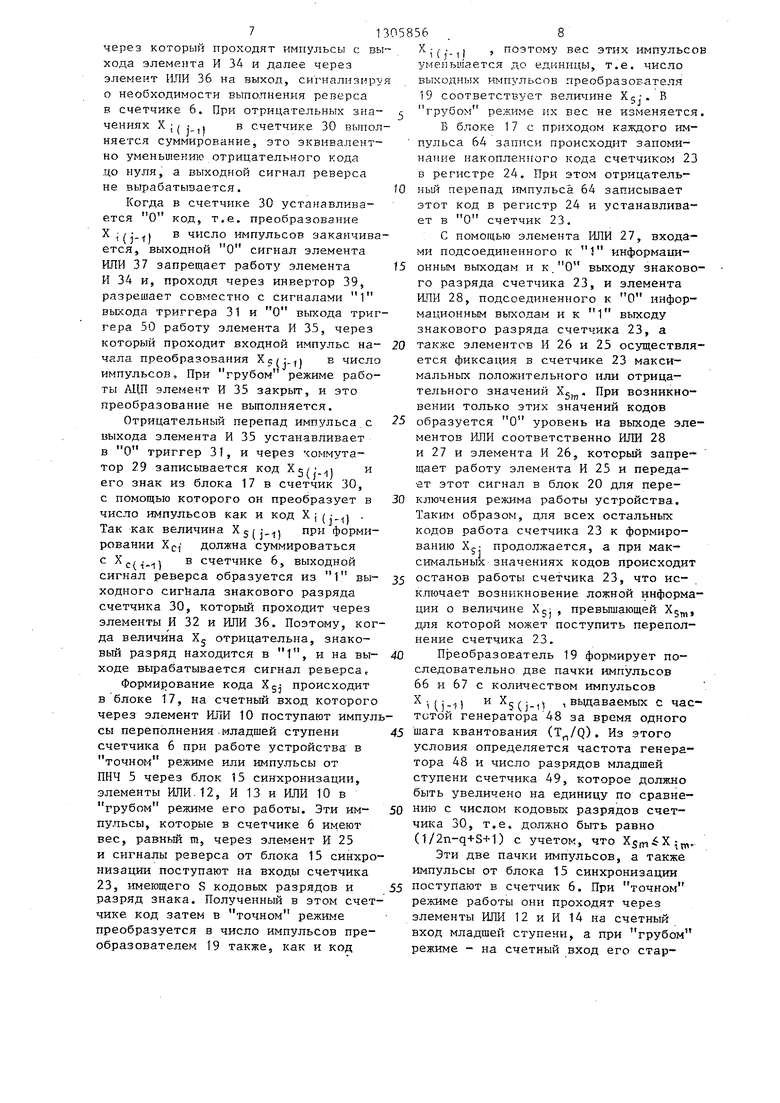

Импульсы с выхода блока 15 синхронизации поступают в счетчик 16, где формируется в течение каждого шага квантования величина Xj. и ее знак. Так как Х- может иметь максимальную величину Х ,, ra/Q S, счег- чик 16 должен состоять из ( +S+1) двоичных разрядов, включая знаковый. Импульсы 63 осуществляют запись кода Xj: и знака в блоке 18 запоминания в ячейку, имеющую адрес, который соответствует коду в q разрядах старшей ступени счетчика 49, сигналь: которого поступают в этот блок , Отрицательный перепад импульсов 63 устана1шивает в О счетчик 16, начинается (1+1)-й шаг квантования и одновременно запускается формирователь 54. С помощью выходного импульса последнего ос уществля- ется считывание кода X(4i)(j-i) и его знака из элемента И 13 и запись их с помощью коммутатора 29 в счетчик 30 преобразователя 19, триггер 31 которого устанавливается этим импульсом в 1.

В преобразователе 19 коды Х-/. . преобразуются в число импульсов, выдаваемых для вычитания в счетчик 6, где формируется величина Х.; . Это преобразование вьшолняется с помощью счетчика 30 и элемента ИЛИ 37, подключенного к 1 выходам его значащих разрядов и разрешающего работу сигнала 68 элемента И 34 до полу- 0

чения

кода.

Сигналы знакового разряда используются для управления режимом работы счетчика 30 и формирования выходного сигнала реверса. При положитель 0

выхода знакового разряда включает вычитание в счетчике 30 и разрешает совместно с сигналом от 1 выхода триггера 31 работу элемента И 33,

через который проходят импульсы с выхода элемента И 34 и далее через элемент Ш1И 36 на выход, сигнализируя о необходимости выполнения реверса в счетчике 6. При отрицательных зна- чениях Х;( , в счетчике 30 выполняется суммирование, это эквивалентно уменьшекшо отрицательного кода до нуля, а выходной сигнал реверса не вырабатывается.

Когда в счетчике 30 устанавливается О код, т.е. преобразование

Х,/;.1 В ЧИСЛО импульсов заканчивается, выходной О сигнал элемента ИЛИ 37 запрещает работу элемента И 34 и, проходя через инвертор 39, разрешает совместно с сигналами 1 выхода триггера 31 и О выхода триггера 50 работу элемента И 35, через который проходит входной импульс начала преобразования Х5(;.л в число импульсов. При грубом режиме работы АЦП элемент И 35 закрыт, и это преобразование не выполняется.

Отрицательный перепад импульса с выхода элемента И 35 устанавливает в О триггер 31, и через коммутатор 29 записывается код Хд/ i и его знак из блока 17 в счетчик 30, с помощью которого он преобразует в число и шульсов как и код X j ( - п - Так как величина 5(1-1) формировании должна суммироваться с y cii-- счетчике 6, выходной сигнал реверса образуется из 1 выходного сигнала знакового разряда счетчика 30, который проходит через элементы И 32 и ИЛИ 36. Поэтому, когда величина Xj отрицательна, знако- Bbrii разряд находится в 1, и на вы

ходе вырабатывается сигнал реверса, Формирование кода Xgj происходит в блоке 17, на счетный вход которого через элемент ИЛИ 10 поступают импульсы переполнения младшей ступени счетчика 6 при работе устройства в

точном режиме или импульсы от ПНЧ 5 через блок 15 синхронизации, элементы ИЛИ.12, И 13 и ИЛИ 10 в грубом режиме его работы. Эти импульсы, которые в счетчике 6 имеют вес, равньй т, через элемент И 25 и сигналы реверса от блока 15 синхроЭти две пачки импульсов, а также импульсы от блока 15 синхронизации

низации поступают на входы счетчика 23, имеющего S кодовых разрядов и 55 поступают в счетчик 6. При точном разряд знака. Полученный в этом счет- режиме работы они проходят через чике код затем в точном режш.1е элементы ИЛИ 12 и И 14 на счетный преобразуется в число импульсов пре- вход младшей ступени, а при грубом образователен 19 также, как и код режиме - на счетный вход его стар

поэтому вес этих импульсов

0

0

5

it)-1,1 уме}1ьшается до единицы, т.е. число

выходных импульсов преобразователя 19 соответствует вел1-гчине Xj;. В грубом режиме их вес не изменяется.

В блоке 17 с приходом каждого импульса 64 записи происходит запоминание накопленного кода счетчиком 23 в регистре 24, При этом отрицатель- ньш перепад импульса 64 записывает этот код в регистр 24 и устанавливает в О счетчик 23,

С помощью элемента ИЛИ 27, входами подсоединенного к 1 информационным выходам и к.О выходу знакового разряда счетчика 23, и элемента ИЛИ 28, подсоединенного к О информационным выходам и к 1 выходу знакового разряда счетчика 23, а также элементов И 26 и 25 осуществляется фиксация в счетчике 23 максимальных положительного или отрицательного значений Х,. При возникновении только этих значений кодов

5 образуется О уровень на выходе элементов ИЛИ соответственно ИЛИ 28 и 27 и элемента И 26, который запре щает работу элемента И 25 и передает этот сигнал в блок 20 для пере0 ключения режима работы устройства. Таким образом, для всех остальных кодов работа счетчика 23 к формированию Хд- продолжается, а при максимальных значениях кодов происходит

5 останов работы счетчика 23, что исключает возникновение ложной информации о величине Xj; , превьшающей Х,, для которой может поступить переполнение счетчика 23.

0 Преобразователь 19 формирует последовательно две пачки импульсов 66 и 67 с количеством импульсов

X : ( : - 1 И Х,

.,j) и A2(-j , выдаваемых с частотой генератора 48 за время одного

5 шага квантования (), Из этого условия определяется частота генератора 48 и число разрядов младшей ступени счетчика 49, которое должно быть увеличено на единицу по сравне0 нию с числом кодовых разрядов счетчика 30, т.е. должно быть равно

(1/2n-q- -S+1) с учетом, что

iw

Эти две пачки импульсов, а также импульсы от блока 15 синхронизации

5 поступают в счетчик 6. При точном режиме работы они проходят через элементы ИЛИ 12 и И 14 на счетный вход младшей ступени, а при грубом режиме - на счетный вход его старшей ступени через элементы ИЛИ 12, И 13 и И.ПИ 10, При этом учет знака и вьтолнение вычитания этих импульсов, которые необходимы при формировании величины Xj.- , осуществляются по со- провождающим сигналам реверса, поступающим от блока 15 синхронизации и преобразователя 19. Полученный код Хр в конце шага квантования импульсом 63 записывается в регистр 7, который хранит этот код в течение следующего шага квантования и выдает его по выходным информационным шинам 21.

ном

Sm

Если при работе устройства в точ- 15 при изменении скорости И выполняется автоматически, но в блоке 20 предусмотрен вид работы с внешним управлением. Для чего по входным командным шинам сигналом Запись в 20 регистр 62 записывается код по первому и второму входам, соответствуюяр-ш виду (автоматиче§.кое или внешнее управление) , и по третьему входу - код точного или грубого реж-шов

режиме в блоке 17 получают код , возникает сигнал 69 о необходимости переключения режима работы, который, проходя через элементы И 56 и ИЛИ 60, в конце очередного периода преобразования изменяет по сигналу 64 в триггере 50 О код на 1 и включает грубый режим. Изменение сигнала на О выходе триггера 50

запускает формирователь 52, выходной 25 работы устройства. При внешнем управ- сигнал которого устанавливает в О ЦАП 4 и счетчик 6, а также через элемент ИЛИ 61 устанавливает в 1 триггер 51. Последний, находясь в этом состоянии в течение периода 30 преобразования, запрещает прохождение через элемент И 58 импульсов от формирователя 54, предназначенных для считывания информации из блока 18.

лении элемент И 56 закрывается сигналом со второго выхода регистра 62, а сигнал с первого его выхода разрешает работу элемента И 57, через который проходит сигнал точного ре- . жима с третьего выхода регистра 62,, Поэтому независимо от сигналов управления сменой режима блока 1 7 по импульсам 64 в триггере 50 устанавливается

Это необходимо, так как использовать 35 заданньй режр$м работы устройства.

точное значение Х, /- ,,) при работе в грубом режиме нельзя и в течение первого периода они заменяются на грубые значения . После этого информация может выдаваться на каждом шаге квантования.

В грубом режиме запись кода в ЦАП 4 в каждом периоде работы не вьшолняется, так как ИМПУЛЬСЫ не проходят через элементы И 55 и ИЛИ 59. Поэтому на выходе ЦАП 4 поддерживается нулевой сигнал, обеспечивая на входе ПНЧ 5 только сигнал от напряжения Ujj, который смаштабирован для этого режима в управляемом делителе 3.

-При дальнейшей работе в грубом режиме при получении кода Xji-c Х., т.е. при уменьшении скорости изменения У ко величины, допустимой для точного режима, происходит изменение состояния триггера 50, аналогично указанному, но только с 1 кода на и включение точного режима

работы устройства. По иэмененито сигнала на 1 выходе триггера 50 запускается формирователь 53, выходной импульс которого проходит через элемент ИЛИ 59 и записывает в ЦАП 4-результат предыдущего шага квантования, а также, аналогично предыдущему переключению,, устанавливается в 1 триггер 51.

В течение первого периода в блоке 18 происходит замена грубых значений Xj/ « на точные и информация выдается на каждом шаге квантования.

Смена режимов работы устройства

работы устройства. При внешнем управ-

лении элемент И 56 закрывается сигналом со второго выхода регистра 62, а сигнал с первого его выхода разрешает работу элемента И 57, через который проходит сигнал точного ре- . жима с третьего выхода регистра 62,, Поэтому независимо от сигналов управления сменой режима блока 1 7 по импульсам 64 в триггере 50 устанавливается

Информация о состоянии устройства в данньш момент времени присутствует на 10-14-х выходах блока 20 управления, по которым последний передает

следующие сигналы: вида (с первого выхода регистра 62) и режима (с О выхода триггера 50) работы устройства, первого периода после смены режима работы (с 1 выхода триггера

51), периода работы (с выхода счетчика 4-9) и недостоверной информации на выходных информационных шинах 21 (с выхода элемента И 58), возникающей в моменты перезаписи нового кода в регистре 7.

Таким образом, в устройстве существенно повъш1ено его быстродействие за счет уменьшения шага кванто- вани я и , и расширения функциональных возможностей благодаря автоматическому пере ключению режимов работы в случае увеличения скорости изменения Uy Bbmie допустимой или при ее обратном снижении до допустимой.

a также благодаря выполнению различных видов и режимов его работы с внешнт управлением.

В отличие от известного преобразователя, в котором за время Т формируется код результата преобразования Хс, соответствующий величине и(с , в устройстве происходит смена результата преобразования с шагом . Код Х,- соответствует так же Upfc но за предшествующее время Т.., поэтому он не содержит погрешности от сетевой помехи. Это осуществляется как в точном, так и в грубом режимах работы устройства.

В отличие от известного предлагаемое устройство продолжает выдавать достоверную информацию о величине Uyj, при ее изменении за Т на величину более ЗОд, но с увеличенным квантом по уровню. .

Все это показывает, что в предлагаемом устройстве решены поставленные перед ним задачи, уменьшена величина шага квантования, расширены функциональные возможности и повышено его быстродействие.

Количественную оценку параметров устройства можно дать, используя данные приведенного примера для из - вестного преобразователя. Так в устройстве с п 14 двоичными разрядами, ПНЧ F 25,6 кГц (запас по частоте ) можно, например, обеспечить за время Т„ Q 16 шагов кван- тования.иу, т.е. время получения каждого нового результата преобразования Хр составляет 1,25 мс в отличие от 20 мс в известном преобразователе. При этом в точном режиме величина кванта по уровню не превышает 0,01% Uj, а код Хс за время 1,25 мс может измениться на 32 кванта, т.е. на 0,32% и или на 5,12% U за Т 20 мс. В грубом режиме величина кванта по уровню не более .0,8% U(, а код результата преобразо- 1вания X.J.. за время 1,25 мс может из- меняФься на 8 квантов, т.е. на 6,4%

Таким образом, для данного приме- ра в устройстве информация о с квантом по уровню в 0,01% И формируется с частотой, в 16 раз превышающей частоту выдачи Хс в известном устройстве, при высоких скоростях изменения Ujj, превьшгающих изменение U;{(; за 20 мс более чем на 5,12% U, в отличие от известного, в котором, для этого случая нельзя получить.

достоверную информацию о U , в данном устройстве результаты преобразования остаются достоверными с уровнем квантования 0,8% U ,

ITl

Формула изобретения

1. Аналого-цифровой преобразователь с промежуточным преобразованием напряжения в частоту импульсов, содержащий первый реверсивный счетчик, управляемый делитель напряжения, первый вход которого является входной шиной, а второй вход является шиной нулевого потенциала и объединен с первым входом цифроаналогового преобразователя, выход которого подключен к первому входу преобразователя напряжения в частоту импульсов, второй вход которого соединен с выходом управляемого делителя напряжения, а первый и второй выходы подключены соответственно к первому и второму входам первого элемента ИЛИ и первому и второму входам блока управления реверсом, выход переполнения младших разрядов первого реверсивного счетчика подключен к первому входу второго элемента ИЛИ, выход которого соединен со счетным входом старших разрядов первого реверсивного счетчика, выходы старших и младших разрядов. которого подключены соответственно к одноименным информационным входам регистра, выходы которого являются первыми выходными шинами, а выходы старших разрядов первого реверсивного счетчика подключены к одноименным вторым входам цифроаналогового преобразователя, третий вход которого соединен с первым выходом блока управления, а четвертый вход объединен с входом обнуления первого реверсивного счетчика и соединен с вторым выходом блока управления, третий выход которого пЬдк.Лючен к входу записи регистра, а четвертый и пятый выходы подключены соответственно к третьему и четвертому входам управляемого делителя напряжения и соответственно к первым входам первого и второго элементов И, вторые входы которых объединены, а выходы подключены соответс-твенно к второму входу второго элемента ИЛИ и счетному входу младших разрядов первого реверсивного счетчика, отличи- .ю щ и и с я тем, что, с целью повыг шения быстродействия за счет уменьшения величины шага квантования входного сигнала во времени, введены третий и четвертый элементы ИЛИ, блок синхронизации, второй реверсивньш счетчик, блок фиксации скорости изменения входного сигнала, блок запоминания, преобразователь кодов в число импульсов, вход синхронизации которого объединен с управляющим

входом блока синхронизации и соединен fO личающийся тем, что блок

с шестым выходом блока управления, седьмой выход которого подключен к входу записи блока фиксации скорости изменения входного сигнала, счетный вход которого соединен с выходом второго элемента ИЛИ, сигнальный выход подключен к первому входу блока управления, а информационные выходы подключены к первым одноименным ин- формационным входам преобразователя кодов в число импульсов, вторые информационные входы которого соединены с одноименными информационными выходами блока запоминания, информационные входы которого соединены с одноименными информационными выходами второго реверсивного счетчика,, вход обнуления которого объединен с входом записи блока запоминания и соединен с третьим выходом блока управления, восьмые -выходы которого подключены к одноименным адресньп- входам блока запоминания, счетный вход которого объединен с входом записи преобразователя кодов в число импульсов и соединен с девятым выходом блока управления, пятый выход которого подключен к управляющему входу преобразователя кодов в число

импульсов, информационных выход кото- 40 ряда которого соединен с вторым рого подключен к первому входу четвертого элемента ИЛИ, выход которого соединен с вторым входом второго элемента И, а второй вход объединен со счетным входом второго реверсив- 45 ного счетчика и соединен с информационным выходом блока синхронизации, информационный вход которого соединен с выходом первого элемента ИЛИ, вход сигнала реверса - с выходом 50 блока управления реверсом, выход сигнала реверса соединен с входами управления реверсом второго реверсивного счетчика и блока фиксации скорости изменения входного сигнала и с 55 первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом знакового разряда преобразователя кодов в число импульсов, а вывходом первого элемента ИЛИ, вых которого соединен с первым входо второго элемента И, второй вход торого подключен к выходу второг элемента ИЛИ, а выход соединен с рьп- входом первого элемента И и ляется сигнальным выходом блока сации скорости изменения входног сигнала.

3. Преобразователь по п. 1, личающийся тем, что пр разователь кодов в число импульс выполнен на трех элементах ЯПИ, ч тырех элементах И. триггере, инв торе, реверсивном счетчике и ком таторе, первые и вторые информац ные входы которого являются соот ственно первыми и BTopbU .iH ииформ онньми входам;и преобразова геля к

ход подк.ггючен к входу управления реверсом первого реверсивного гчет чика, причем второй вход блока управления является шиной записи кола режима работы устройства, третьи входы являются шиной кода режима, а выходы с десятого по четырнадцатый являются вторыми выходными ишнамк. 2, Преобразователь по п. 1 о тфиксации скорости изменения входного сигнала выполнен на двух элементах И, двух элементах ИЛИ, регистре и реверсивном счетчике, вход обну-

ления которого объединен с входом

записи регистра и является входом записи блока фиксации скорости измене- ния входного сигнала, входом управления реверсом которого является

одноименный вход реверсивного счетчика, счетный вход которого соединен с выходом первого элемента И; первь й вход которого является счетным входом блока фиксации скорости изменения входного сигнала, информационными выходами которого являются одноименные выходы регистра, Н11формгл1лон- ные входы которого объединены с одноименными первьми входами первого

элемента ИЛИ и подключены к однои.чен- ным прямым информационны -} выходам реверсивного счетчика, инверс.ные информационные выходы которого подключены к первым входам второго злемента НИИ, второй вход которого объединен с входом знакового разряда регистра и подключен к прямому выходу знакового разряда реверсивного счетчика, инверсный выход знакового разряда которого соединен с вторым

входом первого элемента ИЛИ, выход которого соединен с первым входом второго элемента И, второй вход которого подключен к выходу второго элемента ИЛИ, а выход соединен с вто рьп- входом первого элемента И и является сигнальным выходом блока фиксации скорости изменения входного сигнала.

3. Преобразователь по п. 1, о тличающийся тем, что преобразователь кодов в число импульсов выполнен на трех элементах ЯПИ, че- - тырех элементах И. триггере, инверторе, реверсивном счетчике и комму- таторе, первые и вторые информационные входы которого являются соответственно первыми и BTopbU .iH ииформаци- онньми входам;и преобразова геля ко

15

дов 3 число импульсов, выходом знакового разряда которого является выход первого элемента ИЛИ, первый вход которого подключен к выходу первого элемента И, первый вход которого- соединен с прямым выходом знакового разряда реверсивного счетчика, счетный вход которого объединен с вторым входом первого элемента И, первым входом второго элемента И и подключен к выходу третьего элемента И, первый вход которого объединен с первым входом четвертого элемента И и является входом синхронизации преобразователя кодов в число импульсов, информационным выходом которого является выход третьего элемента И, второй вход которого объединен с входом инвертора и соединен с выходом второго элемента ИЛИ, входы которого соединены с соответствующими информационными выходами реверсивного счетчика, вход записи которого подключен к выходу третьего элемента ИЛИ, а вход управления реверсом объединен с вторым входом второго элемента И и соединен с инверс- ньм выходом знакового разряда реверсивного счетчика, информационные входы которого подключены к соответству- ющим информационным выходам коммутатора, первый управляющий вход которого объединен с первым входом третьего элемента ИЛИ, единичным входом триггера и является входом записи преобразователя кодов в число импульсов, управляющим входом которого яв

13

ляется второй вход четвертого элемента И, третий вход которого подключен к выходу инвертора, а четвертый вход объединен с третьим входом второго элемента И и соединен с прямым выходом триггера, инверсньй выход которого подключен к третьему входу первого элемента И, а нулевой вход триггера объединен с вторым входом третьего элемента ИЛИ, вторым управляющим входом коммутатора и подключен к выходу четвертого элемента И, причем выход второго элемента И соединен с вторым входом первого элемента ИЛИ.

4. Преобразователь по п. 1, отличающийся тем, что блок синхронизации выполнен на двух элементах И, элементе ИЛИ, инверторе, формирователе импульсов и трех одно- вибраторах, выход первого из которых соединен с первым входом первого.

JO

15

3020

25

0585616

элемента И, второй вход которого подключен к выходу инвертора, вход которого объединен с входом первого одновибратора и является управляющим входом блока синхронизации, информационным входом которого является первый вход элемента ИЛИ, который объединен с третьим входом первого элемента И, выход которого соединен с входом второго одновибратора, выход которого подключен к второму входу элемента ИЛИ, выход которого соединен с входом формирователя импульсов, выход которого подключен к первому входу второго элемента И и является информационным выходом блока синхронизации, выходом сигнала реверса которого является выход второго элемента И, второй вход которого соединен с выходом третьего одновибратора, вход которого является входом сигнала реверса блока синхронизации.

5. Преобразователь по п. 1, отличающийся тем, что блок управления выполнен на четырех элементах И, двух триггерах, генераторе импульсов счетчика импульсов, трех формирователях импульсов, ре- . гистре и трех элементах ИЛИ, выход первого из которых является первым выходом блока управления, а первый вход соединен с выходом первого элемента И, первый вход которого объе35 динен с входом первого формирователя

импульсов и является пятым и один- надцатым выходами блока управления и подключен к инверсному выходу первого триггера, информационный вход

40 .Которого соединен с выходом второго элемента ИЛИ, первый вход которого подключен к выходу второго элемента И, первый вход которого соединен с первым выходом регистра, а второй

45 вход я вляется первьм входом блока управления, вторым выходом которого является выход первого формирователя импульсов, который подключен к первому .входу третьего элемента ИЛИ, 50 второй вход которого объединен с вто рым входом первого элемента ИЛИ и подключен к выходу второго формирователя импульсов, вход которого соединен с прямым выходом первого тригге55 ра и является четвертым выходом блока управления, вторым входом которо- го является вход записи регистра,

второй выход которого соединен с пер- Bbw входом третьего элемента И,выход которого подключен к второму ; входу второго элемента ИЛИ, а второй вход соединен с третьим выходом регистра и является десятым пыходом блока управления, двенадцатым ньгхо- дом которого является прямой выход второго триггера, единичньш вход которого соединен с выходом третьего элемента ИЛИ, а инверсный выход подключен к первому входу четвертого элемента И, второй вход которого соединен с вькодом третьего формирователя импульсов, а выход является девятым и четырнадцатым выходами блока управления, седьмой и тринадцатый выходы которого объединены с нулевым

входом второго триггера, с вторым входом первого элемента И, с входом записи первого триггера и подключены к выходу переполнения счетчика импульсов, выход младших разрядов которого подключен к входу третьего формирователя импульсов и является третьим выходом блока управления, восьмыми выходами которого являются соответствующие выходы старших разрядов счетчика импульсов, счетный вход которого подключен к выходу генератора импульсов и является шестым выходом блока управления, третьими входами которого являются информационные входы регистра.

Фиг.З

Фиг. 5

Фиг.

9

ш

8

22

I.. I I

t .1 .

±

J

65I M M 1

I I I I I I

p 111 H in

til

й7 II n n

JL

68 mmm

69

m

u

Я

л

л

и

in

пп

Ч-Л

д

Редактор И.Горная

Заказ 1465/55

Составитель О.Спиридонов

Техред А.Кравчук

Корректор

Тираж 902Подписное

ВНИИЩ1 Государственного комитета СССР по делам изобретений и открытий 1.13035, Москва, Ж-35, Раутская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. HpoeKTHvqH, 4

M I I ( I

Jl Hi

n n n

n n.

II

1 r-

я

я

я

я

гп

.т.

I I

JL

Корректор М.Демчик

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1983 |

|

SU1098006A1 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1983 |

|

SU1109848A1 |

| Устройство для управления намоточным станком | 1989 |

|

SU1817061A1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1990 |

|

SU1707723A1 |

| Функциональный преобразователь | 1980 |

|

SU894748A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Вычислительное устройство | 1981 |

|

SU1001114A1 |

| Аналого-цифровой преобразователь знакопеременных сигналов | 1987 |

|

SU1483641A1 |

Изобретение относится к импульсной технике, в частности к преобразователям напряжения в цифровой код с промежуточным преобразованием напряжения в частоту импульсов, и может быть использовано в прецизионных устройствах сбора аналоговой информации систем контроля и управления технологическими процессами. В устройство, содержащее клемШ Htit

| Тычико К.К | |||

| Преобразователи напряжения в частоту | |||

| - М.: Энергия, 1972, с | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Прянишников в.А | |||

| Интегрирующие цифровые вольтметры постоянного тока | |||

| - Л.: Энергия, 1976, с | |||

| Зубчатое колесо со сменным зубчатым ободом | 1922 |

|

SU43A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-04-23—Публикация

1985-07-01—Подача