I

изобретение относится к радио- . технике и может быть использовано передающей аппаратуре радиолинии телеграфной связи.

Целью изобретения является уменьшение уровня внеполосных составляющих при произвольной скорост манипуляции.

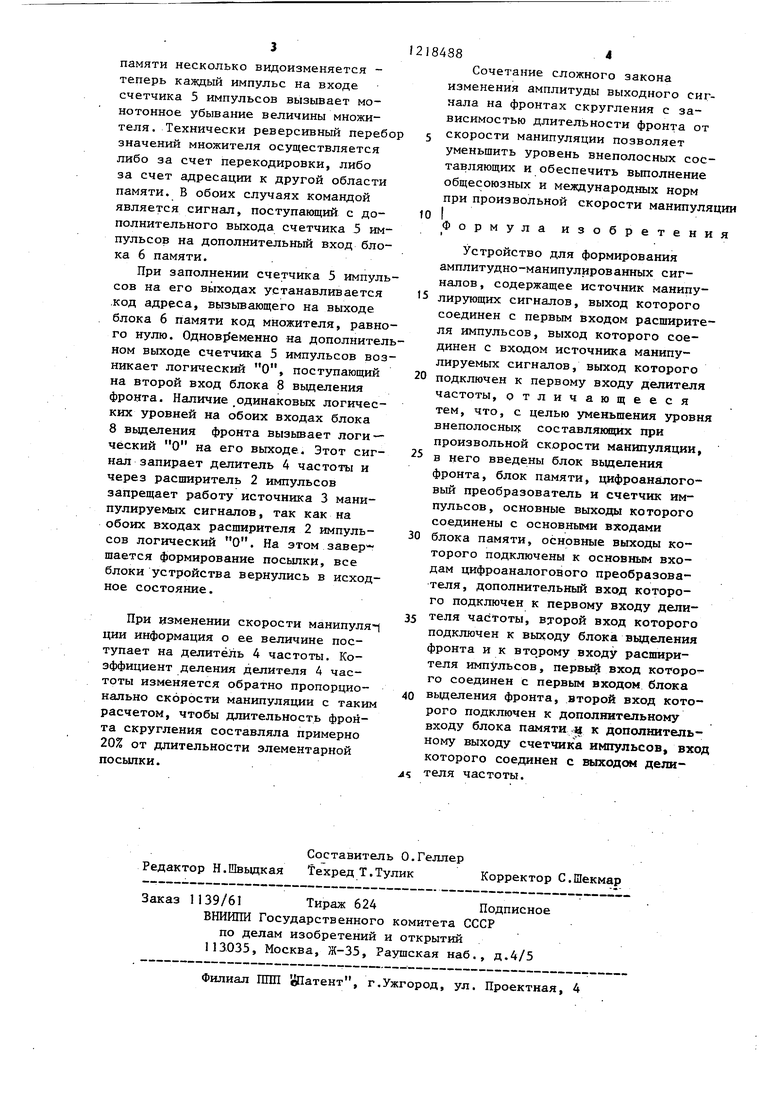

На чертеже изображена структурная электрическая схема предлагаемого устройства.

Устройство для формирования амплитудно-манипулированных сигналов содержит источник 1 манипулирущих сигналов, расширитель 2 импуль сов, источник 3 манипулируемых сигналов, делитель 4 частоты, счетчик 5 импульсов, блок 6 памяти, цифроаналоговый преобразовател 7, блок 8 вьщеления фронта.

Устройство работает следующим образом. ; .

Исходное состояние - установившаяся пауза. В этом случае на выходе источника 1 манипулирующих сигналов и на дополнительном вы- хоце. счетчика 5 импульсов - логические О, вызывающие логический О на выходе блока 8 выделения фронта. Этот сигнал запирает делитель 4 частоты и одновременно поступает на второй вход расширителя 2 импульсов, обеспечивая на выходе последнего сигнал, запирающий источник 3 манипулируемых сигналов .

Сигнал с выхода источника 1 манипулирующих сигналов поступает через расширитель 2 импульсов на управляющий вход источника 3 манипулируемых сигналов и разрешает работу последнего. Одновременно сигнал (логическая I) поступает на первый вход блока 8 вьщеления фронта 3 этот момент на втором входе блока 8, соединенном с дополнительным выходом счетчика 5 импульсов - логический О, поэтому на выходе блока 8 вьщеления фронта возникает логическая 1, разрешающая работу делителя 4 частоты. Коэффициент деления N делителя 4 частота обратно пропорционален скорости манипуляции. Делитель 4 час готы пропускает каждый N -и импульс с выхода источника 3 манипулируемых сигналов на вход счетчика 5 импульсов.Этот импульс, изменяет состояние счетчи18488

ка 5 импульсов, т.е. изменяет код адреса на входах блока 6 памяти. Соответственно изменяется : код множителя, поступающий с выхо5 да блока 6 памяти на вход цифроана -- логового преобразователя ЦАП 7.

В паузе, до сигнала манипуляции, множитель бьш равен нулю. С каждым импульсом на входе счетчика 5 импуль 0 сов множитель монотонно возрастает по выбранному закону (линейному, синусному, sin - sin-му или еще более сложному). На,сигнальный дополнительный .зход ГЩ1 7 поступают

15 немодулированные колебания с выхода источника 3 манипулируемых сигналов . Амплитуда этих колебаний на выходе ЦАП 7 определяется кодом множителя на выходе блока 6 памяти.

20 Выбором сложного закона изменения множителя (в пределах от О до П обеспечивается выполнение общесоюзных и международных норм на. спектр внеполосных излучений.

25 При заполнении счетчика 5 импульсов на его выходах устанавливается код адреса, вызывающего на входе блока 6 памяти код множителя, равного 1. Одновременно на дополни2 тельном выходе счетчика 5 импуль-, сов, соединенном с вторым входом . блока 8 вьщеления фронта, возникает логическая 1. Логические уровни на обоих входах блока 8 вьщеления фронта одинаковы, поэтому на его

выходе возникает логический О, i запирающий делитель 4 частоты. Формирование переднего фронта посьшки на этом заканчивается. На выходе ЦАП 7 устанавливается максимальная амплитуда сигнала.

По окончании посьшки от источника 1 манипулирующих сигналов на первый вход блока 8 вьщеления фронта поступает логический О. В этот момент на второй вход блока 8 вьщеления фронта с дополнительного : выхода счетчика 5 поступает логическая I, поэтому на выходе блока 8 вьщеления фронта возникает логичес0 кая 1, которая проходя через расширитель 2 импульсов, продлевает разрешение работы источника 3 манипулируемых сигналов и вновь разрешает работу делителя 4 частоты. Режим

5 работы делителя 4 частоты и счетчика 5 импульсов такой же, как и во время формирования переднего фронта посьшки, а режим работы блока 6

40

5

памяти несколько видоизменяется - теперь каждый импульс на входе счетчика 5 импульсов вызывает монотонное убывание величины множителя. Технически реверсивный перебо значений множителя осуществляется либо за счет перекодировки, либо за счет адресации к другой области памяти. В обоих случаях командой является сигнал, поступающий с дополнительного выхода счетчика 5 импульсов на дополнительный вход блока 6 памяти.

При заполнении счетчика 5 импульсов на его выходах устанавливается .код адреса, вызьшающего на выходе блока 6 памяти код множителя, равного нулю. Одновг еменно на дополнителном выходе счетчика 5 импульсов возникает логический О, поступающий на второй вход блока 8 вьщеления фронта. Наличие одинаковых логических уровней на обоих входах блока 8 вьщеления фронта вызьюает логический О на его выходе. Этот сигнал запирает делитель 4 частоты и через расширитель 2 импульсов запрещает работу источника 3 мани- пулируемых сигналов, так как на обоих входах расширителя 2 импульсов логический О. На этом завершается формирование посылки, все блоки устройства вернулись в исходное состояние.

При изменении скорости манипуляч ции информация о ее величине поступает на делитель 4 частоты. Ко- зффициент деления делителя 4 частоты изменяется обратно пропорционально скорости манипуляции с таким расчетом, чтобы длительность фронта скругления составляла примерно 20% от длительности элементарной посылки.

Составитель О.Геллер Редактор Н.Швьщкая Техред Т.Тулик Корректор С.Шекмар

Заказ 1139/61 Тираж 624Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ШШ (вПатент, г.Ужгород, ул. Проектная, 4

2184S8

Сочетание сложного закона изменения амплитуды выходного сигнала на фронтах скругления с зависимостью длительности фронта от 5 скорости манипуляции позволяет уменьшить уровень внеполосных составляющих и обеспечить выполнение общесоюзных и международных норм при произвольной скорости манипуляции

10

Формула изобретения

Устройство для формирования амплитудно-манипулированных сигналов, содержащее источник манипулирующих сигналов, выход которого соединен с первым входом расширителя импульсов, выход которого соединен с входом источника манипу- лируемых сигналов, выход которого

подключен к первому входу делителя частоты, отличающееся тем, что, с целью уменьшения уровня внеполоснызс составлякицих при произвольной скорости манипуляции, в него введены блок вьщеления фронта, блок памяти, цифроаналого- вый преобразователь и счетчик импульсов, основные выходы которого соединены с основными входами блока памяти, основные выходы которого подключены к основным входам цифроаналогового преобразователя, дополнительный вход которого подключен к первому входу делителя частоты, второй вход которого подключен к выходу блока выделения фронта и к второму входу расширителя импульсов, первый вход которого соединен с первым входом блока вьщеления фронта, второй вход которого подключен к дополнительному входу блока памяти,« к дополнительному выходу счетчика импульсов, вход которого соединен с выходом делителя частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования сигналов амплитудной манипуляции | 1980 |

|

SU970721A1 |

| Устройство формирования фазоманипулированных сигналов | 1987 |

|

SU1548862A1 |

| Фазовый манипулятор | 1983 |

|

SU1095440A1 |

| Устройство формирования фазоманипулированного сигнала | 1973 |

|

SU492045A1 |

| Фазовый модулятор | 1986 |

|

SU1388974A2 |

| Устройство частотной манипуляции радиосигнала | 1972 |

|

SU456370A1 |

| Устройство формирования амплитудноманипулированных сигналов | 1978 |

|

SU720674A1 |

| Цифровой частотный дискриминатор | 1982 |

|

SU1037422A1 |

| Устройство формирования сигналовС фАзОВОй МАНипуляциЕй | 1979 |

|

SU843161A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

Изобретение относится к радиотехнике и может использоваться в передающей аппаратуре радиолинии телеграфной связи. Уменьшаетсяуровень внеполосных составлякяцих при произвольной скорости манипуляции. Сигнал с выхода источника 1 манипулирующих сигналов поступает на блок 8 выделения фронта БВФ и через расширитель 2 импульсов - на источник 3 манипулируемых сигналов (ИМС) для его запуска. Импульсы с ИМС 3 поступают на делитель 4 частоты (ДЧ) и через цифроаналоговый преобразователь 7 - на выход. ДЧ пропускает на счетчик 5 импульсов каждый N -и импульс. Счетчик 5 импульсов формирует код адреса для блока 6 памяти. Код множителя с блока 6 памяти поступает на цИфроаиалоговый преобразователь 7 для изменения амплитуды импульсов, поступающих с ИМС 3. Напряжение с дополнительного выхода счетчика 5 импульсов подается на другой вход БВФ 8. Сигнал с его выхода является управляющим для ДЧ 4 и расширителя 2 импульсов. Коэффициент деления ДЧ 4 изменяется в зависимости от скорости манипуляции. I нл.

| Устройство формирования амплитудноманипулированных сигналов | 1978 |

|

SU720674A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1986-03-15—Публикация

1984-10-12—Подача