10

25

Изобретение, относится к цифровой вычислительной технике и может быть использовано для вычисления спектра по алгоритму быстрого преобразования Фурье.5

Цель изобретения - расширение области применения за счет обработки последовательностей с переменным шагом скольжения.

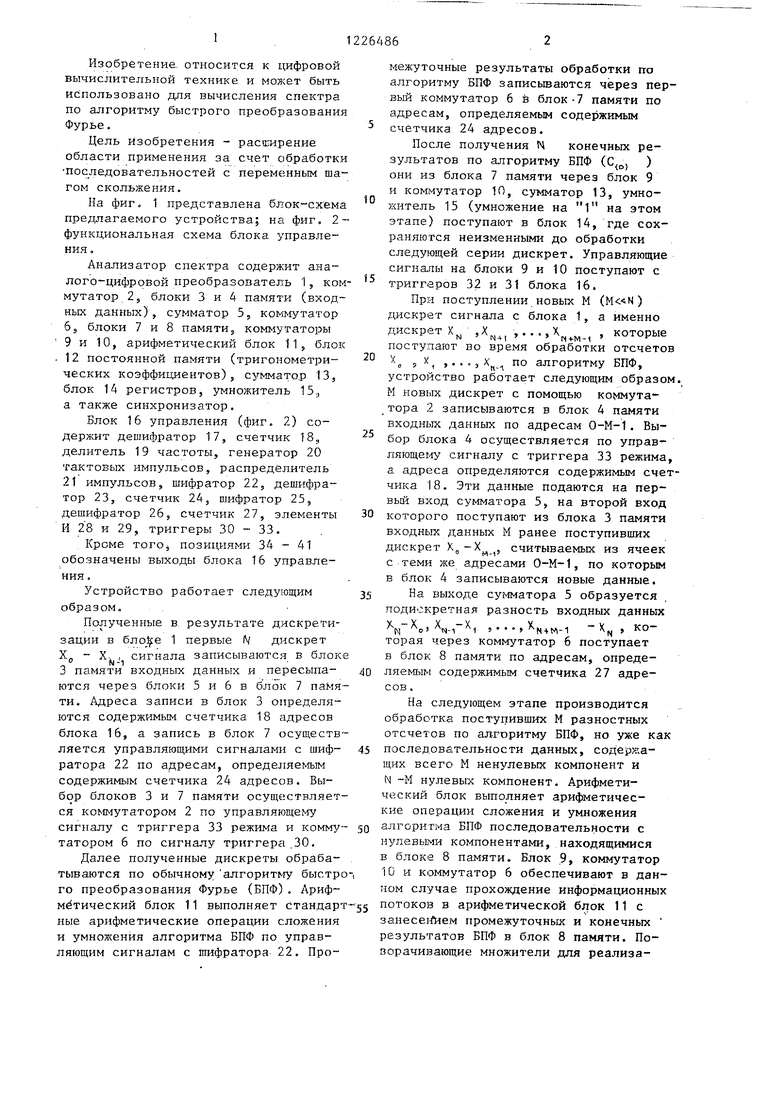

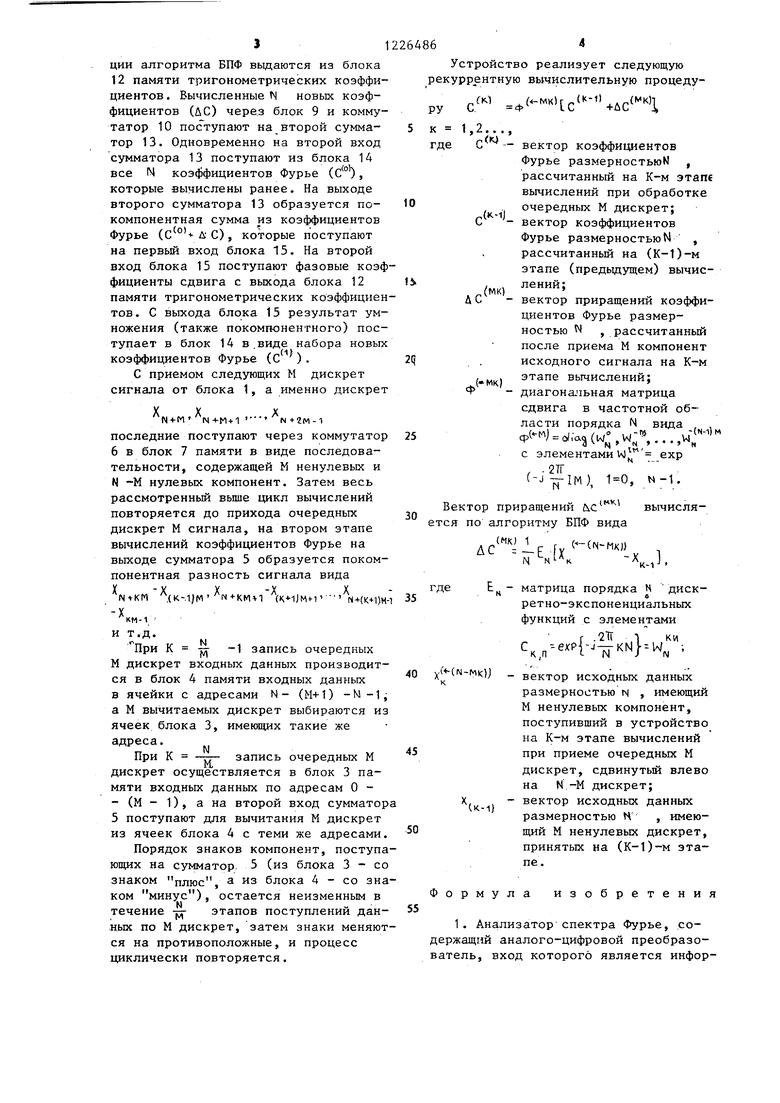

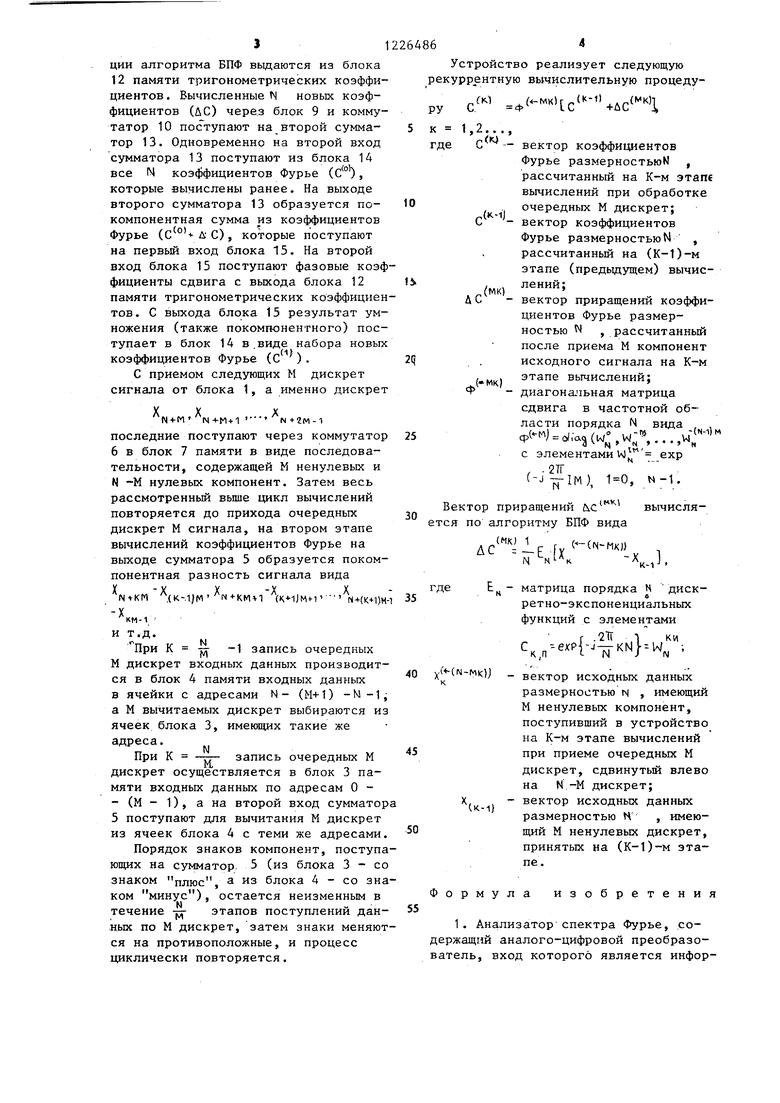

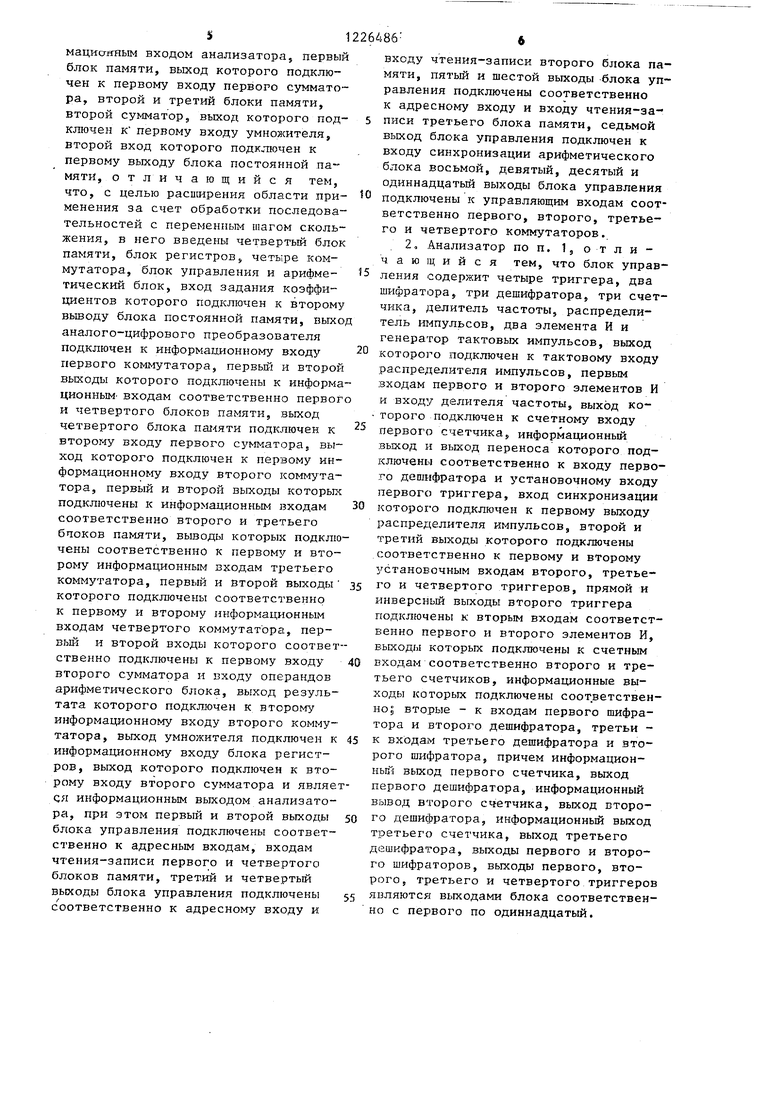

На фиг, 1 представлена блок-схема предлагаемого устройства; на фиг, 2- функциональная схема блока управления ,

Анализатор спектра содержит аналого-цифровой преобразователь 1j ком- мутатор 2, блоки 3 и 4 памяти (входных данных), сумматор 5, коммутатор 6j блоки 7 и 8 памяти, коммутаторы 9 и 10, арифметический блок 11, блок 12 постоянной памяти (тригонометри- 20 ческих коэффициентов)5 сумматор 13, блок 14 регистров, ут ножитель 15, а также синхронизатор.

Блок 16 управления (фиг, 2) содержит дешифратор 17, счетчик 18., делитель 19 частоты, генератор 20 тактовых импульсов, распределитель 21 импульсов, шифратор 22, дешифратор 23, счетчик 24s шифратор 25, дешифратор 26, счетчик 27, элементы 30 И 28 и 29, триггеры 30 - 33,

Кроме того, позициями 34-41 обозначены выходы блока 16 управления .

Устройство работает следующим 35 образом.

Полученные в. результате дискретизации в 1 первые IV дискрет р - X. , сигнала записываются в блоке 3 памяти входных данных и пересыпа- 40 тся через блоки 5 и 6 в блок 7 паМя- ти. Адреса записи в блок 3 определятся содержимым счетчика 18 адресов блока 16, а запись в блок 7 осуществяется управляющими сигналами с шиф- 45 ратора 22 по адресам, определяемым содержимым счетчика 24 адресов. Выбор блоков 3 и 7 памяти осуществляется коммутатором 2 по управляющему сигналу с триггера 33 режима и комму- до татором 6 по сигналу триггера.30.

Далее полученные дискреты обрабатываются по обычному алгоритьгу быстро го преобразования Фурье (БПФ). Арифметический блок 11 выполняет стандарт- 55 ные арифметические операции сложения и умножения алгоритма БПФ по управяющим сигналам с шифратора 22. Про

межуточные результаты обработки по алгоритму БПФ записьшаются через первый коммутатор 6 в блок-7 памяти по адресам, определяемым содержимым счетчика 24 адресов.

После получения N конечных результатов по алгоритму БПФ (С, ) они из блока 7 памяти через блок 9 и коммутатор 10, сумматор 13, умно- хштель 15 (умножение на 1 на этом этапе) поступают в блок 14, где сохраняются неизменными до обработки следующей серии дискрет. Управляющие сигнааы на блоки 9 и 10 поступают с триггеров 32 и 31 блока 16.

При поступлении новых М (M«N ) дискрет сигнала с блока 1, а именно дискрет Х ,Х, ,...,Х , которые поступают во время обработки отсчетов о J 3 . по алгоритму БПФ, устройство работает следующим образом. М новых дискрет с помощью кo мyтa- тора 2 записываются в блок 4 памяти входных данных по адресам О-М-1. Выбор блока 4 осуществляется по управ- ляюще1 у сигналу с триггера 33 режима, а адреса определяются содержимым счетчика 18. Эти данные подаются на первый вход сумматора 5, на второй вход которого поступают из блока 3 памяти входных данных М ранее поступивших дискрет X,-X.j считываемых из ячеек с теми же адресами О-М-1, по которым в блок 4 записываются новые данные.

На выходе сумматора 5 образуется подискретная разность входных данных

о 5 - N4M-i ° торая через коммутатор 6 поступает

в блок 8 памяти по адресам, определяемым содержимым счетчика 27 адресов .

На следующем этапе производится обработка поступивших М разностных отсчетов по ал-горитму БПФ, но уже как последовательности данных, содержащих всего М ненулевых компонент и N -М нулевых компонент. Арифметический блок выполняет арифметические операции сложения и умножения алгоритма БПФ последовательности с иулевьичи компонентами,.находящимися в блоке 8 памяти. Блок 9, коммутатор 10 и коммутатор 6 обеспечивают в данном случае прохождение информационных потоков в арифметической блок 11 с занесе1Л1ем промежуточных и конечных результатов БПФ в блок 8 памяти. Поворачивающие множители для реализации алгоритма БПФ выдаются из блока 12 памяти тригонометрических коэффициентов . Вычисленные N новых коэффициентов (ДС) через блок 9 и коммутатор 10 поступают на второй сумматор 13. Одновременно на второй вход сумматора 13 поступают из блока 14 все коэффициентов Фурье (С°0, которые вычислены ранее. На выходе второго сумматора 13 образуется покомпонентная сумма из коэффициентов Фурье (с ° +Д:С), которые поступают на первьм вход блока 15, На второй вход блока 15 поступают фазовые коэффициенты сдвига с выхода блока 12 памяти тригонометрических коэффициентов. С выхода блока 15 результат умножения (также покомпонентного) поступает в блок 14 в .виде набора новых коэффициентов Фурье (С ).

С приемом следующих М дискрет сигнала от блока 1, а именно дискрет

XX X

N-t-M N-t-M+1 N+2M-1

последние поступают через коммутатор 6 в блок 7 памяти в виде последовательности, содержащей М ненулевых и N -М нулевых компонент. Затем весь рассмотренный выше цикл вычислений повторяется до прихода очередных дискрет М сигнала, на втором этапе вычислений коэффициентов Фурье на выходе сумматора 5 образуется покомпонентная разность сигнала вида

X -X

N+KM (К-.1)М

-X

КМ-1

N

При К -j; -1 запись очередных

М дискрет входных данных производится в блок 4 памяти входных данных в ячейки с адресами N- (M+l) -M-1j а М вычитаемых дискрет выбираются из ячеек блока 3, имеющих такие же адреса.

При К -:j7 запись очередных М

.уУ N -KM4l (K -IJMM - N4{K+i)M-l

М.

дискрет осуществляется в блок 3 памяти входных данных по адресам О - - (М - 1), а на второй вход сумматора 5 поступают для вычитания М дискрет из ячеек блока 4 с теми же адресами.

Порядок знаков компонент, поступающих на сумматор 5 (из блока 3 - со знаком плюс, а из блока 4 - со знаком минус), остается неизменным в течение - этапов поступлений данных по М дискрет, затем знаки меняются на противоположные, и процесс циклически повторяется.

Устройство реализует следующую рекуррентную вычислительную процеду М ф(-мк)с - ЧдС )

РУ к

где

1,2..

М

.(K-1J

ДС

(мк)

вектор коэффициентов Фурье размерностьюМ , рассчитанный на К-м этапе вычислений при обработке очередных М дискрет; вектор коэффициентов Фурье размерностьюN , рассчитанный на (К-1)-м этапе (предыдущем) вычислений;

вектор приращений коэффициентов Фурье размерностью N

рассчитанный

мк)

после приема М компонент исходного сигнала на К-м этапе вычислений; диагональная матрица сдвига в частотной области порядка N вида

{N-l) М

N

jtctv- in .

фМ ,-а(Ы,М;%..., fc« (

11Л

С элементами W exp

, .2ТГ . (-J TflM), , N-1.

Вектор приращений 6iC

(«Kl

вычисляется no алгоритму БПФ вида .(МК) 1 . (-(N-MW)

AC

С I V - .

,.

E - матрица порядка N дискретно-экспоненциальныхфункций с элементами

г .211 1 ки кп- П-Т КМ}-- ;

(N-Mlc)J к

(К-1)

вектор исходных данных размерностью N , имеющий М ненулевых компонент, поступивший в устройство на К-м этапе вычислений при приеме очередных М дискрет, сдвинутый влево на N -М дискрет; вектор исходных данных размерностью N , имеющий М ненулевых дискрет, принятых на (К-1)-м этапе.

Формула изобретения

1. Анализатор спектра Фурье, содержащий аналого-цифровой преобразователь, вход которого является информацистнным входом анализатора, первый блок памяти, выход которого подключен к первому входу первого сумматора, второй и третий блоки памяти, второй сумматор, вькод которого подключен к первому входу умножителя, второй вход которого подключен к первому выходу блока постоянной памяти, отличающийся тем, что, с целью расиирения области применения за счет обработки последовательностей с переменным шагом скольжения, в него введены четвертый блок памяти, блок регистров, четыре ком

мутатора, блок управления и арифметический блок, вход задания коэффициентов которого подключен к второму вьшоду блока постоянной памяти, выхо аналого-цифрового преобразователя подключен к информацион1 ому входу первого коммутатора, первый и второй выходы которого подключены к информационным- входам соответственно первог и четвертого блоков памяти, выход четвертого блока памяти подключен к второму входу первого сумматора, выход которого подключен к первому информационному входу второго коммутатора, первый и второй выходы которьк подключены к информационным входам соответственно второго и третьего бггоков памяти, выводы которых подключены соответственно к первому и второму информационным входам третьего коммутатора, первый и второй выходы которого подключены соответственно к первому и второму информационным входам четвертого коммутатора, первый и второй входы которого соответственно подключены к первому входу второго сумматора и входу операндов арифметического блока, выход результата которого подключен к второму информационному входу второго коммутатора, выход умножителя подключен к информационному входу блока регистров, выход которого подключен к второму входу второго сумматора и являеся информационным выходом анализатора, при этом первый и второй выходы блока управления подключены соответственно к адресным входам, входам чтения-записи первого и четвертого блоков памяти, третий и четвертый выходы блока управления подключены соответственно к адресному входу и

O

5

5

0

0 5 0

5

5

входу чтения-записи второго блока памяти, пятый и шестой выходы блока управления подключены соответственно к адресному входу и входу чтения-записи третьего блока памяти, седьмой выход блока управления подключен к входу синхронизации арифметического блока восьмой, девятый, десятый и одиннадцатый выходы блока управления подключены к управляющим входам соответственно первого, второго, третьего и четвертого коммутаторов.

2, Анализатор по п. 1, отличающийся тем, что блок управления содержит четыре триггера, два шифратора, три дешифратора, три счетчика, делитель частоты, распределитель импульсов, два элемента И и генератор тактовых импульсов, выход которого подключен к тактовому входу распределителя импульсов, первым входам первого и второго элементов И и входу делителя частоты, выход ко- торого подключен к счетному входу первого счетчика, информационный выход и выход переноса которого подключены соответственно к входу первого дешифратора и установочному входу первого триггера, вход синхронизации которог о подключен к первому вьпсоду распределителя импульсов, второй и третий выходы которого подключены соответственно к первому и второму установочным входам второго, третьего и четвертого триггеров, прямой и инверсный выходы второго триггера подключены к вторым входам соответственно первого и второго элементов И, выходы которых подключены к счетным входам соответственно второго и третьего счетчиков, информационные выходы которых подключены соответственно; вторые - к входам первого шифратора и второго дешифратора, третьи - к входам третьего дешифратора и второго шифратора, причем информацион- ньй выход первого счетчика, выход первого дешифратора, информационный вывод второго счетчика, выход второго дешифратора, информационный выход третьего счетчика, выход третьего дешифратора, выходы первого и второго шифраторов, выходы первого, второго, третьего и четвертого триггеров являются выходами блока соответственно с первого по одиннадцатый.

SK

JTl

L.

6 .

/a

/j

flfrM

3f

jffj

7 3g1j 3g}j5lw /l

T:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для быстрого преобразования Фурье-последовательности с нулевыми элементами | 1981 |

|

SU1005070A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1337904A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для выполнения быстрого преобразования Фурье | 1987 |

|

SU1411777A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1983 |

|

SU1124323A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1304034A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для вычисления спектра по алгоритму быстрого преобразования Фурье. Цель изобретения - расширение области применения анализатора за счет обработки последовательностей с переменным шагом скольжения. Это достигается введением в анализатор блока памяти, блока регистров, четырех коммутаторов, блока управления и арифметического блока с соответствующими функциональными связями между ними и известными блоками анализатора. 1 з.п. ф-лы, 2 ил. ND tsD 05 оо 05

да 1 w . 1 /

Редактор 0. Бугир

Заказ 2136/50Тираж 671Подписное

ВНИИ1Ш Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб ., д..4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,

Составитель A. Баранов

Техред Л.Олейник Корректор О. Луговая

| Устройство для измерения коэффициентов фурье | 1973 |

|

SU446073A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дифференцирующе-сглаживающее устройство | 1976 |

|

SU560236A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-23—Публикация

1984-10-09—Подача