Изобретение относится к вычислительной технике и радиотехнике и предназначено для применения в анализаторах спектра и устройствах цифровой обработки сигналов.

Известны устройства, выполняющие операцию дискретного преобразования Фурье (ДПФ) по алгоритмам быстрого преобразования Фурье - БПФ.

Известно арифметическое устройство для выполнения ДПФ - прототип, состоящее из интерполяторов, сумматоров, элементов НЕ, мультиплексоров и счетного триггера, которое выполняет базовую операцию ДПФ путем вычисления методом интерполяции промежуточных спектральных отсчетов.

Основной недостаток прототипа - сравнительно низкая практически достижимая точность вычислений при больших размерах преобразования. Этот недостаток обусловлен малой сходимостью интерполяционного полинома, на основе которого находятся сначала промежуточные значения исходного спектра, а затем и искомые спектральные составляющие. Следствием малой сходимости является то, что для достижения приемлемой точности нахождения промежуточных спектральных отсчетов методом интерполяции при больших размерах преобразования требуется использовать значительное количество весовых коэффициентов, что усложняет устройство.

Другой недостаток прототипа, ведущий к снижению точности преобразования, - это пренебрежение краевыми эффектами при нахождении промежуточных значений спектра на его концах, вызванных неизбежным усечением числа отсчетов, участвующих в вычислениях.

Можно указать также на недостатки прототипа, связанные с тем, что он, предназначенный для работы в анализаторах спектра, выполняющих преобразование Фурье в целом, не учитывает специфики отдельных этапов преобразования, в частности необходимости корректировки количества весовых коэффициентов, их значений, модификации сигналов синхронизации. Кроме того, при реализации анализатора спектра в целом встают вопросы управления процессом преобразования на разных его этапах, взаимодействия со схемами оперативной памяти, проблемы с изменением разрядности чисел, вопросы ввода исходной информации и вывода полученных спектральных отсчетов и т.д.

Целью изобретения является повышение точности преобразования.

Цель достигается за счет того, что в устройство введены мультиплексоры, блок формирования приращения порядка чисел, блок управления, блок оперативной памяти, вход начальной установки, второй тактовый вход, второй вход синхронизации, вход признака текущего изменения размера выходного ДПФ. вход порядка входных чисел, вход признака переключения прямого и обратного преобразования Фурье, вход установки размера ДПФ на выходе анализатора спектра, вход установки размера ДПФ на данном этапе, вход установки режима конвейерной или однопроцессорной обработки сигнала, вход установки режима одновременной или последовательной обработки сигнала.

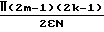

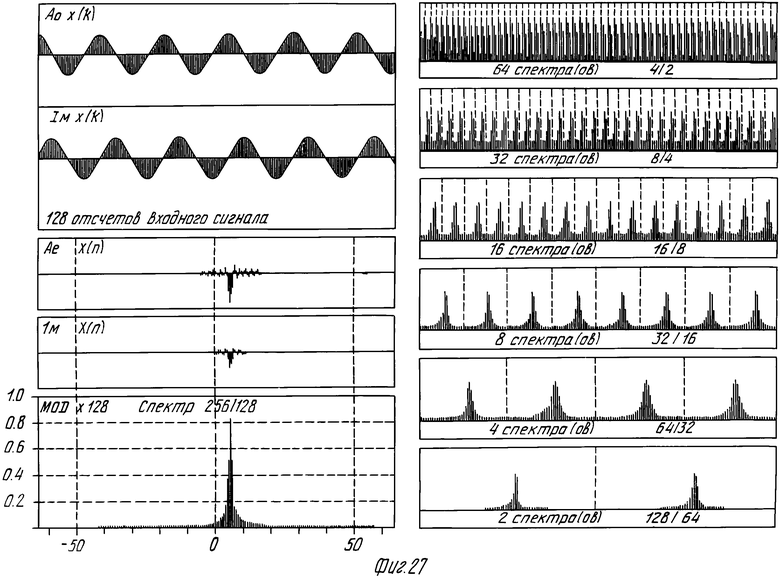

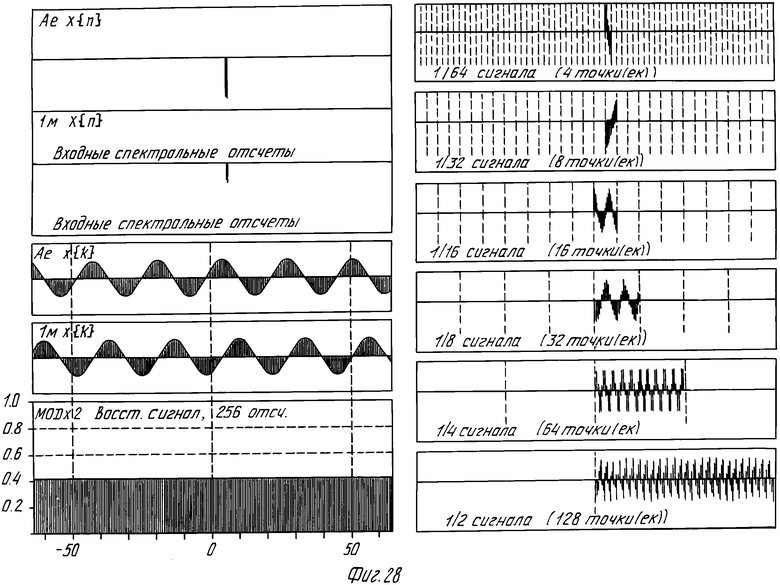

На фиг.1 представлена общая функциональная схема арифметического устройства для выполнения ДПФ; на фиг.2-23 - функциональные схемы элементов общей схемы; на фиг.24-26 - примеры использования устройства в некоторых вычислителях ДПФ; на фиг.27 - графики, иллюстрирующие прямое БПФ; на фиг.28 - графики, иллюстрирующие обратное БПФ.

Общая функциональная схема арифметического устройства содержит многоразрядные мультиплексоры 1-4 с двух направлений (мультиплексоры с векторными входами и выходами), мультиплексор 5 с двух направлений, четыре интерполятора 6-9, блок 10 формирования приращения порядка чисел, блок 11 когерентных сумматоров, блок 12 управления, блок 13 оперативной памяти. Первым - шестнадцатым входами арифметического устройства являются, соответственно информационные (векторные) входы 21-24 (квадратурные отсчеты первого входного спектра или нечетные отсчеты сигнала и квадратурные отсчеты второго входного спектра или четные отсчеты сигнала), вход (векторный) 20 порядка входных чисел, вход (векторный) 27 установки размера БПФ, вход (векторный) 28 установки размера ДПФ на данном этапе, вход 25 переключения прямого и обратного преобразования Фурье, первый вход 19 синхронизации, второй вход 17 синхронизации, вход 29 установки режима конвейерной или однопроцессорной обработки сигнала (KON), вход 18 признака текущего изменения размера выходного ДПФ, вход 30 установки режима одновременной или последовательной обработки, вход 15 начальной установки, первый тактовый вход 26, второй тактовый вход 16, первым - двенадцатым выходами устройства 14 являются соответственно выходы (векторные) 38, 40, 39 и 41 спектра при конвейерной обработке (38, 40 - квадратурные выходы первой половины выходных спектральных отсчетов или нечетных частичных спектров и 39, 41 - квадратурные выходы второй половины выходных спектральных отсчетов или четных частичных спектров), выход (векторный) 37 порядка выходных чисел, выходы (векторные) 31-34 спектра при однопроцессорной обработке (31, 32 - квадратурные выходы четных выходных спектральных отсчетов И 33, 34 - квадратурные выходы нечетных спектральных отсчетов), первый и второй выходы 35 и 36 синхронизации, и выход 389 окончания ДПФ в однопроцессорном вычислителе.

Первый вход мультиплексора 1 соединен с первым выходом 38 блока 13, второй вход - с входом 21, а вход управления - с входом 29. Первый вход мультиплексора 2 соединен с третьим выходом 40 блока 13, второй вход - с входом 22, а вход управления - с входом 29. Первый вход мультиплексора 3 соединен с вторым выходом 39 блока 13, второй вход - с входом 23, а вход управления - с входом 29. Первый вход мультиплексора 4 соединен с четвертым выходом 41 блока 13, второй вход - с входом 24, а вход управления - с входом 29. Первый вход мультиплексора 5 соединен с входом 19, второй вход - с восьмым выходом 35 блока 12, а вход управления - с входом 29.

Первые векторные информационные входы интерполяторов 6-9 подсоединены к векторным выходам соответственно мультиплексоров 1-4, вторые векторные входы управления номера текущего этапа преобразования Фурье соединены вместе и подключены к первому выходу блока 12 управления, третьи входы (синхронизации) этих интерполяторов соединены вместе и подключены к выходу мультиплексора 5, четвертые тактовые входы всех интерполяторов соединены вместе и подключены к (пятому) выходу тактовых импульсов блока 11 когерентных сумматоров. Первый, третий, пятый и седьмой векторные входы блока когерентных сумматоров подсоединены к первым выходам (основных) спектральных отсчетов соответственно интерполяторов 1-4, второй, четвертый, шестой и восьмой входы блока когерентных сумматоров подключены к вторым выходам (промежуточных) отсчетов этих интерполяторов, управляющий (векторный девятый) вход номера текущего этапа преобразования Фурье блока когерентных сумматоров подключен к первому выходу блока 12 управления, вход установки (десятый) подключен к входу 25, вход синхронизации (одиннадцатый) - к выходу мультиплексора 5, вход управления (двенадцатый) режимами записи исходной информации и считывания готового спектра или преобразования Фурье - к седьмому выходу блока 12, тактовый вход (тринадцатый) - к входу 26.

Вход (первый) начальной установки блока 10 формирования приращения порядка чисел соединен с входом 15, вход (второй) установки режима конвейерной или однопроцессорной обработки - с входом 29, вход (третий) признака текущего изменения размера ДПФ - с входом 18, вход (четвертый, векторный) порядка входных чисел - с входом 20, вход (пятый) признака переполнения - с одноименным выходом (девятый) блока 13, а входы признака считывания очередного частичного спектра промежуточного преобразования Фурье (шестой), признака окончания ДПФ в однопроцессорном вычислителе (седьмой), начала обработки присоединяемого частичного спектра при удвоении размера преобразования Фурье на данном этапе (восьмой), первого и второго признака начала каждого этапа преобразования Фурье (девятый и десятый), а также признака считывания приращения порядка чисел выходного частичного спектра (одиннадцатый) соединены соответственно с девятым - четырнадцатым выходами блока 12, тактовый (двенадцатый) вход соединен с тактовым входом 26. Первый и второй (векторные) выходы блока 10 соединены соответственно с входами (восьмой и девятый) первого и второго признака управления сдвигом блока 13, третий выход (векторный) подключен к выходу 37.

Вход (первый векторный) установки размера ДПФ на выходе анализатора спектра блока 12 управления подключен к входу 27, вход (второй векторный) установки размера ДПФ на данном этапе - к входу 28, вход (третий) установки режима конвейерной или однопроцессорной обработки Фурье соединен с входом 29, вход (четвертый) установки режима одновременной или последовательной обработки - с входом 30, вход (пятый) начальной установки - с одноименным входом 15 устройства, первый тактовый вход (шестой) - с одноименным входом 26 устройства, второй тактовый вход (седьмой) - с входом 16 устройства, вход (восьмой) сигнала сопровождения режима конвейерной обработки - с входом 17 и вход (девятый) признака текущего изменения размера ДПФ - с входом 18.

Первый и второй информационные входы (векторные) блока 13 оперативной памяти соединены с входами 21 и 22, третий - шестой информационные входы (векторные) - с первым - четвертым выходами блока 11 когерентных сумматоров, входы управления считыванием нечетных и четных частичных спектров, управления считыванием основных и промежуточных отсчетов спектра, управления режимами запись-считывания, управления режимами записи исходной информации и считывания готового спектра или преобразования Фурье (седьмой, десятый, тринадцатый и четырнадцатый) соединены соответственно с четвертым - седьмым выходами блока 12, первый и второй входы признака управления сдвигом (восьмой и девятый векторные) соединены соответственно с первым и вторым выходами блока 10, первый и второй адресные входы (одиннадцатый и двенадцатый векторные) соединены соответственно с вторым и третьим выходами блока 12, а тактовый вход (пятнадцатый) соединен с входом 26.

Первый - четвертый и шестой - девятый векторные выходы устройства 14 подключены соответственно к первому, третьему, второму и четвертому - девятому выходам блока 13 оперативной памяти (выходы 38, 40, 39, 41 и 31-34 соответственно), пятый векторный выход устройства 14 подключен к третьему выходу блока 10 формирования приращения порядка чисел, а десятый - двенадцатый выходы устройства 14 подключены соответственно к восьмому - десятому выходам блока 12 управления.

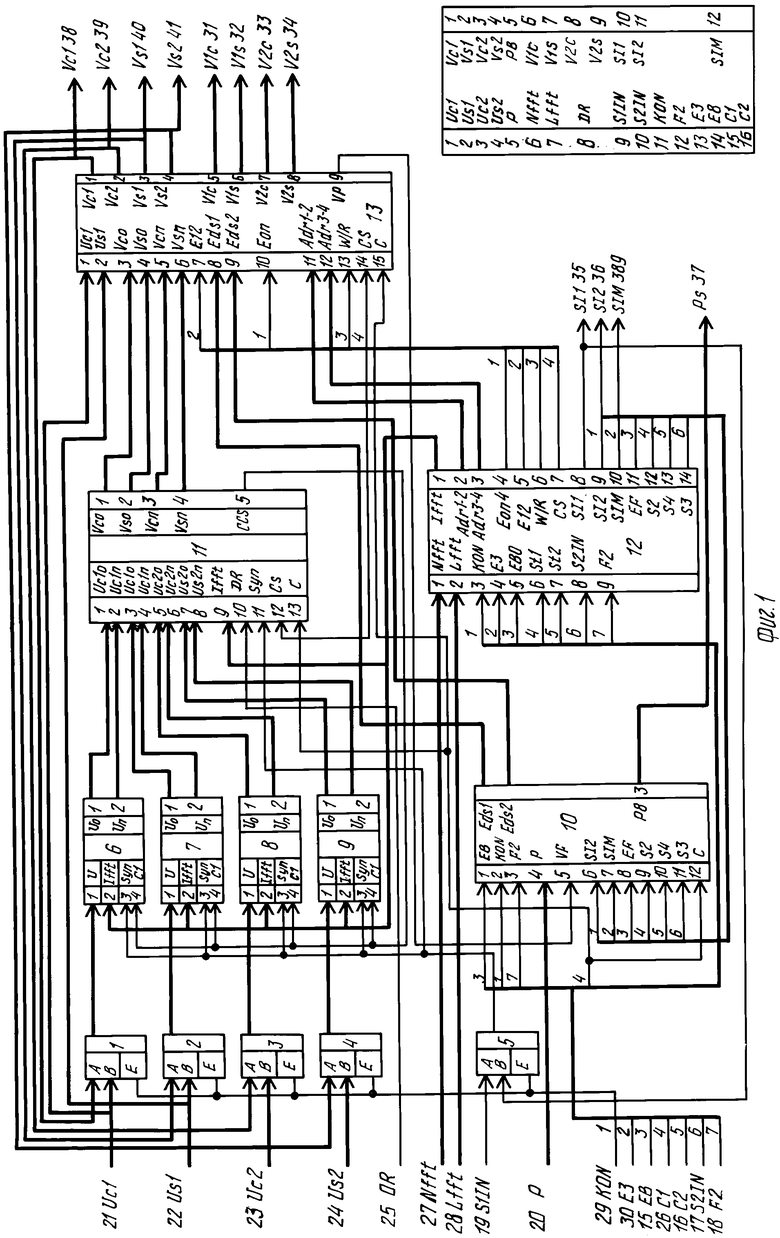

На фиг. 2 изображена схема блока 11 когерентных сумматоров. Он состоит из узла 53 задержки синхронизации, логического элемента 2И 54 и когеретных сумматоров 55s-58s. Первым - восьмым входами блока 11 являются соответственно векторные информационные входы 45-52, девятый - тринадцатый входы блока 11 - это входы номера текущего преобразования Фурье 43 (векторный), признака переключения прямого или обратного ДПФ 25, синхронизации 42, управления режимами записи исходной информации-считывания готового спектра или преобразования Фурье 44 и тактовый 26. Первый - четвертый выходы 55-58 блока 11 - это выходы (векторные) соответственно квадратур четных 55, 56 и нечетных 57, 58 выходных спектральных отсчетов. Пятый выход блока когерентных сумматоров - это выход тактовых сигналов блока (CCS).

Первый вход узла 53 подключен к входу 42, второй вход (векторный) - к входу 43, а третий - к выходу логического элемента 2И 54. Первый - четвертый входы (векторные) когерентного сумматора 55s подключены соответственно к входам 45, 49, 51 и 47 блока 11, первый - четвертый входы (векторные) когерентного сумматора 56s подключены соответственно к входам 47, 51, 45 и 49 блока 11, первый - четвертый входы (векторные) когерентного сумматора 57s подключены соответственно к входам 46, 50, 52 и 48 блока 11, первый - четвертый входы (векторные) когерентного сумматора 58s подключены соответственно к входам 48, 52, 46 и 50 блока 11, пятые входы первого и второго когерентных сумматоров 55s и 56s соединены вместе и подключены к входу логического "0" блока, пятые входы когерентных сумматоров 57s и 58s соединены вместе и подключены к входу логической "1" блока, шестые входы когерентных сумматоров 55s-58s соединены вместе и подключены к входу 25, седьмые входы когерентных сумматоров 55s-58s подключены к выходу узла 53, восьмые входы когерентных сумматоров 55s-58s подключены к выходу элемента 2И 54, выходы (векторные) 55-58 блока 11 когерентных сумматоров подключены соответственно к выходам когерентных сумматоров 55s-58s.

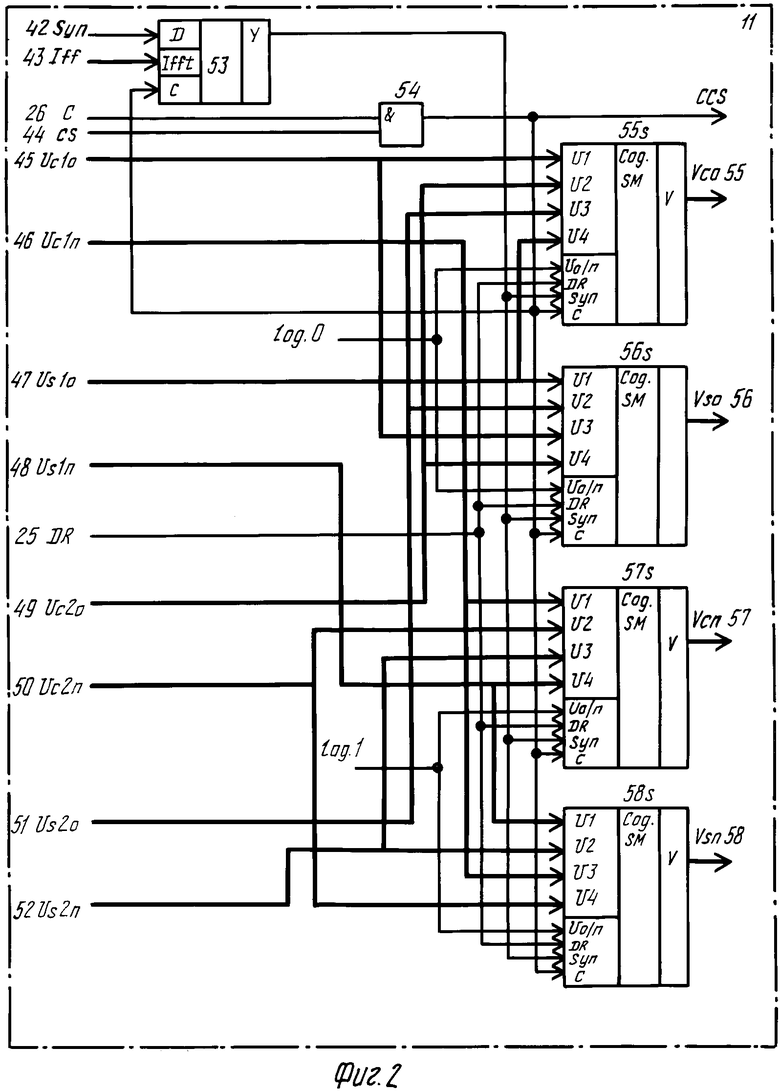

Схема интерполятора по n числу спектральных отсчетов приведены на фиг. 3. Она состоит из узла 59 синхронизации, узла 60 задержки, n/2 двухвходовых сумматоров 61-63, n+1 регистров 64-66, 70-72 и 74, n/2 умножителей 67-69 на весовые коэффициенты и многовходового сумматора 73. Интерполятор имеет входы синхронизации 42, тактовых импульсов 75, информационный 75 и n/2 входов весовых коэффициентов, а также первый и второй выходы соответственно задержанных основных (входных) спектральных отсчетов 77 и промежуточных (рассчитанных) 78.

Синхровход узла 59 синхронизации подключен к входу 42, а тактовый вход - к входу 75 тактовых импульсов. Первый - третий синхровходы узла 60 задержки подключены соответственно к первому - третьему выходам узла 59 синхронизации, тактовый (четвертый) вход узла 60 подключен к входу 75, а информационный (пятый, векторный) - к входу 76. Первые входы сумматоров 61, 62 и 63 (векторные) подключены соответственно к n, n/2+2 и n/2+1 выходам узла 60 задержки, другие входы этих сумматоров (векторные) подключены соответственно к первому n/2-1 и n/2 выходам узла 60 задержки. Первые входы регистров 64, 65 и 66 (векторные) подключены соответственно к выходам сумматоров 61-63, вторые входы этих регистров подключены к входу 75. Первые входы умножителей 67-69 (векторные) подключены соответственно к выходам регистров 64-66, вторые входы (векторные) - к своим источникам весовых коэффициентов (Mn/2, . . .,М2 и М1). Первые входы регистров 70-72 (векторные) подключены соответственно к выходам умножителей 67-69, вторые входы - к входу 75 тактовых импульсов. Входы сумматора n/2 чисел 73 (векторные) подключены к выходам регистров 70-72. Первый вход (векторный) регистра 74 подключен к выходу сумматора 73, а второй вход - к входу 75 тактовых импульсов. Выход регистра 74 подключен к второму выходу (промежуточных спектральных отсчетов) 78 интерполятора. М-й выход узла 60 задержки подключен к первому выходу (задержанных основных спектральных отсчетов) 77 интерполятора.

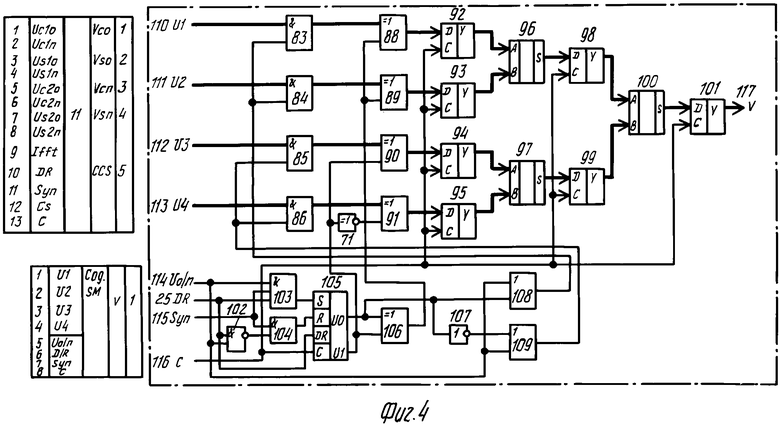

На фиг. 4 изображена схема когерентного сумматора (55s-58s). Схема состоит из пяти элементов 2И 83-86, 104 и одного элемента 3И 103, двух элементов 2ИЛИ 108 и 109, двух элементов НЕ 87 и 107, элемента 2И-НЕ 102, пяти элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 88-91 и 106, семи регистров 92-95, 98 и 101, трех сумматоров 96, 97 и 100 и счетчика 105. Первый - четвертый информационные (векторные) входы когерентного сумматора подключены соответственно к информационным входам 110-113, остальные (пятый-восьмой) - к входу 114 признака переключения суммирования основных или промежуточных отсчетов, входу 25 установки прямого и обратного преобразования Фурье когерентного сумматора, входу 115 синхронизации и тактовому входу 116. Выход когерентного сумматора подключен к выходу 117 регистра 101.

Первые входы (векторные) элементов 2И 83-86 подключены к входам 110-113 соответственно, вторые входы элементов 2И 83-84 - к выходам элемента 2ИЛИ 108, а вторые входы элементов 2И 85, 86 - к выходам элемента 2ИЛИ 109. Первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ (векторные) 88-91 подключены к выходам элементов 2И 83-86 соответственно, вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 88-89 подключены к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 106, а вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 90 и 91 подключены, соответственно к выходу первого разряда счетчика 105 и выходу элемента НЕ 87. Информационные входы (векторные) регистров 92-95 подключены соответственно к выходам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 88-91, а тактовые входы - к входу 116 тактовых импульсов. Входы сумматоров 96 и 97 (векторные) подключены соответственно к выходам регистров 92, 93 и 94, 95. Информационные входы регистров 98 и 99 (векторные) подключены соответственно к выходам сумматоров 96 и 97, тактовые входы этих регистров подключены к входу 116 тактовых импульсов. Входы сумматора 100 (векторные) подключены к выходам регистров 98 и 99. Информационный вход регистра 101 (векторный) подключен к выходу сумматора 100, а тактовый вход - к входу 116 тактовых импульсов. Выход регистра 101 подключен к выходу 117 когерентного сумматора. Первый вход элемента 2И-НЕ 102 подключен к входу 25, а второй - к входу 114. Первый вход элемента 3И 103 подключен к входу 114, второй вход - к входу 115 синхронизации, а третий - к входу 25. Первый вход элемента 2И 104 подключен к входу 115 синхронизации, а второй вход - к выходу элемента 2И-НЕ 102. Вход установки в логическую "1" выходов счетчика 105 подключен к выходу элемента 3И 103, вход установки в логический "0" - к выходу элемента 2И 104, вход изменения направления счета - к входу 25, а тактовый вход - к входу 116 тактовых импульсов. Входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 106 подключены к выходам счетчика 105. Вход элемента НЕ 107 подключен к выходу нулевого разряда счетчика 105. Первый вход элемента 2ИЛИ 109 подключен к выходу элемента НЕ 107, а элемента 2ИЛИ 108 - к выходу нулевого разряда счетчика 105, вторые входы этих элементов подключены к входу 114.

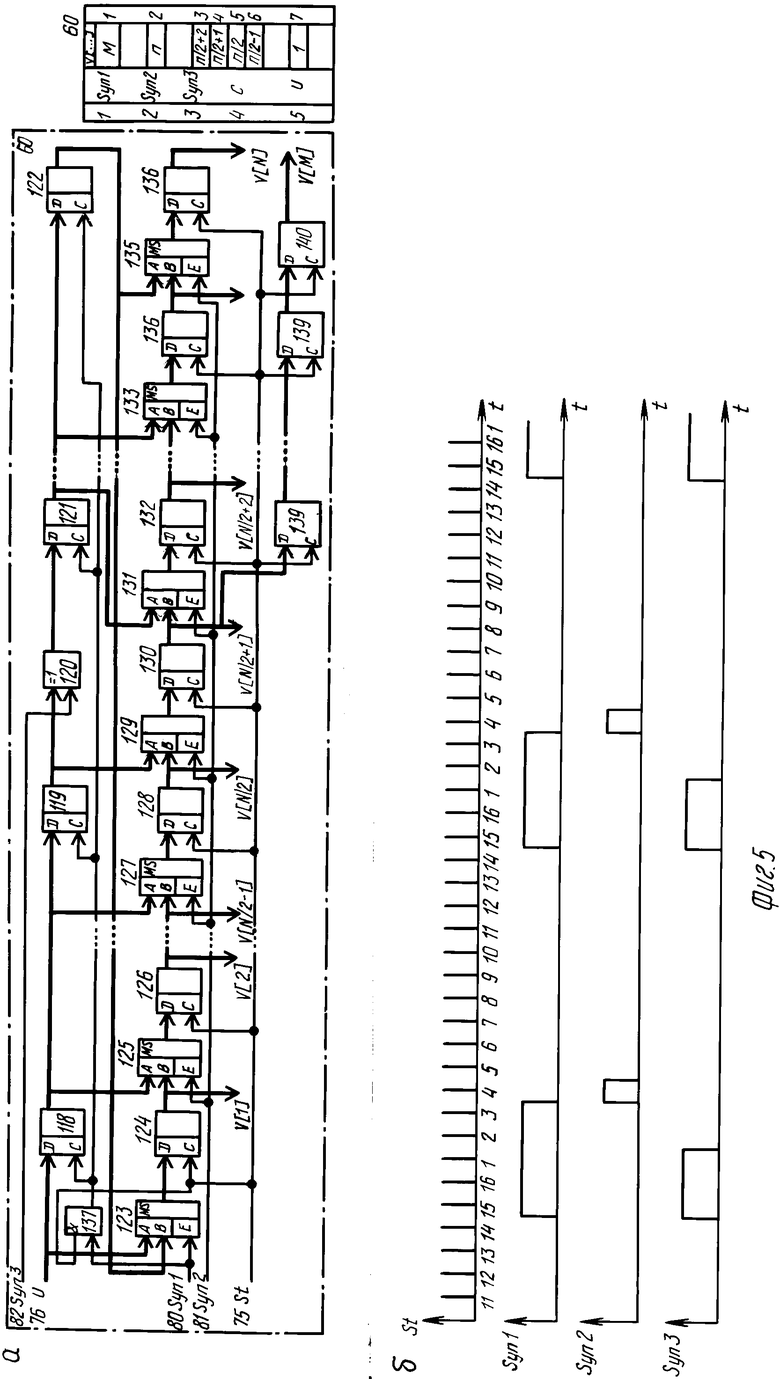

На фиг. 5а изображена схема узла 60 задержки. Узел 60 предназначен для использования в интерполяторах по n отсчетам и состоит из 2n-1 регистров - это соответственно первый, второй,..,n/2, n/2+1, n/2+2,...,n-1 и n-й регистры 124, 126,...,128, 130, 132,...,134 и 136 текущих спектральных отсчетов и соответственно n+1,...,n+n/2, n+n/2+1,...,2n-1-й регистры 118,..., 119 и 121,...,122 крайних спектральных отсчетов, регистра сдвига, состоящего из m последовательно соединенных регистров 138,...,139, 140, элемента 2И 137 и n мультиплексоров 123, 125,...,127, 129, 131,...,133 и 135 с двух направлений - это соответственно первый, второй,...,n/2, n/2+1, n/2+2,..., n-1 и n-й мультиплексоры. Первые три входа 80, 81 и 82 узла задержки - это соответственно первый, второй и третий входы сигналов синхронизации, четвертый вход 75 - вход тактовых импульсов, пятый вход 76 - информационный вход. Выходы узла V[1], V[2],...,V[n/2-1], V[n/2], V[n/2+1], V[n/2+2],..., V[n-1] , V[n] и V[m] узла задержки - это соответственно первый, второй,..., n-й и n+1-й выходы.

Информационный вход регистра 118 (векторный) подключен к входу 76, а тактовый вход - к выходу элемента 2И 137. Информационный вход регистра 119 ((n+n/2)-й регистр крайних спектральных отсчетов) подключен к выходу (n+n/2-1)-го регистра, а тактовый вход - к выходу элемента 2И 137. Первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 120 подключен к выходу регистра 119, а второй вход - к входу 82. Информационный вход регистра 121 подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 120, а тактовый вход - к выходу элемента 2И 137. Информационный вход регистра 122 ((2n-1)-й регистр крайних спектральных отсчетов) подключен к выходу (2n-2)-го регистра памяти, а тактовый вход - к выходу элемента 2И 137. Первый вход мультиплексора 123 подключен к входу 76, второй вход - к выходу регистра 122, а управляющий вход - к входу 80. Информационный вход регистра 124 подключен к выходу мультиплексора 123, а тактовый вход - к входу 75. Первый вход мультиплексора 125 подключен к выходу регистра 118, второй - к выходу регистра 124, а управляющий вход - к входу 81. Информационный вход регистра 126 подключен к выходу мультиплексора 125, а тактовый вход - к входу 75. Первый вход мультиплексора 127 (n/2-й мультиплексор) соединен с выходом (n+n/2-1)-го регистра памяти крайних отсчетов, второй вход с выходом (n/2-1)-го регистра текущих отсчетов, а управляющий вход - с входом 81. Информационный вход регистра 128 соединен с выходом мультиплексора 127, а тактовый вход - с входом 75. Первый вход мультиплексора 129 соединен с выходом регистра 119, второй вход - с выходом регистра 128, а управляющий вход - с входом 81. Информационный вход регистра 130 соединен с выходом мультиплексора 129, а тактовый вход - с входом 75. Первый вход мультиплексора 131 соединен с выходом регистра 121, второй вход - с выходом регистра 130, а управляющий вход - с входом 81. Информационный вход регистра 132 соединен с выходом мультиплексора 131, а тактовый вход - с входом 75. Первый вход мультилексора 133 ((n-1)-й мультиплексор) соединен с выходом (2n-2)-го регистра крайних спектральных отсчетов (вход регистра 122), второй вход - с выходом (n-2)-го регистра текущих спектральных отсчетов, управляющий вход - с входом 81. Информационный вход регистра 134 соединен с выходом мультиплексора 133, а тактовый вход - с входом 75. Первый вход мультиплексора 135 соединен с выходом регистра 122, второй вход - с выходом регистра 134, а управляющий вход - с входом 81. Информационный вход регистра 136 соединен с выходом мультиплексора 135, а тактовый вход - с входом 75. Первый вход элемента 2И 137 соединен с входом 75, а второй вход - с входом 80. Информационный вход регистра 138 соединен с выходом регистра 130, а тактовый вход подключен к входу 75. Информационный вход регистра 139 ((m-1)-й регистр регистра сдвига) соединен с выходом (m-2)-го регистра, а тактовый вход - с входом 75. Информационный вход регистра 140 соединен с выходом регистра 139, а тактовый вход - с входом 75. Выходы первого - n-го регистров текущих спектральных отсчетов - соответственно первый - n-й выходы V[1] - V[n] узла задержки. Выход регистра 140 - (n+1)-й выход V[m] узла задержки.

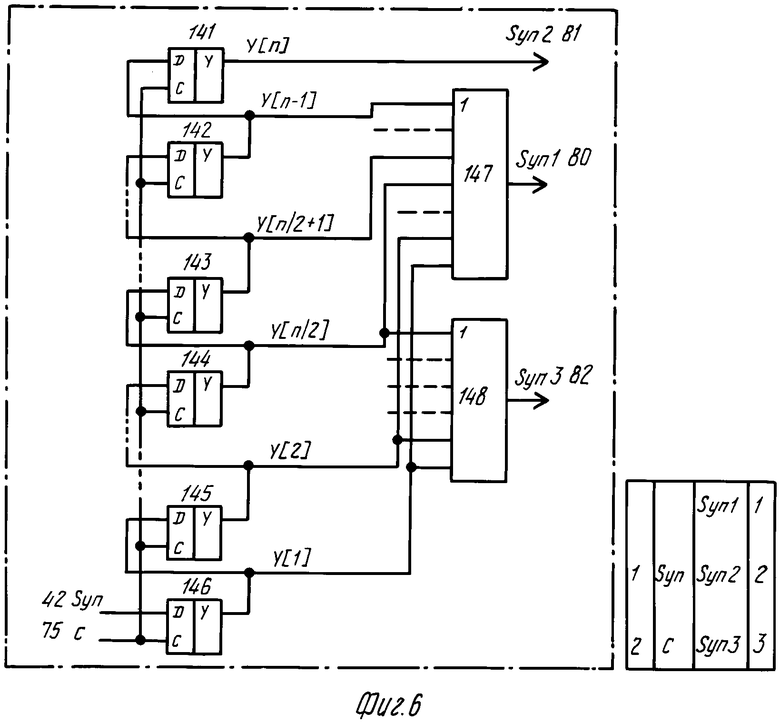

На фиг. 6 представлена схема узла 59 синхронизации интерполятора по n спектральным отсчетам. Она состоит из n D-триггеров 141-146 и двух элементов ИЛИ 147 и 148. Первый и второй входы 42 и 75 узла синхронизации - это входы синхронизации и тактовый, первый, второй и третий выходы - это выходы 80, 81 и 82 соответственно.

D-вход n-го триггера (141) соединен с выходом (n-1)-го триггера (142), D-вход (n-1)-го триггера - с выходом (n-2)-го триггера, . .., D-вход (n/2+1)-го триггера (143) - с выходом n/2-го триггера (144), D-вход n/2-го триггера - с выходом (n/2-1)-го триггера,..., D-вход триггера 145 - с выходом первого D-триггера (146), D-вход первого D-триггера - с входом 42. Тактовые входы всех D-триггеров соединены с входом 75. Элемент ИЛИ 147 имеет n-1 входов, которые подсоединены соответственно к выходам (n-1)-го - первого D-триггеров (142-146). Элемент ИЛИ 148 имеет n/2 входов, которые подсоединены соответственно к выходам n/2-го - первого D-триггеров (144-146). Выходы элементов ИЛИ 148, 147 и D-триггера 141 (n-й D-триггер) - соответственно выходы 80-82.

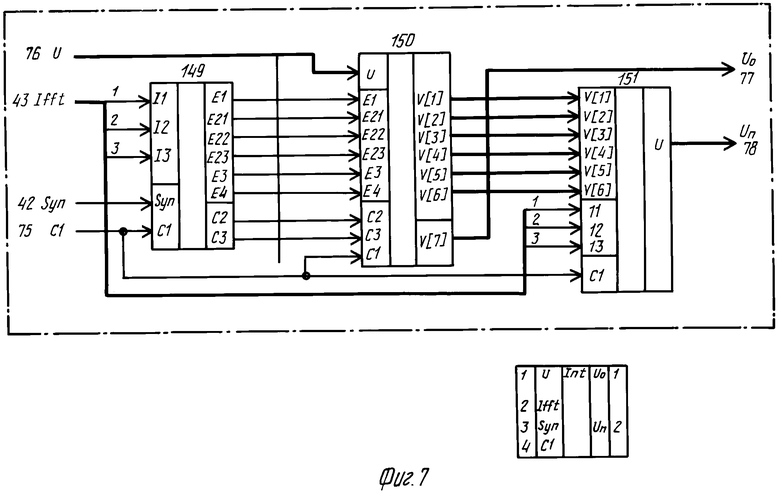

На фиг. 7 представлена схема интерполятора по шести спектральным отсчетам. Схема состоит из узла 149 синхронизации, управляемого узла 150 задержки и весового сумматора 151. Схема интерполятора имеет информационный вход 76 (первый, векторный), второй вход 43 (управляющий, векторный), третий вход 42 (синхронизации) и четвертый вход 75 - тактовый, первый выход 77 (основных спектральных отсчетов, векторный) и второй выход 78 (промежуточных спектральных отсчетов, векторный).

Первые три управляющих входа узла 149 синхронизации (11, 12 и 13) подключены к векторному входу 43, синхровход узла синхронизации подключен к входу 42, а тактовый - к входу 75. Информационный (первый) вход управляемого узла 150 задержки (векторный) подключен к входу 76, первый - шестой управляющие и второй - третий так- товые (второй - девятый) - соответственно к первому - восьмому выходам узла 149, первый тактовый (десятый) вход подключен к входу 75. С первого по шестой информационные входы весового сумматора 151 (векторные) подключены соответственно к первому - шестому выходам узла 150, седьмой - девятый входы - к векторному входу 43, а десятый вход подключен к входу 75 тактовых импульсов. Выход 77 интерполятора подключен к седьмому выходу узла 150 задержки, а выход 78 - к выходу сумматора 151.

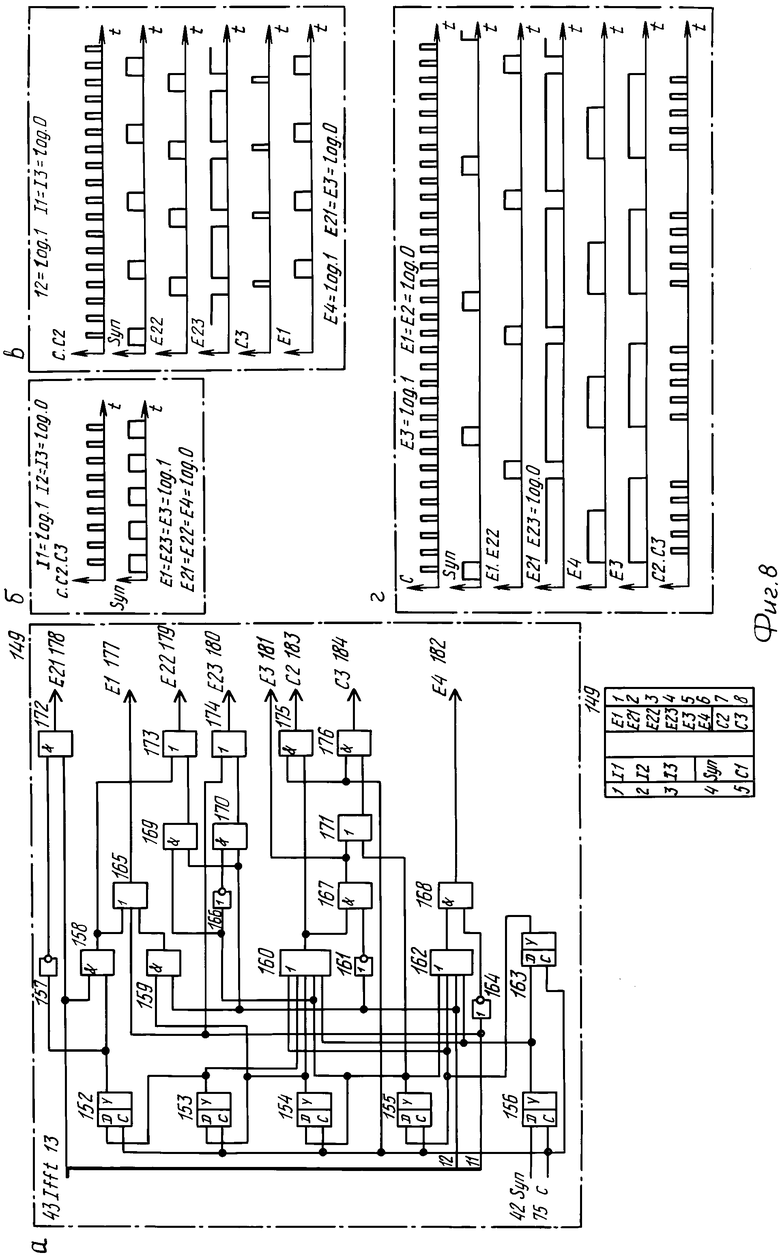

На фиг.8а представлена схема управляемого узла 149 синхронизации. Схема состоит из шести D-триггеров 152-156 и 163, четырех элементов НЕ 157, 161, 164 и 166, пятивходового элемента ИЛИ 160, четырехвходового элемента ИЛИ 162, трехвходового элемента ИЛИ 165, трех двухвходовых элементов ИЛИ 171, 173 и 174 и девяти двухвходовых элементов И 158, 159, 167-170, 172, 175 и 176. Первый - третий управляющие входы узла - это входы 11, 12 и 13 (векторый вход 43), второй вход 42 - это вход синхронизации, третий вход 75 - тактовый. Первый - восьмой выходы схемы синхронизации - это соответственно выходы 177-184.

D-вход триггера 152 подключен к выходу триггера 153, D-вход триггера 153 - к выходу триггера 154, D-вход вход триггера 154 - к выходу триггера 155, D-вход вход триггера 155 - к выходу триггера 163, D-вход триггера 163 - к выходу триггера 156 и D-вход триггера 156 - к входу 42. Все тактовые входы этих триггеров подключены к входу 75 тактовых импульсов. Вход элемента НЕ 157 подключен к выходу триггера 152, вход элемента НЕ 164 - к выходу 11 вектора 43, вход элемента НЕ 161 - к выходу 12 вектора 43 и вход элемента НЕ 166 - к выходу триггера 155. Входы элемента ИЛИ 160 подключены соответственно к выходам триггеров 153, 154, 155, 163 и 156, а входы элемента ИЛИ 162 - соответственно к выходам триггеров 155, 163 и 156, а также выходу 12 вектора 43. Входы элемента ИЛИ 165 подключены соответственно к выходам элементов И 158, 159 и выходу 11 вектора 43. Входы элементов ИЛИ 171, 173 и 174 подключены соответственно к выходам триггера 155 и элементов И 167, 158 и 169, 170 и 11 вектора 43. Первый и второй входы элементов И 158, 159, 167-170, 172, 175 и 176 подключены соответственно к выходам триггера 152 и 13 вектора 43, триггера 154 и 12 вектора 43 элементов ИЛИ 160 и НЕ 161, ИЛИ 162 и НЕ 164, триггера 155 и 12 вектора 43, элемента НЕ 166 и 12 вектора 43, элемента НЕ 157 и 13 вектора 43, элемента ИЛИ 160 и входу 75, элемента ИЛИ 171 и входу 75. Выходы 177 - 184 - это соответственно выходы элементов ИЛИ 165, И 172, ИЛИ 173, 174, И 167, 168, 175 и 176.

На фиг.9 представлена схема управляемого узла 150 задержки интерполятора по шести спектральным отсчетам. Схема состоит из шестнадцати D-триггеров 185-187, 189, 190, 192, 194, 196, 198, 200 и 202 - 207, пяти мультиплексоров 191, 193, 197, 199, 201, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 188 и элемента 2И-3ИЛИ-НЕ 195. Мультиплексоры 191 и 197 имеют прямые выходы, а остальные - инверсные. Первый вход 76 - информационный, векторный, второй - седьмой входы - это первый - шестой управляющие входы 177-182 соответственно, узла, восьмой-десятый входы 183, 184 и 75 - это второй, третий и первый тактовые входы узла. Первый-шестой выходы узла - это выходы 208-213 интерполирующих спектральных отсчетов, седьмой выход - это выход 77 задержанных основных отсчетов. Все информационные входы и выходы векторные.

D-вход триггера 185 подключен к входу 76, D-вход триггера 186 - к выходу триггера 185, D-вход триггера 189 - к выходу ИСКЛЮЧАЮЩЕЕ ИЛИ 188, D-вход триггера 190 - к выходу триггера 189, все тактовые входы указанных триггеров подключены к входу 183. D-вход триггера 187 подключен к выходу триггера 186, а его тактовый вход - к тактовому входу 184. Первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 188 подключен к выходу регистра 187, а второй вход - к входу 182. Первые входы D-триггеров 192, 194, 196, 198, 200 и 202 - 207 подключены соответственно к выходам мультиплексоров 191 и 193, элемента 2И-3ИЛИ-НЕ 195, мультиплексоров 197, 199 и 201, а также D-триггеров 202-206, тактовые входы этих D-триггеров подключены к входу 75 тактовых импульсов. Первый вход мультиплексора 191 подключен к входу 76, второй вход - к выходу D-триггера 190, а управляющий вход - к входу 181. Первые входы мультиплексоров 193, 197, 199 и 201 подключены соответственно к выходам D-триггеров 185, 187, 189 и 190, вторые входы - соответственно к выходам D-тригеров 192, 196, 198 и 200, управляющие входы - к входу 177. Первые входы первого - третьего логических И элементов 2И-3ИЛИ-НЕ 195 подключены соответственно к выходам элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 188, D-триггера 186 и D-триггера 194, вторые входы первого - третьего логических И элемента 2И-3ИЛИ-НЕ 195 подключены соответственно к входам 180, 179 и 178. Выходы 208-213 - выходы D-триггеров 192, 194, 196, 198, 200 и 202 соответственно. Выход 77 подключен к выходу D-триггера 207.

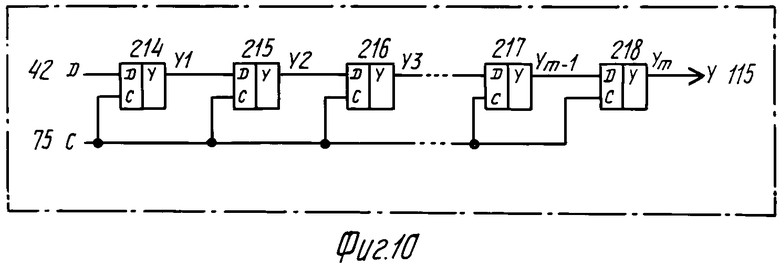

На фиг. 10 представлена схема узла 53 задержки в варианте для интерполятора по n спектральным отсчетам. Схема состоит из m D-триггеров 214-218, соединенных последовательно и представляющих собой последовательный регистр сдвига. Первым и вторым входами схемы являются входы синхронизации 42 и тактовый 75, а выходом - выход 115.

Первый вход (D) триггера 214 подключен к входу 42, первый вход триггера 215 - к выходу триггера 214, первый вход триггера 216 - к выходу триггера 215, . . . , первый вход триггера 217 ((m-1)-й триггер) - к выходу (m-2)-го триггера, первый вход триггера 218 - к выходу триггера 217. Выход 115 схемы подключен к выходу триггера 218.

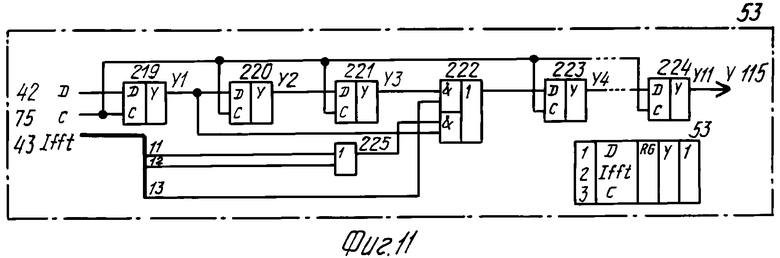

На фиг. 11 представлена схема узла 53 задержки в варианте для интерполятора по шести спектральным отсчетам. Схема состоит из одиннадцати D-триггеров 219-221, 223, ...,224, элемента 2-2И-2ИЛИ 222 и элемента 2ИЛИ 225. Первым-третьим входами схемы соответственно являются входы синхронизации 42, управления 43, (векторный - 11, 12, 13) и тактовый 75, выходом - выход схемы 115.

Первый вход триггера 219 (D) подключен к входу 42, первый вход триггера 220 - к выходу триггера 219, первый вход триггера 221 - к выходу триггера 220, первый вход триггера 223 - к выходу триггера 220, первый вход триггера 223 - к выходу 2-2И-2ИЛИ 222,..., первый вход триггера 224 (одиннадцатый триггер) - к выходу десятого триггера, а все вторые входы триггеров подключены к входу 75 тактовых импульсов. Одни входы логических И элемента 2-2И-2ИЛИ 222 подключены к выходам триггеров 221 и 219, другие входы логических И этого элемента - соответственно к третьему управляющему входу 43 (13) и выходу элемента 2ИЛИ 225. Входы элемента 2ИЛИ 225 подключены к первому и второму входам 43 (11 и 12). Выход 115 узла 53 задержки подключен к выходу триггера 224.

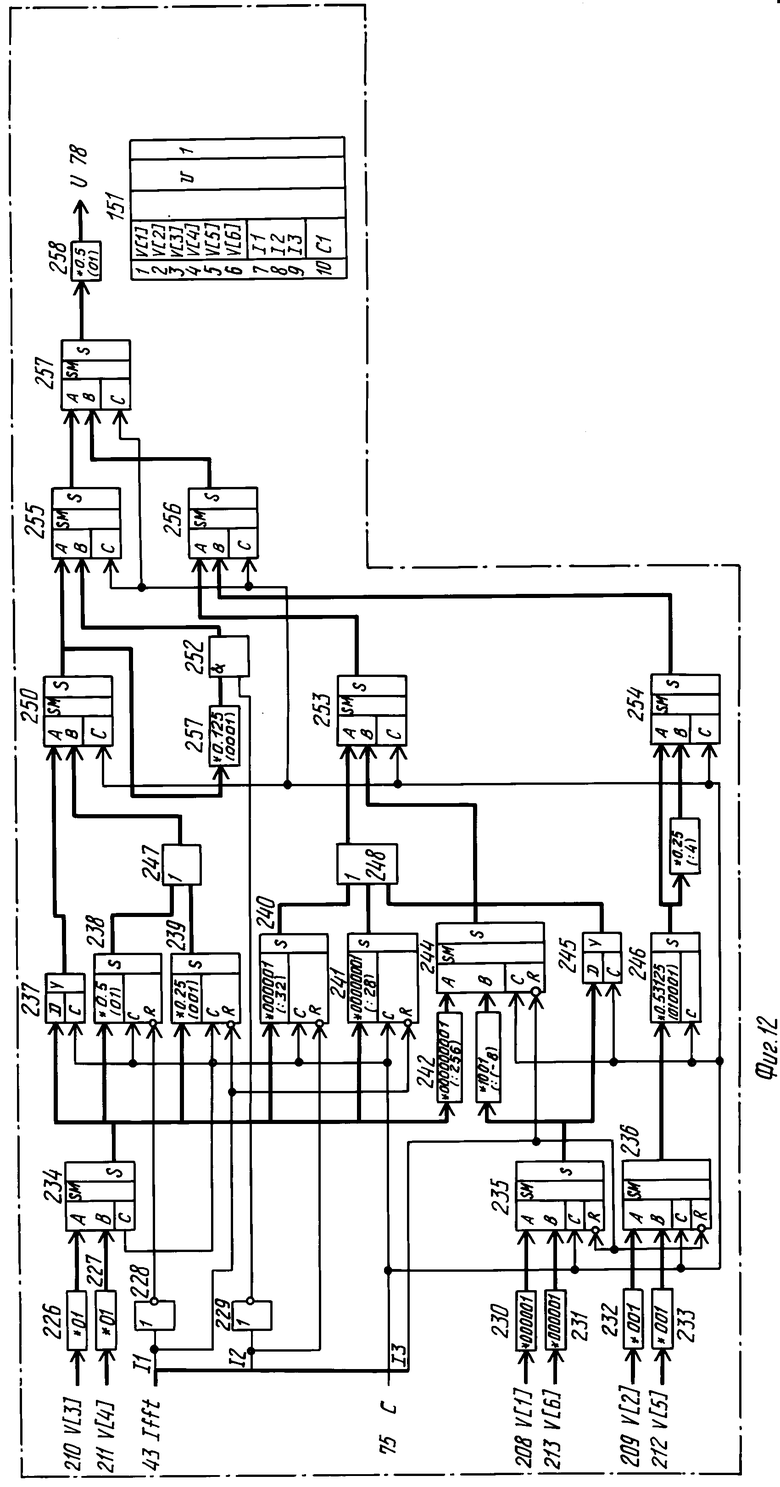

На фиг.12 представлена схема весового сумматора 151 в варианте интерполятора по шести спектральным отсчетам. Схема состоит из одиннадцати блоков 226, 227, 230-233, 242, 243, 249, 251 и 258 масштабирования, двух элементов НЕ 228 и 229, десяти сумматоров с выходными регистрами памяти 234, 244, 250 и 253 - 257 и с выходными регистрами и установкой в логический "0" 235 и 236, двух регистров 237 и 245, четырех регистров 238-241 с масштабированием, регистра 246 с умножителем, двухвходового элемента ИЛИ 247, двухвходового элемента И 252 и трехвходового элемента ИЛИ 248. Входами (первые - шестой) схемы являются первый - шестой информационные 208-213, первый - третий управляющие (седьмой - девятый) 43 (векторный 11, 12 и 13) и тактовый 75 (десятый), входом - выход 78.

Входы блоков 226, 227, 230-233, 242, 243, 249, 251 и 258 масштабирования подключены соответственно к входам 210, 211, 208, 213, 209 и 212 и к выходам сумматоров 234, 235, регистра 246, сумматоров 250 и 257. Входы элементов НЕ 228 и 229 подключены соответственно к первому и второму входам 43 (11 и 12). Информационные входы сумматоров 234 - 236, 244, 250 и 253 - 257 подключены соответственно к выходам блоков 226 и 227, 230 и 231, 232 и 233, 242 и 243, регистра 237 и элементов ИЛИ 247, 248 и сумматора 244, регистра 246 и блока 249, сумматора 250 и элемента И 252, сумматоров 253 и 254, 255 и 256. Тактовые входы сумматоров подключены к входу 75. Входы установки в логический "0" сумматоров 235 и 236 подсоединены к третьему управляющему входу 43 (13). Информационные входы регистров 237-241 подключены к выходу сумматора 234, а регистров 245 и 246 - соответственно к выходам сумматоров 235 и 236. Тактовые входы всех регистров подключены к входу 75. Входы установки в логический "0" регистров 238-241 подключены соответственно к выходу элемента НЕ 228 и к первому - третьему управляющим входам 43 (11, 12 и 13). Вход установки регистра 244 подключен к третьему входу 43 (13). Первый и второй входы элемента ИЛИ 247 подключены соответственно к выходам регистров 238 и 239, первый - третий входы элементов ИЛИ 248 - к выходам регистров 240, 241 и 245, а первый и второй входы элементов И 252 - к выходу блока 251 масштабирования и выходу элемента НЕ 229. Выход 78 весового сумматора подключен к выходу блока 258 масштабирования.

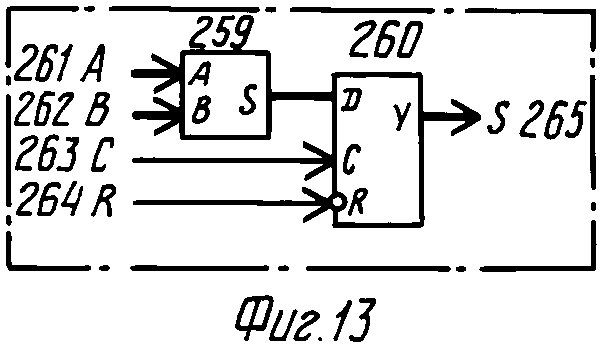

На фиг.13 представлена схема сумматора с регистром памяти и установкой в логический "0". Схема состоит из сумматора 259 двух чисел и регистра 260 на D-триггерах с установкой в логический "0". Входами схемы являются информационные 261 и 262, тактовый 263 и установочный 264, а выходом - выход 265. Входы сумматора 259 соединены с входами 261 и 262. D-вход регистра 260 подключен к выходу сумматора 259, тактовый вход - к входу 263, а установочный - к входу 264. Выход 265 подключен к выходу регистра 260.

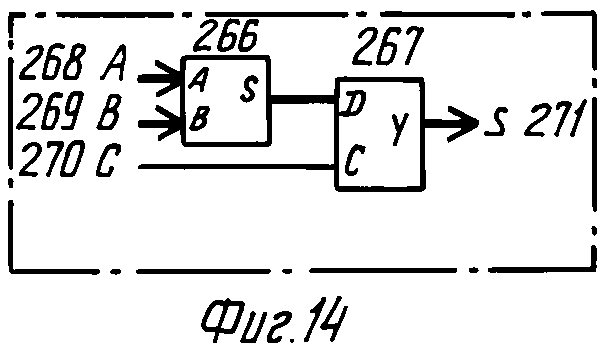

На фиг.14 представлена схема сумматора с регистром памяти. Схема состоит из сумматора 266 двух чисел и регистра 267 на D-триггерах. Входами схемы являются информационные 268 и 269 и тактовый 270, выходом - выход 271. Входы сумматора 266 соединены с входами 268 и 269. D-вход регистра 267 подключен к выходу сумматора 266, а тактовый вход - к входу 270. Выход 271 подключен к выходу регистра 267.

На фиг.15 представлена схема регистра с масштабированием и установкой в логический "0". Схема состоит из блока 272 масштабирования и регистра 273 на D-триггерах. Входами схемы являются информационный 274, тактовый 275 и установочный 276, выходом - выход 277. Вход блока 272 масштабирования подключен к входу 274, D-вход регистра - к выходу блока 272, его тактовый вход - к входу 275, а установочный - к входу 276. Выход регистра с масштабированием подключен к выходу 277 регистра 273.

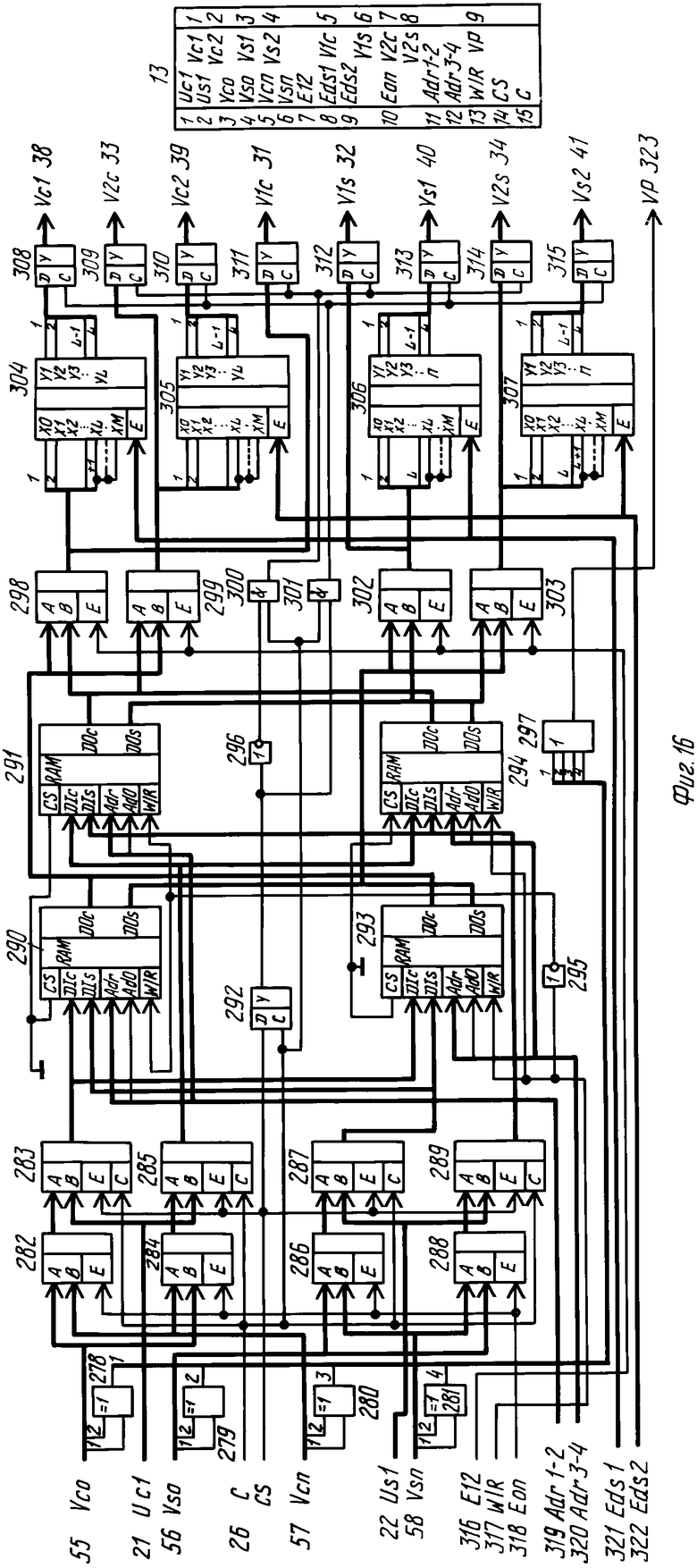

На фиг.16 приведена схема блока 13 оперативной памяти. Схема состоит из четырех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 278-281, восьми мультиплексоров 282, 284, 286, 288, 298, 299, 302 и 303 с двух направлений, четырех мультиплексоров 283, 285, 287 и 289, совмещенных с регистрами памяти, D-триггера 292, четырех узлов оперативной памяти (ОЗУ) 290, 291, 293 и 294, двух элементов НЕ 295 и 296, элемента 4ИЛИ 297, двух элементов 2И 300 и 301, четырех сдвигателей 304 - 307, а также восьми регистров 308 - 315.

Первым - пятнадцатым входами блока 13 оперативной памяти являются соответственно первый - шестой информационные входы, из которых входы 21, 22 - квадратурные входы сигнала, подлежащего преобразованию, входы 55, 56 - квадратурные входы основных спектральных отсчетов и входы 57, 58 - квадратурные входы промежуточных (интерполированных) спектральных отсчетов. Кроме того, имеются входы управления считыванием нечетных и четных частичных спектров 316, управления записью основных и промежуточных отсчетов спектра 318, управления режимами записи-считывания 317, управления режимами записи исходной информации и считывания готового спектра или преобразования Фурье 44 (соответственно седьмой, десятый, тринадцатый и четырнадцатый входы блока 13), первый и второй входы 321 и 322 соответственно признака управления сдвигом (восьмой и девятый входы блока 13), первый и второй адресные входы 319 и 320 (соответственно одиннадцатый и двенадцатый блока 13), а также тактовый вход 26 (пятнадцатый блока 13). Блок 13 имеет восемь информационных векторных выходов, из которых выходы 38-41, первый - четвертый выходы блока 13) - это соответственно нечетные и четные квадратурные выходы частичных спектров, а выходы 31 - 34 (пятый - восьмой выходы блока 13) - это соответственно квадратурные выходы нечетных и четных выходных спектральных отсчетов. Выход 323 (девятый выход блока 13) - это выход сигнала переполнения.

Входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 278-281 подключены к двум старшим разрядам входов 55-58 соответственно. Первые входы мультиплексоров 282, 284, 286 и 288 подключены соответственно к входам 55, 57, 56 и 58, а вторые входы этих мультиплексоров подключены соответственно к входам 57, 55, 58 и 56. Управляющие входы указанных мультиплексоров подключены к входу 318. Первые входы мультиплексоров 283, 285, 287 и 289 подключены к выходам мультиплексоров 282, 284, 286 и 288, а их вторые входы - к входам 21 (мультиплексоры 283 и 285) и 22 (мультиплексоры 287 и 289). Управляющие входы этих мультиплексоров подключены к входу 44, а тактовые - к входу 26. Первые и вторые информационные входы ОЗУ 290, 292, 293 и 294 подключены к выходам мультиплексоров 283 и 287, 285 и 289, 283 и 287, 285 и 289 соответственно. Адресные шины ОЗУ 290 и 291 подключены к входу 319, причем нулевой разряд ОЗУ 290 подключен к первому адресному разряду шины 319, а ОЗУ 291 - к второму. Адресные шины ОЗУ 293 и 294 подключены к входу 320, причем нулевой разряд ОЗУ 293 подключен к первому разряду шины 320, а ОЗУ 294 - к второму.

Входы управления режимами записи-считывания ОЗУ 290 и 291 подключены к выходу элемента НЕ 295, а такие же входы ОЗУ узлов 293 и 294 - к входу 319. Входы управления включением выходов ОЗУ (CS) подключены к логическому "0" (режим "выходы включены"). D-вход триггера 292 подключен к входу 44, а тактовый вход - к входу 26. Вход элемента НЕ 296 подключен к выходу триггера 292. Первые входы элементов 2И 300 и 301 подключены к входу 26 тактовых импульсов, а вторые - соответственно к выходам элемента НЕ 296 и триггера 292. Первый и второй входы мультиплексора 298 подключены соответственно к первым выходам ОЗУ 290, 293 и 291, 294 соответственно. Первые и второй входы мультиплексора 299 подключены соответственно к первым выходам ОЗУ 291, 294 и 290, 293 соответственно. Аналогично только к вторым выходам ОЗУ 290, 291, 293 и 294 подключены первые и вторые входы мультиплексоров 302 и 303. Управляющие входы всех мультиплексоров подключены к входу 316. Входы элемента 4ИЛИ 297 подключены к выходам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 278-281. Информационные входы сдвигателей 304-299, 302 и 303 соответсвенно. При этом старший (L+1)-й разряд в каждом сдвигателе подключен к старшим входам сдвигателя, число которых равно количеству используемых сдвигов разрядов. Управляющие входы сдвигателей 304 и 306 подключены к входу 321, а управляющие входы сдвигателей 305 и 307 - к входу 322. Информационные входы (число их L) регистров 308, 310, 313 и 315 подключены к выходам сдвигателей 304-307 соответственно, а тактовые входы - к выходу элемента 2И 301. Информационные входы (число их L+1) регистров 311, 309, 312 и 316 подключены соответственно к выходам мультиплексоров 298, 299, 302 и 303, а их тактовые входы - к выходу логического элемента 2И 300. Выходы 13, 38-41 31-34 схемы - соответственно выходы регистров 308, 310, 313, 311, 312, 309 и 314 памяти. Выход 323 подключен к выходу логического элемента 4ИЛИ 297.

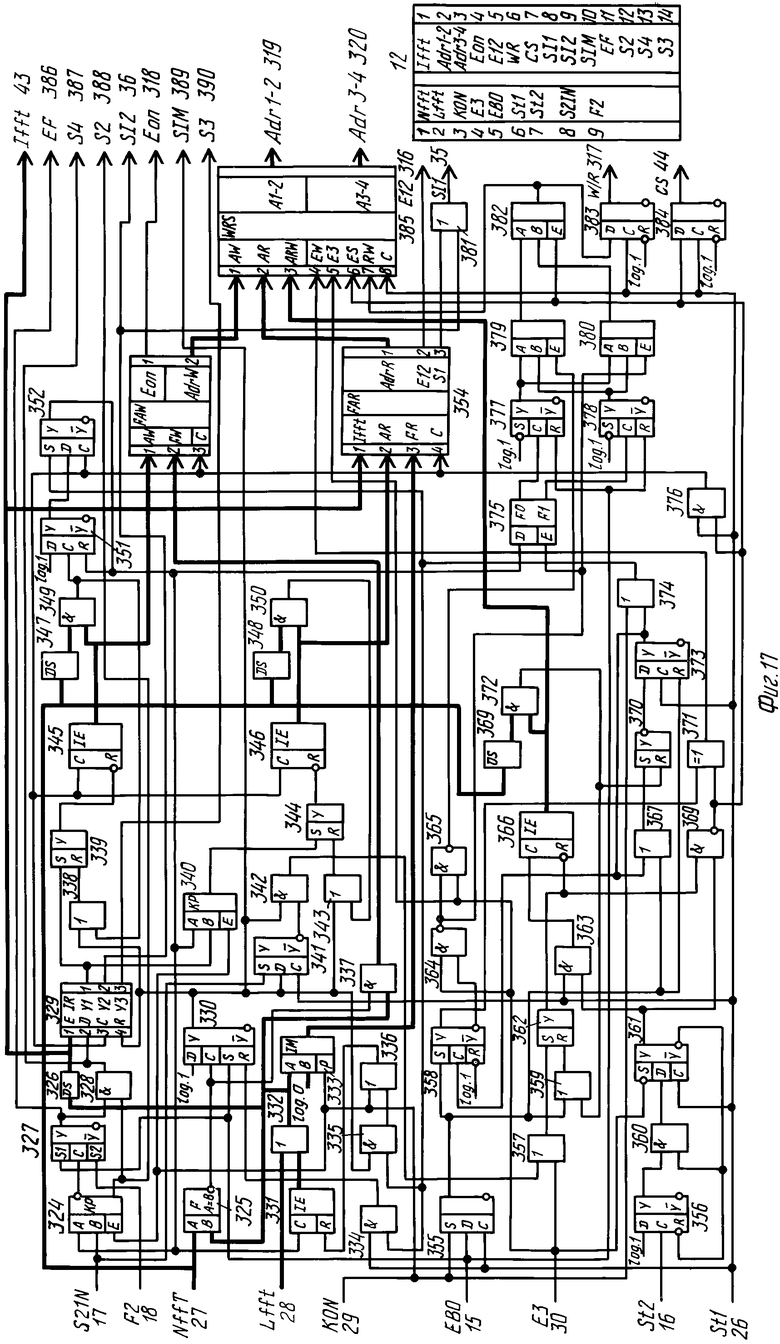

На фиг.17 приведена схема блока 12 управления. Эта схема состоит из пяти мультиплексоров 324, 340, 379, 380 и 382 с двух направлений, схемы 325 сравнения, четырех дешифраторов 326, 347, 348 и 369, счетного триггера 327 с двумя входами установки в логическую "1", трех счетных RS-триггеров 358, 377 и 378, семи элементов 2И 328, 334, 335, 342, 360, 363 и 376, трех элементов 2И-НЕ 364, 365 и 368, трех элементов И-ИЛИ 349, 350 и 372, группы элементов 2И 337 с векторными входами и выходами, представляющей собой параллельное соединение схем 2И, узла 329 задержки, D-триггера с 330 R- и S-входами, четырех счетчиков 331, 345, 346 и 366 с установкой в начальное состояние, восьми элементов 2ИЛИ 336, 338, 343, 357, 367, 374 и 381, группы элементов 2ИЛИ 332 с векторными входами и выходом, представляющей собой параллельное соединение схем 2ИЛИ, сумматора 333 с входом переноса, трех RS-триггеров 339, 344 и 362 с прямыми выходами и одного RS-триггера 370 с инверсным выходом, девяти D-триггеров 341, 351, 352, 355, 356, 361, 373, 383 и 384 с установкой в начальное состояние узла 353 формирования адресов записи 353, узла 354 формирования адресов чтения 354, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 371, демультиплексора 375 и узла 385 переключений.

Блок 12 имеет девять входов: первый векторный 27 - вход установки размера ДПФ на выходе анализатора спектра, вход (второй векторный) 28 установки размера ДПФ на данном этапе, вход (третий) 29 установки режима конвейерной или однопроцессорной обработки Фурье, вход (четвертый) 30 установки режима одновременной или последовательной обработки, вход (пятый) 15 начальной установки, (шестой) первый тактовый вход 26, второй тактовый вход (седьмой) 16, вход (восьмой) 17 сигнала сопровождения режима конвейерной обработки и вход (девятый) 18 признака текущего изменения размера ДПФ. Блок 12 имеет четырнадцать выходов: первый векторный 43 (выход номера текущего этапа преобразования Фурье), второй векторный 319 (выход адресной шины первого и второго ОЗУ), третий векторный 320 (выход адресной шины третьего и четвертого ОЗУ), четвертый 318 (управление записью основных или промежуточных - интерполированных спектральных отсчетов), пятый 316 (управление считыванием нечетных или четных частичных спектров), шестой 319 (управление режимами записи-считывания), седьмой 44 (управление режимами записи исходной информации-считывания готового спектра или преобразования Фурье), восьмой 35 (синхроимпульсы начала считывания очередного частичного спектра промежуточного этапа преобразования Фурье), девятый 36 (синхроимпульсы окончания одного (очередного) этапа преобразования Фурье), десятый 389 (период одного этапа преобразования Фурье), одиннадцатый 386 (начало обработки присоединяемого частичного спектра при удвоении размера преобразования Фурье на данном этапе), двенадцатый 388 (первый синхроимпульс признака начала каждого этапа преобразования Фурье), тринадцатый 387 (второй синхроимпульс признака начала каждого этапа преобразования Фурье в данном устройстве), четырнадцатый 390 (синхроимпульс признака считывания приращения порядка чисел выходного частичного спектра).

Первый вход мультиплексора 324 подключен к выходу D-триггера 352, второй его вход - к входу 17, а управляющий - к входу 29. Один вход (векторный) схемы 325 сравнения подключен к входу 27, а другой (тоже векторный) - к выходу группы элементов 2ИЛИ 332. Вход (векторный) дешифратора 326 подключен к выходу группы элементов 2ИЛИ 332. Первый вход установки в логическую "1" счетного триггера 327 подключен к входу 15, тактовый вход - к инверсному выходу мультиплексора 324, а второй вход установки в логическую "1" - к входу 18. Один вход элемента 2И 328 подключен к прямому выходу триггера 327, а другой - к прямому выходу мультиплексора 324. Первый вход (управляющий, векторный) узла 329 задержки подключен к выходу дешифратора 326, второй (информационный) - к выходу логического элемента 2И 328, третий (тактовый) - к выходу логического элемента 2И 376 и четвертый (установочный) - к выходу триггера 330. Информационный вход (D) триггера 330 подключен к логической "1", тактовый вход - к инверсному выходу схемы 325 сравнения, вход установки в логическую "1" - к входу 15, а вход установки в логический "0" - к выходу элемента 2И 334. Тактовый вход счетчика 331 подключен к выходу триггера 352, а установочный - к выходу элемента 2ИЛИ 336. Первый вход (векторный) группы элементов 2ИЛИ 332 подключен к входу 28, а другой (тоже векторный) - к выходу счетчика 331.

Первый вход сумматора 333 (векторный) подключен к выходу группы элементов 2ИЛИ 332, другой вход (тоже векторный) - к логическому "0", а вход переноса - к входу 29. Первый вход элемента 2И 334 подключен к входу 26, а второй - к выходу элемента 2ИЛИ 374. Первый вход элемента 2И 335 подключен к выходу триггера 330, а второй - к выходу логического элемента 2ИЛИ 374. Первый вход элемента 2ИЛИ 336 подключен к входу 29, а второй - к выходу элемента 2И 335. Первый вход группы элементов 2И 337 (векторный) подключен к выходу группы элементов 2ИЛИ 332, а второй - к инверсному выходу схемы 325 сравнения. Первый вход элемента 2ИЛИ 338 подключен к выходу триггера 330, а второй - к выходу элемента И-ИЛИ 349. Вход установки в логическую "1" RS-триггера 339 подключен к первому выходу узла 329 задержки, а вход установки в логический "0" - к выходу элемента 2ИЛИ 338. Первый вход мультиплексора 340 подключен к выходу триггера 352, второй вход - к первому выходу узла 329 задержки, а управляющий вход - к входу 29. Информационный (D) вход D-триггера 341 подключен к выходу триггера 330, тактовый вход - к входу 26, а вход установки в логическую "1" - к входу 17. Первый вход элемента 2И 342 подключен к выходу триггера 330, а второй - к инверсному выходу триггера 341. Первый вход элемента 2ИЛИ 343 подключен к выходу триггера 330, а второй вход - к выходу элемента И-ИЛИ 350. Вход установки в логическую "1" RS-триггера 344 подключен к выходу мультиплексора 340, а вход установки в логический "0" - к выходу элемента 2ИЛИ 343. Тактовый вход счетчика 345 подключен к выходу элемента 2И 376, а установочный - к выходу триггера 339. Тактовый вход счетчика 346 подключен к выходу элемента 2И 376, а установочный - к выходу триггера 344. Входы деширфаторов 347 и 348 (векторные) подключены к входу 27. Первые входы (векторные) элементов И-ИЛИ 349 и 350 подключены к выходам соответственно дешифраторов 347 и 348, вторые входы этих схем (тоже векторные) - соответственно к выходам счетчиков 345 и 346. Информационный (D) вход D-триггера 351 подключен к логической "1", тактовый - к выходу элемента И-ИЛИ 349, а вход установки в логический "0" - к выходу триггера 52. Информационный (D) вход D-триггера 352 подключен к выходу триггера 351, тактовый вход - к выходу задержки 2И 376, а вход установки в логическую "1" - к выходу элемента 2ИЛИ 374. Первый информационный вход (векторный) узла 353 формирования адресов записи подключен к выходу счетчика 345, второй вход (тоже векторный) - к выходу группы элементов 2И 337, а тактовый - к выходу элемента 2И 376. Первый вход (векторный) узла 354 формирования адресов считывания подключен к выходу дешифратора 326, второй (информационный, тоже векторный) - к выходу счетчика 346, третий (векторный) - к выходу сумматора 333, а тактовый - к выходу элемента 2И 376. Информационный (D) вход D-триггера 355 подключен к входу 15, тактовый вход - к входу 26, а вход установки в логическую "1" - к входу 29. Информационный (D) вход D-триггера 356 подключен к логической "1", тактовый вход - к входу 16, а вход установки в логический "0" (инверсный) - к инверсному выходу триггера 361. Первый вход элемента 2ИЛИ 357 подключен к выходу элемента 2И 342, а второй - к входу 30. Вход установки в логическую "1" счетного RS-триггера 358 подключен к выходу триггера 355, тактовый вход - к прямому выходу триггера 373, а вход установки в логический "0" (инверсный) - к логической "1". Первый вход элемента 2ИЛИ 359 подключен к выходу триггера 355, а второй - к выходу элемента И-ИЛИ 372. Первый вход элемента 2И 360 подключен к прямому выходу триггера 356, а второй - к инверсному выходу триггера 361. Вход установки в логическую "1" (инверсный) D-триггера 361 подключен к входу 30, тактовый вход - к входу 26, а D-вход - к выходу элемента 2И 360. Вход установки в логическую "1" RS-триггера 362 подключен к выходу элемента 2ИЛИ 357, а вход установки в логический "0" - к выходу элемента 2ИЛИ 359. Первый вход элемента 2И 363 подключен к прямому выходу триггера 361, а второй - к входу 26 тактовых импульсов. Первый вход элемента 2И-НЕ 364 подключен к входу 30, а второй - к инверсному выходу триггера 358. Первый вход элемента 2И-НЕ 365 подключен к выходу элемента 2И-НЕ 364, а второй - к входу 30. Тактовый вход счетчика 366 подключен к выходу элемента 2И 363, а вход установки в начальное состояние - к выходу триггера 362. Первый вход элемента 2ИЛИ 367 подключен к прямому выходу триггера 373, а второй вход - к выходу триггера 355. Первый вход элемента 2И-НЕ 368 подключен к выходу элемента 2И 363, а второй вход - к прямому выходу триггера 361. Вход дешифратора 369 (векторный) подключен к входу 27. Вход установки в логическую "1" RS-триггера 370 подключен к выходу элемента 2ИЛИ 367, а вход установки в логический "0" - к выходу элемента И-ИЛИ 372. Первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 371 подключен к прямому выходу триггера 358, а второй вход - к выходу элемента 2И-НЕ 368. Первый вход (векторный) элемента И-ИЛИ 372 подключен к выходу дешифратора 369, а второй (тоже векторный) - к выходу счетчика 366. Информационный вход (D) D-триггера 373 подключен к инверсному выходу триггера 370, тактовый вход - к входу 26, а вход установки в логический "0" - к выходу триггера 355. Первый вход элемента 2ИЛИ 374 подключен к входу 29, а второй - к прямому выходу триггера 373. Информационный вход демультиплексора 375 подключен к выходу триггера 352, а управляющий - к выходу элемента 2И-НЕ 364. Первый вход элемента 2И 376 подключен к входу 26, а второй - к выходу элемента 2И-НЕ 368. Вход установки в логическую "1" (инверсный) счетного RS-триггера 377 подключен к логической "1", тактовый вход - к первому выходу демультиплексора 375, а вход установки в логический "0" (инверсный) - к входу 15. Так же подключены установочные входы счетного RS-триггера 378, тактовый вход которого подключен к второму выходу демультиплексора 375. Первые входы мультиплексора 379 и 380 подключены к выходу триггера 377, вторые входы - к выходу триггера 378, а управляющие входы - соответственно к выходам элементов 2И-НЕ 365 и 364. Первый и второй входы мультиплексора 382 подключены соответственно к выходам мультиплексоров 379 и 380, управляющий вход мультиплексора 382 подключен к выходу элемента 2И-НЕ 368. Первый вход элемента 2ИЛИ 381 подключен к третьему выходу узла 354, а второй - к второму выходу узла 329 задержки. Информационный (D) вход D-триггера 383 подключен к выходу мультиплексора 382, тактовый вход - к входу 26, а вход установки в логический "0" (инверсный) - к логической "1". Информационный вход (D) вход D-триггера 384 подключен к выходу элемента 2И-НЕ 368, тактовый вход - к входу 26, а вход установки в логический "0" (инверсный) - к логической "1". Первый информационный (первый векторный) вход узла 385 переключения подключен к второму выходу узла 353, второй информационный вход (второй векторный) - к первому выходу узла 354, третий информационный вход (третий векторный) - к выходу счетчика 366, вход переключения адресного пространства (четвертый) - к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 371, вход смещения разрядов (пятый) - к входу 30, второй управляющий вход (шестой) - к выходу элемента 2И-НЕ 368, первый управляющий вход (седьмой) - к выходу мультиплексора 382 и тактовый вход (восьмой) - к входу 26.

Первый выход 43 блока 12 - выход дешифратора 326, второй выход (векторный) 319 - первый выход узла 385, третий выход (векторный) 320 - второй выход узла 385, четвертый выход 318 - первый выход узла 353, пятый выход 316 - второй выход узла 354, шестой выход 319 - выход триггера 383, седьмой выход 44 - выход триггера 384, восьмой выход 35 - выход элемента 2ИЛИ 381, девятый выход 36 - второй выход узла 329 задержки, десятый выход 389 - выход триггера 330, одиннадцатый выход 386 - прямой выход триггера 327, двенадцатый выход 388 - прямой выход мультиплексора 324, тринадцатый выход 387 - выход элемента 2И 328, четырнадцатый выход 390 - третий выход узла 329 задержки.

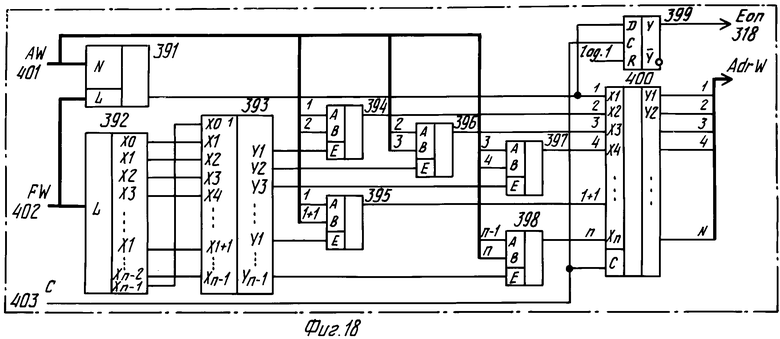

На фиг. 18 представлена схема узла 353 формирования адресов записи. Схема состоит из n-входового мультиплексора 391, дешифратора 392, группы элементов ИЛИ 393, n-1 мультиплексоров 394 - 398, D-триггера 399 и регистра 400. Схема узла имеет информационный вход 401 (первый) - это вход адресов, подлежащих формированию, адресный вход 402 (второй) - вход управления работой формирователя и тактовый вход 403 (третий). Выходов узла два: первый выход 318 - сигнал управления переключением основных и промежуточных отсчетов и второй выход 404 - выход адресов записи.

Информационный (векторный) вход мультиплексора 391 подключен к входу 401, а вход управления (векторный) - к входу 402. Вход (векторный) дешифратора 392 подключен к входу 402. Второй - n-й входы группы элементов ИЛИ 393 подключены соответственно к первому - (n-1)-у выходам дешифратора 392, а первый вход группы элементов ИЛИ 393 подключен к n-у выходу дешифратора 392. Нулевой - (n-2)-й разряды информационного входа 401 подключены к первому входу мультиплексоров 394-398 соответственно, первый - (n-1)-й разряды этого входа подключены к вторым входам указанных мультиплексоров, а управляющие входы мультиплексоров подключены соответственно к первому - (n-1)-у выходам группы элементов ИЛИ 393. Первый информационный вход регистра 400 подключен к выходу мультиплексора 391, второй - n-й входы подключены к выходам мультиплексоров 394-398 соответственно, а тактовый вход подключен к входу 403. Информационный (D) вход D-триггера 399 подключен к выходу мультиплексора 391, тактовый вход - к входу 403, а вход установки в логический "0" (инверсный) - к логической "1". Первый выход 318 узла 353 подключен к выходу триггера 399, а второй его выход 404 - соответственно к первому - n-у выходам регистра 400.

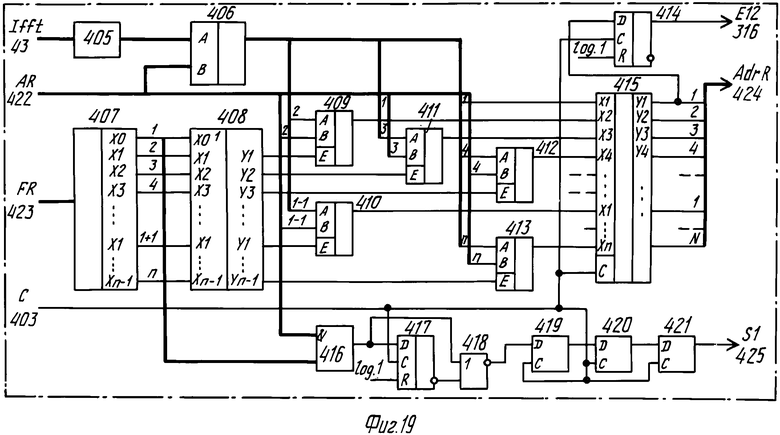

На фиг. 19 представлена схема узла 354 формирования адресов чтения. Схема состоит из шифратора 405, вычитателя 406, дешифратора 407, группы элементов ИЛИ 408, n-1 мультиплексоров 409-413, элемента 2И-nИЛИ 416, элемента 2ИЛИ-НЕ 418, пяти D-триггеров 414, 417, 419-421 и регистра 415. Входами узла являются управляющий 43 (первый), информационный 422 (второй), адресный 423 (третий) и тактовый 403 (четвертый). Первый выход 316 узла формирования - управления переключением четных-нечетных частичных спектров, второй 424 - адресная шина чтения и третий выход 425 - синхросигнал окончания чтения очередной пары частичных спектров.

Входы шифратора 405 подключены к входу 43. Вход вычитаемого вычитателя 406 подключен к выходу шифратора 405, а вход уменьшаемого - к входу 422. Вход дешифратора 407 подключен к входу 423. Первый - n-й входы группы элементов ИЛИ 408 подключены к соответствующим выходам дешифратора 407. Вторые входы мультиплексоров 409-413 подключены соответственно к первому - (n-1)-у разрядам информационного входа 422, первые входы этих мультиплексоров подключены соответственно к первому - (n-1)-у разрядам вычитателя 406, а управляющие входы - соответственно к первому - (n-1)-у выходам группы элементов ИЛИ 408. Первые входы логических И элемента 2 И-nИЛИ 416 подключены к нулевому - (n-1)-у разрядам входа 422, а вторые входы - соответственно к первому - n-у выходам дешифратора 407. Информационные (D) входы D-триггеров 417 и 414 подключены соответственно к выходу ИЛИ элемента 2И-ИЛИ 416 и первому выходу регистра 415, тактовые входы - к входу 403, а входы установки в логический "0" (инверсные) - к логической "1". Первый вход элемента 2ИЛИ-НЕ 418 подключен к инверсному выходу триггера 417, а второй - к выходу элемента 2И-nИЛИ 416. Информационные D-входы триггеров 419-421 подключены соответственно к выходу логического элемента 2ИЛИ-НЕ 418 и выходам триггеров 419, 420, тактовые входы - к входу 403. Информационные первый - n-й входы регистра 415 подключены соответственно к первому (нулевой разряд) выходу вычитателя 406 и выходам мультилексоров 409-413, тактовый вход регистра 415 подключен к входу 403. Первый выход 316 узла 354 подключен к выходу триггера 414, а второй выход 424 (векторный) - соответственно к первому - n-у выходам регистра 415. Выход 425 (третий) подключен к выходу триггера 421.

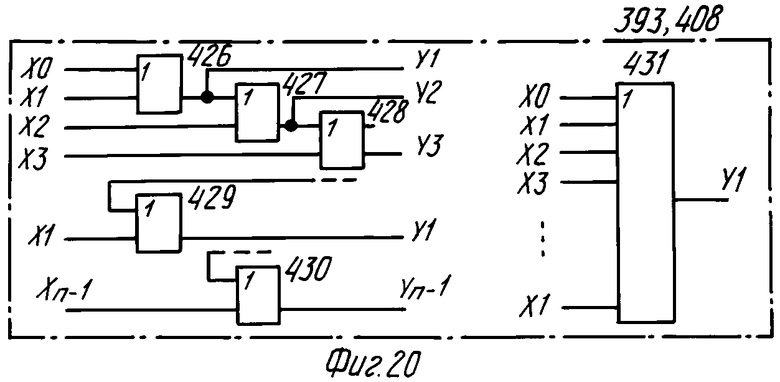

На фиг.20 приведена схема группы элементов ИЛИ 393 (408). Схема состоит из n-1 логических двухвходовых элементов ИЛИ 426-430. Схема имеет n входов и n-1 выходов.

Первый и второй входы элемента ИЛИ 426 подключены к первому и второму входам группы соответственно, первый и второй входы элемента ИЛИ 427 - к выходу предыдущего (426) и следующему входу группы (третьему) соответственно, входы третьего элемента ИЛИ 428 подключены к выходу второго элемента ИЛИ 427 и четвертому входу группы соответственно, входы i-го элемента ИЛИ 429 подключены соответственно к выходу (i-1)-го элемента ИЛИ и (i+1)-у входу группы и т.д., входы (n-1)-го элемента ИЛИ 430 подключены к выходу предыдущего (n-2)-го элемента ИЛИ и n-у входу всей схемы. Первый - (n-1)-й выходы группы подключены соответственно к выходам первого (426) - n-го (430) элементов ИЛИ. По существу, по каждому i-у выходу группа элементов ИЛИ представляет собой (i+1)-входовый элемент ИЛИ 431.

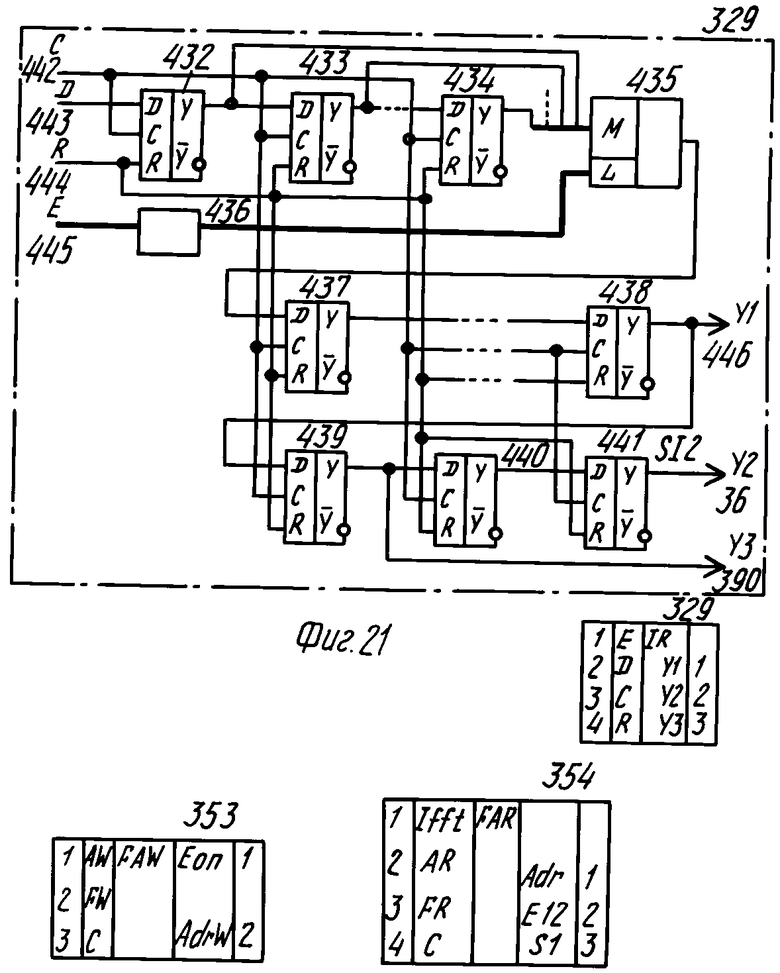

На фиг. 21 представлена схема узла 329 задержки. Схема состоит из n+3 D-триггеров 432-434, 437-441, а также шифратора 436 и мультиплексора 435. Входами схемы являются первый (векторный) 445, второй, информационный 443, третий тактовый 442 и четвертый установочный 444. Выходов схемы задержки три: выход 446 (первый), выход 36 (второй) и выход 390 (третий).

Информационные входы (D) D-триггеров 432-434 и 437-441 подключены соответственно к входу 443, выходам триггеров 432, 433,..., выходу мультиплексора 435 и выходам триггеров 437,...,438-440, тактовые входы - к тактовому входу 442, а установочные входы - к входу 444. Информационные входы (М) мультиплексора 435 подключены к выходам триггеров 432, 433,...,434, а вход шины управления (L) - к выходу шифратора 436, входом которого является входная шина 445. Первый выход узла подключен к выходу 446 триггера 438, второй 36 - к выходу триггера 441, а третий 390 - к выходу триггера 439.

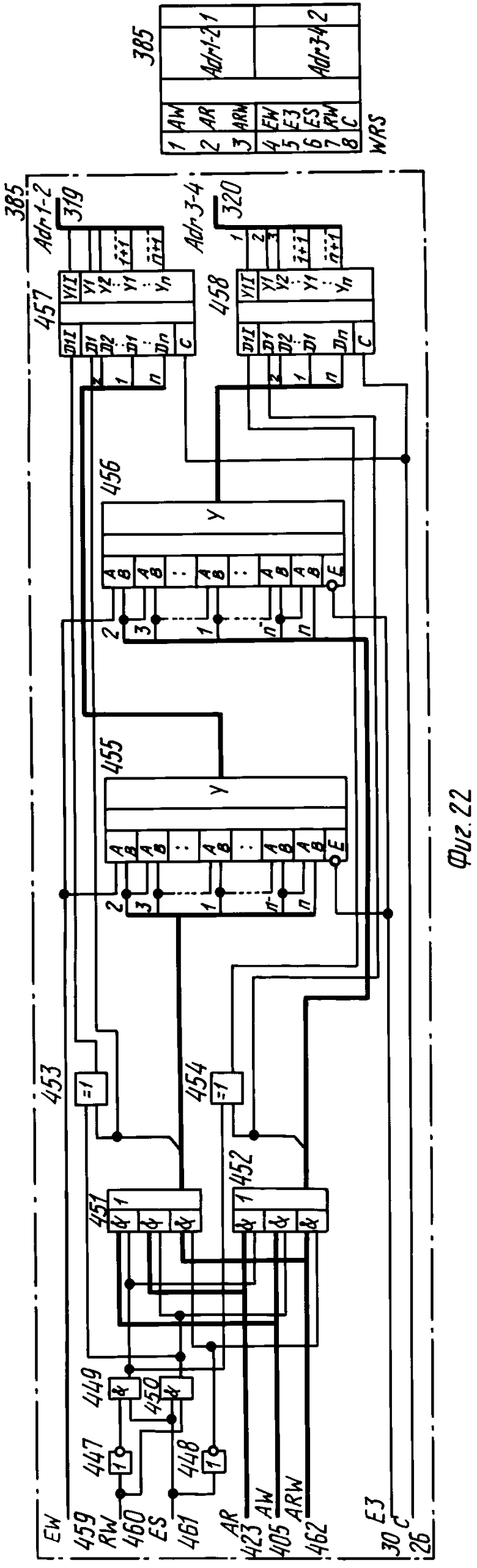

На фиг. 22 представлена схема узла 385 переключения. Схема состоит из двух элементов НЕ 447 и 448, элементов 2И 449 и 450, элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 453 и 454, двух групп элементов 2И-3ИЛИ 451 и 452, двух (n-1)-канальных мультиплексоров 455 и 456 и двух регистров 457 и 458. Входами узла являются первый информационный 405 (первый векторный), второй информационный 423 (второй векторный), третий информационный 462 (третий векторный), вход переключения адресного пространства 459 (четвертый), вход смещения разрядов 30 (пятый), второй управляющий вход 461 (шестой), первый управляющий вход 460 (седьмой) и тактовый вход 26 (восьмой). Выходами узла 385 являются векторные выходы первый 321 и второй 322.

Входы элементов НЕ 447 и 448 подключены соответственно к входам 460 и 461. Входы элемента 2И 449 подключены к выходу элемента НЕ 447 и входу 461, а первый и второй входы элемента 2И 450 - к входам 460 и 461. Первый и второй входы первых логических И группы элементов 2И-3ИЛИ 461 подключены соответственно к входу 404 и выходу логического элемента 2И 449, первый и второй входы вторых логических И этой группы подключены соответственно к векторному входу 424 и выходу логического элемента 2И 450, а первый и второй входы третьих логических И группы элементов 2И-3ИЛИ 451 подключены соответственно к векторному входу 462 и выходу элемента НЕ 448. Первый и второй входы вторых логических И группы элементов 2И-3ИЛИ 452 подключены соответственно к векторному входу 404 и выходу логического элемента 2И 449, первый и второй входы первых логических И этой группы подключены соответственно к векторному входу 424 и выходу логического элемента 2И 450, а первый и второй входы третьих логических И группы элементов 2И-3ИЛИ 452 подключены соответственно к векторному входу 462 и выходу элемента НЕ 448. Первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 453 подключены соответственно к выходу элемента 2И 450 и первому выходу группы элементов 2И-3ИЛИ 451, а входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 454 подключены соответственно к выходу элемента 2И 449 и первому выходу группы элементов 2И-3ИЛИ 452. Первый вход первого канала мультиплексора 455 подключен к входу 459, а первые входы остальных (второго - (n-1)-го) каналов этого мультиплексора подключены, соответственно к второму - (n-1)-у выходам группы элементов 2И-3ИЛИ 451, вторые входы указанных каналов мультиплексора 455 подключены соответственно к второму - n-у выходам группы элементов 2И-3ИЛИ 451. Первый вход первого канала мультиплексора 456 подключен к входу 459, а первые входы остальных (второго - (n-1)-го) каналов этого мультиплексора подключены соответственно к второму - (n-1)-у выходам группы элементов 2И-3ИЛИ 452, вторые входы указанных каналов мультиплексора 456 подключены соответственно к второму - n-у выходам группы элементов 2И-3ИЛИ 452. Первый вход регистра 457 подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 453, второй вход - к первому выходу группы элементов 2И-3ИЛИ 451, а остальные информационные входы (третий - (n+1)-й) подключены соответственно к первому - (n-1)-у выходам мультиплексора 455, тактовый вход регистра 457 подключен к входу 26. Первый вход регистра 458 подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 454, второй вход - к первому выходу группы элементов 2И-3ИЛИ 452, а остальные информационные входы (третий - (n+1)-й) подключены соответственно к первому - (n-1)-у выходам мультиплексора 456, тактовый вход регистра 458 подключен к входу 26. Первый (векторный) выход 319 узла переключения подключен к первому - (n+1)-у выходам регистра 457, второй (векторный) выход 320 - к первому - (n+1)-у выходам регистра 458.

На фиг. 23 представлена схема блока 10 формирования приращения порядка чисел. Схема состоит из двух элементов 2ИЛИ 463 и 464, двух элементов 2И-НЕ 465 и 466, двух элементов НЕ 467 и 473, двух групп элементов 2И-НЕ 488 и 489, двух элементов НЕ 467 и 473, двух групп элементов 2И-НЕ 488 и 489, двух групп элементов 2-2И-2ИЛИ 468 и 472, триггера 474, вычитателя 471, девяти регистров 469, 470, 476-478, 482-484 и 490, трех D-триггеров 485-487, демультиплексора 475, а также трех сумматоров 479-481. Входами блока 10 являются вход 15 (первый) начальной установки, вход 29 (второй) установки режима конвейерной или однопроцессорной обработки, вход 18 (третий) признака текущего изменения размера ДПФ, вход 20 (четвертый векторный) порядка входных чисел, вход 323 (пятый) признака переполнения, вход 36 признака считывания очередного частичного спектра промежуточного преобразования Фурье (шестой), вход 389 признака окончания ДПФ в однопроцессорном вычислителе (седьмой), вход 386 начала обработки присоединяемого частичного спектра при удвоении размера преобразования Фурье на данном этапе (восьмой), входы 388 и 387 соответственно, первого и второго признаков начала каждого этапа преобразования Фурье (девятый и десятый), вход 390 признака считывания приращения порядка чисел выходного частичного спектра (одиннадцатый), а также тактовый (двенадцатый) вход. Выходами блока 10 являются векторные первый 321, второй 322 и третий 37.

Первые входы элементов 2ИЛИ 463 и 464 подсоединены соответственно к входу 386 и выходу элемента 2ИЛИ 463, а вторые входы этих элементов - к входу 18. Первые входы элементов 2И-НЕ 465 и 466 подсоединены соответственно к выходам элементов 2ИЛИ 464 и 463, а вторые их входы - к входу 388. Первые входы первого логического И группы элементов 2-2И-2ИЛИ 468 подсоединен к входу 20, а второго логического И этой же группы - к выходу регистра 484, вторые входы логических И этих групп элементов соединены вместе и подсоединены соответственно к входу 29 и выходу элемента НЕ 467. Вход элемента НЕ 467 подключен к входу 29. Информационные (D) входы регистров 469 и 470 подключены к выходу группы элементов 2-2И-2ИЛИ 468, тактовые входы этих регистров подсоединены соответственно к выходам элементов 2И-НЕ 465 и 466, а установочные - к входу 15. Первый и второй входы (уменьшаемого и вычитающего) вычитателя 471 подключены соответственно к выходам регистров 470 и 469. Первые входы первого и второго логических И группы элементов 2-2И-2ИЛИ 472 подключены к выходам регистров 470 и 469 соответственно, а вторые входы соединены вместе и подсоединены соответственно к выходу знакового разряда вычитателя 471 и выходу элемента НЕ 473. Вход элемента НЕ 473 подключен к выходу знакового разряда вычитателя 471. Вход установки в логическую "1" RS-триггера 474 подключен к входу 323, а вход установки в логический "0" - к входу 390. Информационный векторный вход демультиплексора 475 подключен к выходу абсолютного значения разности вычитателя 471, а управляющий вход - к выходу знакового разряда. Информационные входы регистров 476-478 подключены соответственно к первому, второму выходам демультиплексора 475 и выходу группы элементов 2-2И-2ИЛИ 472, тактовые входы всех указанных регистров подключены к входу 387, а входы установки в логический "0" - к входу 389. Первые входы сумматоров 479 и 480 подключены соответственно к выходам регистров 476 и 477, а вторые входы - к выходу триггера 485. Первый вход сумматора 481 подсоединен к выходу регистра 478, а второй - к выходу триггера 486. Информационные (D) входы регистров 482-484 подключены к выходам сумматоров 479-481 соответственно, их тактовые входы - соответственно к выходу триггера 487 и входу 36, а входы установки в логический "0" всех указанных регистров - к входу 15, D-входы триггеров 485-487 подсоединены соответственно к выходу триггера 474, выходу триггера 485 и входу 390. Тактовые входы (С) всех триггеров подсоединены к входу 26. Первый и второй входы элемента 2И-НЕ 488 подсоединены к выходу регистра 484 и входу 29 соответственно, первый и второй входы группы элементов И-НЕ 489 подключены к выходу группы элементов 2И-НЕ 488 и входу 29 соответственно. Информационный (D) вход регистра 490 подключен к выходу регистра 484, его тактовый вход - к входу 36, а входы установки в логическую "1" и "0" подключены соответственно к входам групп элементов 2И-НЕ 489 и 488. Первый выход 321 блока 10 подключен к выходу регистра 482, второй выход 322 - к выходу регистра 483, а третий 37 - к выходу регистра 490.

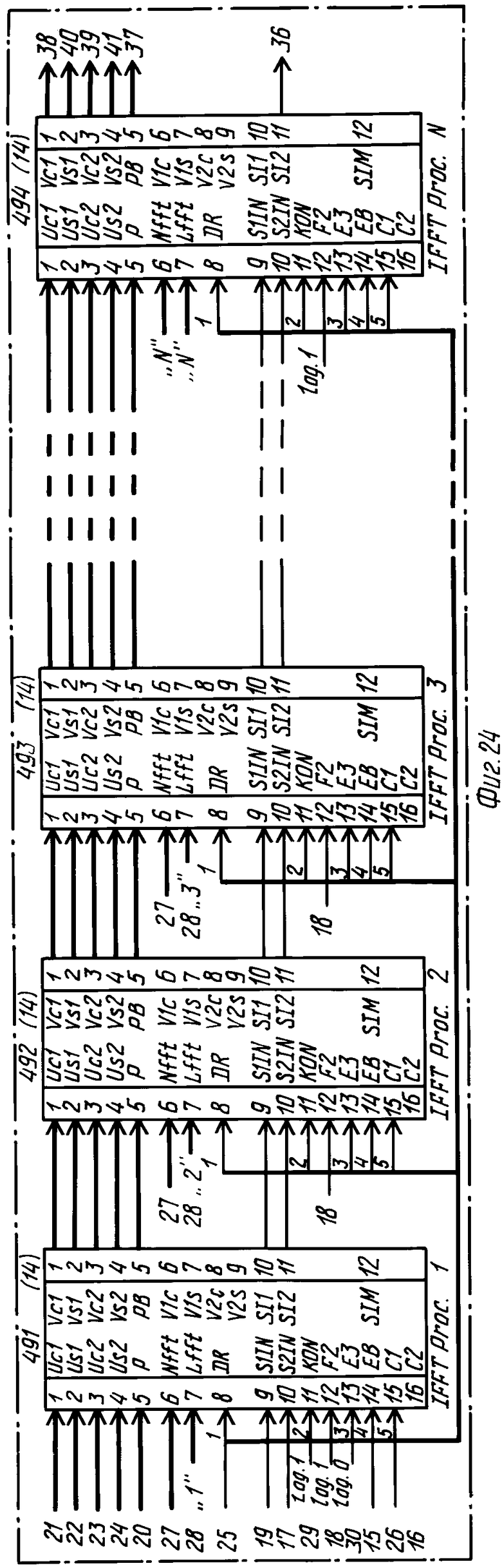

На фиг.24 представлена схема конвейерного вычислителя БПФ. Схема предназначена для нахождения ДПФ, размерность которого равняется два в степени N, где N - количество этапов БПФ. Схема состоит из N устройств 14, соединенных последовательно (элементы 491-494). Входами вычислителя являются информационные векторные 21-24 (первый - четвертый входы элемента 491), по которым поступают мантиссы комплексных соответственно нечетных и четных отсчетов сигнала, общий порядок отсчетов Р поступает с векторного входа 20 (пятый вход процессора 491). По входу 27 (шестой векторный вход процессора 491) поступает объявленный для первого этапа размер БПФ. По входу 28 (седьмой векторный вход процессора 491) поступает двоичная единица в соответствии с номером этапа БПФ. По входу 25 (восьмой вход процессора 491) устанавливается режим прямого (DR = log 0) или обратного преобразования Фурье. По входу 19 (девятый вход устройства 491) поступают синхроимпульсы S1IN, а по входу 17 (десятый вход устройства 491) устанавливается "1" - сигнал включения конвейерного режима работы устройства 14. По входу 18 (двенадцатый вход процессора 491) устанавливается логическая "1" - сигнал запрета изменения размера БПФ на данном этапе. По входу 30 (тринадцатый вход устройства 491) поступает сигнал начальной установки. По входу 26 (пятнадцатый вход устройства 491) поступают тактовые импульсы С1.

Выходами конвейерного вычислителя БПФ являются выход четных (38 и 40) и нечетных (39 и 41) комплексных спектральных отсчетов (мантиссы - первый-четвертый выходы процессора 494). Выход общего порядка 37 - это пятый выход устройства 494. Выход 36 - это выход синхронизации начала каждого выходного спектра (одиннадцатый выход устройства 494).

Первый - пятый векторные входы устройств 492-494 (второй - N-й) соединены соответственно с первым-пятым выходами предыдущих (первого - (N-1)-го) устройств 14. Девятый и десятый входы этих устройств соединены с десятым и одиннадцатым выходами предыдущих к ним устройств 14. Шестые входы всех остальных устройств 14, кроме последнего 494, подсоединены аналогично устройству 491. На шестой вход последнего, N-го устройства 14 подается двоичный код числа N. На седьмой вход всех устройств 14 подается двоичный код в соответствии с номером этапа БПФ. Восьмой, одиннадцатый, тринадцатый, четырнадцатый и пятнадцатый входы всех устройств 14 подключены к соответствующим входам устройства 491. На двенадцатый вход последнего устройства 14 (494), который обслуживает N-й этап БПФ, подается логическая "1". На двенадцатые входы всех остальных устройств 14 подается логический "0" или логическая "1" в зависимости от того, изменяется или не изменяется на данном этапе БПФ объявленная размерность БПФ.

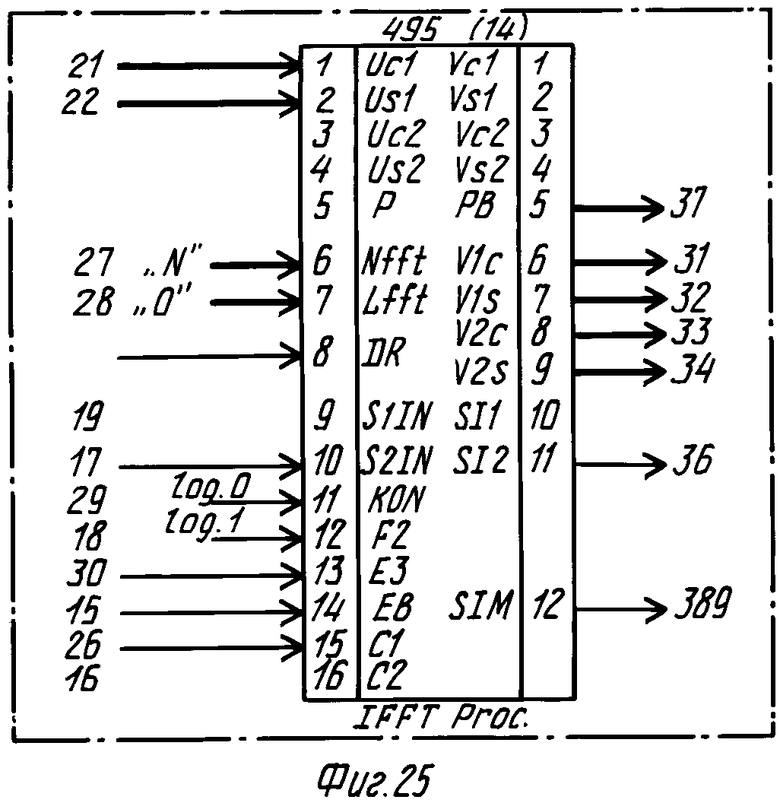

На фиг.25 представлена схема подключения арифметического устройства 14 в режиме однопроцессорного вычислителя с последовательной обработкой сигнала. Входами процессора для комплексных отсчетов сигнала (мантиссы) являются входы 21 и 22 - это первый и второй входы устройства 14 (495). Вход порядка (общий) - это вход 20 (пятый вход устройства 495). По входу 27 (шестой вход устройства 495) устанавливается размер БПФ. На входе 28 (седьмой вход устройства 495) устанавливается логический "0". На входе 25 (восьмой вход устройства 495) устанавливается режим прямого (DR = log.0) или обратного БПФ. По входу 17 (девятый вход устройства 495) устанавливается внешней (S2IN = log.0) или внутренней (S2IN = log.1) режим синхронизации. На входах 29 и 18 (одиннадцатый и двенадцатый входы устройства 495) устанавливаются соответственно логический "0" и логическая "1". Входы 30, 15 и 26 (тринадцатый - пятнадцатый входы устройства 495) являются входами соответственно внешней синхронизации, начальной установки и тактовый. Выходами однопроцессорного вычислителя 495 БПФ являются выходы четных (31 и 32) и нечетных (33 и 34) комплексных спектральных отсчетов (мантиссы - шестой - девятый выходы устройства 495). Выход 37 общего порядка - это пятый выход устройства 495. Выход 389 - это выход синхронизации начала обработки сигнала (выдачи выходного спектра) - двенадцатый выход устройства 495.

На фиг.26 представлена схема подключения арифметического устройства 14 (496) в режиме однопроцессорного вычислителя с параллельной обработкой сигнала. Входами устройства 496 для комплексных отсчетов сигнала (мантиссы) являются входы 21 и 22 - первый и второй входы устройства 496. Вход порядка (общий) - это вход 20 (пятый вход устройства 496). По входу 27 (шестой вход устройства 496) устанавливается размер БПФ. На входе 28 (седьмой вход устройства 496) устанавливается логический "0". На входе 25 (восьмой вход устройства 496) устанавливается режим прямого (DR=log.0) или обратного БПФ. По входу 17 (десятый вход устройства 496) устанавливается S2IN = log.1). На входах 29, 18 и 30 (одиннадцатый-тринадцатый входы устройства 496) устанавливаются соответственно логический "0", логическая "1" и логическая "1". Входы 15, 26 и 16 (четырнадцатый, шестнадцатый - входы устройства 496) являются входами соответственно начальной установки и первый и второй тактовые. Выходами однопроцессорного вычислителя 496 БПФ являются выходы четных (31 и 32) и нечетных (33 и 34) комплексных спектральных отсчетов (мантиссы - шестой - девятый выходы устройства 496). Выход 37 общего порядка - это пятый выход устройства 496. Выход 389 - это выход признака окончания (начала следующей) обработки сигнала (выдачи выходного спектра) - двенадцатый выход устройства 496.

Алгоритм работы устройства можно обосновать следующим образом.

Пусть, например, требуется найти 2N-точечное ДПФ, т.е. вычислить по известной последовательности x(n), n = 0, 2N-1, спектр X(k), который выражается формулой

X(k) = x(n)e

x(n)e . (1)

. (1)

Разбивают правую часть формулы (1) на две суммы

X(k) = x(n)e

x(n)e +

+  x(n)e

x(n)e и получают во второй сумме n = n1 + N, тогда

и получают во второй сумме n = n1 + N, тогда

X(k) = x(n)e

x(n)e + e-jπk

+ e-jπk x(n1+N)e

x(n1+N)e =X1(k) + X2(k)e-jπk.

=X1(k) + X2(k)e-jπk.

(2) X1(k) и X2(k) в (2) представляют собой 2N-точечные ДПФ последовательности из 2N членов, в которых последние N членов взяты равными нулю.

Пусть k = 2l, l =  . Рассматривая теперь только четные члены X1(k) и X2(k), т.е. X1(l) и X2(l), обнаруживают, что

. Рассматривая теперь только четные члены X1(k) и X2(k), т.е. X1(l) и X2(l), обнаруживают, что

X1(l) = x(n)e

x(n)e и

и

X2(l) =  x(n1+N)e

x(n1+N)e (3) являются N-точечными ДПФ соответственно первой и второй половин исходной последовательности x(n).

(3) являются N-точечными ДПФ соответственно первой и второй половин исходной последовательности x(n).

Нечетные члены последовательностей X1(k) и X2(k) можно вычислить, например, методом интерполяции.

Следует заметить, что нахождение нечетных членов указанных выше последовательностей методом непосредственной интерполяции X1(l) и X2(l) сопряжено с большими погрешностями вследствие того, что не выполняются условия теоремы отсчетов Котельникова-Нейквиста.

Действительно, рассматривая обе половины x(n) как спектры последовательностей X1(l) и X2(l), можно отметить, что максимальная частота каждого такого спектра равняется N-1, что непосредственно следует из выражения (3). Согласно выводам указанной теоремы максимальная частота спектра из N отсчетов не может превышать величины N/2.

Для того, чтобы соблюдались условия теоремы Котельникова-Найквиста, необходимо вычислять ДПФ в симметричных пределах, т.е.

X1(l)⊂ = (n+N/2)e

(n+N/2)e , n=-

, n=- , (4) или, положив n = n1 - N/2, получают

, (4) или, положив n = n1 - N/2, получают

X1(l)⊂ = x(n1)e

x(n1)e = ejπlX1(l). (5)

= ejπlX1(l). (5)

После проведения интерполяции учитывая связь между k и l, можно написать

X1(k)⊂= e X1(k),

X1(k),

X2(k) = e X2(k). (6)

X2(k). (6)

Решая уравнения (6) относительно X1(k) и X2(k), получают

X1(k) = e X1(k)⊂;

X1(k)⊂;

X2(k) = e X2(k)⊂.

X2(k)⊂.

Теперь находят искомый спектр

X(k) = e X1(k)⊂+ e

X1(k)⊂+ e X2(k)⊂. (7)

X2(k)⊂. (7)

Умножив выражение (7) на e jπk , можно снова перейти к симметричной форме вычисления ДПФ, приспособленной для интерполяции:

X(k)⊂= X(k) ejπk = e

X(k) ejπk = e X1(k)⊂+ e

X1(k)⊂+ e X2(k)⊂ . (8)

X2(k)⊂ . (8)

Полностью симметричная форма в выражении (4) получается, если сместить числовую ось еще на 0,5:

X(l) = X(n+N/2-0.5) e

X(n+N/2-0.5) e , (9) при этом последовательность X(l) имеет наименьшую (для ненулевых x(n) величину спектра (N/2 - 0,5) и наиболее приспособлена для нахождения промежуточных значений методом интерполяции. Значения спектра, рассчитанные по выражению (9) и отличающиеся по аргументу на N, равным по величине и противоположны по знаку, т.е. периодичность X(l) составляет 2N. Периодичность спектральных отсчетов, рассчитанных в соответствии с выражением (4) или (1), равна N.

, (9) при этом последовательность X(l) имеет наименьшую (для ненулевых x(n) величину спектра (N/2 - 0,5) и наиболее приспособлена для нахождения промежуточных значений методом интерполяции. Значения спектра, рассчитанные по выражению (9) и отличающиеся по аргументу на N, равным по величине и противоположны по знаку, т.е. периодичность X(l) составляет 2N. Периодичность спектральных отсчетов, рассчитанных в соответствии с выражением (4) или (1), равна N.

Для того, чтобы увеличить точность нахождения интерполированных значений, а следовательно, и точность вычисления ДПФ, можно перейти к вычислениям при удвоенной частоте Котельникова-Найквиста ( ε = 2). В этом случае при вычислениях X1'(l) и X2'(l) необходимо определять ДПФ размера не N, а 2N, дополняя отсутствующие отсчетны нулями. При этом X'(k) имеет размерность 4N, k =  , a l =

, a l =

При вычислении X1'(l) и X2'(l) ( ε = 2) добавляют нули симметрично к началу и концу соответствующих половин исходной последовательности x(n). При этом для получения симметричной формы, удобной для интерполяции, пользуются выражением (9).

После проведения интерполяции составляют X1'(k)c и X2'(k)c. Для нахождения X'(k)с необходимо X1'(k)c и X2'(k)c преобразовать так, чтобы они соответствовали ДПФ со смещением отсчетов внутри интервала -2N + 2N на ±N/2 относительно центра. Для этого X1'(k) и X2'(k) необходимо умножить соответственно на e jπk/4 и e -jπk/4 . Складывая затем полученные частичные спектры, получают

X′(k)⊂= e X

X (k)⊂+ e

(k)⊂+ e X

X (k)⊂. (10)

(k)⊂. (10)

Выражения (8) и (10) можно объединить, учитывая величину ε.

X(k)⊂= e X1(k)⊂+ e

X1(k)⊂+ e X2(k)⊂. (11)

X2(k)⊂. (11)

Для нахождения нечетных значений спектров Xi(k)с по известным из Xi(l)c четным значениям полагают, что исходная последовательность x(n), расположенная симметрично относительно начала координат, совпадает с выборочными значениями периодической функции xp(t) в точках t = (-N/2 + n)T + 0,5T, где n =  , Т - период дискретизации x(n). Интервал периодичности xp(t) равняется ε NT. Пусть также спектр функции xp(t) ограничен величиной 1/2T. В этом случае он состоит из ε N спектральных составляющих (гармоник), каждая из которых численно равна соответствующей дискретной спектральной составляющей X(l). Удвоить количество спектральных составляющих за счет нахождения промежуточных значений можно, увеличив в два раза интервал периодичности функции xp(t). Образуют новую периодическую функцию xp'(t) =xp(t)H(t), где H(t) - функция с интервалом периодичности 2 ε NT, спектром, ограниченным величиной 1/2Т, и значениями, равными единице в точках t = (-N/2 + n + 0,5)Т и нулю в точках t = (-N/2 ± εN + n + 0,5)Т для n =

, Т - период дискретизации x(n). Интервал периодичности xp(t) равняется ε NT. Пусть также спектр функции xp(t) ограничен величиной 1/2T. В этом случае он состоит из ε N спектральных составляющих (гармоник), каждая из которых численно равна соответствующей дискретной спектральной составляющей X(l). Удвоить количество спектральных составляющих за счет нахождения промежуточных значений можно, увеличив в два раза интервал периодичности функции xp(t). Образуют новую периодическую функцию xp'(t) =xp(t)H(t), где H(t) - функция с интервалом периодичности 2 ε NT, спектром, ограниченным величиной 1/2Т, и значениями, равными единице в точках t = (-N/2 + n + 0,5)Т и нулю в точках t = (-N/2 ± εN + n + 0,5)Т для n =  .

.

Представляют H(t) в виде суммы гармоник. Учитывая симметричность, можно написать

H(t) = 0.5 + Amcos(Π(2m-1)t/εNT) .

Amcos(Π(2m-1)t/εNT) .

(12)

В выражении (12) имеются только нечетные гармоники с нулевой фазой.

Находят спектр xp'(t):

X′(ω) =  xp(t)H(t)e-jωtdt. (13)

xp(t)H(t)e-jωtdt. (13)

Представляют H(t) через обратное преобразование Фурье:

H(t) =

+

+

-

- +

+ +

+  ejωtdω.

ejωtdω.

(14)

После подстановки выражения (14) в уравнение (13) получают

X′(ωt) =

+

+

-

- +

+  +

+

+

X(n)

X(n) t+

t+  T-nT

T-nT e

e dtdω1. (15)

dtdω1. (15)

После вычислений в выражении (15) получают

X′(ωT) =  X′(ωT)+

X′(ωT)+

X

X T-

T-  + X

+ X T-

T-  .

.

Как и ранее, полагают ωT =  и получают выражение для расчета искомых спектральных составляющих:

и получают выражение для расчета искомых спектральных составляющих:

X′(k) = A

A X′(k-2m+1)+X′(k+2m-1)

X′(k-2m+1)+X′(k+2m-1) , k=

, k= . (16)

. (16)

Из выражения (16) следует, что нечетные спектральные составляющие могут быть вычислены из четных путем суммирования взвешенных значений и, наоборот, четные составляющие можно аналогично вычислить через нечетные.

Из выражения (16) следует также, что для нахождения точных нечетных, т. е. промежуточных, значений спектра число взвешивающих множителей М необходимо взять равным N/2, а сами взвешивающие множители Аm - в соответствии с выражением (12). При этом функции H(t) отличается от прямоугольной, но в точках определения x(n) она все равно на интервале -N/2 - N/2 равна единице, а на интервале N/2 - 3N/2 - нулю и т.д.

При другом выборе М (M <Në2) вычисленные X'(k отличаются от истинных и появляются ошибки при нахождении промежуточных спектральных отсчетов.