1

Изобретение относится к вычислительной технике и может быть использовано в качестве многопрограммног циклического переключателя каналов, управляемого генератора кодовых: по- следовательностей и делителя частоты с переменным коэффициентом деления в дискретных системах автомати- ческо1 о управления и обработки цифровой информации.

Цель изобретения - расширение функциональных возможностей.

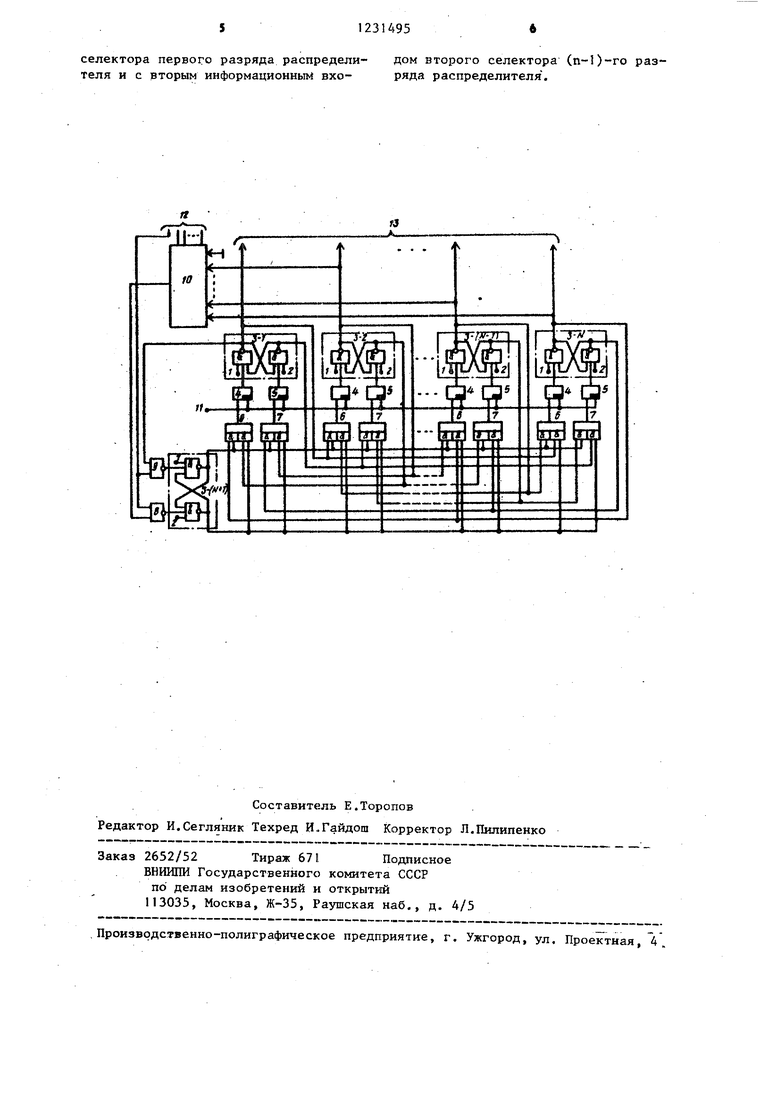

На чертеже показан N-разрядный распределитель импульсов.

Распределитель импульсов содержи входы 1 установки, входы 2 сброса, асинхронные КЗ-триггеры 3, формирователи 4 и 5 импульсов, селекторы 6 и 7, элементы И-НЕ 8 и 9, мультиплексор 10, тактовый вход 11, группу 12 входов задания режимов,-. группу 13 вьпсодов.

N-разрядный распределитель импульсов работает следующим образом,

.Перед началом работы распредели- теля в любом из возможных режимов переключения его основные N-триггер по входам 1 и 2 устанавливаются в пложения, соответствующие одной из кодовых комбинаций данного режима переключения, а на его группе 12 входов задания режимов устанавливаеся соответствующая комбинация еди- ничных и нулевых логических уровней потенциалов, Б зависимости от тре- буемого направления переключения

выходных каналов (М+1)-ьш управляющий триггер по входам 1 и 2 устанав .ливается в .единичное или нулевое логическое) положение.

При поступлении по тактовом входу 11 тактовых импульсов они проход через те формирователи 4 и 5 импульсов-, на информационных входах которых в данных тактах имеются единичн логические потенциалы. От их задних фронтов (спадов) в соответствующих формирователях 4 и 5 формируются нулевые короткие импульсы, которые поступают к определенным. (единич1ным или нулевым.) информационным- входам разрядных асинхронных триггеров,и в зависимости от заданной циклограммы переключения при данном режиме под- тверждают их первона чальные состояния или же переключают в противоположные состояния.

5 0

15 ю 5

5

0

0

В режиме прямого направления поочередного переключения выходных каналов распределителя (К+1)-Ый триггер по входам 1 и 2 устанавливается в единичное логическое состояние. В зависимости от требуемого числа едии;иц, потактно сдвигаемых по разрядам кольцевого распределителя, соответствующая группа основных триг- геров также по входам i и 2 устанавливаются в единичные состояния, а остальные триггеры - в нулевые состояния. Ко всем входам группы 12 входов задания режима прикладываются нулевые логическое потенциалы. Благодаря этому элементы И-БЕ 8 и 9 запираются по вторым входам и независимо от логических по-тенциалов переключаемых выходных каналов распределителя обеспечивают неизменное исходнЬе логическое состояние управляющего (N+l)-ro триггера. При подаче тактовых импульсов ко входу П обеспечивается поочередный кольцевой сдвиг вправо записанных в смежных разрядах триггеров логических единиц.

Изменение числа логических единиц в сдвигаемых кодовых комбинациях осуществляется изменением исходных состояний тригге.ров, т,е. изменением числа записанных в разрядах единиц.

кольцевого сдвига предварительно записанных в основных триггерах распределителя кодовьге наций в обратном направлении переключения выходных -каналов создаются при установке управляющего(К+1)- го триггера в нулевое исходное состояние ,

Рдя создания автоматического переключения режимов к первому управ- ляюш;ему входу группы 12 прикладывается единичный логический потенциал. Это позволяет элементам И-БЕ 8 и 9 управлять процессом автоматического реверсирования управляющего (N+l)-ro триггера по единичным сигналам, поочередно выдаваемым от выхода первого разряда распределителя импульсов и от выхода мультиплексора 10, А к адресным входам мульти- плексор-а 10 прикладывается набор логических нулевых и единичных по- тенпиал:ов, определяющий длину цикла переключения при данном режиме переключения.

Так, например, для обеспечения полных циклов кольцевой циркуляции

3

различных кодовых комбинаций по всей

.разрядности распределителя к адресным входам мультиплексора по входам 12 прикладывается набор логич ских потенциалов, обеспечивающий БЬ Зор последнего его информационного входа и тем самым подключение к его выходу прямого выхода триггера последнего разряда распределителя.

Для обеспечения сокращенных цик- лов различных кодовых комбинаций к адресным входам мультиплексора прикладываются соответствующие наборы логических потенциалов, обеспечиваю,щие подключение к его выходу выходов триггеров соответствующих разрядов.

Формула изобретения

N-разрядный распределитель импульсов , содержащий в каждом разряде триггер, два формирователя импульсов причем выходы первого и второго формирователей импульсов в каждом раз- ряде распределителя импульсов соединены соответственно с первым единичным и первым нулевым входами триггера, вторые единичные и вторые нулевые входы триггеров распределителя импульсов являются соответственно входами установки и входами сброса распределителя импульсов, прямые- выходы триггеров являются соответственно выходами.распределителя им- пульсов, тактовый вход которого соединен с синхровходами формирователей импульсов,отличающийся- тем, что, с целью расширения функциональных возможностей за. счет обес печения прямых и обратных направлений всех возможных N-тактных режимов переключения выходных каналов при переменном периоде, в распределитель введен мультиплексор, два ;элемента И-НЕ, дополнительный триггер, а в каждый разряд распределителя введены два селектора, -причем выходы первого и второго селекторов в каждом разряде, распределителя соединены с инфор- мадионными входами соответственно первого и второго формирователей импульсов, прямой выход дополнительного триггера соединен с первыми управляющими входами первых и вторых селекторов всех разрядов распределителя, вторые управляющие входы которых соединены с инверсным выходом

s

5

0

5 о 5 0

4954

дополнительного триггера, первый вход группы входов задания режимов распределителя соединен с первыми входами первого и второго элементов И-НЕ, прямой выход первого разряда распределителя соединен с первым информационным входом первого селектог- ра второго разряда распределителя, с вторым информационным входом первого селектора п-го разряда и со вторым входом первого элемента И-ЕЕ, выход которого соединен с первым единичным входом дополнительного триггег ра, первый нулевой вход которого соединен с выходом мультиплексора, группа управлякнцих входов которого соединена с входами со второго по (п+1)-й группь входов задания режимов распределителя, второй единичный и втог рой нулевой входы дополнительного триггера являются соответственно входами установки и сброса распределителя , первый информационный вход мультиплексора соединен с шиной нулевого потенциала распределителя, прямые выходы разрядов со второго по (п+1)-й распределителя соединены соответственно с первыми информационными входами первых селекторов последующих разрядов распределителя, с вторыми информационными входами первых селекторов предыдущих разрядов распределителя и с информационными входами со второго по (п-1)-й мультиплексора, прямой выход п-го

разряда распределителя соединен с первым информационным входом первого селектора первого разряда., с вторым информационным входом первого селектора (п-1)-го разряда и с п-м информационным входом мультиплексора,

инверсный выход первого разряда рас- I

пределителя соединен с первым информационным входом второго селектора второго разряда распределителя и с вторым информационным входом второго селектора п-го разряда распределителя, инверсные выходы разрядов

с второго .по (п-1)-й распределителя соединены соответственно с вторыми информационными входами первых селекторов предыдущих разрядов и с первыми информационными входами вторых селекторов последующих разрядов распределителя, инверсный выход п-го разряда распределителя соединен с первым информационным входом второго

$1231495«

селектора первого разряда распредели- дом второго селектора (n-l)-ro раз- теля и с вторым информационным вхо- ряда распределителя .

| название | год | авторы | номер документа |

|---|---|---|---|

| @ -Разрядный распределитель импульсов | 1983 |

|

SU1150622A1 |

| Кольцевой счетчик | 1988 |

|

SU1538250A1 |

| Распределитель импульсов | 1982 |

|

SU1023315A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1982 |

|

SU1061230A1 |

| N-разрядный распределитель импульсов | 1980 |

|

SU960782A1 |

| Двухрежимный распределитель импульсов для управления трехфазным шаговым двигателем | 1981 |

|

SU1019571A1 |

| Трехканальный двухрежимный распределитель импульсов для управления шаговым двигателем | 1980 |

|

SU907753A1 |

| Устройство для многорежимного управления трехфазным шаговым двигателем | 1981 |

|

SU1001423A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1981 |

|

SU993428A1 |

| Устройство для многорежимного управления @ -фазным шаговым электродвигателем | 1982 |

|

SU1083321A1 |

Изобретение относится к области вычислительной техники и может быть использовано в качестве многопрограммного циклического переключателя каналов. Отличительной особенностью устройства является обеспечение переменного периода в прямом и обратном направлении. Целью изобретения является расширение функциональных возмо жностей. Поставленная цель достигается за счет введения мультиплексора, двух элементов И-НЕ дополнительного триггера и введения в каждый разряд распределителя селектора. I ил. со со СП

| N-разрядный распределитель импульсов | 1980 |

|

SU960782A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Распределитель импульсов | 1982 |

|

SU1023315A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-15—Публикация

1984-09-04—Подача