(54) ТРЕХКАНАЛЬНЫЙ ДВУХРЕЖИМНЫЙ РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ

1

Изобретение относится к электротехнике, а именно к автоматизированному электроприводу, и может быть использовано для двухрежимного управления трехфазным шаговым двигателем.

Известен реверсивный распределитель 5 импульсов для управления трехфазным шаговым двигателем, содержащий в каждом разряде RS-триггер, единичный и нулевой выходы которого соединены через элементы И с соответствуюш,ими входами преды- ю душего триггера для одной системы связей и последуюшего - для другой системы 1.

Недостатками этого распределителя являются сложность схемы и ее управления.

Наиболее близким к изобретению по тех- js нической сущности является трехканальный реверсивный распределитель импульсов для управления шаговым двигателем, содержащий в каждом разряде Dt триггер с тактовым, информационным и установочными входами, и подключенный к его ин- ° формационному входу логический элемент 2И-ИЛИ-НЕ, первые входы которого подключены к нулевым выходам триггеров смежных каналов, а вторые входы -

к двум шинам управления направлением переключения выходных каналов 2.

Недостатками этого известного устройства являются сложность управления и низкая надежность функционирования.

Цель изобретения - повышение надежности устройства.

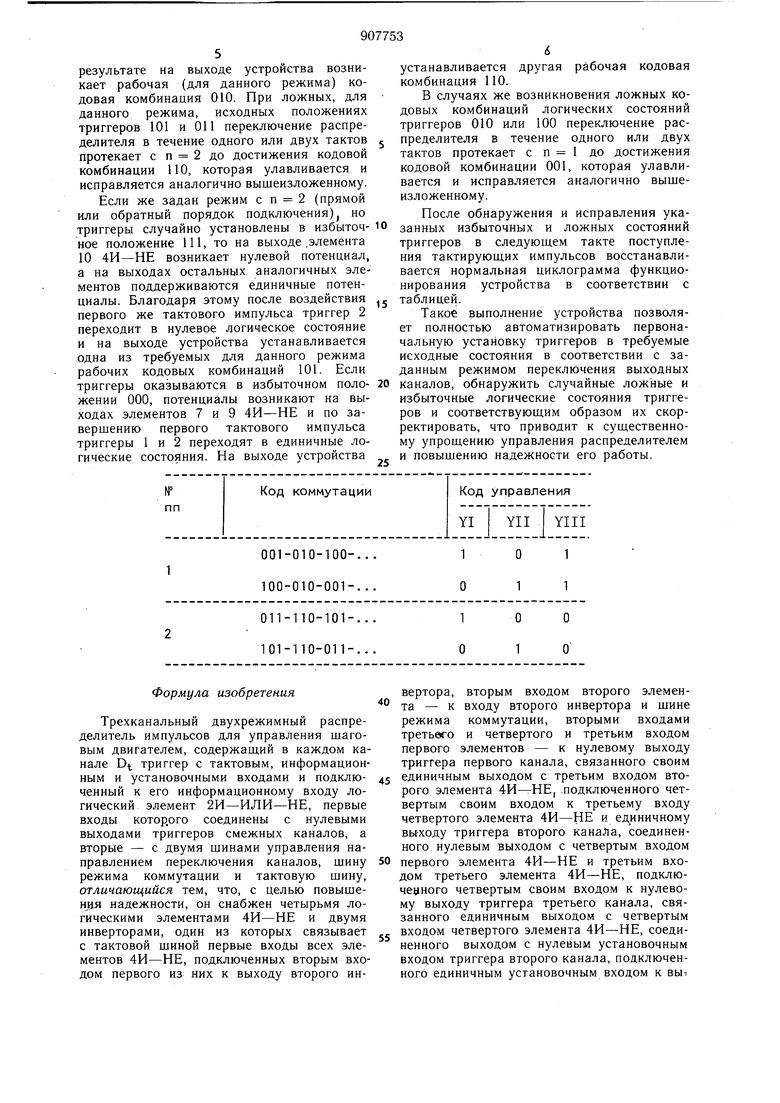

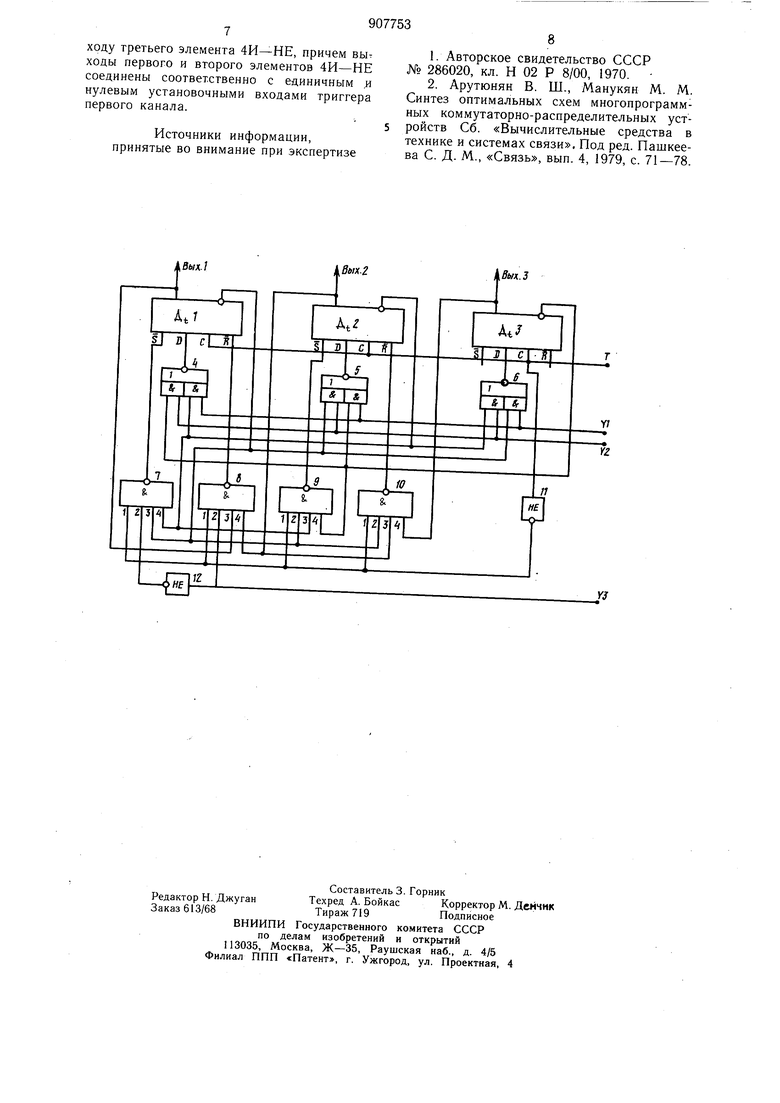

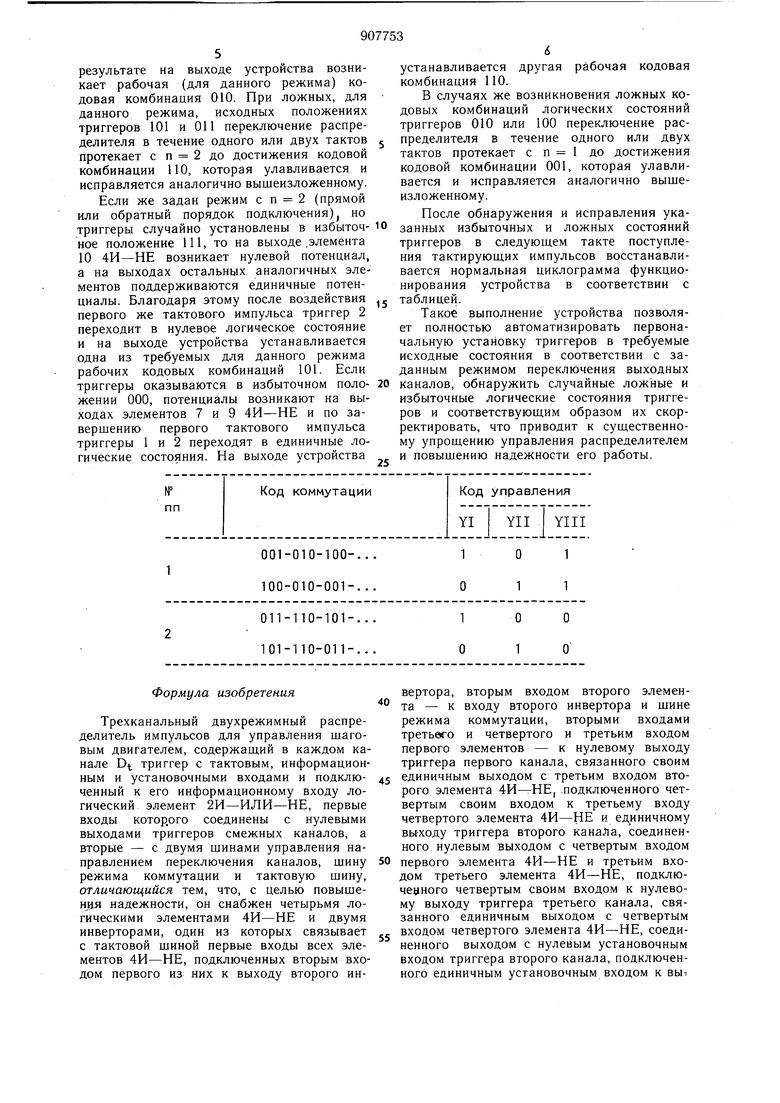

Поставленная цель достигается тем, что трехканальный двухрежимный распределитель импульсов снабжен четырьмя логическими элементами 4И-НЕ и двумя инверторами, один из которых,связывает с тактовой шиной первые входы всбх элементов 4И-НЕ, подключенных вторым входом первого из них к выходу второго инвертора, вторым входом второго элемента к входу второго инвертора и шине режима коммутации, вторыми входами третьего и четвертого и третьим входом первого элементов к нулевому выходу триггера первого канала, связанного своим единичным выходом с третьим входом второго элемента 4И-НЕ, подключенного четвертым своим входом к третьему входу четвертого элемента 4И-НЕ и единичному выходу триггера второго канала, соединенного нулевым выходом с четвертым входом первого элемента 4Й-НЕ и третьим входом четвертого элемента 4И-НЕ, подключенного четвертым своим входом к нулевому выходу триггера третьего канала, связанного единичным выходом с четвертым входом четвертого элемента 4И-НЕ, соединенного выходом с нулевым установочным входом триггера второго канала, подключенного единичным установочным входом к выходу третьего элемента 4И-НЕ, причем выходы первого и второго элементов 4И-НЕ соединены соответственно с единичным и нулевым установочными входами триггера первого канала. На чертеже представлена принципиальная схема трехканального реверсивного двухрежимного распределителя с блоком автоматической установки, самоконтроля и самокоррекции логических состоянии триггеров. Распределитель состоит из трех D триггеров 1-3, трех логических элементов 4-6 2Й-ИЛИ-НЕ, общей тактирующей шины Т, подключенной к тактовым входам всех триггеров, двух управляющих порядком (прямым и обратным) переключения щин У1 и У2, четырех логических элементов 7-10 4И-НЕ, двух элементов 11 и 12 НЕ и третьей щины управления числом одновременно возбуждаемых (режимом коммутации) фаз УЗ. Первые входы всех элементов 4И-НЕ соединены между собой и подключены через первый элемент 11 НЕ к общей тактируюц.1,ей шине Т. Второй вход второго элемента 8 4И-НЕ непосредственно и второй вход первого элемента 7 4И- НЕ через второй элемент 12 НЕ подключены к дополнительно введенной щине управления УЗ. Вторые входы третьего и четвертого элементов 9 и 10 4И-НЕ, третий вход первого элемента 7 4И-НЕ и третий вход второго элемента 8 4И-НЕ подключены соответственно к нулевому и единичному выходам триггера первого разряда Dt 1. Четвертый вход первого элемента 7 4И-НЕ, третий вход третьего элемента 9 4И-НЕ и четвертый вход второго элемента 8 4И-НЕ, третий вход четвертого элемента 10 4И-НЕ подключены соответственно к нулевому и единичному выходам триггера второго разряда Dt 2. Четвертые входы третьего и четвертого элементов 9 и 10 4И-НЕ, подключены соответственно к нулевому и единичному выходам триггера третьего разряда Dt 3. Устройство работает следующим образом. Перед созданием каждого из двух возможных симметричных режимов переключения фаз двигателя к управляющим щинам У1, У2 и УЗ устройства прикладываеется приведенный в таблице кодовый набор уровней потенциалов. После включения питания элементы памяти (Dt триггеры) в общем случае устанавливаются в произвольные логические состояния. При этом возможна установка триггеров 1-3 как в положения, соответствующие заданным режимам коммутации, так и в ложные и избыточные положения. Устройство обеспечивает нормальные режимы переключения выходных каналов если первоначальная установка D триггеров соответствует одному из кодовых комбинаций заданного по таблице режимов коммутации, т. е. если при заданном режиме п 1 триггеры устанавливаются в исходные состояния 001, 010 или 100 и при заданном режиме п 2 устанавливаются в исходные состояния 011, 110 или 101. Состояния триггеров, соответствующие кодам 000 и 111 для любого из нормальных режимов являются избыточными и исключаются для обеспечения нормальной работы устройства. Состояния же Oil, 101 или 110 для режима с п 1 и состояния 001, 010 или 100 для режима с п 2 являются ложными и должны быть скорректированы. Дополнительно введеннБге четыре логических элемента 7-10 4И-НЕ вместе с инверторами 11 и 12 и шиной управления УЗ выполняют функцию обнаружения ложных и избыточных логических состояний триггеров 1-3 и автоматической их установки в требуемые для каждого режима логические состояния после включения питания, а также после воздействия помех и наводок. Так, например, если задан режим с п 1 (прямой или обратный порядок переключения), но триггеры случайно установлены в избыточные состояния 111, то на выходах элементов 8 4И-НЕ и 10 4И-НЕ. возникают нулевые потенциалы, а на выходах элементов 7 4И-НЕ и 9 4И-НЕ поддерживаются единичные потенциалы. Благодаря этому после действия первого тактового импульса триггеры 1 и 2 переходят в нулевые логические состояния и на выходе устройства устанавливается одна из требуемых рабочих кодовых комбинаций данного режима переключения выходных каналов 001. Если триггеры оказываются в избыточном состоянии 000, то нулевой потенциал возникает на выходе элемента 9 4И-НЕ, который после воздействия тактирующего импульса приводит к переходу триггера 2 в единичное состояние, т. е. на выходе устройства устанавливается другая рабочая кодовая комбинация этого режима 010. При ложном для рассматриваемого режима состоянии триггеров 110 нулевой потенциал возникает на выходе элемента 8 4И-НЕ и после воздействия тактирующего -импульса триггер 1 переходит в нулевое состояние. В результате на выходе устройства возникает рабочая (для данного режима) кодовая комбинация 010. При ложных, для данного режима, исходных положениях триггеров 101 и 011 переключение распределителя в течение одного или двух тактов протекает с п 2 до достижения кодовой комбинации 110, которая улавливается и исправляется аналогично вышеизложенному. Если же задан режим с п 2 (прямой или обратный порядок подключения), но триггеры случайно установлены в избыточ- ю ное положение 111, то на выходе .элемента 10 4И-НЕ возникает нулевой потенциал, а на выходах остальных аналогичных элементов поддерживаются единичные потенциалы. Благодаря этому после воздействия первого же тактового импульса триггер 2 переходит в нулевое логическое состояние и на выходе устройства устанавливается одна из требуемых для данного режима рабочих кодовых комбинаций 101. Если триггеры оказываются в избыточном поло- 20 жении 000, потенциалы возникают на выходах элементов 7 и 9 4И-НЕ и по завершению первого тактового импульса триггеры 1 и 2 переходят в единичные логические состояния. На выходе устройства устанавливается другая рабочая кодовая комбинация ПО. В случаях же возникновения ложных кодовых комбинаций логических состояний триггеров 010 или 100 переключение распределителя в течение одного или двух тактов протекает с п 1 до достижения кодовой комбинации 001, которая улавливается и исправляется аналогично вышеизложенному. После обнаружения и исправления указанных избыточных и ложных состояний триггеров в следующем такте поступления тактирующих импульсов восстанавливается нормальная циклограмма функционирования устройства в соответствии с таблицей. Такое выполнение устройства позволяет полностью автоматизировать первоначальную установку триггеров в требуемые исходные состояния в соответствии с заданным режимом переключения выходных каналов, обнаружить случайные ложные и избыточные логические состояния триггеров и соответствующим образом их скорректировать, что приводит к существенному упрощению управления распределителем и повышению надежности его работы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухрежимный распределитель импульсов для управления трехфазным шаговым двигателем | 1981 |

|

SU1019571A1 |

| Устройство для многорежимного управления трехфазным шаговым двигателем | 1981 |

|

SU1001423A1 |

| Трехканальный трехрежимный распределитель импульсов для управления шаговым двигателем | 1984 |

|

SU1275734A1 |

| Устройство для многорежимного управления трехфазным шаговым двигателем | 1977 |

|

SU725184A1 |

| Кольцевой реверсивный распределитель уровней с нечетным числом каналов | 1987 |

|

SU1450104A1 |

| Трехканальный реверсивный распределитель уровней | 1984 |

|

SU1226648A1 |

| @ -Канальный распределитель | 1983 |

|

SU1166292A1 |

| Трехканальный реверсивный распределитель уровней | 1983 |

|

SU1142891A1 |

| Реверсивный счетчик | 1981 |

|

SU982201A1 |

| Распределитель | 1983 |

|

SU1088123A1 |

Формула изобретения

Трехканальный двухрежимный распределитель импульсов для управления шаговым двигателем, содержащий в каждом канале D триггер с тактовым, информационным и установочными входами и подключенный к его информационному входу логический элемент 2И-ИЛИ-НЕ, первые входы котор.ого соединены с нулевыми выходами триггеров смежных каналов, а вторые - с двумя шинами управления направлением переключения каналов, шину режима коммутации и тактовую шину, отличающийся тем, что, с целью повыщеHjiH надежности, он снабжен четырьмя логическими элементами 4И-НЕ и двумя инверторами, один из которых связывает с тактовой щиной первые входы всех элементов 4И-НЕ, подключенных вторым входом первого из них к выходу второго инвертора, вторым входом второго элемента - к входу второго инвертора и щине режима коммутации, вторыми входами третьего и четвертого и третьим входом первого элементов - к нулевому выходу триггера первого канала, связанного своим

5 единичным выходом с третьим входом второго элемента 4И-НЕ, .подключенного четвертым своим входом к третьему входу четвертого элемента 4И-НЕ и единичному выходу триггера второго канала, соединенного нулевым выходом с четвертым входом

первого элемента 4И-НЕ и третьим входом третьего элемента 4И-НЕ, подключеуного четвертым своим входом к нулевому выходу триггера третьего канала, связанного единичным выходом с четвертым входом четвертого элемента 4И-НЕ, соединенного выходом с нулевым установочным входом триггера второго канала, подключенного единичным установочным входом к вьь

7

ходу третьего элемента 4И-НЕ, причем выт ходы первого и второго элементов 4И-НЕ соединены соответственно с единичным и нулевым установочными входами триггера первого канала.

Источники информации, принятые во внимание при экспертизе

I Яш./

8

1 Авторское свидетельство СССР Яо 286020, кл. И 02 Р 8/00, 1970. 2. Арутюнян В. Ш., Манукян М. М. Синтез оптимальных схем многопрограммных коммутаторно-распределительных устройств Сб. «Вычислительные средства в технике и системах связи. Под ред. Пашкеева С. Д. М., «Связь, вып. 4, 1979, с. 71-78.

(Вт.З

8ых.2

Авторы

Даты

1982-02-23—Публикация

1980-06-10—Подача