Изобретение относится к импульсной технике и может быть использовано для предотвращения юза и буксования транснортного средства, например железнодорожного подвижного состава, с целью выделения сигнала, соответствующего скорости наиболее быстро или наиболее медленно вращающейся колесной пары.

Цель изобретения - повышение быстродействия устройства за счет уменьшения времени на обработку входного сигнала„

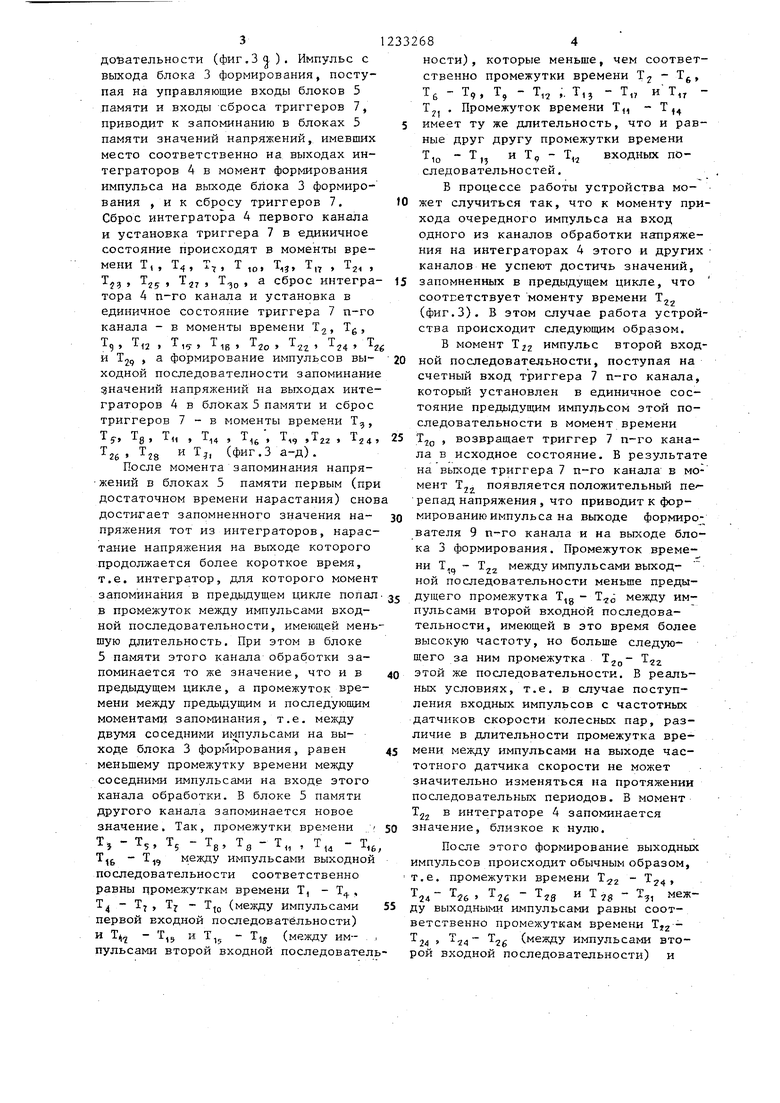

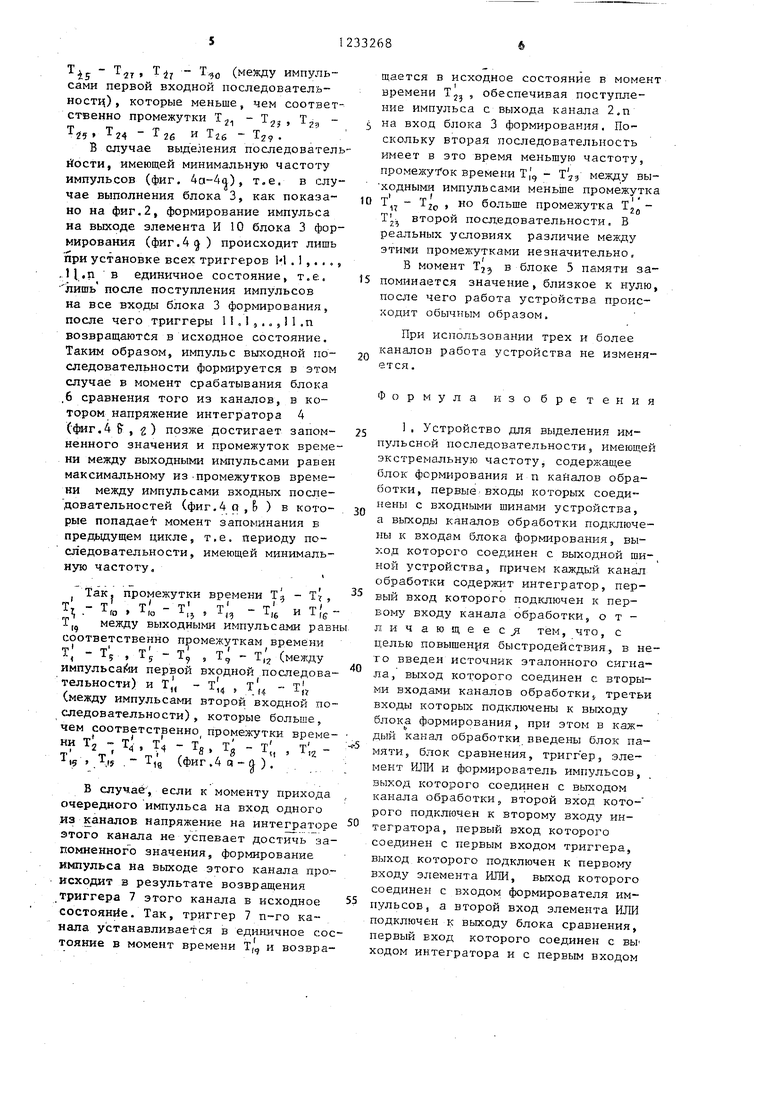

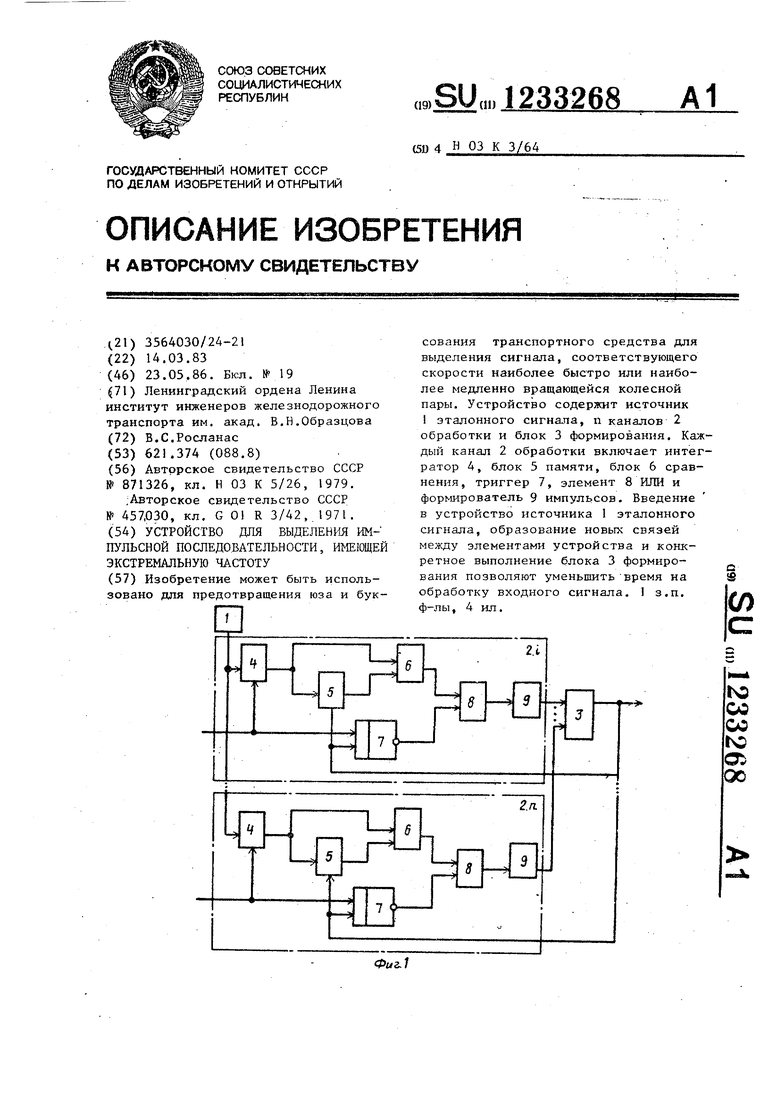

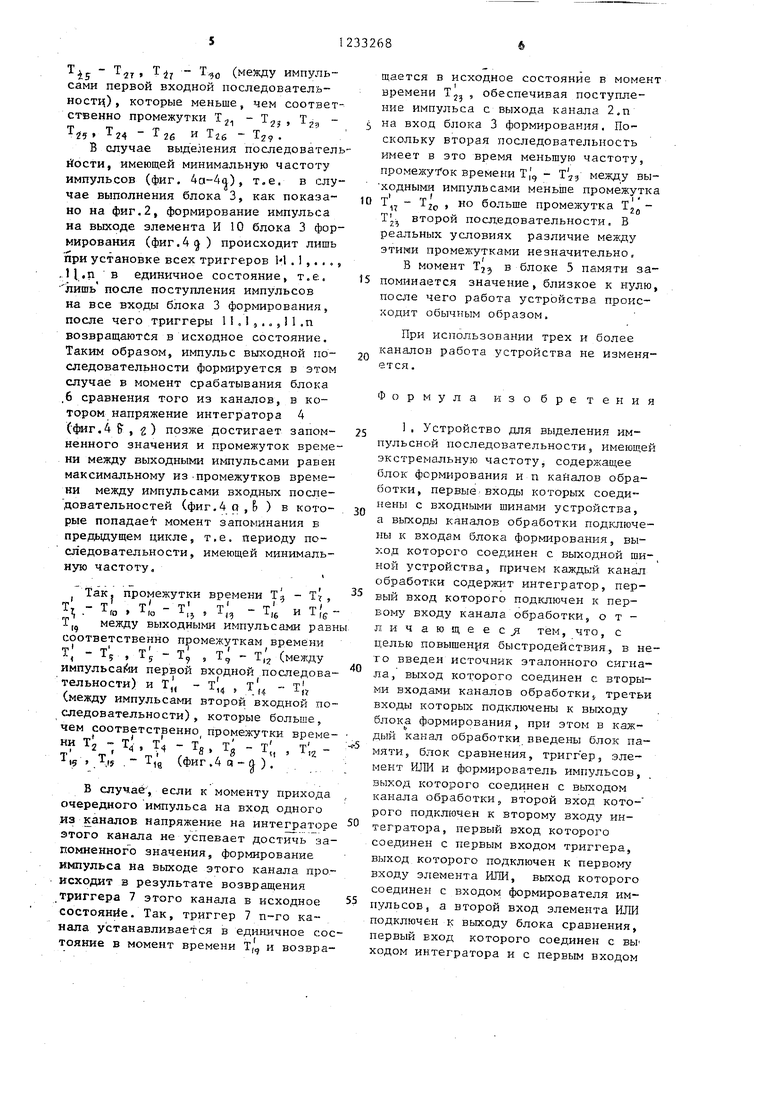

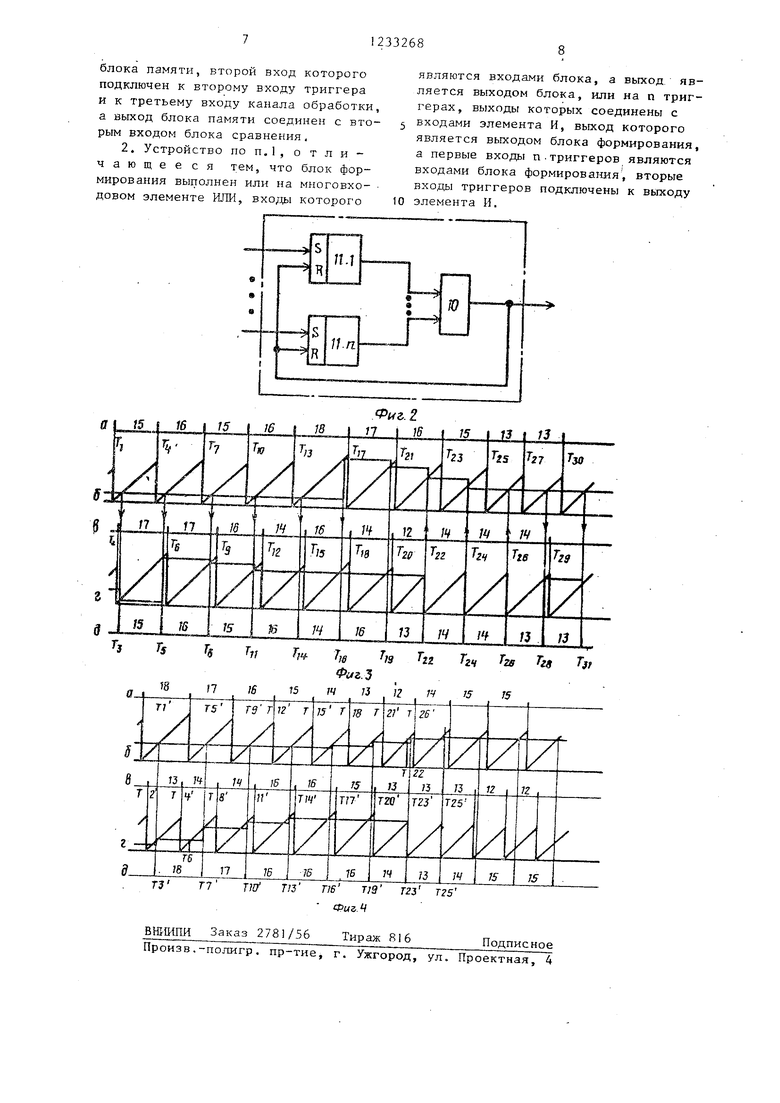

На фиг,1 представлена структурная схема устройства для выделения импульсной последовательности, имеющей экстремальную частоту; на фиг, 2 -- функциональная схема блока вания для выделения посг/едователь- ности, имеющей минимальную частоту; на - временные диаграммы, поясняющие работу устройства при выделении последовательности, имеющей

максимальную частоту; на фиг.4 I

то же, при выделении последовательности, имеющей минимальную частоту.

Устройство для выделения импульсной последовательности, имеющей экстремальную частоту, содержит источник эт,алошюго сигнала, п каналов 2, 2.П обработки и блок 3 формирования, причем первые вход1л каналов 2.,.., 2.П обработки соединены с входными шинами устройства, выход источника 1 эталонного сигнала подключен к вторым входам каналов 2.:lf,.., 2.П обработки, выходы которых соединены с входами блока 3 формирования, выход которого подключен к выходной шиьге устройства и к третьим входам каналов обработки, при этом каждый канал обработки содержит интегратор 4, блок 5 памяти, блок 6 сравнения, триггер 7, элемент ИЛИ 8 и формирователь 9 импульсов , выход которого соединен с ходом канала обработки, первый вход которого подютючен к первым входам интегратора 4 и триггера 7, второй вход канала обработки соединен с вторым входом интегратора 4, выход триггера 7 подключен к первому входу элемента ИЛИ 8 ,i выход которого соединен с входом формирователя 9 импульсов, а второй вход элемента ШШ . 8 подключен к выходу блока 6 сравнения, первый вход которого соединен с зьгходом интегратора 4 и с первым

15

20

2332682

входом блока 5 памяти, второй вход которого подключен к втором входу триггера 7 и к третьему входу канала обработки, а выход блока 5 памяти 5 соединен с вторым входом блока 6 сравнения.

При выделении последовательности, имеющей максимальную частоту, блок

3формирования содержит многовходо- 10 вой элемент ИЛИ, входы и выход которого соединены соответственно с входами и выходами блока формирования,

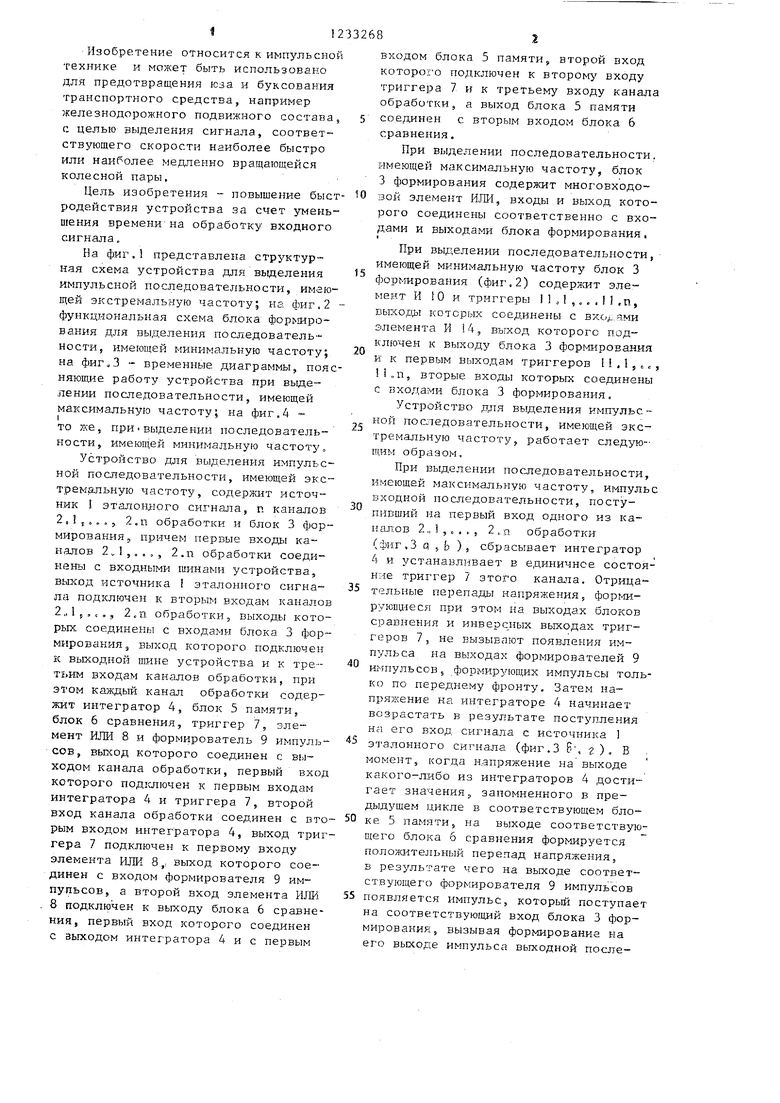

При выделении последовательности, имеющей минимальную частоту блок 3 формирования (фиг, 2) содерлсит элемент И 1 О к триггеры 1,1,о.,И.п, выходы которых соединены с элемента И 4, выход которого подключен к выходу блока 3 фop -lиpoвaния и к первым выходам триггеров i . 1 , .«, , вторые входы которых соединены с входами блока 3 формирования,

Устройство для выделения импульс „ ной пос:аедовательности, имеюЕ1ей экстремальную частоту, работает следую-- щим образом.

При вьщелении последовательности, имеющей максимальную частоту, импульс входной последовательности, поступивший на первый вход одного из ка- на.пов 2„ ,,,, 2 „п обработки (фи;г,3 а ,Ь ), сбрасывает интегратор

4и устанавливает в единичное состояние триггер 7 этого канала. Отрица35 тельные перепады напряжения, фор14и- руюп1иеся при этом на выходах блоков сравнения и инверсных выходах триггеров 7, не вызывают появления импульса на выходах формирователей 9 импульсов, формирующих импульсы только по переднему фронту. Затем напряжение на интеграторе 4 начи1 ает возрастать в результате поступления на его вход сигнала с источника 1 эталонного сигнала (фиг.З В , г ). В момент, когда напряжение на выходе какого-либо из интеграторов 4 достигает значения, запомненного в предыдущем цикле в соответствующем бло50 ке 5 памяти, на выходе соответствующего блока 6 сравнения формируется положительный перепад напряжения, в результате чего на выходе соответствующего формирователя 9 импульсов

55 появляется импульс, который поступает на соответствующий вход блока 3 формирования, вызывая формирование на его выходе импульса выходной после40

45

довательности (фиг.3|). Импульс с выхода блока 3 формирования, поступая на управляющие входы блоков 5 памяти и входы -сброса триггеров 7, приводит к запоминанию в блоках 5 памяти значений напряжений, имевших место соответственно на выходах интеграторов 4 в момент формирования импульса на выходе блока 3 формирования , и к сбросу триггеров 7. Сброс интегратора 4 первого канала и установка триггера 7 в единичное состояние происходят в моменты времени Т,, Т, Т,. Т ,„. Т,,. Т„ . Т,

J- : c Ч .

7

Т.

10 1 -47 2

LJ, , 25 г7 а сброс интегратора 4 п-го канала и установка в единичное состояние триггера 7 п-го канала - в моменты времени Tj, Т,

9

и Т

12 19- 1В Zo 22 24 гй

2ц , а формирование импульсов вы- ходной последователности запоминание значений напряжений на выходах интеграторов 4 в блоках 5 памяти и сброс триггеров 7 - в моменты времени Т,

Tf. T

TI,

,т,

24

16

, Tjg и Tj, (фиг.З а-д).

После момента запоминания напря- жений в блоках 5 памяти первым (при достаточном времени нарастания) снов достигает запомненного значения напряжения тот из интеграторов, нарастание напряжения на выходе которого продолжается более короткое время, т.е. интегратор, для которого момент запоминания в предыдущем цикле попал в промежуток между импульсами входной последовательности, имеющей меньшую длительность. При этом в блоке 5 памяти этого канала обработки запоминается то же значение, что и в предыдущем цикле, а промежуток времени между предыдущим и последующим моментами запоминания, т.е. между двумя соседними импульсами на выходе блока 3 формирования, равен меньшему промежутку времени между соседними импульсами на входе этого канала обработки. В блоке 5 памяти другого канала запоминается новое значение. Так, промежутки времени

Tj 5

- Т

т т -

8

«. Т

11 Id -46

между импульсами выходной последовательности соответственно равны промежуткам времени Т, - Т, Т - Т , Tj - Т,о (между импульсами первой входной последовательности)

Т,

7

- Т.

и Т

15

- Т

18

(между им24

24 26

пульсами второй входной последователь- рой входной последовательности) и

ности), которые меньше, чем соответственно промежутки времени Т - Т,

- Т

9

Т, 42

,. т,, - Т,

и Т.

T.JI . Промежуток времени Т, Т , имеет ту же длительность, что и равные друг другу промежутки времени

to

15

й

20

а

25

30

35

40

- Т,

и То - Т

1-2

ВХОДНЫХ ПО45

- 10 13 9

следовательностей.

Б процессе работы устройства может случиться так, что к моменту прихода очередного импульса на вход одного из каналов обработки напряжения на интеграторах 4 этого и других каналов не успеют достичь значений, запомненных в предыдущем цикле, что соответствует моменту времени 1 (фиг.З). В этом случае работа устройства происходит следующим образом.

В момент импульс второй входной последовательности, поступая на счетный вход триггера 7 п-го канала, который установлен в единичное состояние предыдущим импульсом этой последовательности в момент времени , возвращает триггер 7 п-го канала в исходное состояние, В результате на выходе триггера 7 п-го канала в момент , появляется положительный пе-- репад напряжения , что приводит к формированию импульса на выходе формирователя 9 п-го канала и на выходе блока 3 формирования. Промежуток времени Т,д - Т,,2 между импульсами выходной последовательности меньше предыдущего промежутка Т,д - между импульсами второй входной последовательности, имеющей в это время более высокую частоту, но больше следующего за ним промежутка Т этой же последовательности. В реальных условиях, т.е. в случае поступления входных импульсов с частотных датчиков скорости колесных пар, различие в длительности промежутка времени между импульсами на выходе частотного датчика скорости не может значительно изменяться иа протяжении последовательных периодов. Б момент

2Z

в интеграторе 4 запоминается

значение, близкое к нулю.

После этого формирование выходных импульсов происходит обычным образом,

5

т.е.

т 24

промежутки времени Т

-26

26

- Т

га

и Т

22 2S

- т

- т 1

24

между выходными импульсами равны соответственно промежуткам времени Т, - (между импульсами вто24

24 26

рой входной последовательности) и

T.J.J - 1, - (между импульсами первой входной последователь- ностц), которые меньше, чем соответ- ственно промежутки Т - , , 24

- Т

26

И Тгб - Тг9 .

В случае выделения последователь йости, имеющей минимальную частоту импульсов (фиг. 4a-4(j), т,е, в случае выполнения блока 3, как показа- но на фиг.2, формирование импульса на выходе элемента И 10 блока 3 формирования (фиг.А) происходит лишь при установке всех триггеров 11 . 1 ,. , ,, ,11.п в единичное состояние, т.е. лишь после поступления импульсов на все входы блока 3 формирования, после чего триггеры 1 , 1 , . , 1 1 .п возвращаются в исходное состояние. Таким образом, импульс выходной по- следовательности формируется в этом случае в момент срабатывания блока ,6 сравнения того из каналов, в котором напряжение интегратора 4 (фиг.4 &, г) позже достигает запом- ненного значения и промежуток време . ни между выходными 1п-тупъс.анк ранен максимальному из .промежутков времени между импульсами входных последовательностей (фиг.4с1,& ) в кото- рые попадает момент запоминания в предьщущем цикле, т.е. периоду по- сл едовательности, имеющей минимальную частоту.

Так. промежутки времени Т - Т,

, . 10 5 Т) е Т между выходными импульсами равн

соответственно промежуткам времени

т; - т;,, т; - т, , т - т; (между

импульсайи первой входной последовательности) и Т,, - т| , т , - т;

(между импульсами второй входной последовательности) , которые больше, чем соответственно промежутки време-

ни т - т;, т; - тд, Tg - т;, , т;, -

- (фиг.4 q-g).

т т

15 |

- Т

18

В случае , если к момбшту прихода очередного импульса на вход одного из каналов напряженке на интеграторе этого канала не успевает достичь за- помненногЪ значения, формирование импульса на выходе этого канала происходит в результате возвращения триггера 7 этого канала в исходное состояние. Так, триггер 7 п-го канала устанавливается в еди1-шчное состояние в момент времени Т, и возвраs о 5 0

5

5

0

5

щается в исходное состояние в момент времени Т , обеспечивая поступление импульса с выхода канала 2,п на вход блока 3 формирования. По-- скольку вторая последовательность имеет в это время меньшую частоту, промежуток времени Т,,, - Т, между вы- ходными импульсами меньше промежутка т , - Tjp , но больше промежутка - Tl. второй посдедовательности, В реальных условиях различие между этими промежутками незначительно,

В момент Т, в блоке 5 памяти запоминается значение, близкое к нулю, после чего работа устройства происходит обычным образом.

При использовании трех и более каналов работа устройства не изменяется.

Формула изобретения

1. Устройство для выделения импульсной последовательностиэ имеющей экстремальную частоту, содержащее блок формирования и п каналов обработки, первые ВХОДЫ которых соединены с входньти шинами устройства, а вьпсорь) каналов обработки подключены к входам блока формирования, выход которого соединен с выходной ши- ной устройства, причем каждый канал обработки содержит интегратор, первый вход которого подключен к пер- входу канала обработки, о т - л и ч а ю щ е е с ji тем, что, с целью повышен 1я быстродействия, в него введен источник эталонного сигнала, выход которого соединен с вторыми входами каналов обработкиj третьи входы которых подключены к выходу блока формирования, при этом в каждый канал обработки введены блок памяти, блок сравнения, тригг ер, элемент ШШ и формирователь импульсов, выход которого соединен с выходом канала обработки, второй вход кото- рого подключен к второму входу интегратора, первый вход которого соединен с первым входом триггера, выход которого подключен к первому входу элемента ИЛИ, выход которого соединен с входом формирователя импульсов, а второй вход элемента РШИ подключен к выходу блока сравнения, первый вход которого соединен с вы ходом интегратора и с первым входом

блока памяти, второй вход которого подключен к второму входу триггера и к третьему входу канала обработки, а выход блока памяти соединен с вторым входом блока сравнения,

2. Устройство по п,1, о т л и - чающее ся тем, что блок формирования выполнен или на многовхо- довом элементе ИЛИ, входа: которого

s % - Ъв 13 Гг2 /2, Тгв Тгв 7,

Фи& 5

J8П ГЧ 7J г /V 75 Г5

ТЗ Т7 ЛО Ш Г/5 Т/9 ГЛЗ Т25

Фиг. Ч

ВШШПИ Заказ 2781/56Тираж 816

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

являются входами блока, а выход, является выходом блока, или на п триггерах, выходы которых соединены с входами элемента И, выход которого является выходом блока формирования, а первые входы п . триггеров являются входами блока формировагшя, вторые входы триггеров подключены к выходу элемента И.

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения временных параметров сфигмографических кривых | 1980 |

|

SU900219A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| Устройство для передачи и приема телеметрической информации | 1986 |

|

SU1397956A1 |

| СПОСОБ ТЕЛЕВИЗИОННОГО ВЕЩАНИЯ С ЗАЩИТОЙ ОТ НЕСАНКЦИОНИРОВАННОГО ПРИЕМА И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2013024C1 |

| Многоканальный автономный прибор для исследования скважин в процессе бурения | 1981 |

|

SU983261A1 |

| Устройство для оценки неоднородности дисперсии случайных процессов | 1990 |

|

SU1764066A1 |

| Устройство обработки информации | 1989 |

|

SU1817255A1 |

| Параллельный анализатор частотного спектра | 1981 |

|

SU998971A1 |

| УСТРОЙСТВО ПОИСКА СИГНАЛА СИНХРОНИЗАЦИИ СПУТНИКОВОЙ СИСТЕМЫ СВЯЗИ | 1995 |

|

RU2093963C1 |

| Устройство цветовой синхронизации телевизионного приемника системы "СЕКАМ | 1980 |

|

SU985975A1 |

Изобретение может быть использовано для предотвращения юза и буксования транспортного средства для выделения сигнала, соответствующего скорости наиболее быстро или наиболее медленно вращающейся колесной пары. Устройство содержит источник эталонного сигнала, п каналов 2 обработки и блок 3 формирования. Каждый канал 2 обработки включает интегратор 4, блок 5 памяти, блок 6 сравнения, триггер 7, элемент 8 ИЛИ и формирователь 9 импульсов. Введение в устройство источника 1 эталонного сигнала, образование новых связей между элементами устройства и конкретное выполнение блока 3 формирования позволяют уменьшить время на обработку входного сигнала. 1 з.п. ф-лы, 4 ил. § (Л 1чЭ оо оо 1C х оо

| Устройство для получения разностной частоты двух импульсных последовательностей | 1979 |

|

SU871326A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Прибор для вычерчивания конических сечений | 1922 |

|

SU457A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

Авторы

Даты

1986-05-23—Публикация

1983-03-14—Подача