1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством.

Целью изобретения является уменьшение динамической погрешности преобразователя.

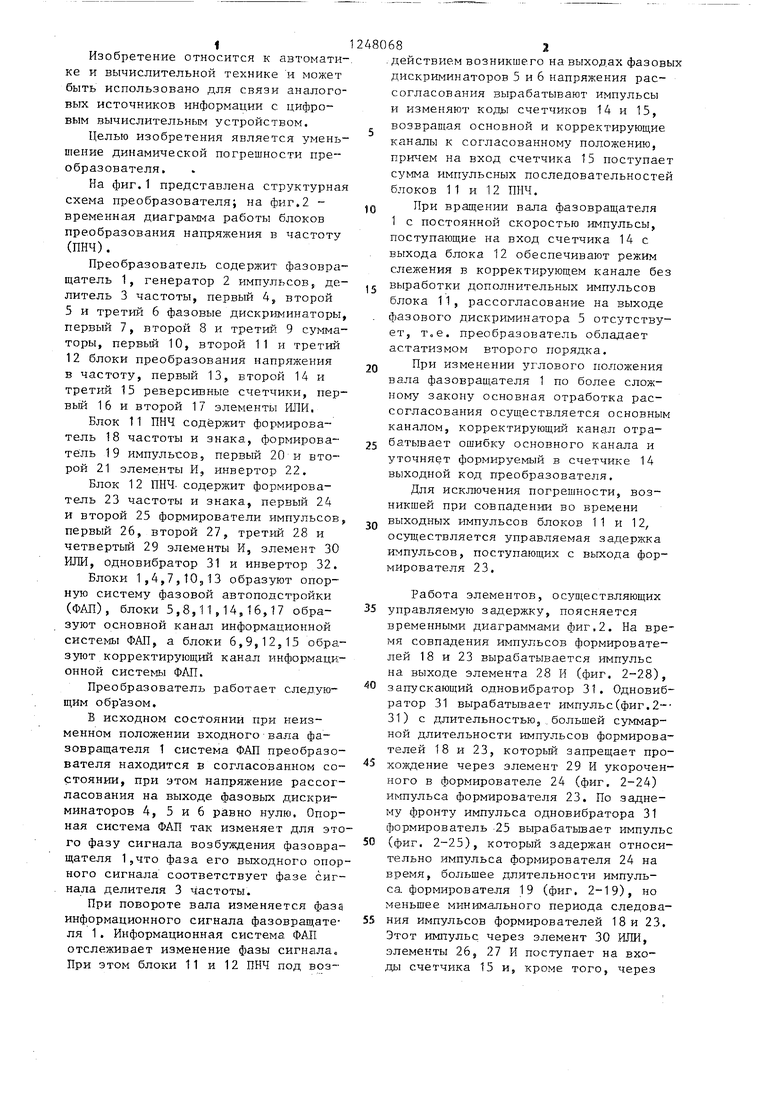

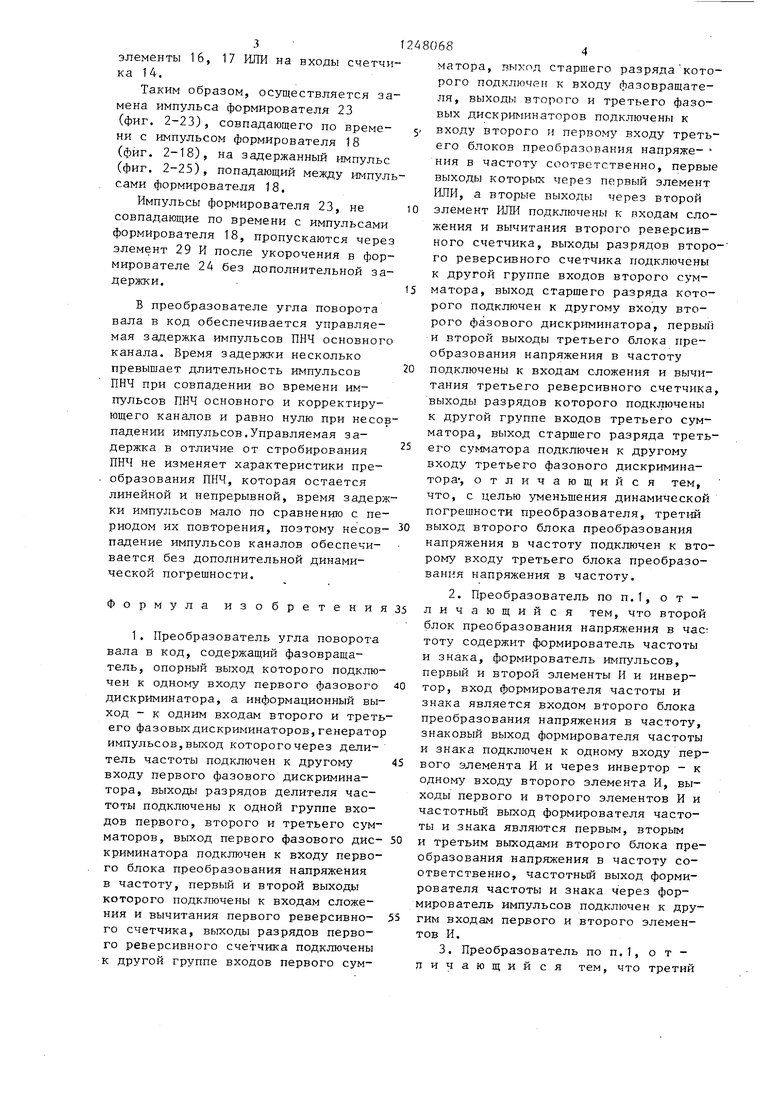

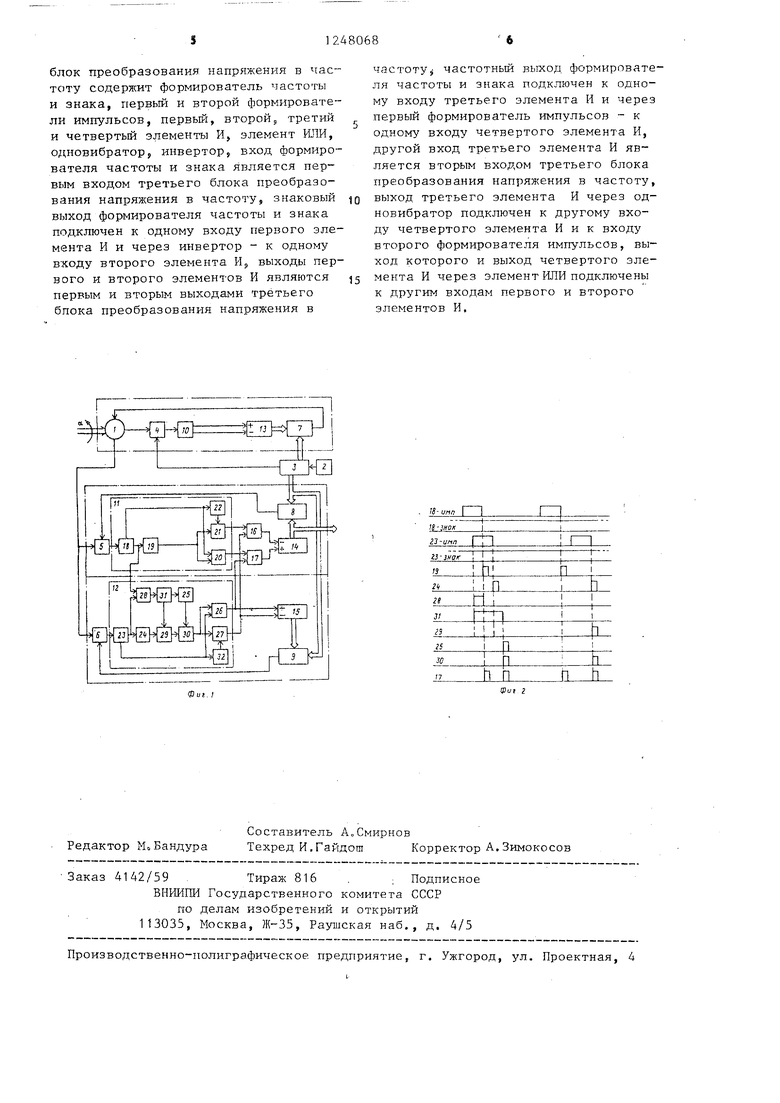

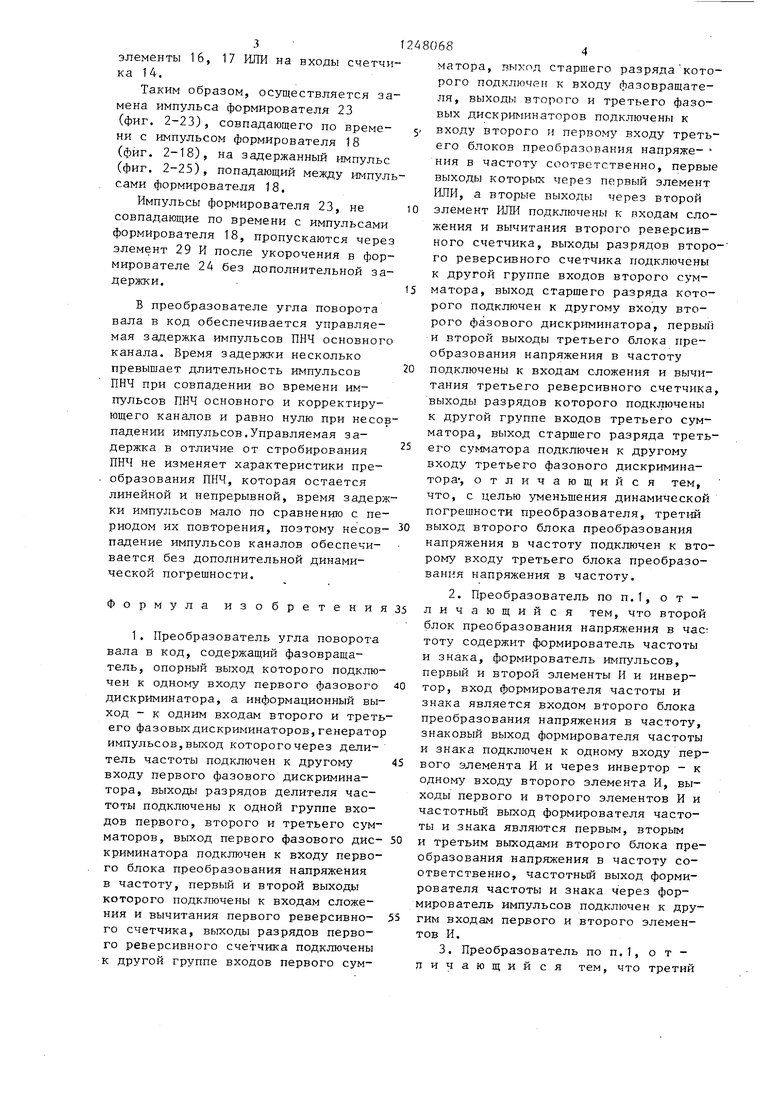

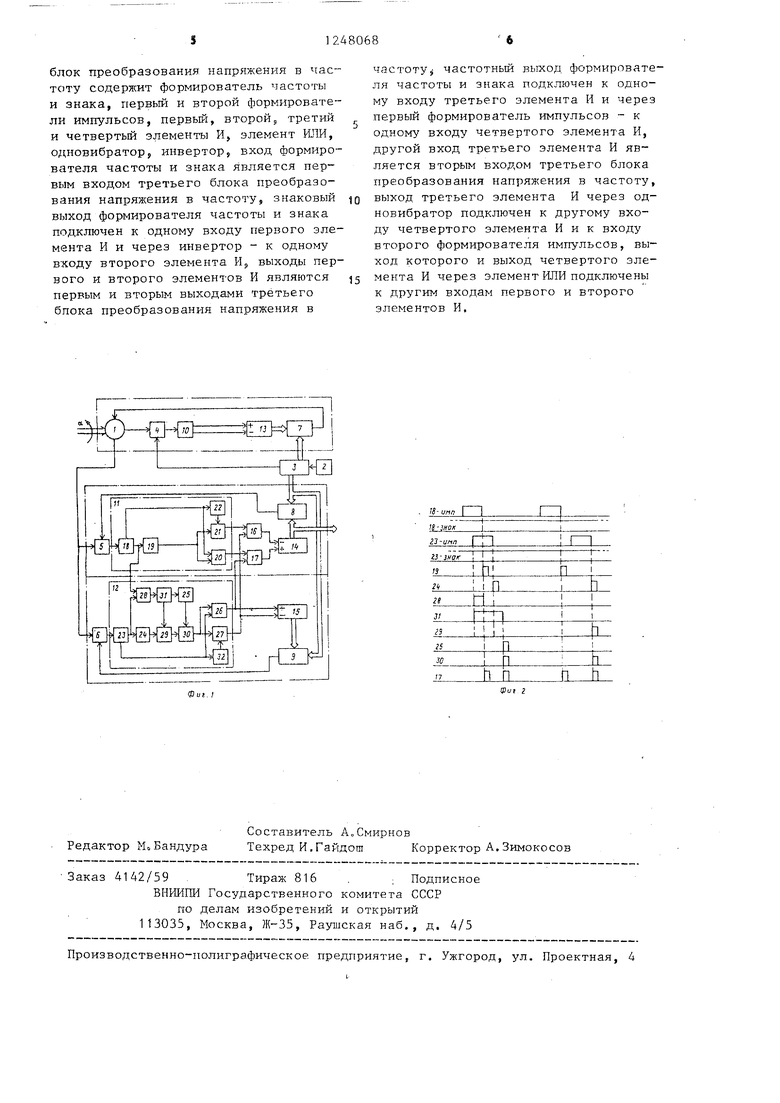

На фиг.1 представлена структурная схема преобразователя; на фиг.2 - временная диаграмма работы блоков преобразования напряжения в частоту (ПНЧ).

Преобразователь содержит фазовращатель 1, генератор 2 импульсов,, делитель 3 частоты, первый 4, второй 5 и третий 6 фазовые дискриминаторы, первый 7, второй 8 и третий 9 сумматоры, первый 10, второй 11 и третий 12 блоки преобразования напряжения в частоту, первый 13, второй 14 и третий 15 реверсивные счетчики, первый 16 и второй 17 элементы Ш1И.

Блок 11 ПНЧ содержит формирователь 18 частоты и знака, формирователь 19 импульсов, первый 20 и второй 21 элементы И, инвертор 22.

Блок 12 ПНЧ. содержит формирователь 23 частоты и знака, первый 24 и второй 25 формирователи импульсов, первый 26, второй 27, третий 28 и четвертый 29 элементы И, элемент 30 ИЛИ, одновибратор 31 и инвертор 32. Блоки 1,4,7,10,13 образуют опорную систему фазовой автоподстройки (ФАЛ), блоки 5,8,11,14,16,17 образуют основной канал информационной системы ФАП, а блоки 6,9,12,15 образуют корректирующий канал информационной системы ФЛП.

Преобразователь работает следующим обр азом,

В исходном состоянии при неизменном положении входного вала фазовращателя 1 система ФАП преобразователя находится в согласованном состоянии, при этом напряжение рассогласования на выходе фазовых дискриминаторов 4, 5 и 6 равно нулю. Опорная система ФАП так изменяет для этого фазу сигнала возбуждения фазовращателя 1,что фаза его выходного опорного сигнала соответствует фазе сиг- . нала делителя 3 частоты.

При повороте вала изменяется фаза информационного сигнала фазовращателя 1. Информационная система ФАЛ отслеживает изменение фазы сигнала. Лри этом блоки 11 и 12 ПНЧ под воз480682

, действием возникшего на выходах фазовых дискриминаторов 5 и 6 напряжения рассогласования вырабатывают импульсы и изменяют ко;ды счетчиков 14 и 15, возвращая основной и корректирующие каналы к согласованному положению, причем на вход счетчика 15 поступает сумма импульсных последовательностей блоков 11 и 12 ПНЧ.

0 При вращении вала фазовращателя 1 с постоянной скоростью импульсы, поступающие на вход счетчика 14 с выхода блока 12 обеспечивают режим слежения в корректирующем канале без

,5 выработки дополнительных импульсов

блока 11, рассогласование на выходе . фазового дискриминатора 5 отсутствует, т„е. преобразователь обладает астатизмом второго порядка.

20 При изменении углового положения вала фазовращателя 1 по более сложному закону основная отработка рассогласования осуществляется основным каналом, корректирующий канал отра25 батывает ошибку основного канала и уточняет формируемый в счетчике 14 выходной код преобразователя.

Для исключения погрешности, возникшей при совпадении во времени

,Q выходных импульсов блоков 11 и 12, осуществляется управляемая задержка импульсов, поступающих с выхода формирователя 23.

Работа элементов, осуп1ествляющих

35 управляемую задержку, поясняется

временными диаграммами фиг.2. На время совпадения импульсов формирователей 18 и 23 вырабатывается импульс на выходе элемента 28 И (фиг. 2-28),

0 запускающий одновибратор 31. Одновибратор 31 вырабатывает импульс(фиг.2-- 31) с длительностью,,большей суммарной длительности импульсов формирователей 18 и 23, которьм запрещает про45 хождение через элемент 29 И укороченного в формирователе 24 (фиг. 2-24) импульса формирователя 23. По заднему фронту импульса одновибратора 31 формирователь 25 вырабатывает импульс

50 (фиг. 2-25), который задержан относительно импульса формирователя 24 на время, большее длительности импульса формирователя 19 (фиг. 2-19), но меньшее минимального периода следова55 ния импульсов формирователей 18 и 23. Этот импульс через элемент 30 :ИЛИ, элементы 26, 27 И поступает на входы счетчика 15 и, кроме того, через

3

или

на входы счетчиэлементы 16, 17 ка 14.

Таким образом, осуществляется замена импульса формирователя 23 (фиг. 2-23), совпадающего по времени с импульсом формирователя 18 (фиг. 2-18), на задержанный импульс (фиг. 2-25), попадающий между импульсами формирователя 18.

Импульсы формирователя 23, не совпадающие по времени с импульсами формирователя 18, пропускаются через элемент 29 И после укорочения в формирователе 24 без дополнительной задержки.

В преобразователе угла поворота вала в код обеспечивается управляемая задержка импульсов ПНЧ основного канала. Время задержки несколько превышает длительность импульсов ПНЧ при совпадении во времени импульсов ПНЧ основного и корректирующего каналов и равно нулю при несовпадении импульсов.Управляемая задержка в отличие от стробирования ПНЧ не изменяет характеристики преобразования ПНЧ, которая остается линейной и непрерывной, время задержки импульсов мало по сравнению с пе

риодом их повторения, позтому несов падение импульсов каналов обеспечивается без дополнительной динамической погрешности.

Формула изобретения

1. Преобразователь угла поворота вала в код, содержащий фазовращатель, опорный выход которого подключен к одному входу первого фазового дискриминатора, а информационный выход - к одним входам второго и третьего фазовыхдискриминаторов,генератор импульсов,выход которого через делитель частоты подключен к другому входу первого фазового дискриминатора, выходы разрядов делителя частоты подключены к одной группе входов первого, второго и третьего сумматоров, выход первого фазового дис- криминатора подключен к входу первого блока преобразования напряжения в частоту, первый и второй выходы которого подключены к входам сложения и вычитания первого реверсивно- го счетчика, выходы разрядов первого реверсивного счетчика подключены к другой группе входов первого сум1248068

10

15

20

25

30

35

4045 50 55

матора, выход старшего разряда которого подключен к входу фазовращателя, выходы второго и третьего фазовых дискриминаторов подключены к входу второго и первому входу третьего блоков преобразования напряже- ния в частоту соответственно, первые выходы которых через первый элемент Ш1И, а вторые выходы через второй элемент ИЛИ подключены к входам сложения и вычитания второго реверсивного счетчика, выходы разрядов второ- го реверсивного счетчика подключены к другой группе входов второго сумматора, выход старшего разряда которого подключен к другому входу второго фазового дискриминатора, первый и второй выходы третьего блока преобразования напряжения в частоту подключены к входам сложения и вычитания третьего реверсивного счетчика, выходы разрядов которого подключены к другой группе входов третьего сумматора, выход старшего разряда третьего сумматора подключен к другому входу третьего фазового дискриминатора-, отличающийся тем, что, с целью уменьшения динамической погрешности преобразователя, третий выход второго блока преобразования напряжения в частоту подключен к второму входу третьего блока преобразования напряжения в частоту.

2. Преобразователь по п.1, отличающийся тем, что второй блок преобразования напряжения в час: тоту содержит формирователь частоты и знака, формирователь импульсов, первый и второй элементы И и инвертор, вход формирователя частоты и знака является входом второго блока преобразования напряжения в частоту, знаковый выход формирователя частоты и знака подключен к одному входу первого элемента И и через инвертор - к одному входу второго элемента И, выходы первого и второго элементов И и частотный выход формирователя частоты и знака являются первым, вторым и третьим выходами второго блока преобразования напряжения в частоту соответственно, частотный выход формирователя частоты и знака через формирователь импульсов подключен к другим входам первого и второго элементов И.

3. Преобразователь по п.1, о т - дичающий ся тем, что третий

блок преобразования напряжения в частоту содержит формирователь частоты и знака, первый и второй формирователи импульсов, первьш, второй третий и четвертый элементы И, элемент ИЛИ, одновибраторJ инвертор, вход формирователя частоты и знака является первым входом третьего блока преобразования напряжения в частоту, знаковый выход формирователя частоты и знака подключен к одному входу первого элемента И и через инвертор - к одному входу второго элемента И, выходы первого и второго элементов И являются первым и вторым выходами третьего блока преобразования напряжения в

частоту.) частотный выход формирователя частоты и знака подключен к одному входу третьего элемента И и через первый формирователь импульсов к одному входу четвертого элемента И, другой вход третьего элемента И является вторым входом третьего блока преобразования напряжения в частоту, выход третьего элемента И через одновибратор подключен к другому входу четвертого элемента Инк входу второго формирователя импульсов, выход которого и выход четвертого элемента И через элемент ИЛИ подключены к другим входам первого и второго элементов И,

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1984 |

|

SU1236610A1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1095213A1 |

| Преобразователь угла поворота вала в код | 1979 |

|

SU898482A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1446691A2 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1280699A1 |

| Преобразователь угла поворотаВАлА B КОд | 1978 |

|

SU830461A1 |

| Преобразователь кода в угловое положение вала | 1983 |

|

SU1088048A1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1042058A1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1076934A1 |

| Фазовая следящая система | 1981 |

|

SU954926A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. С целью уменьшения динамической погрешности преобразователя третий вы- ход второго блока преобразования напряжения в частоту (ПНЧ) подключен к второму входу третьего блока ПНЧ, Опорньй выходной сигнал фазовращателя и .сигнал с выхода делителя частоты сравниваются в первом фазовым дискриминаторе, по выходному напряжению которого в первом блоке ПНЧ формируются импульсы на первом или втором выходе в зависимости от знака выходного напряжения первого фазового дискриминатора. Эти импульсы поступают на входы первого реверсивного счетчика, в зависимости от кода которого смещается фаза опорного сигнала фазовращателя до согласованного положения с фазой выходного сигнала делителя частоты. Информационный выходной сигнал фазовращателя сравнивается по фазе на втором и третьем фазовых дискриминаторах с выходными сигналами старшего разряда соответственно второго и третьего сумматоров, на первую группу входов которых поступает циклически из- меняюш;ийся код с выходов разрядов делителя частоты, а на вторую группу входов - выходной код второго и третьего реверсивных счетчиков со- .ответственно. При наличии рассогла- сования .входных сигналов второй и третий фазовые дискриминаторы формируют постоянные напряжения, которые воздействуют на второй и третий блоки ПНЧ соответственно. Выходные сигналы второго и третьего блоков ПНЧ поступают на входы сложения и вычитания второго и третьего реверсивных счетчиков, смещая фазу выходных .сигналов второго и третьего сумматоров. Кроме того, выходные сигналы третьего блока ПНЧ поступают на входы сложения и вычитания второго реверсивного счетчика. В третьем блоке ПНЧ предусмотрена управляемая задержка импульсов, срабатывающая при совпадении импульсов второго и третьего блоков ПНЧ. 2 з.п.ф- лы, 2 ил. € сл ю 4 00 о О5 00

JS-unn

Ч - знок

Zl UMn

1} - jygir

«

21,

21

LLIL .i±a

. 11., 5

JlJL

Фи1. I

Редактор М.Бандура

Составитель А„Смирнов

Техред И.Гайдош Корректор А.Зимокосов

Заказ 4142/59 . Тираж 816 . . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

«But г

| Патент США № 4079374, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Преобразователь угла поворотаВАлА B КОд | 1978 |

|

SU830461A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1986-07-30—Публикация

1984-10-23—Подача