Изобретение относится к защите полупроводниковых преобразователей, предназначено для защиты и диагностики состояния тиристоров автономного инвертора напряжения и является усо вершенствсванием устройства по авт. св. № 1116492.

Цель изобретения - расширение функциональных возможностей устройства.

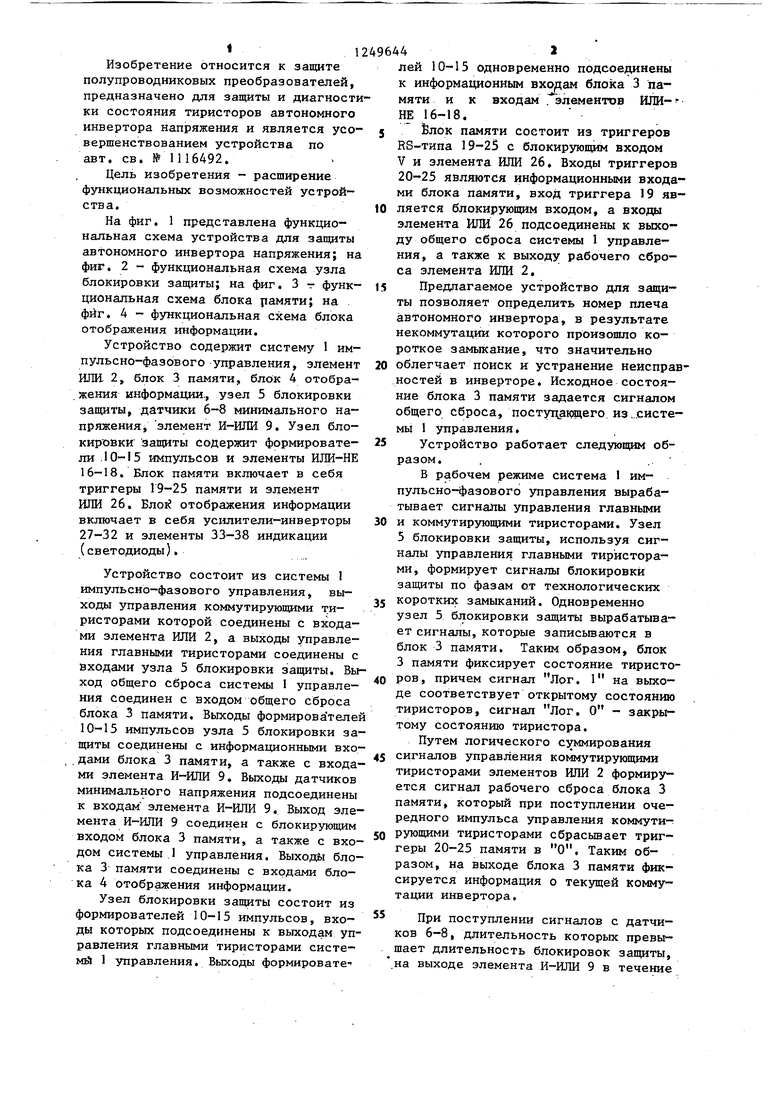

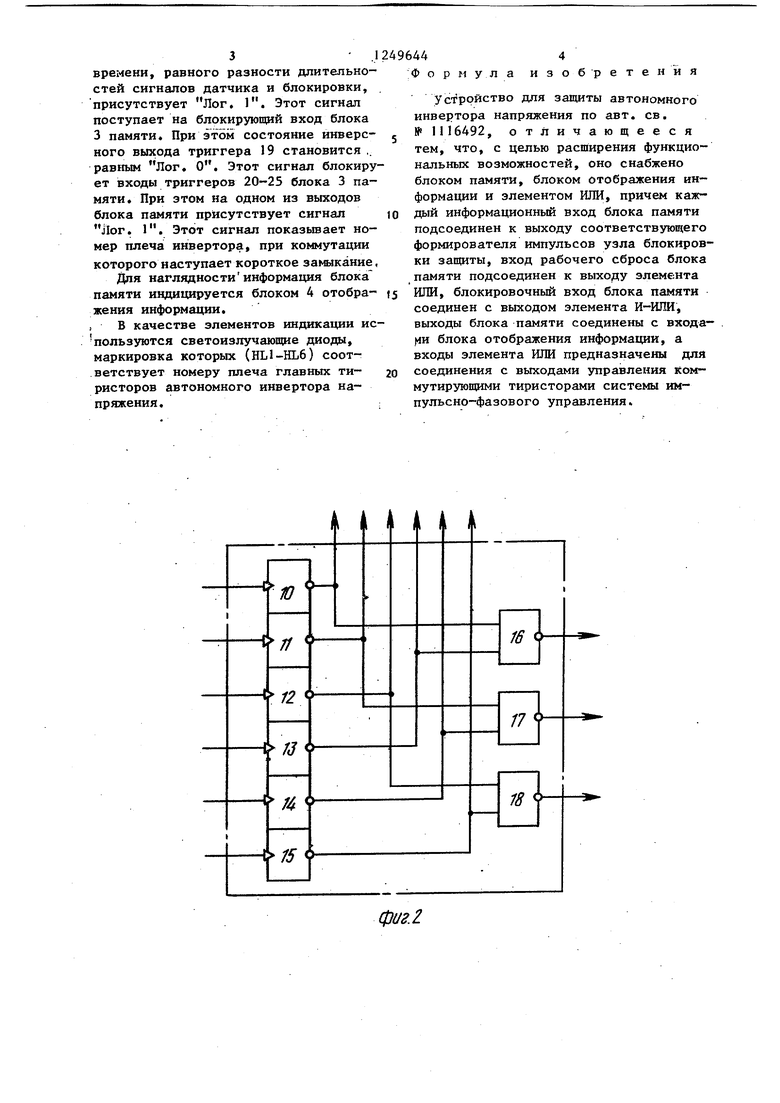

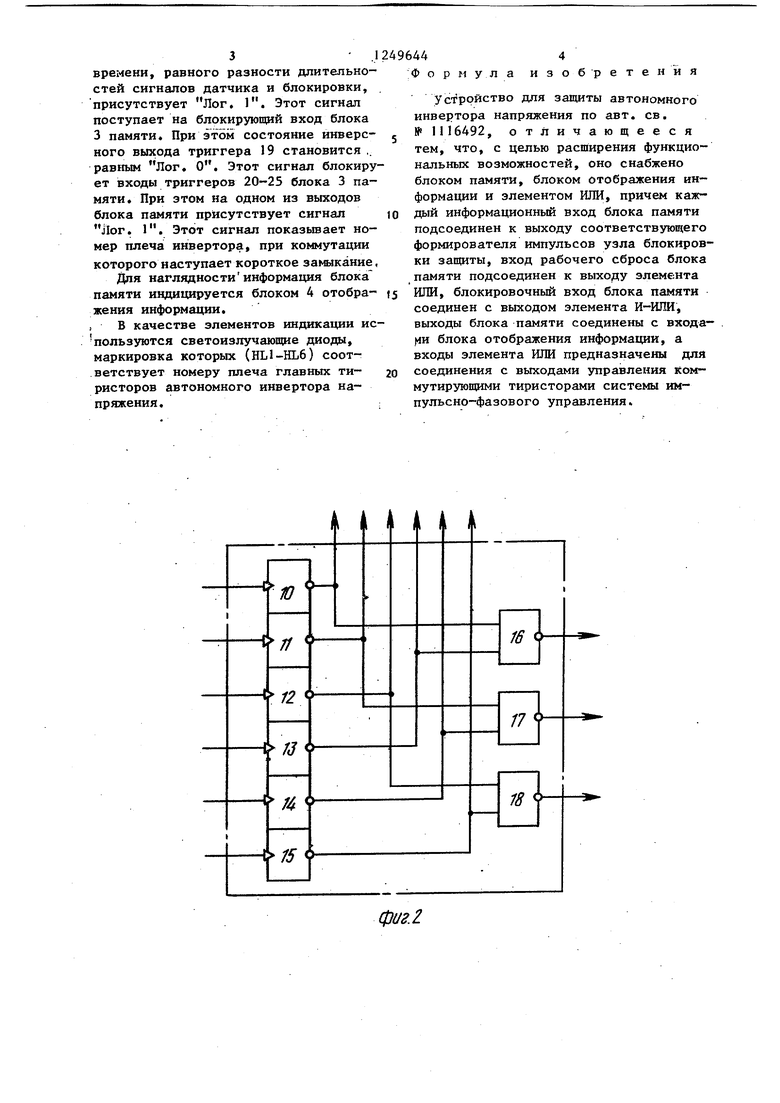

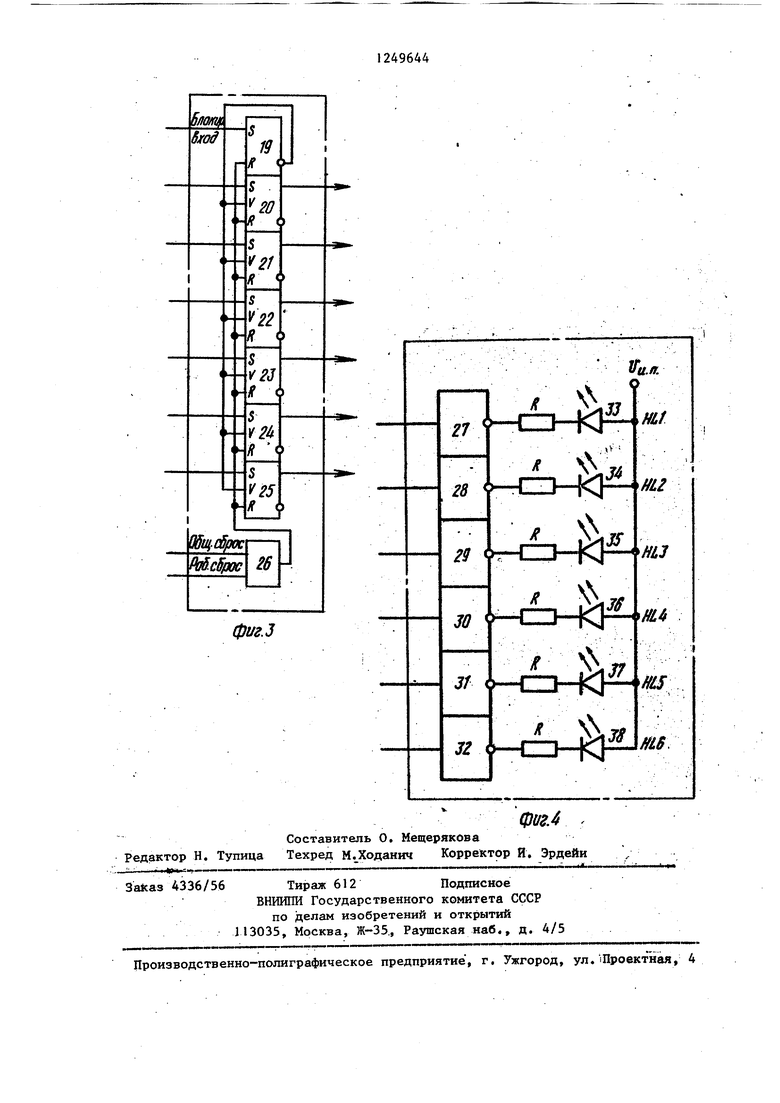

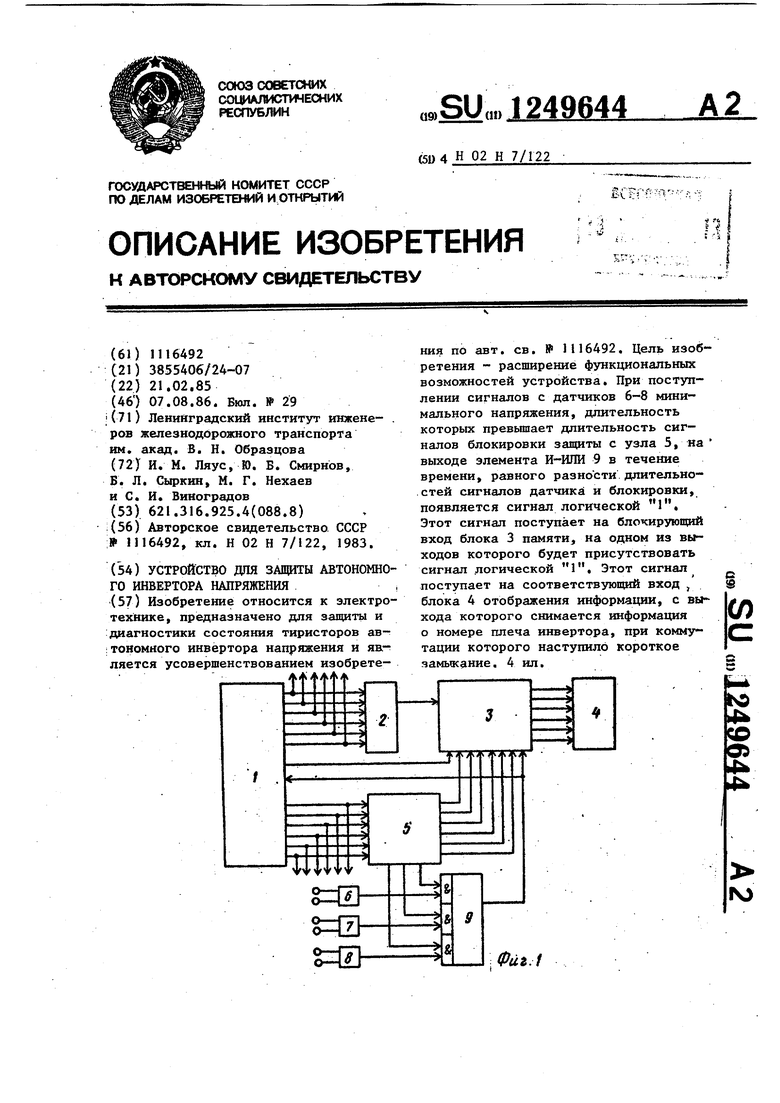

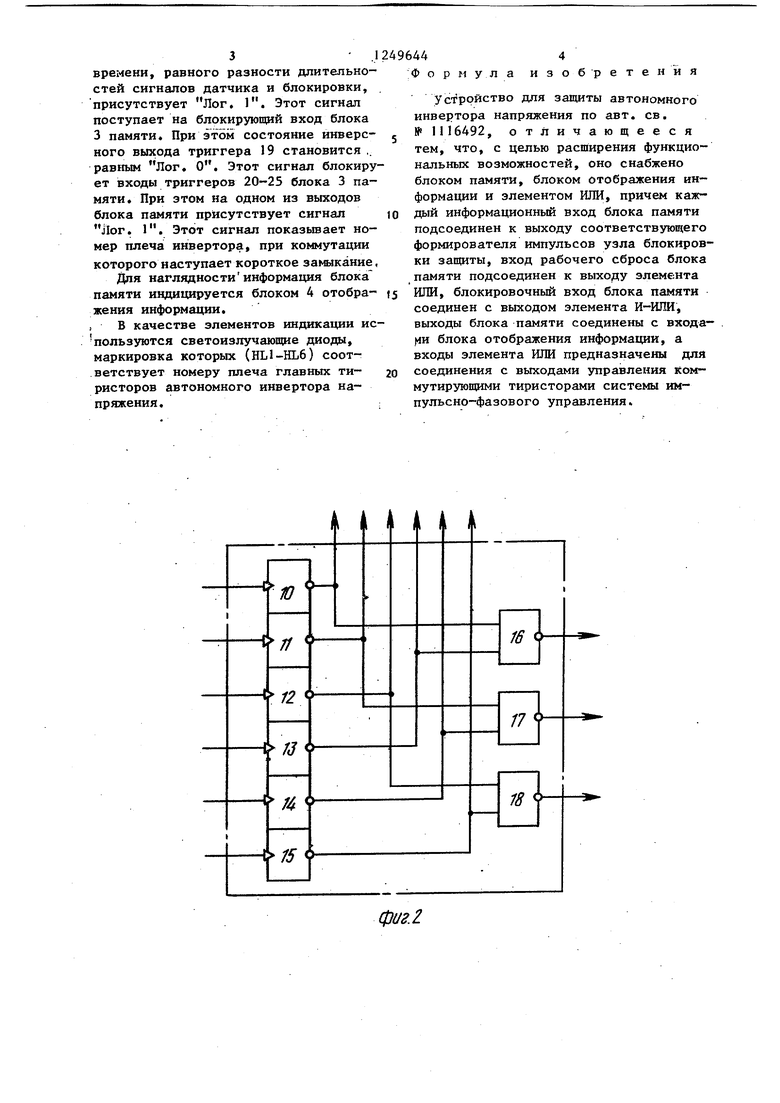

На фиг. 1 представлена функциональная схема устройства для защиты автономного инвертора напряжения; на фиР. 2 - функциональная схема узла блокировки защиты; на фиг. 3 - функциональная схема блока рамяти; на фиг. А - функциональная схема блока отображения информации.

Устройство содержит систему 1 им- пульсно-фазового управления, элемент ИЛИ- 2, блок 3 памяти, блок 4 отображения информации., узел 5 блокировки защиты, датчики 6-8 минимального напряжения, элемент И-ШТИ 9. Узел блокировки защиты содержит формирователи .10-15 импульсов и элементы ИЛИ-НЕ 16-18. Блок памяти включает в себя триггеры 19-25 памяти и элемент ИЛИ 26. Блой отображения информации включает в себя усилители-инверторы 27-32 и элементы 33-38 индикации (светодиоды).

Устройство состоит из системы 1 импульсно-фазового управления, выходы управления коммутирующими тиристорами которой соединены с входами элемента ИЛИ 2, а выходы управления главными тиристорами соединены с входами узла 5 блокировки защиты. Выход общего сброса системы 1 управления соединен с входом общего сброса блока 3 памяти. Выходы формирова телей 10-15 импульсов узла 5 блокировки защиты соединены с информационными вхо- . дами блока 3 памяти, а также с входами элемента И-ИЛИ 9. Выходы датчиков минимального напряжения подсоединены к входам элемента И-ИЛИ 9. Выход элемента И-ИЛИ 9 соединен с блокирующим входом блока 3 памяти, а также с входом системы. управления. Выходы блока 3 памяти соединены с входами блока 4 отображения информации.

Узел блокировки защиты состоит из формирователей 10-15 импульсов, входы которых подсоединены к выходам управления главными тиристорами систе- мй 1 управления. Выходы формировате

9644а

лей 10-15 одновременно подсоединены к информационным входам блока 3 памяти и к входам . элементов ИЛИ- НЕ 16-18.

5 Ёлок памяти состоит из триггеров RS-типа 19-25 с блокирующим входом V и элемента ИЛИ 26. Входы триггеров 20-25 являются информационными входами блока памяти, вход триггера 19 яв- 10 ляется блокирующим входом, а входы элемента ИЛИ 26 подсоединены к выходу общего сброса системы 1 управления, а также к выходу рабочего сброса элемента ИЛИ 2,

15 Предлагаемое устройство для защиты позволяет определить номер плеча автономного инвертора, в результате некоммутации которого произощло короткое замыкание, что значительно 20 облегчает поиск и устранение неисправностей в инверторе. Исходное состояние блока 3 памяти задается сигналом общего сброса, постудающего. из ...системы 1 управления.

25 Устройство работает следующим образом. .. В рабочем режиме система 1 им- пульсно-фазового управления вырабатывает сигналы управления главными 30 и коммутирующими тиристорами. Узел 5 блокировки защиты, используя сигналы управления главными тиристорами, формирует сигналы блокировки защиты по фазам от технологических 35 коротких замыканий. Одновременно

узел 5 блокировки защиты вырабатывает сигналы, которые записьгоаются в блок 3 памяти. Таким образом, блок 3 памяти фиксирует состояние тиристо- 40 ров, причем сигнал Лог. 1 на выходе соответствует открытому состоянию тиристоров, сигнал Лог. О - закрытому состоянию тиристора.

Путем логического суммирования 45 сигналов управления коммутирующими тиристорами элементов ИЛИ 2 формируется сигнал рабочего сброса блока 3 памяти, который при поступлении очередного импульса управления коммути-: 50 рующими тиристорами сбрасывает триггеры 20-25 памяти в О. Таким образом, на выходе блока 3 памяти фиксируется информация о текущей коммутации инвертора.

55 При поступлении сигналов с датчиков 6-8, длительность которых превышает длительность блокировок защиты, .на выходе элемента И-ШШ 9 в течение

3 .1

времени, равного разности длительностей сигналов датчика и блокировки, присутствует Лог. 1. Этот сигнал поступает на блокирующий вход блока 3 памяти. При этом состояние инверсного выхода триггера 19 становится ,. равным Лог, О. Этот сигнал блокирует входы триггеров 20-25 блока 3 памяти. При этом на одном из выходов блока памяти присутствует сигнал jlor. 1. Этот сигнал показьгаает номер плеча инвертора, при коммутации которого наступает короткое замыкание, Для наглядности информация блока памяти индицируется блоком 4 отображения информации.

, В качестве элементов индикации ис- пользуются светоизлучающие диоды, маркировка которых (НЫ-НЬб) соответствует номеру плеча главных тиристоров автономного инвертора напряжения.

249644

;Ф о р и у л а

изобретения

Устройство для защиты автономного инвертора напряжения по авт. св. № 1116492, отличающееся тем, что, с целью расширения функциональных возможностей, оно снабжено блоком памяти, блоком отображения информации и злементом ИЛИ, причем каж

дый информационный вход блока памяти подсоединен к выходу соответствующего формирователя импульсов узла блокировки защиты, вход рабочего сброса блока памяти подсоединен к выходу элемента

ИЛИ, блокировочный вход блока памяти соединен с выходом элемента И-ИЛИ, выходы блока памяти соединены с входа- и блока отображения информации, а входы элемента ИЛИ предназначены для

соединения с выходами управления коммутирующими тиристорами системы им- пульсно-фазового управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты автономного инвертора напряжения | 1983 |

|

SU1116492A1 |

| Устройство для управления асинхронным электродвигателем | 1990 |

|

SU1829102A1 |

| Устройство контроля параметров тиристорного преобразователя | 1982 |

|

SU1100610A1 |

| Устройство для контроля системы управления вентильным преобразователем | 1983 |

|

SU1185486A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ С АВТОНОМНЫМ ИНДУКТОРОМ | 2005 |

|

RU2291548C1 |

| Способ пуска непосредственного преобразователя частоты с искусственной коммутацией | 1984 |

|

SU1221702A1 |

| Устройство для блокировки информации при включении и выключении электропитания | 1988 |

|

SU1522212A1 |

| СИСТЕМА СТАБИЛИЗАЦИИ МОМЕНТА ВРАЩЕНИЯ СИЛОВЫХ ГИРОСТАБИЛИЗАТОРОВ | 2008 |

|

RU2382334C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ В ПЕРЕМЕННОЕ ВЫСОКОЙ ЧАСТОТЫ С ЭЛЕКТРОННЫМ УСТРОЙСТВОМ ЗАЩИТЫ | 2001 |

|

RU2222093C2 |

| АДАПТИВНАЯ СИСТЕМА УПРАВЛЕНИЯ ГИРОСТАБИЛИЗАТОРОМ | 2008 |

|

RU2381451C1 |

Изобретение относится к электротехнике, предназначено для защиты и диагностики состояния тиристоров ав- ;тономного инвертора напряжения и яа- ляется усовершенствованием изобретения по авт. ев. № 1116492. Цель изобретения - расширение функциональных возможностей устройства. При поступлении сигналов с датчиков 6-8 минимального напряжения, длительность которых превышает длнтельность сигналов блокировки защиты с узла 5, на выходе элемента И-ШШ 9 в течение времени, равного разности длительностей сигналов датчика и блокировки, появляется сигнал логической 1, Этот сигнал поступает на блокирующий вход блока 3 памяти, на одном из выходов которого будет присутствовать сигнал логической 1. Этот сигнал поступает на соответствующий вход , блока 4 отображения информации, с вы хода которого снимается информация о номере плеча инвертора, при коммутации которого наступило короткое замьткание. 4 ил. (Л

.

| Авторское свидетельство | |||

| Устройство для защиты автономного инвертора напряжения | 1983 |

|

SU1116492A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-08-07—Публикация

1985-02-21—Подача