Изобретение относится к автоматике и вычислительной технике и может .быть использовано при построении вычислительных систем и устройств, в которых не допускается потеря информации в блоках памяти в моменты переходных процессов при включении и вык- газчении электропитания

Целью изобретения является повьше- ние достоверности работы устройства

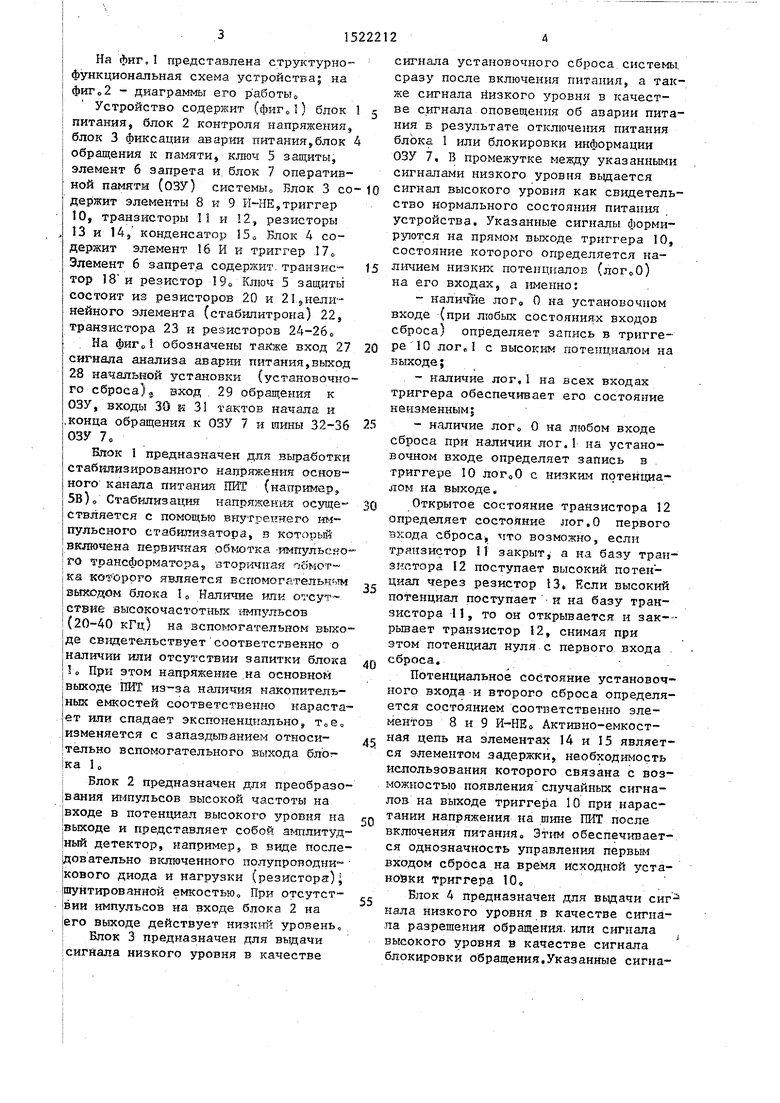

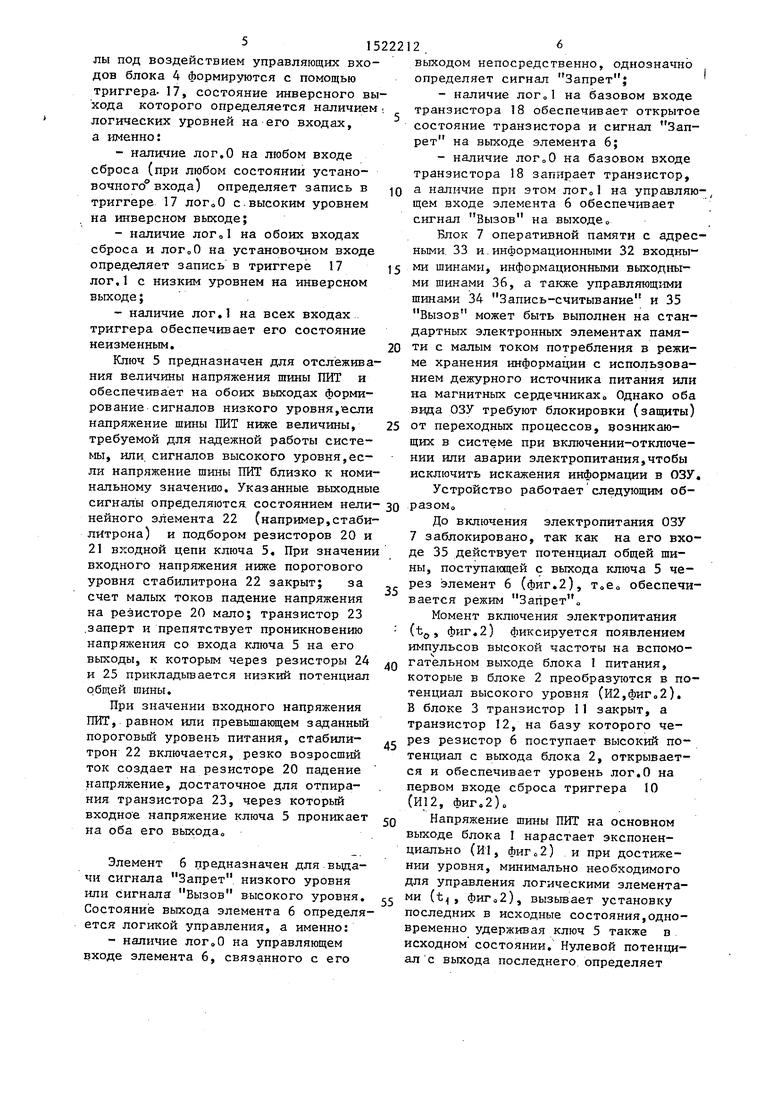

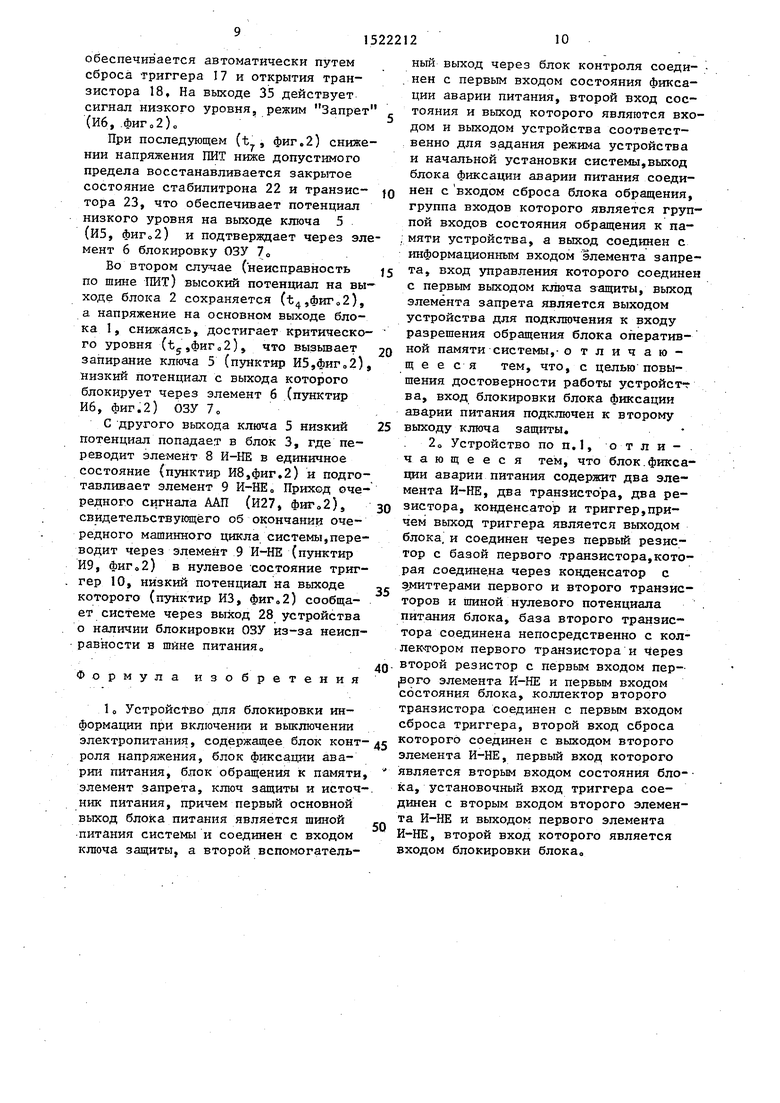

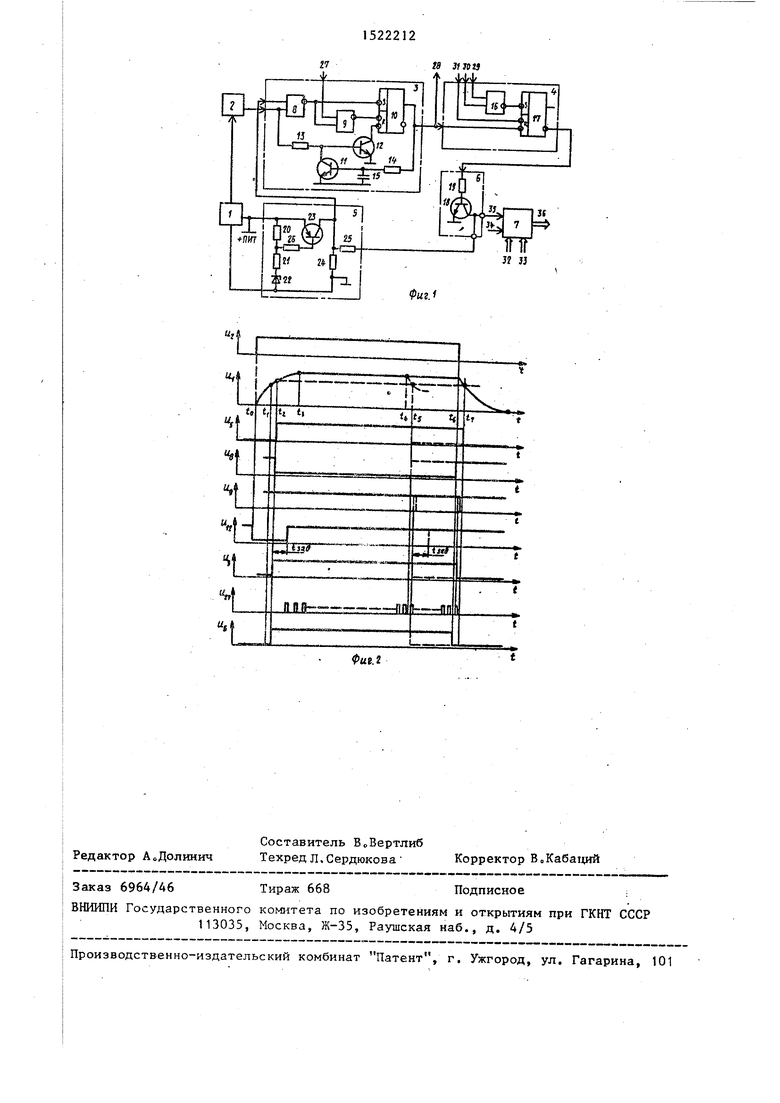

На Лиг,1 представлена структурно- функциональная схема устройства; на фиГо2 - диаграммы его р аботыо

Устройство содержит (фиГо) блок 1 питания, блок 2 контроля напряжения, блок 3 фиксация аварии питания,блок 4 обращения к памяти, ключ 5 защиты, элемент б запрета и, блок 7 оперативной памяти (ОЗУ) системно Блок 3 содержит элементы 8 к 9 ,триггер 10, транзисторы 1 и 12, резисторы 13 и 14, конденсатор 15а Блок 4 содержит элемент 16 И и триггер 17 о Элемент 6 запрета содержит, транзистор 18 и резистор 19о Ключ 5 защиты состоит из резисторов 20 и 215нели- нейного элемента (стабилитрона) 22, транзистора 23 и резисторов 24-26о

На фиго обозначены вход 27 сигнала анализа аварии питания,выход 28 начальной установки (установочно го сброса)J вход . 29 обращения к ОЗУ, входы 30 к 31 тактов начала и конца обращения к ОЗУ 7 и гаины 32-36 ОЗУ 7„

Блок 1 предназначен для выработки стабилизированного напряжения основного канала питания ПИТ (например, 5В)о Стабилизация напряжения осуществляется с помощью внутреннего да1- пульсного стабилизатора, в которьй включена первичная обмотка -импульсяо- I го трансформатора, вторичная OCJMOT- 1 ка ко у оррго является вспомогательньтм I выходом блока 1 Наличие или отсут ствие высокочастотных г мпульсов (20-40 кГц) на вспомогательном вько- де свидетельствует соответственно -о наличии НИИ отсутствии запитки блока , При этом напряжение .на основном выходе ПИТ из-за наличия накопительных емкостей соответственно нарастает или спадает экспоненциально, Тое .1изменяется с запаздьгоанием относи- )тельно вспомогательного выхода бло;- |ка 1„ , I Блок 2 предназначен для преобразо- вания импульсов высокой частоты на входе в потенциал высокого уровня на {вьрсоде и представляет собой амплитуд- |ный детектор, например, в виде после- |довательно включенного полупроводни jKOBoro диода и нагрузки (резистора); шунтированной емкостью При отсутст- |вии импульсов на входе блока 2 на его выходе действует уровень, I Блок 3 предназначен для вьщачи : сигнала низкого уровня в качестве

5

0

5

0

5

0

5.

0

5

сигнгща установочного сброса системы, сразу после включения питания, а также йизкого уровня в качестве сигнала оповещения об аварии питания в результате отключения питания блока 1 или блокировки информации ОЗУ 7, В промежутке между указанными сигналами низкого уровня выдается сигнал высокого уровня как свидетельство нормального состояния питания устройства. Указанные сигналы формируются на прямом выходе триггера 10, состояние которого определяется на- Л1тчием низких потенциалов (логоО) на его входах, а именно:

-налич ив лоГо О на установочном входе (при любых состояниях входов сброса) определяет запись в триггере 10 логв1 с высоким потепциапом на выходе;

-наличие лог,I на всех входах триггера обеспечивает его состояние неизменным;

-наличие лог„ О на любом входе сброса при наличии лог.1 на установочном входе определяет запись в триггере 10 лоГоО с низким потенциалом на выходе.

Открытое состояние транзистора 12 определяет состояние лог,О первого вкода сброса, что возможно, если транзистор II закрыт, а на базу транзистора 2 поступает высокий потенциал через резистор 13 Если высокий потенциал поступает и на базу транзистора П , то он открывается и зак--- рьшает транзистор 12, снимая при этом потенциал нуля с первого входа . сброса.

Потенциальное состояние установочного входа и второго сброса определяется состоянием соответственно зле- менТов 8 и 9 И-РШо Активно-емкостная цепь на элементах 14 и 15 является элементом задержки, необходимость ислользования которого связана с возможностью появления случайных сигналов на выходе триггера 10 при нарастании напряжения на шине ПИТ после включения питания Этим обеспечизает- ся однозначность управления первым входом сброса на время исходной уста- нойки триггера 10

Блок 4 предназначен для вьщачи сигнала низкого уровня в качестве сигнала разрешения обращения, или сигнала высокого уровня в качестве сигнала блокировки обращения.Указанные сигна515

лы под воздействием управляющих входов блока 4 формирзпотся с помощью триггера- 17, состояние инверсного выхода которого определяется наличием логических уровней на его входах, а именно:

-наличие лог,О на любом входе сброса (при любом состоянии установочного входа) определяет запись в триггере 17 логоО с.высоким уровнем

на инверсном выходе;

-наличие лог на обоих входах сброса и лоГоО на установочном входе определяет запись в триггере 17 лог,1 с низким уровнем на инверсном выходе;

-наличие лог,1 на всех входах триггера обеспечивает его состояние неизменным.

Ключ 5 предназначен для отслеживания величины напряжения пганы ПИТ и обеспечивает на обоих выходах формирование сигналов низкого уровня,вели напряжение шины ПИТ ниже величины, требуемой для надежной работы системы, или. сигналов высокого уровня,если напряжение шины ШГГ близко к номинальному значению. Указанные выходны сигналы определяются состоянием нели нейного элемента 22 (например,стабилитрона) и подбором резисторов 20 и 21 входной цепи ключа 5, При значени входного напряжения ниже порогового уровня стабилитрона 22 закрыт; за счет малых токов падение напряжения на резисторе 20 мало; транзистор 23 .заперт и препятствует проникновению напряжения со входа ключа 5 на его выходы, к которым через резисторы 24 и 25 прикладьгаается низкий потенциал общей шины.

При значении входного напряжения ПИТ, равном или превышакидем заданный пороговьй уровень питания, стабили- трон 22 включается, резко возросший ток создает на резисторе 20 падение напряжение, достаточное для отпирания транзистора 23, через который входное напряжение ключа 5 проникает на оба его выхода

Элемент б предназначен для выдачи сигнала Запрет низкого уровня или сигнала Вызов высокого уровня, Состояние выхода элемента 6 определяется логикой управления, а именно:

-наличие лог„О на управляющем входе элемента 6, связанного с его

Q

5

0

5 о д

, п

е

5

126

выходом непосредственно, однозначно определяет сигнал Запрет ;

-наличие лог„1 на базовом входе транзистора 18 обеспечивает открытое состояние транзистора и сигнал Запрет на выходе элемента 6;

-наличие лог„О на базовом входе транзистора 18 запирает транзистор,

а наличие при этом лог на управляющем входе элемента 6 обеспечивает сигнал Вызов на выходе

Блок 7 оперативной памяти с адресными 33 и информационными 32 входными шинами, информационными выходными шинами 36, а также управляющими шинами 34 Запись-считывание и 35 Вызов может быть выполнен на стандартных электронных элементах памяти с малым током потребления в режиме хранения информации с использованием дежурного источника питания или на магнитньпс сердечниках Однако оба вида ОЗУ требуют блокировки (защиты) от переходных процессов, возникающих в системе при включении-отключении или аварии электропитания,чтобы исключить искажения информации в ОЗУ,

Устройство работает следующим об- разомо

До включения электропитания ОЗУ

7заблокировано, так как на его входе 35 действует потенциал общей шины, поступакхцей с выхода ключа 5 через элемент 6 (фиг,2), Тов обеспечивается режим Запрет

Момент включения электропитания (tj,, фиг, 2) фиксируется появлением импульсов высокой частоты на вспомогательном выходе блока 1 питания, которые в блоке 2 преобразуются в потенциал высокого уровня (И2,),

8блоке 3 транзистор 11 закрыт, а транзистор 12, на базу которого через резистор 6 поступает высокий потенциал с выхода блока 2, открывается и обеспечивает уровень лог,О на первом входе сброса триггера 10 (И12, фиг,2)„

Напряжение шины ПИТ на основном выходе блока 1 нарастает экспоненциально (И1, фиго2) и при достижении уровня, минимально необходимого для управления логическими элементами (t, ), вызьшает установку последних в исходные состояния,одновременно удерживая ключ 5 также в исходном состоянии. Нулевой потенциал с выхода последнего определяет

единичное сост.ояние выхода элемента .8 И-НЕ (И8з фмго2) и установочного

входа триггера

благодаря чему

последний под воздействием упомянутого выше нулевого потенциала на входе сброса устанавливается в нулевое исходное состоянивз автоматически обеспечивая на выходе сигнал установочного сброса системы (И35фиГр2) низкого уровня

Этим же сигналом Сброс триггер 17 блока 4 устанавливается в нулевое состояние с высоким потенциалом на инверсном выходе, которьШдпопадая через резистор 19 в базу транзистора 183 открьгоает последнийг чем подтвер/кдает исходное состояние с низким потенци,алом на выводе, элемент а б Напряжение на шшш ПИТ, продолжая нарастать3 достигает заданного нилсне- го уровня питания системы (t,фиг.2)з что создает в схеме ключа 5 условия для включения стабилиг рона 22 и отпирания транзистора 23 На выходах ключа 5 возншсает сигнал высокого уровня (H5s €1)иго2)э который не изменяет состояния на входе 35, ОЗУ 7s так как транвистор 18 открыт (сохраняет™ ся режим Запрет), но .зато з блоке 3 из меняет состояние элемента В K-H S на нулевое (-KSj фиг„2)5, как теперь на обоих его Екодах действую : сигналы высокого уровня В результате на установочный вход триггера «О поступает сигнал лоГоО,. -тто однозначно (независимо от состояния входа сброса) создает на выходе этого триггера сигнал высокого уровня (ИЗ, фиг.2),5 а его на выходе 28 устройства воспринимается системой как сигнал зключения (режим ТТуск) разрешающий вьтолнение заданных операций с доступом к информации ОЗУ 7 о

С этого момента ( фиг,2) устройство переходит Б рабочее состоя- ние а г женног

в блоке 4 снимается активный потенциал лог о О с входа сброса триггера 75 подготавливая его к восприятию сигналов управления системы по входам 29-31 о Доступ к ОЗУ 7 обеспечивается переводом триггера 7 в единичное состояние и запиранием транзистора 18 При этом на выходе 35 действует высокий потенциал разрешения с выхода тсгаоча 5 поступающий через элемент 6 (ИЗ, Ибз фиг„2)г

0

5

0

5

0

-в блоке 3 через активно-емкостную цепь 14, 15 открывается транзистор 11, что закрьгоает транзистор 12, снимая активньй потенциал лого О с первого входа сброса триггера 10 (И12, фиг„2);

-формируемый системой в конце каждого машинного цикла входной сигнал анализа аварии питания (МП), попадая со входа 27 устройства (И27,

фиг,2) на вход элемента 9 И-НЕ. не

меняет его единичное состояние, так как на другом входе этого элемента действует нулевой потенциал с выхода элемента 8 И-НЕ, Тое„ на втором входе сброса триггера 10 поддерживается сигнал высокого уровня (И9, фигс,2)о

Выход системы из онисанного рабочего состояния с блокировкой информации Oiny обеспечивается устройством в двух случаях:

-при снятии (аварии) внешней запитки блока I питания (tg,фигo2)}

- при возникновении в системе ситуации, вызьтающей- критическое снижение напряжения шины ПИТ (tф,фиг,2)„

Б первом случае (авария) момент отключения запитки блока 1 (tg, фиго2) фиксируется по исчезновении импульсов высокой частоты на вспомогательном выходе блока 1 и снятии потенциала высокого уровня с выхода блока 2 (И2, фиг,2)„ В блоке 3 это переводит элемент 8 И-НЕ в единичное состояние (ив, фиго2), что освобождает установочный вход триггера 10 от действия активного нулевого потенциала и подготавливает элемент 9 И-НЕ к приходу очередного сигнала АПП системы (И27, ).

Одновременно напряжение на шине ПИТ (основном выходе блока 1) начинает спадать экспоненциально,некоторое время удерживаясь в пределах заданного допуска (И1, фиг о 2), что сохраняет высокий потенциал на выходе ключа 5 (И5, фиго2) и работоспособность системы в целом, которая, завершая очередной машинный цикл, формирует на входе 27 сш нал ААП (И27, фиго2). В результате в блоке 3 срабатьгоает элемент 9И-НЕ (И9, фиг.2),с выхода которого сигнал лог.О переводит триггер 10 в нулевое состояние (ИЗ, фиг,2) с низким потенциалом на выходе 28 устройства (режим Сброс), чем сообщает системе о факте Снятия питания. Блокировка информации ОЗУ 7

обеспечивается автоматически путем сброса триггера 17 и открытия транзистора 18, На выходе 35 действует сигнал низкого уровня, режим Запрет (И6, .фиго2)„

При последующем (t, фиг.2) снижении напряжения ПИТ ниже допустимого предела восстанавливается закрытое состояние стабилитрона 22 и транзис- тора 23, что обеспечивает потенциал низкого уровня на выходе ключа 5 (И5, фиго2) и подтверяздает через элемент 6 блокировку ОЗУ 7о .

Во втором случае (неисправность по шине пит) высокий потенциал на выходе блока 2 сохраняется (t,UHro2), а напряжение на основном выходе блока 1, снижаясь, достигает критическо- го уровня (t,,фиго2), что вызьшает запирание ключа 5 (пунктир И55фиг„2) низкий потенциал с выхода которого блокирует через элемент б (пунктир И6, фиг.2) ОЗУ 7„

С другого выхода ключа 5 низкий потенциал попадает в блок 3, где переводит элемент 8 И-НЕ в единичное состояние (пунктир И8,фиг.2) и подготавливает элемент 9 И-НЕо Приход очередного сигнала ААП (И27, фиГо2), свидетельствующего об окончании очередного матннного цикла системы,переводит через элемент 9 И-НЕ (пунктир И9, фнго2) в нулевое состояние триггер 10, низкий потенциал на выходе которого (пунктир ИЗ, фиго2) сообщает системе через выход 28 устройства о наличии блокировки ОЗУ из-за неисправности в Шине питания

Формула изобретения

1 о Устройство для блокировки информации при включении и выключении электропитания, содержащее блок конт роля напряжения, блок фиксации аварии питания, блок обращения к памяти элемент запрета, ключ защиты и источ ник питания, причем первый основной выход блока питания является шиной питания системы и соединен с входом ключа защиты, а второй вспомогатбльньш выход через блок контроля соеди- нен с первым входом состояния фиксации аварии питания, второй вход состояния и выход которого являются входом и выходом устройства соответст, венно для задания режима устройства и начальной установки системы,выход блока фиксации аварии питания соединен с входом сброса блока обращения, группа входов которого является группой входов состояния обращения к па, мяти устройства, а выход соединен с информационным входом элемента запрета, вход управления которого соедине с первым выходом ключа защиты, выход элемента запрета является выходом устройства для подключения к входу разрешения обращения блока оперативной памяти системы,- отличающееся тем, что, с целью повышения достоверности работы устройст-г ва, вход блокировки блока фиксации аварии питания подключен к второму выходу ключа защиты, - 2о Устройство по п. 1, о т л и - чающееся тем, что блок.фиксации аварии питания содержит два элемента И-НЕ, два транзистора, два резистора, конденсатор и триггер,причем выход триггера является выходом блока, и соединен через первый резистор с базой первого транзистора,которая соединена через конденсатор с э,миттерами первого и второго транзисторов и шиной нулевого потенциала питания блока, база второго транзистора соединена непосредственно с кол- лек-тором первого транзистора и через второй резистор с первым входом пер-(Вого элемента И-НЕ и первым входом состояния блока, коллектор второго транзистора соединен с первым входом сброса триггера, второй вход сброса которого соединен с выходом второго элемента И-НЕ, первый вход которого является вторым входом состояния блока, установочный вход триггера соединен с вторым входом второго элемента И-НЕ и выходом первого элемента И-НЕ, второй вход которого является входом блокировки блока

ta лпгз

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для блокировки информации в вычислительной системе при включении и выключении электропитания | 1985 |

|

SU1310825A1 |

| Мостовой усилитель | 1989 |

|

SU1693716A2 |

| Устройство реверсирования тока | 1988 |

|

SU1598154A2 |

| Устройство для блокировки и перезапуска ЭВМ при сбоях питания | 1981 |

|

SU993267A1 |

| Формирователь центра тяжести импульсов | 1983 |

|

SU1129581A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для перезапуска и контроля электропитания микроЭВМ | 1989 |

|

SU1797122A1 |

| Устройство для блокировки информации в вычислительной системе при включении и выключении электропитания | 1989 |

|

SU1735853A1 |

| Устройство для блокировки пуска агрегата | 1986 |

|

SU1312520A1 |

| Устройство для дифференциальной защиты | 1988 |

|

SU1610533A2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении вычислительных систем и устройств, в которых не допускается потеря информации в блоках памяти /ОЗУ/ в моменты возникновения переходных процессов при включении и выключении электропитания. Целью изобретения является повышение достоверности работы устройства за счет фиксации аварии питания при любой блокировке ОЗУ, в том числе и вызванной снижением уровня питания ниже критического, а также за счет повышения помехоустойчивости путем формирования сигнала "сброс" без использования дифференцирования напряжения питания. Цель достигается введением новых связей в устройство, содержащее блок контроля питания, блок фиксации аварии питания, блок питания, блок обращения к памяти, ключ защиты и элемент запрета. Устройство нейтрализует действие переходных процессов при включении питания исходной блокировкой ОЗУ по входу "вызов" и формированием системного сигнала "сброс" с момента автоматической фиксации запитки блока питания и до момента достижения напряжением на выходе блока питания номинального уровня, после чего автоматически сигнал "сброс" снимается, а ОЗУ разблокируется. Устройство в рабочем режиме непрерывно отслеживает состояние системы питания и в момент нарушения ее нормального состояния /снятия внешней запитки блока питания или снижения напряжения на выходе блока питания до уровня ниже критического/, защищает ОЗУ путем автоматической блокировки его входа "вызов" с одновременной фиксацией аварии питания, переводящей вычислительную систему в исходное состояние сигналом "сброс" в привязке к концу очередного машинного цикла. 1 з.п.ф-лы, 2 ил.

Авторы

Даты

1989-11-15—Публикация

1988-02-25—Подача