управления и связи. Является дополни тельным к авт.ев, № 873388. Цель нзобретеиия - повьшю.ние стабильности выходных параметров генератора. Для достиясения поставленной цепи в известное устройство наведены преобразователь (П 55 га.рмонт иески; колебаний в постоянное напряжение,, П 56 импульсных сигналов в постояинс напряжениеJ П 58 постоянного напря- ження в цифровой код П 60 частоты в цифровой код, П 61 фазового сдвига в цифровой код 5 второй аттенюатор 17 сигналов синусоидальной формы третий 545 четвертый 57 и пятьш 59 управляемые переключатели, микропроцессор 62, блок 66 cHirtxpouHsauHH,;

Изобретение относится к импульсной технике 5 предназна емо для получения программно управляемых модулированных к немодулированных вьюо- кочастотных () колебаний, низко- частотньп: (НЧ) сигналов я постоянных напряжений и может быть использовано в автоматических информацноыно изкеритель 1ых системах, в автоматшпзс

ких системах управления и связи, в автоматизированные системах контроля электротехнической и радиоэлектронной аппаратуры, тл является усовершенствованием устройства по основноку авт,св.№ 873388.

Цель изобретения - гювьт ег ше стабильности выходных параметров генератора.

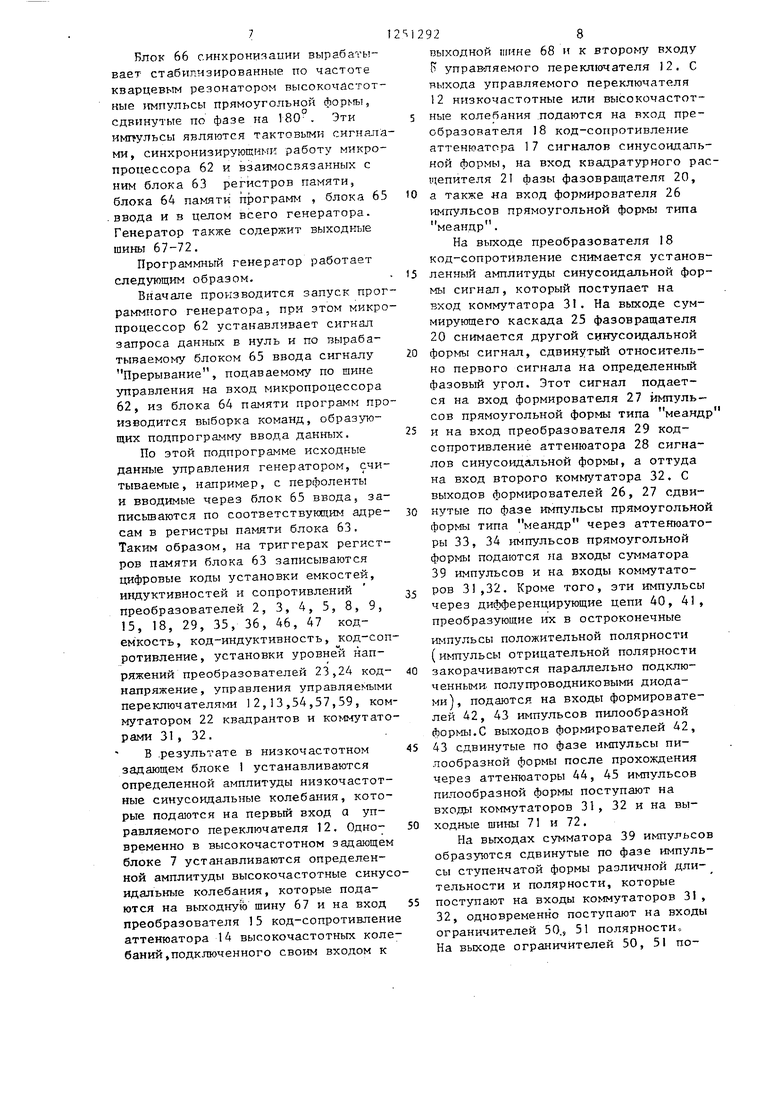

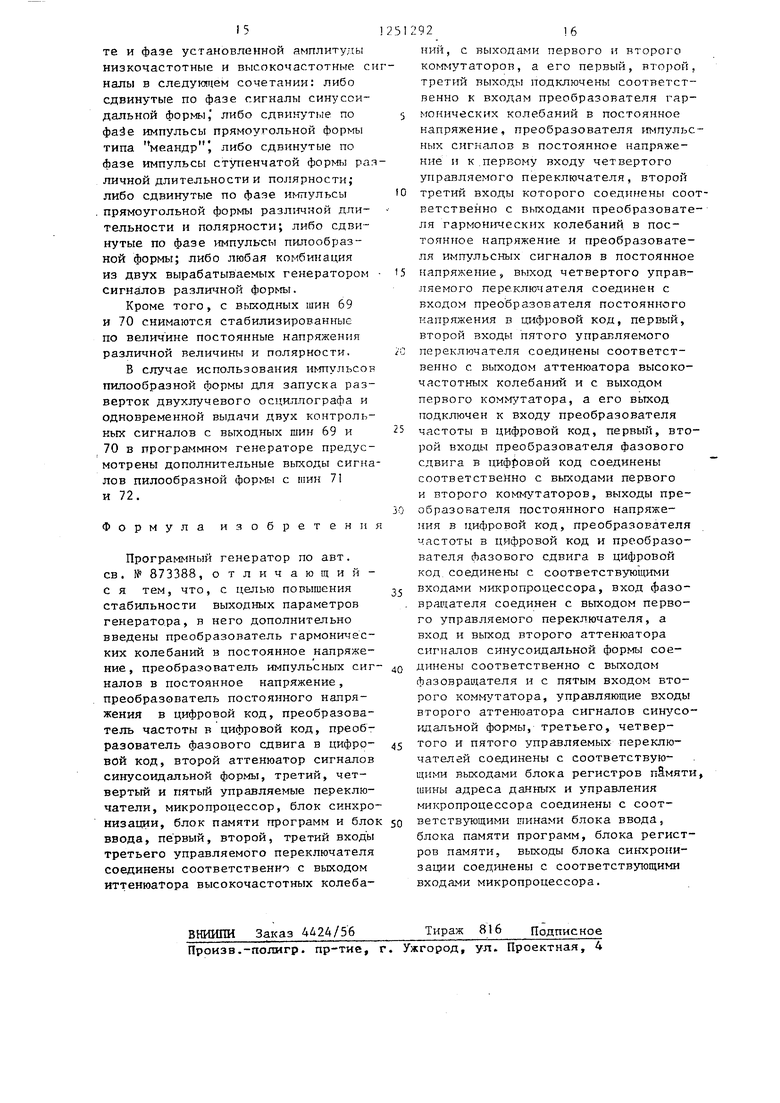

На чертеже предстсшлена функциональная схема програгвдного генератора.

Устройство содержи:т низкочастот- ньш задающий блок 1, вырабатывающий низкочастотные синусоидальные колебания, в который входят первьш,, :i3To- рой преобразователи 2,3 код-емкость первый второй преобразователи 4,5 код-сопротивление5 усилитель б низкой частоты, инвертир1,тощг-й вход которого заземленJ а неишзертируюш,ш вход через последовательно соединенные преобразователи 2 н 4 соединен с преобразователями 3,5 и с выхб, 64 памяти прот рамм и блок 65 ввода В соответствии г заг исанны- ми в регистрах памяти блока 63 цифро кодами с выходных шин 67,68 сн;имаются модулированные и немодулированные высокочастотные колебания соответственно, с шины 67 - мощные высокочастотные колебания, с гаины 68 - ослабленные., стабилизированные по амплитуде и частоте высокочастотные колебания; с выходных тин 69, 70 - стабилизированные по амплитуде, частоте и фазе установленной амплитуды низкочастотные и высокочастотные сигналы в различных сочета н Hytx . ил .

0

дом усилителя 6 высокочастотный за .ца тав;ий блок 7,, вырабатываюигий высокочастотные синусеидгшьные колебания и осу1цествлягощ1те модуляцию иысоко- чястотнь(Х колебаний низкочаптотньми сигналами, содержа1днй преобр зова- талъ 8 код-емкость, преобразо атель 9 код-индуктивность. усилитель 10 высокой частоты и блок 1I модуляции н усиления мощности, причем преобразователь 8 код-емкость, преобразователь 9 код-индуктивность и усилитель 10 высокой частстьз образуют зысокочастотную автоколебательную системуэ выполненную по индуктивной трехточечной схеме, вход и выход преобразователя 8 код-емкость соединены с входом и выходом преобразователя 9 код-индуктивность, средний отвод которого заземлен, Н подклшче- ны к входу и выходу усилителя 10 высокой частоты. Ус:нлитель 10 высокой частоты подключен своим входом к высокочастотному входу блока 11 мо- дуляци;и к усиления мощности, первый уйравляемый переключатель 12, первый; вход которого связан с выходом усилителя 6 5 второй управляемый переключатель 3 выход которого соединен с входом блока 1 модуляции и усиления мощности, аттенюатор 14 высокочастотных колебаний, содержащий преобразователь 15 код-сопротивление и постоянный резистор 16, вы3

ход блокл 11 модуляции н усиления мощности соединен с входом преобразователя 15 код-сопротивление аттенюатора 14 высокочастотшзгх колебаний, подключенного споим выходом к второму входу управляемого переключателя 12, аттенюатор 17 сигна.ао синусоидальной формы, содержащий преобразователь 8 код-сопротивлени и постоянный резистор 19, фазовра- щатель 20, содержащий последовательно соединенный квадратурный расщепитель 21 фазы, коммутатор 22 квадратов, первый, второй выходы которого соединены соответственно с преобразователями 23 и 24 код-напряжение , выходы которых связаны соответственно с первым, вторым входами суммируюпего каскада 25, формирователи 26,27 прямоугольных импульсо типа меандр, причем входы преобразователя 18, квадратурного расщепления 21 фазы, формирователя 26 соединены с выхо/хом управ. гяемого переключателя 12, а вход формирова- теля 21 - с выходом суммирующего каскада 25 и с входом второго аттенюатора 28 сигналов синусоидальной фо.рмы, содержащего преобразователь 29 код-сопротивление, к выходу кото рого подключен постоянный резистор 30, коммутаторы 31,32, выходы которых соответственно соединены с первым и вторым входами управляемого переключателя 13. Выходы формирова- телей 26,27 импульсов прямоугольной формы типа меандр через аттенюаторы 33,34 импульсов прямоугольной формы, состоящие из преобразователей 35,36 код-сопротивление и пос- тоянных резисторов 37, 38, соединены с первыми входами коммутаторов 31 , 32 и с первым, вторым входами сумматора 39 импульсов.

Одновременно выходы формировате- лей 26,27 импульсов прямоугольной формы типа меандр через первую, вторую дифференцирующую цепь 40,41 соединены с входами первого, второго формирователей 42,43 импульсов пилообразной формы, выходы которы 1; через первый, второй аттенюаторы 44,45 импульсов пилообразной формы, состоящие из преобразователей 46, 47 код-сопротивление и постоянных резисторов 48, 49, соединены с вторыми входами коммутаторов 31,32. Первый и второй выходы сумматора 39

2924

импульсов, назначение которого состоит в суммировании сдвинутых по фазе импульсов прямоугольной формы типа меандр и в получении на сво- ITX нагрузках импульсов ступенчатой формы различной длительности и полярности, соединены с третьими входам1{ коммутаторов 31,32 и одновременно соединены с входами первого, второго ограничителей 50,51 полярности, предназначенные д.пя преобразования импульсов ступенчатой формы в и -тульсы прямоугольной формы различной длительности и гголярности Выход ограничителя 50 полярности содинен с входом первой фильтрующей цепи 52 и с четвертым входом коммутатора 31, а выход второго ограничителя 51 полярности соединен с входо второй фильтрующей цепи 53 и с четвертым входом коммутатора 32. Назначение фильтрующих цепей 52, 53 состоит в преобразовании импульсов прямоугольной формы в постоянное напряжение. Выходы фильтрующих цепей 52, 53 соединены с пятыми входами коммутаторов 31, 32.

Первый, второй, третий входы третьего управляемого переключателя 54 соединены соответственно с выходом преобразователя 15 код-сопротивление аттенюатора 14 высокочастотных колебаний и с выходами коммутаторов 31, 32. Первый, второй, третий выходы управляемого переключателя 54 подключены к входам преобразователя 55 гармонических колебаний в постоянное напряжение, преобразователя 56 импульсных сигналов в постоянное напряжение и к первому входу четвертого управляемого переключателя 57, соединенного вторым, третьим входами с выходами преобразователя 55 гармонических колебаний в постоянное напряжение и преобразователя 56 импульсных сигналов в постоянное напряжение. Выход управляемого переключателя 57 соединен с входом преобразователя 58 постоянного напряжения в цифровой код. Первый, второй входы пятого управляемого переключателя 59 соединены с выходом преобразователя 15 код- сопротивление аттенюатора 14 высокочастотных колебаний и с выходом коммутатора 31, а его выход подключен к входу преобразователя 60 частоты в цифровой код.

Входы преобразователя 61 фазового сдвига Е цифровой код соединены с вь ходами коммутаторов 31 и 32, Выходы преобразователя 58 постоянного напряжения н цифровой код преобразователя 60 частоты Е цифровой код и преобразователя 61 фазового сдвига в цифровой код соединены с входами микропроцессора 62,, взаимосвязанного шиной адреса (), ти-- ной управления (ЩУ) и -линой даннык (ШД) с блоком 63 регистров памяти, с блоком 64 памяти программ и с блоком 65 ввода. Синхронизирующий вход, микропроцессора 62 соединен

с выходом блока 66 синкронизацмн.

I

Управляющие входы преобразователей

25 3, 4, 5, 8, 9, 15, 18, 23, 24, 29, 35, 36-, 46, 47, управляемых переключателей 2, 13, 54, 57,, 59, коммутатора 22 квадрантов и коммутаторов 31э32 соединены с соответствующими выходами блока 63 регистров памят

Микропроцессор 62 содержит регистр команд, дешифратор команд ycT ройство управления, рет лстры общего назначения (РОНы,1 ; указатель стека, счетчик команд, регистр адреса, арифметическо-логическое устройство ( А.ИУ 5 регистр признаков,, аккумулятор I интерфейс. Регистр команд предназначен для временного хранения кo aIщы5 выбранной из блока 64 памяти программ. Дешифратор команд преобразует код команды в нуж ггуго последовательность сигналов управления. Устройство управления обеспечивает взаит юдействие различных: блоков микропроп,ессора и взаимосвязанных с Hi-M узлов генератора. Регистры общего назначения предназначены для хранения считанных циф|ровых Кодов, подлежащих обработке Е: арифметичес- ко-логическом устройстве. Указатель стека определяет адрес тех ячеек пак5яти в стеке, в которых хранр;тся: нуяалш адрес возврата из подпрограммы ввода данных в программу обработки вводимых данньп-с. Счетчик команд предназначен ,для управления очередностью считывания команд из блока 64 памяти программ он хранит адрес команды, которая должна выполняться непосредственно за текущей командой Pei HCTp адреса предна;)начен для хранения адресов памяти в течение

0

5

0

времени, которое требуется для Ч х декодирования .Арифметическо-ло- гическое устройство осуществляет арифемтические и логические опера- iiKv, над, цифровымрг кодами.

Регистр признаков со,держит ин- формшдию о результатах вычислений, произведенных в fJW, в частности признак знака. Аккумулятор предназначен для хранения тдафровы с кодов, являющиеся результатом проведенных н ЛЛУ операций. Интерфейс обеспечивает сопряжеггие между блоками микро-процессора и его сопряжение с взаи- мосвяззлными с ним узлами генератора.

Блок 63 регистров памяти является оперативным запоминающим устройством, в состав которого входит набор собранньш на статических триггерах регистров памяти, предназначенных для восприятия записываемых По соответствующим адресам двоичных кодов установки значений параметров элементов генератора и характеристик выходных сигналов, для хранения этих кодов, для воздействия этими кодами на преобразователи 2 3,, 4}

8, 9,

i J

L 23, 24, 29, 35,

0

0

5

46,, 47, управляемое переключит ели 12 „ 13,, 54, 57, 59s коммутаторы 22, 31, 32 и для создания детерминиро- 1эанных изменений установленных параметров и характеристик 5 автоматически изменяемых пропорционально запи- сываем1|ГМ в регистры памяти цифровым кодак. Кроме того, в блоке 63 расположены регистры памяти, используемь е 3 качестве стека, в котором хранятся адреса возврата из -подпрограммы зяода данных в программу обработки ; здодимых данных.

Блюк 64 памяти программ представляет собой постоянное запоминающее . устройство, в нем ззписанъ размещен- Hbie по соответствующим адресам пос- ,педовательности команд, составляю- ш,ие подпрог-рамму ввода данных и пpoгpaJ-I fy обработки вводимьгс дан- н:ьп.

BJEOK 65 ввода обеспечивйет ввод ,:тэ.нных в блок 63 регистров памяти по вырабатываемому им сигналу Прерывание, подаваемому по шине управления на вход микропроцессора 62,

Блок 66 синхронизации вырабатывает стабилизированные по частоте кварцевым резонатором высокочастотные т пульсы прямоугольной , сдвинутые по фазе на 180-. Эти импульсы являются тактовыми сигнрлта ми, синхронизирующими работу микропроцессора 62 и взаимосвязанных с ним блока 63 регистров памяти, блока 64 памяти программ , блока 65 .ввода и в целом всего генератора. Генератор также содержит выходные шины 67-72.

Программный генератор работает следующим образом.

Вначале производится запуск программного генератора, при этом микропроцессор 62 устанавливает сигнал запроса данных в нуль и по вырабатываемому блоком 65 ввода сигналу Прерывание, подаваемому по шине управления на вход микропроцессора 62, из блока 64 памяти программ производится выборка команд, образующих пoдпpoгpaм fy ввода данных.

По этой подпрограмме исходные данные управления генератором, считываемые, например, с перфоленты и вводимые через блок 65 ввода, за- письшаются по соответствующим адресам в регистры памяти блока 63. Таким образом, на триггерах регистров памяти блока 63 записываются цифровые коды установки емкостей, шздуктивностей и сопротивлений преобразователей 2, 3, 4, 5, 8, 9, 15, 18, 29, 35, 36, 46, 47 код- ем кость, код-индуктивность, код-сопротивление , установки ypOBHeli напряжений преобразователей 23,24 код- напряжение, управления управляемыми переключателями 12,13,54,57,59, коммутатором 22 квадрантов и коммутаторами 31, 32.

В .результате в низкочастотном задающем блоке 1 устанавливаются определенной амплитуды низкочастотные синусоидальные колебания, которые подшотся на первый вход а управляемого переключателя 12. Одновременно в высокочастотном задающем блоке 7 устанавливаются определенной амплитуды высокочастотные синусоидальные колебания, которые подаются на выходную шину 67 и на вход преобразователя 15 код-сопротивление аттенюатора 14 высокочастотных колебаний, подключенного своим входом к

S12928

выходной шине 68 и к второкту входу В управляемого переключателя 12. С выхода управляемого переключателя 12 низкочастотные или высокочастот- 5 ные колебания .подаются на вход преобразователя 18 код-сопротивление аттенюатора 17 сигналов синусоидальной формы, на вход квадратурного расщепителя 21 фазы фазовращателя 20, О а также на вход формирователя 26 импульсов прямоугольной формы типа меандр.

На выходе преобразователя 18 код-сопротивление снимается установ- 15 ленный амплитуды синусоидальной формы сигнал, который поступает на вход коммутатора 31. На выходе суммирующего каскада 25 фазовращателя 20 снимается другой синусоидальной 20 формы сигнал, сдвинутый относительно первого сигнала на определенный фазовый угол. Этот сигнал подается на вход формирователя 27 импульсов прямоугольной формы типа меандр 25 и на вход преобразователя 29 код- сопротивление аттенюатора 28 сигналов синусоидальной формы, а оттуда на вход второго кoм ryтaтopa 32. С выходов формирователей 26, 27 сдви- 0 нутые по фазе импульсы прямоугольной формы типа меандр через аттенюаторы 33, 34 импульсов прямоугольной формы подаются на входы сумматора 39 импульсов и на входы коммутато- 5 ров 31,32. Кроме того, эти импульсы через дифференцирующие цепи 40, 41, преобразующие их в остроконечные импульсы положительной полярности (и myльcы отрицательной полярности 0 закорачиваются параллельно подключенными, полупроводниковыми диодами), подаются на входы формирователей 42, 43 импульсов пилообразной формы.С выходов формирователей 42, 5 43 сдвинутые по фазе импульсы пилообразной формы после прохождения через аттенюаторы 44, 45 импульсов пилообразной формы поступают на входы коммутаторов 31, 32 и на вы- 0 ходные шины 71 и 72.

На выходах сумматора 39 импульсов образуются сдвинутые по фазе импульсы ступенчатой формы различной дли- тельности и полярности, которые поступают на входы коммутаторов 31 , 32, одновременно поступают на входы ограничителей 50,, 51 полярности. На выходе ограничителей 50, 51 поляркости сдвинутые по фазе икп гуль- сы ступенчатой форм1з1 преобразугатся в сдвинутые по фазе импульсы прямоугольной различной длительности и полярности. С выхода первого ограничителя 50 полярности прямо-- уг ольньге импульсы положительной полярности подаются на вход фильтруй- щей цепи 52 и на вход первого котлу- татора ас выхода ограничителя 55 полярности прямоугсльныв ш-туль- сы отрицательной полярности подаит- ся на вход второй фильтрующей цепи 53 и ка вход коммутатора 32. Образующееся на выходе фшльтрующей цепи 52 постоянное напряжение положительной полярности подается на вход коммутатора 31, а образующееся на выходе фильтрующей цепи 53 постоянное напряУиение отрицательной полярности подается на вход ко№--г/татора 32 выхода. С выходов комт-гутаторов сигна,пы поступают на первый и второй входы унранпяемого переключателя 13 и одновременно на выходные шины 69, 70.

Одновременно сигналы, снимаемые с выходных шин 69.70; подаются на входы преобразователя б фазового сдви- га в цифровой коДз сигналы., сяршае- мъте с выходных шин 685 69 и 70 „ подаются на входы управляемого переключателя 5А J а сигналь,. сн -1маемы:е с выходных шин , подаются на входы управляемого переключателя . 59.

После запуска генератора и уста новления сигналов на его вькодных гнездах производится стабкл11зация параметров выход1-1ЫХ сигнапов, которая осутцествляется следующим образом.

Пусть, напргечер, на выходной тине 68 осз-тдествляется съем стабилизированных по амплитуде и частоте высо-- кочастотньгх колебания:, а на выход- рпнтах 69 и 70 производится съеу. стабилизированных по амплитуде, частоте и фазе сдвинутых по фазе ни:-з- кочастотньгк и тулъсов прямоугольной формъ типа меандр. В этом случае записаннъп- Ш в регистрах памяти блока 63 1а1фровьгми кодами вход и управляемого переключателя 12 соединен г его ВЫХОДОМ; вход ког-п утатора 31 выхода соединен с его выходом у вход коммутатора 32 эькода соединен с его выходом, вход -упраэляемого

е .

10

ts

20

25

292 .К)

переключателя 54 соединен с его выходом g вход управляемого переключателя 57 соединен с его выходом, вход управляемого переключателя 59 соег- дмнен с его выходом.

Поскольку подпрограмма ввода данных уже завершена; то через посредство указателя стека из стека в счетчик команд заносится адрес первой команды программы обработки вводимых данных,, По выбранной из блока 64 памяти программ команде производится считьгаание цифрового кода, записанного в регистре памяти 63, свя- занньм с преобразователем 15 код-сопротивление, аттенюатора 14 высокочастотных колебаний и цифрового кода, полученного на выходе преобразователя 58 гюстоякного напряжения в цифровой код, Считаннь е цифровые ходы записываются в регистры общего назначения микропроцессора 62 к в АЛУ осуществляется вычитание считанных цифровых кодов. Полученный результат помещается в аккмуля- тор и суммируется в АЛУ (с учетом пЬлученного знака) с записанным s РОНе первоначальным цифровым кодом считанным с регистра блока

0 63, связанного с преобразователем 15 код-сопротивление. Полученный откорректированный код з;шисьтаетск по соответствующему адресу вместо первоначального цифрового кода, коррекк тируя устаковленное значение преобразователя 5 код-сопротивление.. Затем по команде из блока 64 памяти программ осуществляется считывание цифрового кодаз записанного в

jO регистре памяти блока 63, связанным с преобразователем 8 р;од-емкость высокочастотного задакзцего блока 7 и цифрового кода; полученного на ныходе преобразователя 60 частоты в

rj цифровой код. Считанные щфровые коды записываются в регистры общего т азна гения микропроцессора 62 и в AJD осуществляется вычитание считанных цифровьЕХ кодов, полученный результат помещается в aккy ryлктop и суммируется в AJTY (с учетом полу- -енного знака) с записанным в РОНе первоначапьным цифровым кодом, считанным с регистра памяти блока 63, связанного с преобразователем 8 код-емкость. Получеянъгй откорректированный код занисьшается но соот- ветствугацему ад;ресу вместо перво-

50

5Ь

начального цифрового кода, корректируя установленное значение преобразователя 8 код-емкость.

После этого из блока 64 памяти программ считывается команда, по которой цифровыми кодами на соответствующих регистрах памяти блока 63 производится подключение входа управляемого переключателя 54 к его выходу и входа управляемого пере- ключателя 59 к его выходу.

Затем по команде из блока 64 памяти программ производится считывание цифрового кода, записанного в регистре памяти блока 63, связанным с преобразователем 35 код-сопротивление аттенюатора 33 импульсов прямоугольной формы и цифрового код полученного на вькоде преобразователя 58 постоянного напряжения в цифровой код. Считанные цифровые коды записываются в регистры общего назначения микропроцессора 62 и в АЛУ осуществляется вычитание считанных цифровых кодов, полученный ре зультат помещается в аккумулятор и суммируется в АЛУ (с учетом полученного знака) с записанным в РОНе первоначальным цифровым кодом, считанным с регистра памяти блока 63, связанного с преобразователем 35 код-сопротивление. Полученный откорректированный код записывается по соответствующему адресу вместо первоначального цифрового кода, коррек- тируя установленное значение преобразователя 35 код-Сопротивление. Следующим зтапом по команде из блока 64 памяти программ производится считьшание цифровых кодов, записан- ных в регистрах памяти блока 63,связанных с преобразователями 4,5 код- сопротивление низкочастотного щего блока 1 и цифрового кода, полученного на выходе преобразователя 60 частоты в цифровой код. Считанные цифровые коды записываются в регистры общего назначения микропроцессора 62 и в АЛУ осуществляется поочередное вычитание из первого и второго считанных кодов третьего считанного кода, полученные результаты помещаются в аккуь.улятор и суммируются в АЛУ (с учетом полученных знаков) с записанными в РОНах первым и вторым считанным кодами. Полученные откорректированные коды записываются по соответствующим

адресам вместо первоначальных тптф- ровых кодов, корректируя устанор.пеп ные значения преобразователей 4,5 код-сопротивление,

Затем из блока 64 памяти програм считывается команда, по которой циф poBbw кодом ка соответстпугацем регистре памяти блока 63 производит подключение входа управляемого переключателя 54 к его выходу. После этого по команде из блока 64 памяти программ производится считывание цифрового кода, записанного в регистре памяти блока 63, связанным с преобразователем 36 код-сопротивление аттенюатора 34 импульсоп прямоугольной форм111 и цифрового кода , полученного на выходе преобразователя 58 постоянного напряжения в цифровой код.Считанные цифровые коды записываются в регистры общего назначения микропроцессора 62 и в АЛУ осуществляется вычитание считанных ьщфровых кодов, полученный результат помещается в аккумулятор и суммируется в АЛУ (с учетом полученного знака с записанным в РОНе первоначальным цифровым кодом, считанным с регистра памяти блока 63, связанного с преобразователем 36 код-сопротивлени Полученный откорректированньп-1 код записывается по соответствующему адресу вместо первоначального цифрового кода, корректируя установленное значение преобразователя 36 код-соп ротивлен-ие.

Наконец по команде из блока 64 памяти программ производится считывание цифровых кодов, записанных в регистрах памяти блока 63, связанных с преобразователями 23, 24 код-напряжение фазовращателя 20 и цифрового кода, полученного на выходе преобразователя 61 фазового сдвига в цифровой код. Считанные цифровые коды записываются в регистры общего назначения микропроцессора 62, и в АЛУ осуществляется поочередное вычи- тание из первого и второго считанных кодов третьего считанного кода, полу результаты помещаются в аккумулятор и суммируются в АЛУ (с том полученнь х наков) с записапшлми в РОНах первым и вторым считанными кодами. Полученные откорректированнь е коды записываются по соответствующим адресам вместо первоначальных цифровых кодов, корректируя уставовn

.Г1енгш1е значения ираобра юпа-се-пай 2 Т и 24 код 1чалрякен}- е.

Рассмотраин ле прот1;еспы корвакт гpOBK i циклически ПО в or,;iV)T СЯ Кя

протяжет-ип всего интервала opeMeirn требующегося для зьща -га си налсп г втиходгтых ыин 68, о9 и 70 Для го записаи 1ые п -ОНях лервона чапь- иые :ифроные коды., с;г ит;:: --лые с jje- г тстроп пя ят1т: блока 63, сяяза пгьк с преобразопателя-мл. зн чеиля рых корректкр1 10 :-ся., сох раняются и них ка протяжет ии всего f p&MSim С7оема выходн гх сигналов и чсп олъ- зуются в кгтчес гпе orropr::r-:X прт1 корректл|эовк( параметрог слтлгалоя,, С1-л1маемьпс в ачч:; время с r;;,ixor. пин 68, 69 и 70,,

В результ ате с вь:хо; о:ой ;1:( ППз1 58 осуществляе пу я ст-,ем стабштизироваи- ных по , и частот е я- сотсо - частотиьгх ко5 ебапкй„ а г иы-хо,;Ц1Ъ1х шин 69 ;-; 70 осу цсствл,яе : с,я стабилизированных по ai- i/ja-i ryr,;, частоте ); фазе слв--1 - У ы;, по фазе

съем с выходных иж-:: оУ ;: /и с гаГм ,г(изированиых ло ,г м;т; у г.е ,, час ,го - о и фазе сд,зннутьпч по фаз, сягчалп : ,цруг их форм частот ., п тагоке ста- билиз1-шо:йаит ь Х ::о ,г;с вмходн1хх поотоят ных налэяжеул:.

При , ь с,пучае о абчлизации а;uuiHTyiujJ слп-алог С Л-ус оидя, формьц снимаемьге с ь;хо,1 атой шинб t j вход первот о : о: №,;ут;;тор; 31 с-ое,11;я-- -1ен с ет О вьг хлцом; вход у(го,ав,11яекО го пере1;,лючателг; сэ t:,JXT;iGi-T с кг о выходом, вход ;,чтра,влдсгого ттсре ключателя 57 сосгд ан с его дом и ocyiii;ecTB,iin ется Koia:ie-стировка ЗЕ ачсния преобразов.рте,ггя 8 код- солротивлеттие; ,

При CTa6Hjtii3 ai piM й,млJЯiтyдьr скгл ЛОВ СИКуСОИП;аЛ Ь ЯОЙ .-,, ,дной 70, Bxo,t;, xo :yтa- тора 32 соедпнан с вьга:одоМ; П7СОД угуразляеноге пео кз узчатсил 5 соедитгегт с его зыхо,дом 0 :уп-ествлг ется корректтфо вкя ав а-гс-лгия rfpaoR-- разователя 29 коя-сов Г1О ивтто1тие .

При стабляизалик амапи у,г:,г TfN,rny,abcoB т(шюобраз:ной ciopi -rh ., мьпс с выходкой гпинь 69, Bnixoj i; ком-- мутатора 31 соелинги с БЬ;ходо -г пход упрая,дяемово г;е р:яляоч атэ,

14

с-оедииен с его выходом, вход управ- ,; яемого дереключятеля 57 соединен с его выходом и ослпествляется корректировка значения преобразовате- ,яя fj.b код-сопротивление.

При стабилизации амплитуды -1мпул сов пилообразной формы, снимаемых с выходной 70 5 вход коммутатора Н2 соедигчен с его выходом, вход удра,вляемо1 о перею почателя 54 сое- , с его вьжодом к осуществляетс корректировка значения преобразователя 4, код-сопротивление,

При стабилизации величины положи Te,JtbHiiix постоянных напряжений, сни- маеь.фчх с вьг -:одной lumm 69. выход ког. мутаторя 31 соединен с его вы- ходом, Bxo,;i угт-р/авляекого переключат пя 5/-, соединен с С го выходом, вход управляемого переключателя 57 соединен с er,;i выходом и осуществляетс корректт-ровка значения преобразоват ,Я ЗЬ код-сопротивление.

При С абилизации величины отри- г.татеЛЕ. т-.-;с постояннъгх напряженг-ш, с пимаемьк с выходкой щины 70, вход ког.-п- утатора 32 соединен с его выходом., вход управляемого переключатля 54 с, с С:го выходом и осу- ш,зств,дяетсл корректировка -лчачения npao6pa3OBaTejm 36 код-сопрот ивлени

высокочастотных сигналов с вьп1ОД11ь:х шкн 69 и 70 вход S управляемого переключателя 12 еое- ,п,лнен с аг о выxoдo i,

При с-Е.еме высокочастотных коле- папий с выходт гх шин 67 и 68, моду- ,дировап::5 ых низкочбстотныг тн сигнала- ЛИ; сни;чаемЕ тнн с выходной шины 69., -ход управляемого переключателя 13 соединен с его ььгходом, а при моду- ,;:яции сигнш1ами, снимаемыми с выходной шины 70, выход управляемого перетслю -гателя 13 соединен с его входоьт,

Таким образом, в соответствии с запиг анкыми в регистрах памяти блока 63 дифровы1 1и кодами с выходных шин 67 и 68 снимаются модулированные и 1-I.&мо, г,у- 1ирова,нные высокочастотные ко- ггеба гия соответственно с ии ты 67 - , высокочастотные ко,пебания и с типы 68 - ослабленные 5 сгабилкзи- ::оваиные по амплитуде и частоте, вы- г;окочастоные колебания.

На выходах коммутаторов 3 и 32 с пыхо/дньгх ;пин 69 и 70 снимаются ста- блдия-ированные по амплитзще j часто15

те и фазе установленной амплитуды низкочастотные и высокочастотные сналы в следующем сочетании: либо сдвинутые по фазе сигналы синусоидальной формы, либо сдвинутые по фа:3е импульсы прямоугольной формы типа меандр , либо сдвинутые по фазе импульсы ступенчатой формы ра личной длительности и полярности; либо сдвинутые по фазе импульсы . прямоугольной формы разл1-гч1-1ой длительности и полярности; либо сдвинутые по фазе импуль сы пилообразной формы; либо любая комбинация из двух вырабатываемых генератором сигналов различной формы.

Кроме того, с выходных шин 69 и 70 снимаются стабилизированные по величине постоянные напряжения различной величины и полярности,

В случае использования импульсов пилообразной формы для запуска разверток двухлучевого осциллографа и одновременной выдачи двух контрольных сигналов с выходных шин 69 и 70 в программном генераторе предусмотрены дополнительные выходы сигналов пилообразной формы с шин 71 и 72.

Формула изобретения

Программный генератор по авт. св. № 873388, отличающий- с я тем, что, с целью повышения стабильности выходных параметров генератора, в него дополнительно введены преобразователь гармонических колебаний в постоянное напряжение, преобразователь импульсных сиг налов в постоянное напряжение, преобразователь постоянного напряжения в цифровой код, преобразователь частоты в цифровой код, преобразователь фазового сдвига в цифро- вой код, второй аттенюатор сигналов синусоидальной формьт, третий, четвертый и пятый управляемые переключатели, микропроцессор, блок синхронизации, блок памяти программ и бло ввода, пе рвый, второй, третий входы третьего управляемого переключателя соединены соответственно с выходом иттенюатора высокочастотных колебаВНИИПИ Заказ 4i24/56

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

зЮ 5

/о

5

O

5 о 5 0

НИИ, с выходами первого и второго KONfMyTETopoB, а его первый, второй, третий выходы подключены соответственно к входам преобразователя гар- могчических колебаний в постоянное напряжение, преобразователя рп шульс- ных сигналов в постоянное напряжение и к .первому входу четвертого управляемого переключателя, второй третий входы которого соединены соответственно с выходами преобразователя гармонических колебаний в постоянное напряжение и преобразователя импульсных сигналов в постоянное напряжение, выход четвертого управляемого переклю ателя соединен с входом преобразователя постоянного напряжения в цифровой код, первый, второй входы пятого управляемого переключателя соединены соответственно с выходом аттенюатора высокочастотных колебаний и с выходом первого коммутатора, а его выход подключен к входу преобразователя частоты в цифровой код, первый, второй входы преобразователя фазового сдвига в цифровой код соединены соответственно с выходами первого и второго коммутаторов, выходы преобразователя постоянного напряжения в цифровой код, преобразователя частоты в цифровой код и преобразователя фазового сдвига в цифровой код.соединены с соответствующими входами микропроцессора, вход фазо- врагдателя соединен с выходом первого управляемого переключателя, а вход и выход второго аттенюатора сигналов синусоидальной формы соединены соответственно с выходом фазовращателя и с пятым входом второго коммутатора, управляющие входы второго аттенюатора сигналов идапьной формы, третьего, четвертого и пятого управляемых переключателей соединены с соответствующими выходами блока регистров п9.мяти, шины адреса данных и управления микропроцессора соединены с соответствующими ягинами блока ввода, блока памяти программ, блока регистров памяти, выходы блока синхронизации соединены с соответствующими входами микропроцессора.

Тираж 816 Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Программный генератор | 1980 |

|

SU917319A1 |

| Программный генератор | 1982 |

|

SU1051688A2 |

| Программный генератор | 1983 |

|

SU1190484A1 |

| Инфранизкочастотный программный генератор | 1980 |

|

SU919055A1 |

| Программный генератор | 1982 |

|

SU1062858A2 |

| Програмный генератор | 1979 |

|

SU873388A1 |

| Программный генератор | 1980 |

|

SU951656A2 |

| Устройство автоматической установки калиброванных уровней сигнала | 1985 |

|

SU1318922A1 |

| Тестер контроля и диагностики электронных модулей | 1986 |

|

SU1396099A1 |

| УСТРОЙСТВО ДЛЯ ИССЛЕДОВАНИЯ БИОЛОГИЧЕСКОЙ АКТИВНОСТИ МОЗГА | 1993 |

|

RU2076625C1 |

Изобретение относится к импульсной технике. Предназначено для получения программно управляемь1х модулированных и немодулированных высокочастотных колебаний, низкочастотных сигналов и постоянных напряжений. Может быть использовано в автоматических информационно-измерительных системах, в автоматических системах б а S ел (пА ho rv9 o

| Програмный генератор | 1979 |

|

SU873388A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-08-15—Публикация

1983-07-01—Подача