$3

(Л

со

со

05

о (Х

;о

ияющий блок 2, индикатор 3, печатающий блок 4, измеритель 5 дискретных сигналов, коммутатор 7, генератор 8 дискретных сигналов, пульт 17 ввода данных, блок 18 срав- и шинный формирователь 19. Введение измерителя 6 аналоговых сигналов, генератора 9 аналоговых сигналов, блока Ц) памяти коммутатора, измерителя 11 сопротивлений и напряжений блока 12 обмена, блоков 13 и 14 генерации и контроля сиг- йалов произвольной формы, генератора 15 Последовательного кода, генератора 16 тестов и измерительного резистора 20 обеспечивает контроль и диагностику модулей аналого-дискретного типа, программируемых контролеров с различными системами команд и интерфейсов. В описании приведены примеры реализации коммутатора 7, блока 10 памяти, диспетчера 1, блока 12 обмена, блока 13 генерации сигналов произвольной формы, блока 14 контроля сигналов произвольной формы, генератора 16 тестов и блока 18 сравнения. 8 з.п. ф-лы, 9 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ТЕЛЕФОННЫМИ ЛИНИЯМИ СВЯЗИ | 1992 |

|

RU2006927C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ ПАРАМЕТРОВ НАПРЯЖЕНИЯ | 1990 |

|

RU2018147C1 |

| Устройство для ввода в электронную вычислительную машину величин измеряемых параметров быстропеременных и пульсирующих потоков жидкости и газа | 1982 |

|

SU1054824A1 |

| Цифровой измеритель угловой скорости | 1985 |

|

SU1275292A1 |

| Устройство для контроля узлов электронных вычислительных машин | 1976 |

|

SU667969A1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| Система для контроля параметров | 1985 |

|

SU1255996A1 |

Изобретение относится к технике автоматизированного контроля и может быть использовано в устройствах как модуль гибких ироизводственных систем. Цель изобретения - расширение области применения и функциональных возможностей и повышение производительности устройства. Тестер содержит диспетчер 1, запол

1

И.зобретение относится к технике автоматизированного контроля и может быть использовано в устройствах как модуль гибких производственных систем или в качестве средства цехового экономического контроля при мелкосерийном производстве электронных модулей, отличающихся широким спектром выполняемых функций.

Целью изобретения является расширение области применения и функциональных возможностей, заключающееся в обес- печении контроля и диагностики модулей аналого-диск ретного типа, программируемых контроллеров с различными системами команд и интерфейсов при повышении производительности за счет упрощения испы- тательных программ.

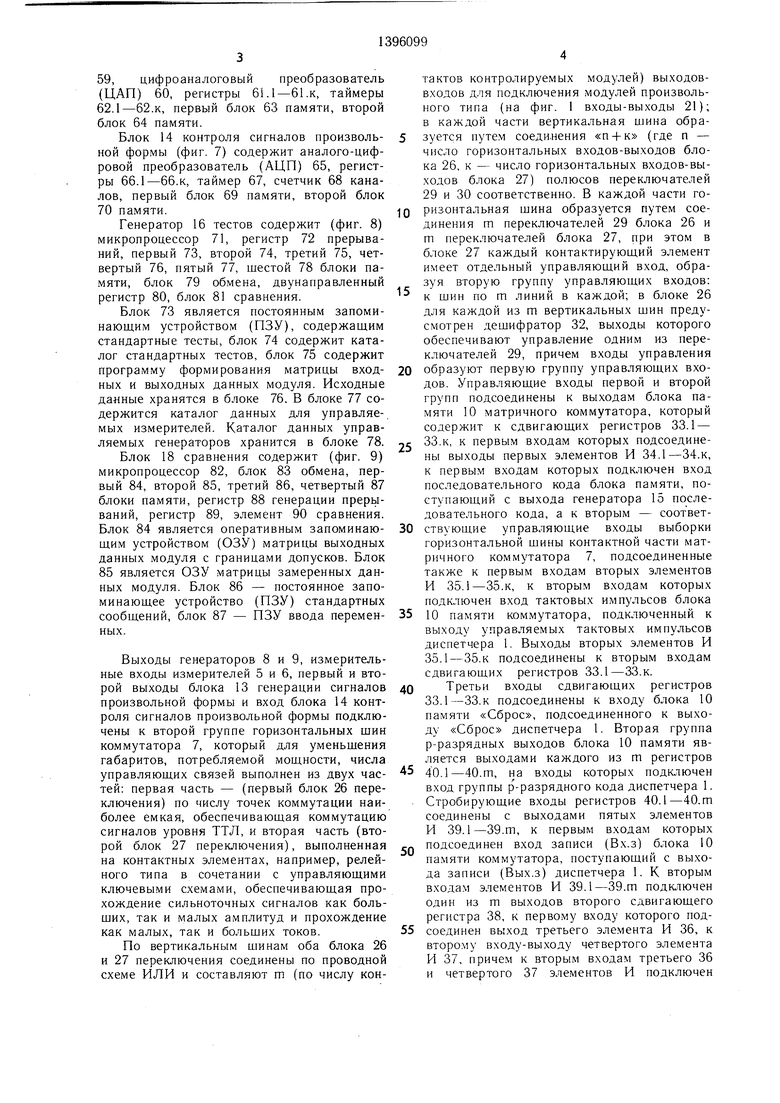

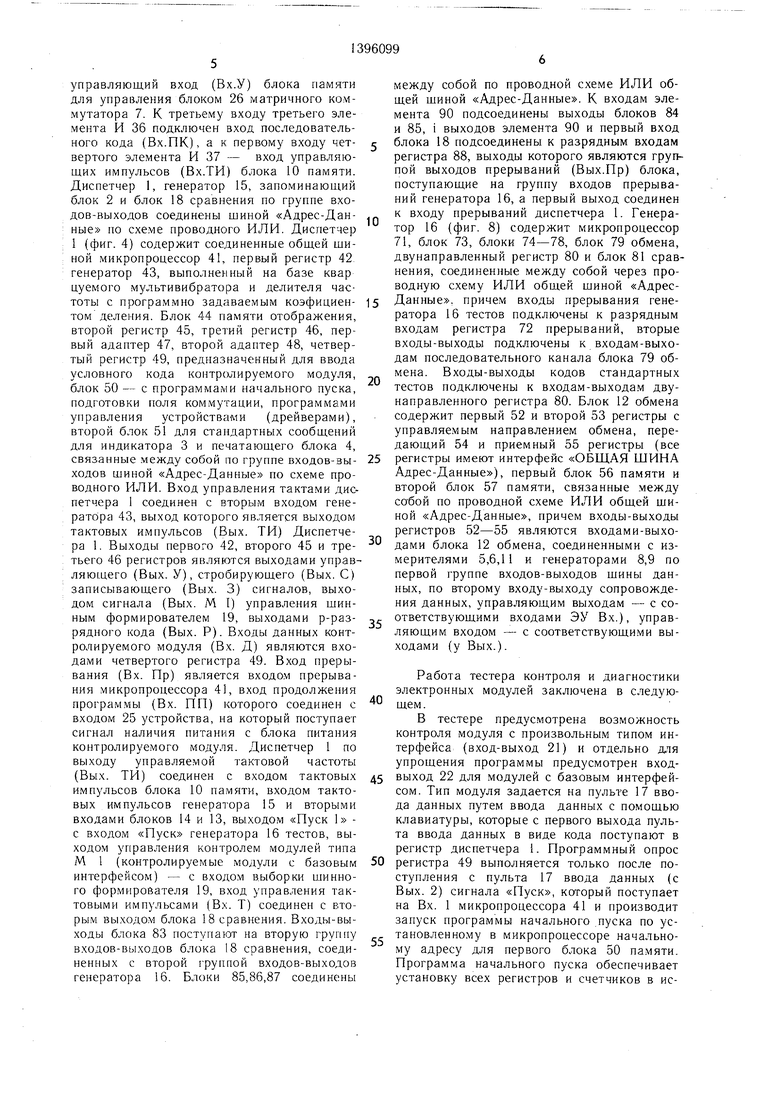

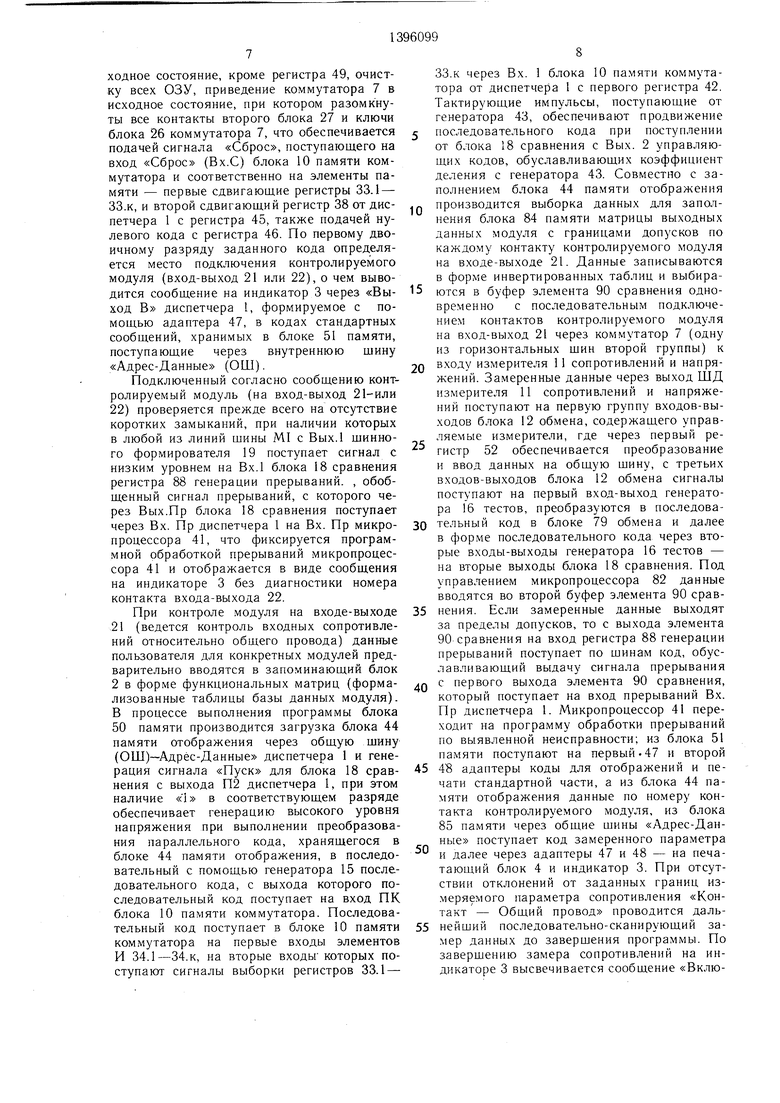

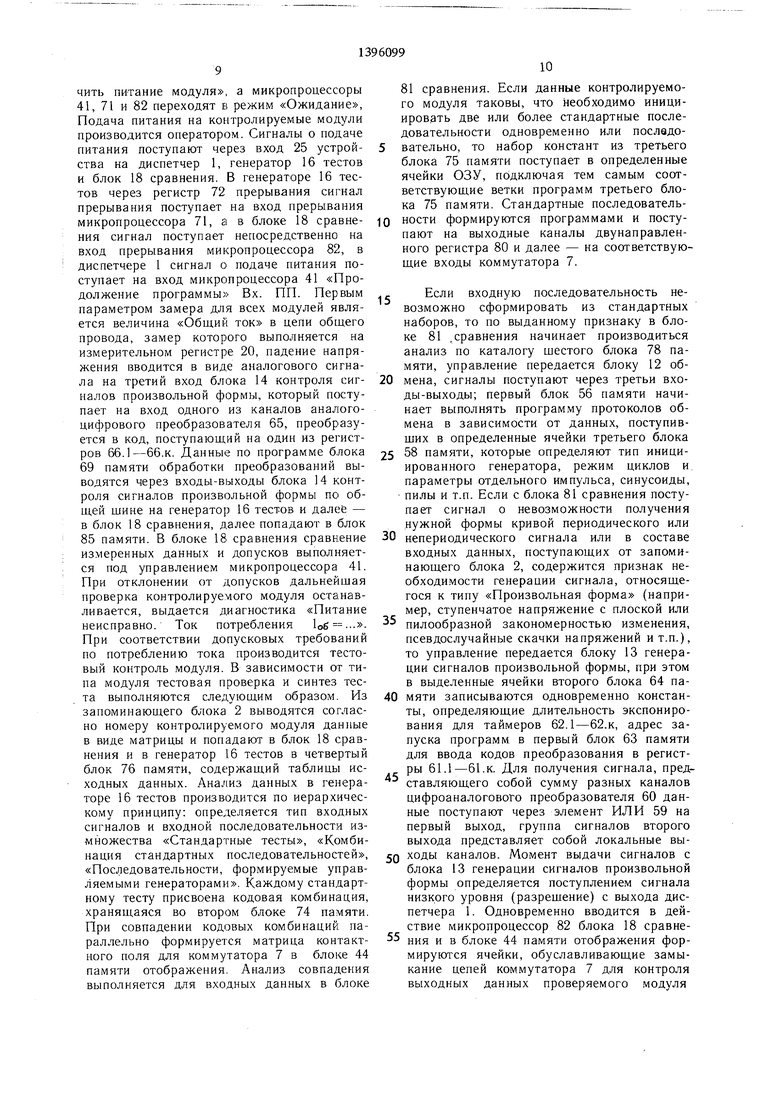

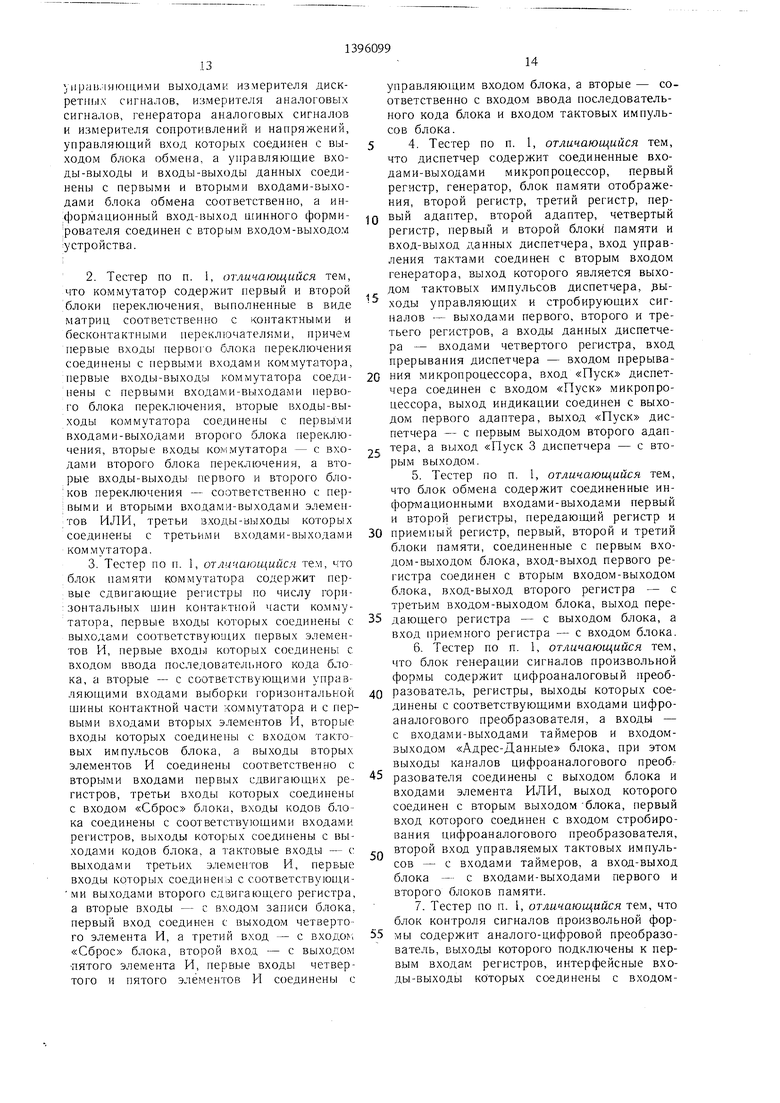

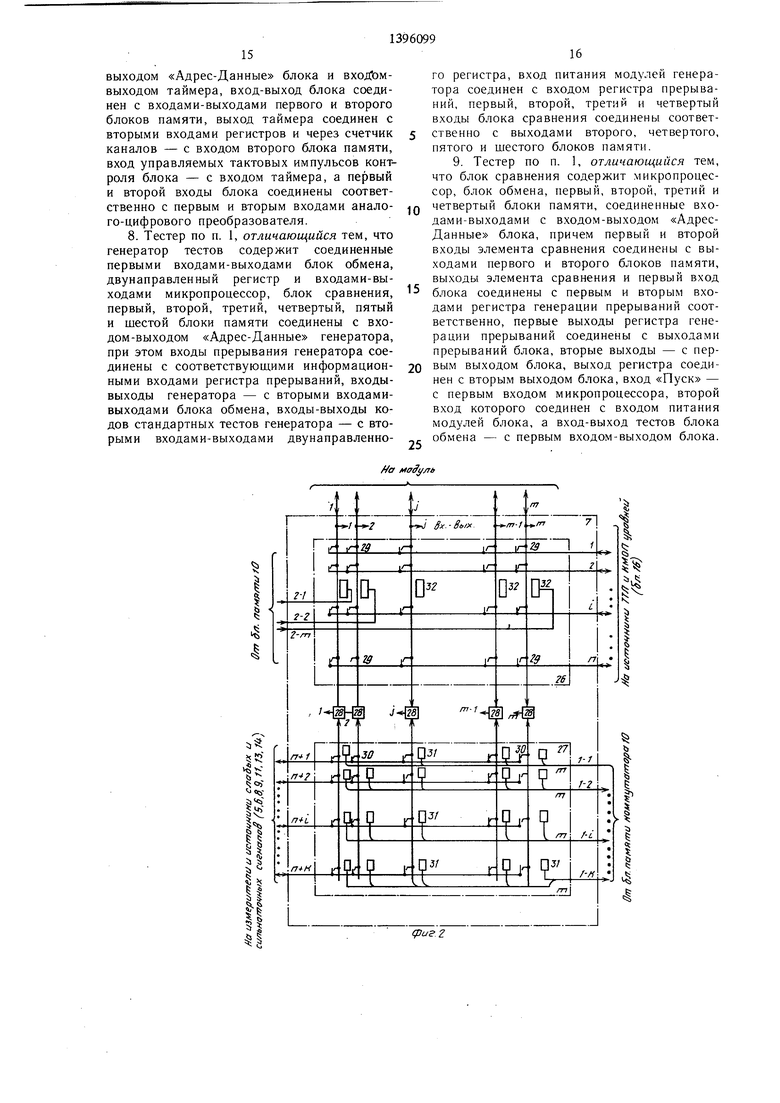

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема коммутатора; на фиг. 3 - структурная схема блока памяти; на фиг. 4 - структурная схема диспетчера; на фиг. 5 - струк- турная схема блока обмена; на фиг. 6 - структурная схема блока генерации сигналов произвольной формы; на фиг. 7 - структурная схема блока контроля сигналов произвольной формы; на фиг. 8 - структурная схема генератора тестов; на фиг. 9 - структурная схема блока сравнения.

Тестер контроля и диагностики электронных модулей содержит {фиг. 1) диспетчер 1, запоминающий блок 2, индикатор 3, печатающий блок 4, измеритель 5 дискрет- ных сигна лов, измеритель 6 аналоговых сигналов, коммутатор 7, генератор 8 дискретных сигналов, генератор 9 аналоговых сигналов, блок 10 памяти коммутатора, измеритель П сопротивлений и напряжений, блок 12 обмена, блок 13 генерации сигналов произвольной формы, блок 14 контроля сигналов произвольной формы, генератор 15 последовательного кода, генератор 16 тестов, пу. от 17 ввода данных, блок 18 сравнения, шинный формирователь 19, измерительный резистор 20, первый 21 и второй 22 входы-выходы устройства соответственно, общую шину 23 источника, общую шину 24 модуля, вход 25 наличия питания.

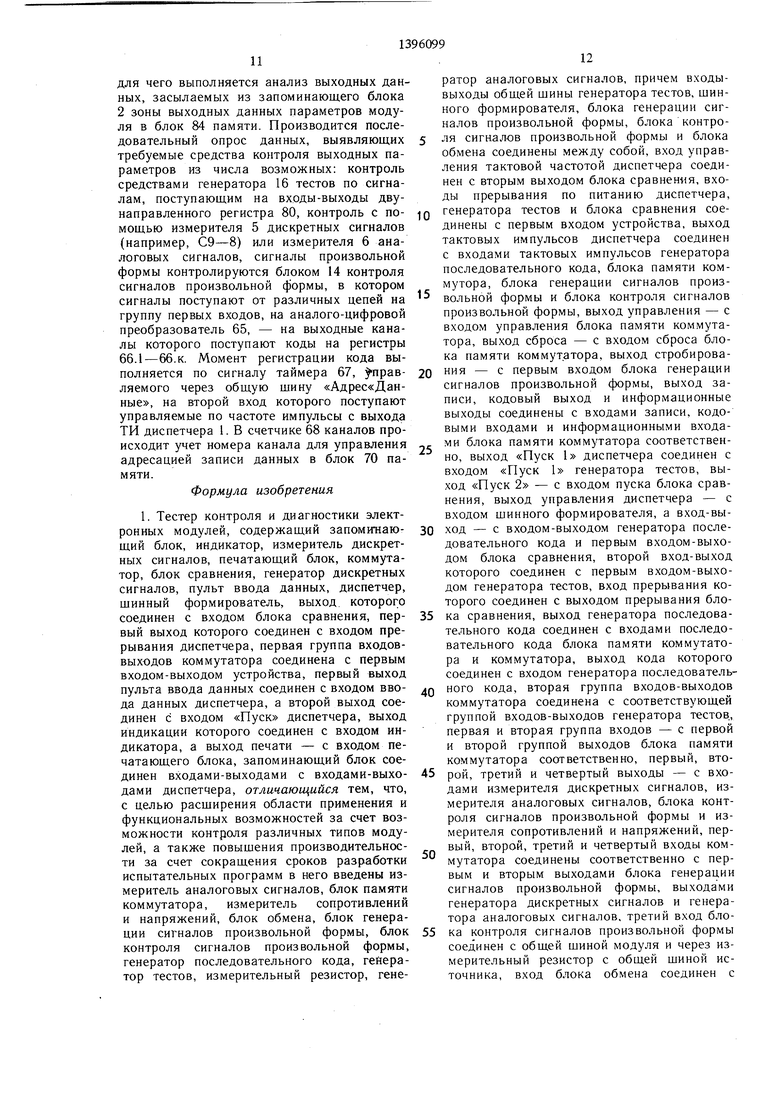

Коммутатор 7 (фиг. 2) содержит первый блок 26 переключения, являющийся частью коммутатора и выполненный на бесконтактных элементах, второй блок 27 переключения, являющийся частью коммутатора и выполненный на контактных структурах, элементы 28..т ИЛИ, связывающие вертикальные шины матрицы на контактных и бесконтактных структурах и реализующие проводную функцию ИЛИ, переключатель 29, бесконтактный для сигналов ТТЛ и КМОП уровней (-15в-ч-15в), переключатель 30, контактный для сильноточных сигналов с низкими и высокими напряжениями, управляющий элемент 31 контактного переключателя, дещифратор 32 бесконтактного переключателя.

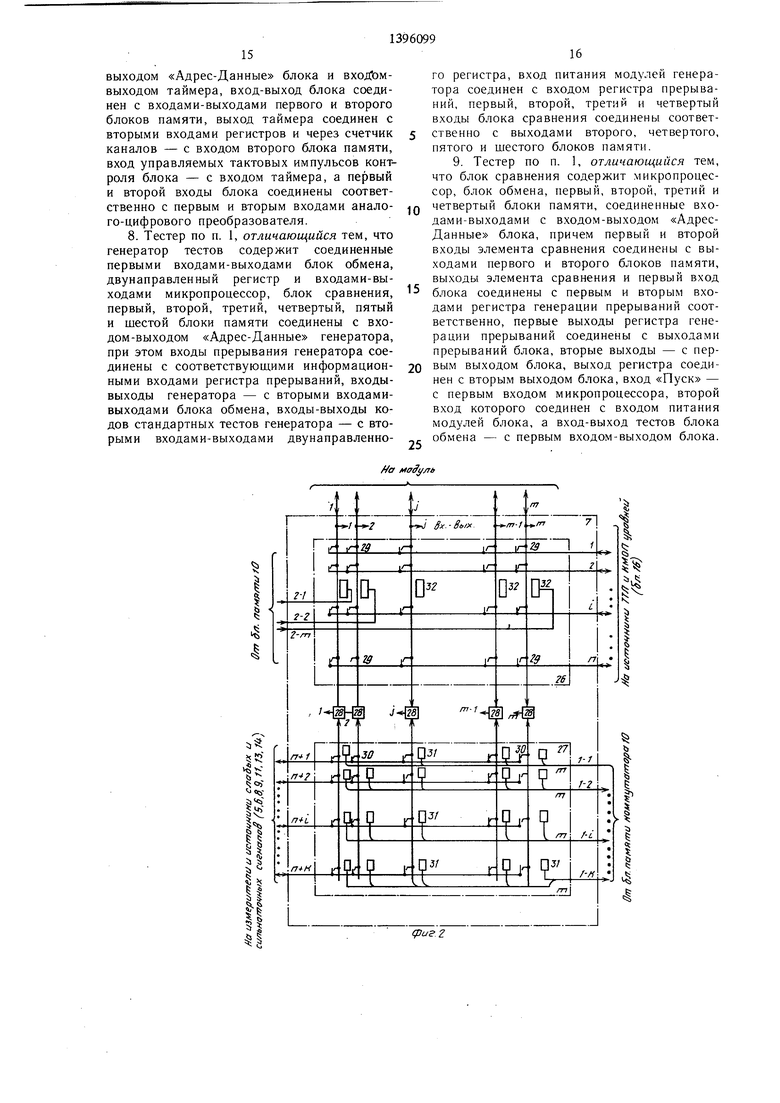

Блок 10 памяти коммутатора (фиг. 3) содержит первые сдвигающие регистры 33.1-33.к, первые элементы И 34.1-34к, вторые элементы И 35.1-35.к, третий элемент И 36, четвертый элемент И 37, второй сдвигающий регистр 38, пятые элементы И 39.1-39.т, регистры 40.1-40. т.

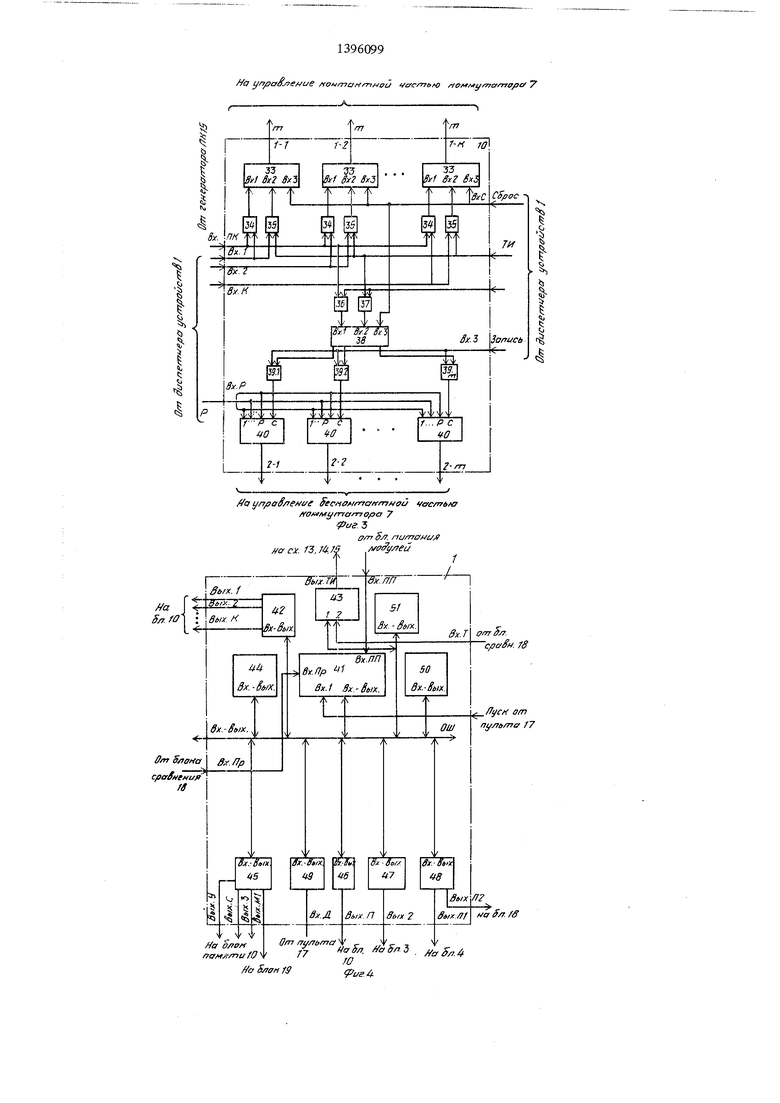

Диспетчер 1 (фиг. 4) содержит микропроцессор 41, первый регистр 42, генератор 43, блок 44 памяти отображения, второй регистр 45, третий регистр 46, первый адеп- тер 47, второй адептер 48, четвертый регистр 49, первый 50 и второй 51 блоки памяти.

Блок 12 обмена (фиг. 5) содержит первый регистр 52, второй регистр 53, передающий регистр 54, приемный регистр 55, первый блок 56 памяти, блок 57 памяти, третий блок 58 памяти.

Блок 13 генерации сигналов произвольной формы (фиг. 6) содержит элемент ИЛИ

59, цифроаналоговый преобразователь (ЦАП) 60, регистры 61.1-61.к, таймеры 62.1-62.к, первый блок 63 памяти, второй блок 64 памяти.

Блок 14 контроля сигналов произвольной формы (фиг. 7) содержит аналого-цифровой преобразователь (АЦП) 65, регистры 66.1-66.к, таймер 67, счетчик 68 каналов, первый блок 69 памяти, второй блок 70 памяти.

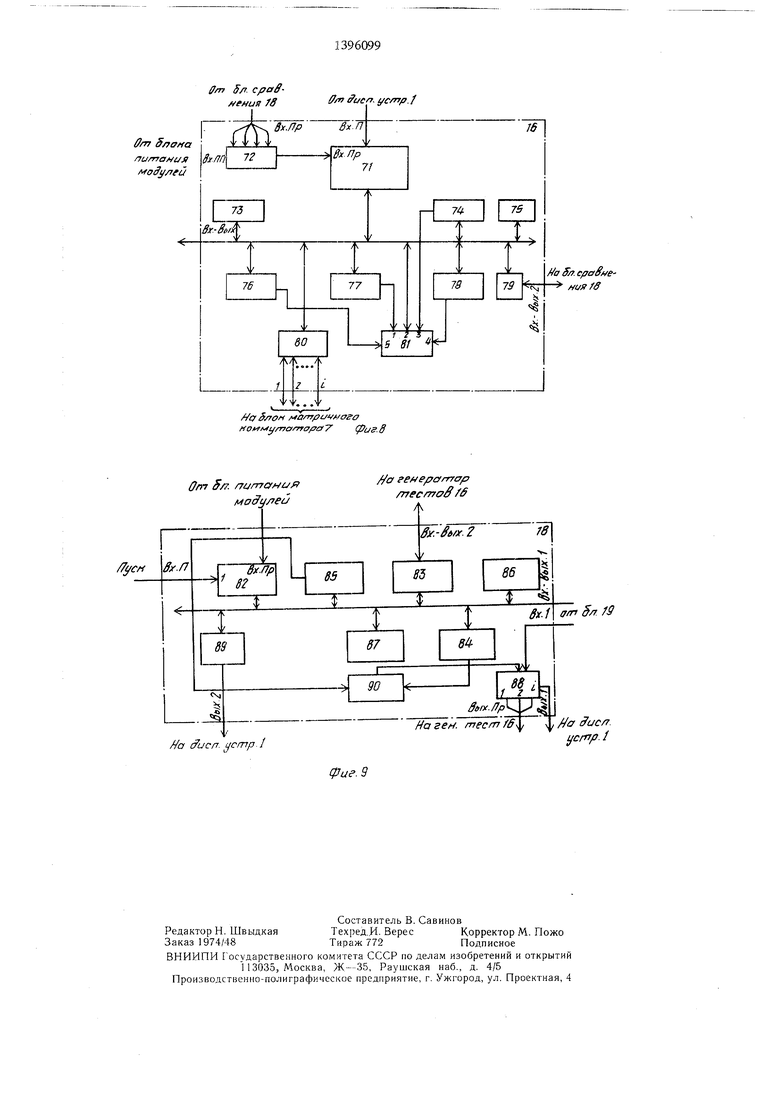

Генератор 16 тестов содержит (фиг. 8) микропроцессор 71, регистр 72 прерываний, первый 73, второй 74, третий 75, четвертый 76, пятый 77, шестой 78 блоки памяти, блок 79 обмена, двунаправленный регистр 80, блок 81 сравнения.

Блок 73 является постоянным запоминающим устройством (ПЗУ), содержащим стандартные тесты, блок 74 содержит каталог стандартных тестов, блок 75 содержит программу формирования матрицы входных и выходных данных модуля. Исходные данные хранятся в блоке 76. В блоке 77 содержится каталог данных для управляемых измерителей. Каталог данных управляемых генераторов хранится в блоке 78.

Блок 18 сравнения содержит (фиг. 9) микропроцессор 82, блок 83 обмена, первый 84, второй 85, третий 86, четвертый 87 блоки памяти, регистр 88 генерации прерываний, регистр 89, элемент 90 сравнения. Блок 84 является оперативным запоминающим устройством (ОЗУ) матрицы выходных данных модуля с границами допусков. Блок 85 является ОЗУ матрицы замеренных данных модуля. Блок 86 - постоянное запоминающее устройство (ПЗУ) стандартных сообщений, блок 87 - ПЗУ ввода переменных.

Выходы генераторов 8 и 9, измерительные входы измерителей 5 и 6, первый и второй выходы блока 13 генерации сигналов произвольной формы и вход блока 14 контроля сигналов произвольной формы подключены к второй группе горизонтальных шин коммутатора 7, который для уменьшения габаритов, потребляемой мощности, числа управляющих связей выполнен из двух частей: первая часть - (первый блок 26 переключения) по числу точек коммутации наиболее емкая, обеспечивающая коммутацию сигналов уровня ТТЛ, и вторая часть (второй блок 27 переключения), выполненная на контактных элементах, например, релейного типа в сочетании с управляющими ключевыми схемами, обеспечивающая прохождение сильноточных сигналов как больших, так и малых амплитуд и прохождение как малых, так и больших токов.

По вертикальным шинам оба блока 26 и 27 переключения соединены по проводной схеме ИЛИ и составляют ш (по числу контактов контролируемых модулей) выходов- входов для подключения модулей произвольного типа (на фиг. 1 входы-выходы 21); в каждой части вертикальная шина образуется путем соединения «п + к (где п - число горизонтальных входов-выходов блока 26, к - число горизонтальных входов-выходов блока 27) полюсов переключателей 29 и 30 соответственно. В каждой части гоQ ризонтальная шина образуется путем соединения m переключателей 29 блока 26 и m переключателей блока 27, при этом в блоке 27 каждый контактирующий элемент имеет отдельный управляющий вход, образуя вторую группу управляющих входов:

к шин по m линий в каждой; в блоке 26 для каждой из m вертикальных шин предусмотрен дешифратор 32, выходы которого обеспечивают управление одним из переключателей 29, причем входы управления

0 образуют первую группу управляющих входов. Управляющие входы первой и второй групп подсоединены к выходам блока памяти 10 матричного коммутатора, который содержит к сдвигающих регистров 33.1 -

5 33.к, к первым входам которых подсоединены выходы первых элементов И 34.1-34.к, к первым входам которых подключен вход последовательного кода блока памяти, поступающий с выхода генератора 15 последовательного кода, а к вторым - соответ0 ствующие управляющие входы выборки горизонтальной шины контактной части матричного коммутатора 7, подсоединенные также к первым входам вторых элементов И 35.1-35.к, к вторым входам которых подключен вход тактовых импульсов блока

5 10 памяти коммутатора, подключенный к выходу управляемых тактовых импульсов диспетчера 1. Выходы вторых элементов И 35.1-35.к подсоединены к вторым входам сдвигающих регистров 33.1-33.к.

0 Третьи входы сдвигающих регистров 33.1-33.к подсоединены к входу блока 10 памяти «Сброс, подсоединенного к выходу «Сброс диспетчера 1. Вторая группа р-разрядных выходов блока 10 памяти является выходами каждого из m регистров

5 40.1-40.т, на в.ходы которых подключен вход группы р-разрядного кода диспетчера 1. Стробирующие входы регистров 40.1-40.ш соединены с выходами пятых элементов И 39.1-39.т, к первым входам которых

- подсоединен вход записи (Вх.з) блока 10 памяти коммутатора, поступающий с выхода записи (Вых.з) диспетчера 1. К вторым входам элементов И 39.1-39.m подютючен один из ш выходов второго сдвигающего регистра 38, к первому входу которого под5 соединен выход третьего эле.мента И 36, к второму входу-вы.ходу четвертого элемента И 37, причем к вторым входам третьего 36 и четвертого 37 элементов И подключен

10

управляющий вход (Вх.У) блока памяти для управления блоком 26 матричного коммутатора 7. К третьему входу третьего элемента И 36 подключен вход последовательного кода (Вх.ПК), а к перЕЮму входу четвертого элемента И 37 - вход управляющих импульсов (Вх.ТИ) блока 10 памяти. Диспетчер 1, генератор 15, запоминающий блок 2 и блок 18 сравнения по группе входов-выходов соединены шиной «Адрес-Данные по схеме проводного ИЛИ. Диспетчер 1 (фиг. 4) содержит соединенные общей шиной микропроцессор 41, первый регистр 42, генератор 43, выполненный на базе квар цуемого мультивибратора и делителя частоты с программно задаваемым коэфициен- 15 том деления. Блок 44 памяти отображения, второй регистр 45, третий регистр 46, первый адаптер 47, второй адаптер 48, четвертый регистр 49, предназначенный для ввода условного кода коптролируемого модуля, блок 50 - с программами начального пуска, подготовки поля коммутации, программами управления устройствами (дрейверами), второй блок 51 для стандартных сообщений для индикатора 3 и печатающего блока 4,

20

между собой по проводной схеме ИЛИ общей щиной «Адрес-Данные. К входам элемента 90 подсоединены выходы блоков 84 и 85, i выходов элемента 90 и первый вход блока 18 подсоединены к разрядным входам регистра 88, выходы которого являются группой выходов прерываний (Вых.Пр) блока, поступающие на группу входов прерываний генератора 16, а первый выход соединен к входу прерываний диспетчера 1. Генератор 16 (фиг. 8) содержит микропроцессор 71, блок 73, блоки 74-78, блок 79 обмена, двунаправленный регистр 80 и блок 81 сравнения, соединенные между собой через проводную схему ИЛИ общей шиной «Адрес- Данные, причем входы прерывания генератора 16 тестов подключены к разрядным входам регистра 72 прерываний, вторые входы-выходы подключены к входам-выходам последовательного канала блока 79 обмена. Входы-выходы кодов стандартных тестов подключены к входам-выхода.м двунаправленного регистра 80. Блок 12 обмена содержит первый 52 и второй 53 регистры с управляемым направлением обмена, передающий 54 и приемный 55 регистры (все

связанные между собой по группе входов-вы- 25 регистры имеют интерфейс «ОБЩАЯ ШИНА ходов шиной «Адрес-Данные по схеме про-Адрес-Данные), первый блок 56 памяти и

второй блок 57 памяти, связанные между собой по проводной схеме ИЛИ общей щиной «Адрес-Данные, причем входы-выходы регистров 52-55 являются входам и-выховодного ИЛИ. Вход управления тактами диспетчера 1 соединен с вторым входом гене- paTdpa 43, выход которого яв.ляется выходом тактовых импульсов (Вых. ТИ) Диспетчера 1. Выходы первого 42, второго 45 и третьего 46 регистров являются выходами управляющего (Вых. У), стробирующего (Вых. С) записывающего (Вых. 3) сигналов, выходом сигнала (Вых. М I) управления шиндами блока 12 обмена, соединенными с измерителями 5,6,11 и генераторами 8,9 по первой группе входов-выходов шины данных, по второму входу-выходу сопровождения данных, управляющим выходам - с со35

ляющим входом ходами (у Вых.)

с соответствующими вы40

ным формирователем 19, выходами р-раз- ответствующими входами ЭУ Вх.), управ- рядного кода (Вых. Р). Входы данных контролируемого модуля (Вх. Д) являются входами четвертого регистра 49. Вход прерывания (Вх. Пр) является входом прерывания микропроцессора 41, вход продолжения программы (Вх. ПП) которого соединен с входом 25 устройства, на который поступает сигнал наличия питания с блока питания контролируемого модуля. Диспетчер 1 по выходу управляемой тактовой частоты (Вых. ТИ) соединен с входом тактовЕ х импульсов блока 10 памяти, входом тактовых импульсов генератора 15 и вторыми входами блоков 14 и 13, выходом «Пуск 1 - с входом «Пуск генератора 16 тестов, выходом управления контролем модулей типа М 1 (контролируемые модули с базовым интерфейсом) - с входом в.ыборки шинного формирователя 19, вход управления тактовыми импульсами (Вх. Т) соединен с вторым вы.ходом блока 18 сравнения. Входы-выходы блока 83 поступают на вторую группу входов-выходов блока 18 сравнения, соединенных с второй группой входов-выходов генератора 16. Блоки 85,86,87 соединены

Работа тестера контроля и диагностики электронных модулей заключена в следующем.

В тестере предусмотрена возможность контроля модуля с произвольным типом интерфейса (вход-выход 21) и отдельно для упрощения программы предусмотрен вход45 выход 22 для модулей с базовым интерфейсом. Тип модуля задается на пульте 17 ввода данных путем ввода данных с помощью клавиатуры, которые с первого выхода пульта ввода данных в виде кода поступают в регистр диспетчера 1. Программный опрос

50 регистра 49 выполняется только после поступления с пульта 17 ввода данных (с Вых. 2) сигнала «Пуск, который поступает на Вх. 1 микропроцессора 41 и производит запуск программы начального ,пуска по ус- тановленному в микропроцессоре начальному адресу для первого блока 50 памяти. Программа начального пуска обеспечивает установку всех регистров и счетчиков в ис0

5

0

между собой по проводной схеме ИЛИ общей щиной «Адрес-Данные. К входам элемента 90 подсоединены выходы блоков 84 и 85, i выходов элемента 90 и первый вход блока 18 подсоединены к разрядным входам регистра 88, выходы которого являются группой выходов прерываний (Вых.Пр) блока, поступающие на группу входов прерываний генератора 16, а первый выход соединен к входу прерываний диспетчера 1. Генератор 16 (фиг. 8) содержит микропроцессор 71, блок 73, блоки 74-78, блок 79 обмена, двунаправленный регистр 80 и блок 81 сравнения, соединенные между собой через проводную схему ИЛИ общей шиной «Адрес- Данные, причем входы прерывания генератора 16 тестов подключены к разрядным входам регистра 72 прерываний, вторые входы-выходы подключены к входам-выходам последовательного канала блока 79 обмена. Входы-выходы кодов стандартных тестов подключены к входам-выхода.м двунаправленного регистра 80. Блок 12 обмена содержит первый 52 и второй 53 регистры с управляемым направлением обмена, передающий 54 и приемный 55 регистры (все

5 регистры имеют интерфейс «ОБЩАЯ ШИНА Адрес-Данные), первый блок 56 памяти и

дами блока 12 обмена, соединенными с измерителями 5,6,11 и генераторами 8,9 по первой группе входов-выходов шины данных, по второму входу-выходу сопровождения данных, управляющим выходам - с со

ляющим входом ходами (у Вых.)

с соответствующими выответствующими входами ЭУ Вх.), управ-

ответствующими входами ЭУ Вх.), управ-

Работа тестера контроля и диагностики электронных модулей заключена в следующем.

В тестере предусмотрена возможность контроля модуля с произвольным типом интерфейса (вход-выход 21) и отдельно для упрощения программы предусмотрен входвыход 22 для модулей с базовым интерфейсом. Тип модуля задается на пульте 17 ввода данных путем ввода данных с помощью клавиатуры, которые с первого выхода пульта ввода данных в виде кода поступают в регистр диспетчера 1. Программный опрос

регистра 49 выполняется только после поступления с пульта 17 ввода данных (с Вых. 2) сигнала «Пуск, который поступает на Вх. 1 микропроцессора 41 и производит запуск программы начального ,пуска по ус- тановленному в микропроцессоре начальному адресу для первого блока 50 памяти. Программа начального пуска обеспечивает установку всех регистров и счетчиков в исходкое состояние, кроме регистра 49, очистку всех ОЗУ, приведение коммутатора 7 в исходное состояние, при котором разомкнуты все контакты второго блока 27 и ключи блока 26 коммутатора 7, что обеспечивается подачей сигнала «Сброс, поступающего на вход «Сброс (Вх.С) блока 10 памяти коммутатора и соответственно на элементы памяти - первые сдвигающие регистры 33.1 - 33.к, и второй сдвигаюихий регистр 38 от диспетчера 1 с регистра 45, также подачей нулевого кода с регистра 46. По первому двоичному разряду заданного кода определяется место подключения контролируемого модуля (вход-выход 21 или 22), о чем выводится сообщение на индикатор 3 через «Выход В диспетчера 1, формируемое с помощью адаптера 47, в кодах стандартных сообщений, хранимых в блоке 51 памяти, поступающие через внутреннюю щину «Адрес-Данные (ОШ).

Подключенный согласно сообщению контролируемый модуль (на вход-выход 21-или 22) проверяется прежде всего на отсутствие коротких замыканий, при наличии которых в любой из линий щины Ml с Вых.1 шинного формирователя 19 поступает сигнал с низким уровнем на Вх.1 блока 18 сравнения регистра 88 генерации прерываний. , обобщенный сигнал прерываний, с которого через Вых.Пр блока 18 сравнения поступает через Вх. Пр диспетчера 1 на Вх. Пр микропроцессора 41, что фиксируется программной обработкой прерываний микропроцессора 41 и отображается в виде сообщения на индикаторе 3 без диагностики номера контакта входа-выхода 22.

При контроле модуля на входе-выходе 21 (ведется контроль входных сопротивлений относительно общего провода) данные пользователя для конкретных модулей предварительно вводятся в запоминающий блок 2 в форме функциональных матриц (формализованные таблицы базы данных модуля). В процессе выполнения программы блока 50 памяти производится загрузка блока 44 памяти отображения через общую щину (ОШ)-Адрес-Данные диспетчера 1 и генерация сигнала «Пуск для блока 18 сравнения с выхода П2 диспетчера 1, при этом наличие « в соответствующем разряде обеспечивает генерацию высокого уровня напряжения при выполнении преобразования параллельного кода, хранящегося в блоке 44 памяти отображения, в последовательный с помощью генератора 15 последовательного кода, с выхода которого последовательный код поступает на вход ПК блока 10 памяти коммутатора. Последовательный код поступает в блоке 10 памяти коммутатора на первые входы элементов И 34.1-34.К, на вторые входы которых поступают сигналы выборки регистров 33.1 -

последовательного кода при поступлении от блока 18 сравнения с Вых. 2 управляющих кодов, обуславливающих коэффициент деления с генератора 43. Совместно с заполнением блока 44 памяти отображения

производится выборка данных для заполнения блока 84 памяти матрицы выходных данных модуля с границами допусков по каждому контакту контролируемого модуля на входе-выходе 21. Данные записываются в форме инвертированных таблиц и выбираются в буфер элемента 90 сравнения одновременно с последовательным подключением контактов контролируемого модуля на вход-выход 21 через коммутатор 7 (одну из горизонтальных щин второй группы) к

0 входу измерителя 11 сопротивлений и напряжений. Замеренные данные через выход ШД измерителя 11 сопротивлений и напряжений поступают на первую группу входов-выходов блока 12 обмена, содержащего управляемые измерители, где через первый регистр 52 обеспечивается преобразование и ввод данных на общую щину, с третьих входов-выходов блока 12 обмена сигналы поступают на первый вход-выход генератора 16 тестов, преобразуются в последова0 тельный код в блоке 79 обмена и далее в форме последовательного кода через вторые входы-выходы генератора 16 тестов - на вторые выходы блока 18 сравнения. Под управлением микропроцессора 82 данные вводятся во второй буфер элемента 90 срав5 нения. Если замеренные данные выходят за пределы допусков, то с выхода элемента 90 сравнения на вход регистра 88 генерации прерываний поступает по щинам код, обуславливающий выдачу сигнала прерывания

Q С первого выхода элемента 90 сравнения, который поступает на вход прерываний Вх. Пр диспетчера 1. Микропроцессор 41 переходит на программу обработки прерываний по выявленной неисправности; из блока 51 памяти поступают на первый.47 и второй

5 4В адаптеры коды для отображений и печати стандартной части, а из блока 44 памяти отображения данные по номеру контакта контролируемого модуля, из блока 85 памяти через общие щины «Адрес-Данные поступает код замеренного параметра и далее через адаптеры 47 и 48 - на печатающий блок 4 и индикатор 3. При отсутствии отклонений от заданных границ измеряемого параметра сопротивления «Контакт - Общий провод проводится даль5 нейший последовательно-сканирующий замер данных до заверщения программы. По заверщению замера сопротивлений на индикаторе 3 высвечивается сообщение «Включить питание модуля, а микропроцессоры 41, 71 и 82 переходят в режим «Ожидание, Подача питания на контролируемые модули производится оператором. Сигналы о подаче питания поступают через вход 25 устройства на диспетчер 1, генератор 16 тестов и блок 18 сравнения. В генераторе 16 тестов через регистр 72 прерывания сигнал прерывания поступает на вход прерывания микропроцессора 71, а в блоке 18 сравнения сигнал поступает непосредственно на вход прерывания микропроцессора 82, в диспетчере 1 сигнал о подаче питания поступает на вход микропроцессора 41 «Продолжение программы Вх. ПП. Первым параметром замера для всех модулей является величина «Обилий ток в цепи общего провода, замер которого выполняется на измерительном регистре 20, падение напряжения вводится в виде аналогового сигнала на третий вход блока 14 контроля сигналов произвольной формы, который поступает на вход одного из каналов аналого- цифрового преобразователя 65, преобразуется в код, поступающий на один из регистров 66.1-66.к. Данные по программе блока 69 памяти обработки преобразований выводятся через входы-выходы блока 14 контроля сигналов произвольной формы по общей шине на генератор 16 тестов и далее - в блок 18 сравнения, далее попадают в блок 85 памяти. В блоке 18 сравнения сравнение измеренных данных и допусков выполняется под управлением микропроцессора 41. При отклонении от допусков дальнейшая проверка контролируемого модуля останавливается, выдается диагностика «Питание неисправно. Ток потребления 1об ...- При соответствии допусковых требований по потреблению тока производится тестовый контроль модуля. В зависимости от типа модуля тестовая проверка и синтез теста выполняются следующим образом. Из запоминающего блока 2 выводятся согласно номеру контролируемого модуля данные в виде матрицы и попадают в блок 18 сравнения и в генератор 16 тестов в четвертый блок 76 памяти, содержащий таблицы исходных данных. Анализ данных в генераторе 16 тестов производится по иерархическому принципу: определяется тип входных сигналов и входной последовательности из- множества «Стандартные тесты, «Комбинация стандартных последовательностей, «Последовательности, формируемые управляемыми генераторами. Каждому стандартному тесту присвоена кодовая комбинация, хранящаяся во втором блоке 74 памяти. При совпадении кодовых комбинаций параллельно формируется матрица контактного поля для коммутатора 7 в блоке 44 памяти отображения. Анализ совпадения выполняется для входных данных в блоке

81 сравнения. Если данные контролируемого модуля таковы, что необходимо инициировать две или более стандартные последовательности одновременно или последовательно, то набор констант из третьего блока 75 памяти поступает в определенные ячейки ОЗУ, подключая тем самым соответствующие ветки программ третьего блока 75 памяти. Стандартные последовательности формируются программами и поступают на выходные каналы двунаправленного регистра 80 и далее - на соответствующие входы коммутатора 7.

- Если входную последовательность невозможно сформировать из стандартных наборов, то по выданному признаку в блоке 81 .сравнения начинает производиться анализ по каталогу шестого блока 78 памяти, управление передается блоку 12 об0 мена, сигналы поступают через третьи входы-выходы; первый блок 56 памяти начинает выполнять программу протоколов обмена в зависимости от данных, поступивших в определенные ячейки третьего блока

5 58 памяти, которые определяют тип инициированного генератора, режим циклов и параметры отдельного импульса, синусоиды, - пилы и т.п. Если с блока 81 сравнения поступает сигнал о невозможности получения нужной формы кривой периодического или

0 непериодического сигнала или в составе входных данных, поступающих от запоминающего блока 2, содержится признак необходимости генерации сигнала, относящегося к типу «Произвольная форма (например, ступенчатое напряжение с плоской или

пилообразной закономерностью изменения, псевдослучайные скачки напряжений и т.п.), то управление передается блоку 13 генерации сигналов произвольной формы, при этом в выделенные ячейки второго блока 64 па0 мяти записываются одновременно константы, определяющие длительность экспонирования для таймеров 62.1-62.к, адрес запуска программ в первый блок 63 памяти для ввода кодов преобразования в регистры 61.1-61.к. Для получения сигнала, представляющего собой сумму разных каналов цифроаналогового преобразователя 60 данные поступают через элемент ИЛИ 59 на первый выход, группа сигналов второго выхода представляет собой локальные вы0 ходы каналов. Момент выдачи сигналов с блока 13 генерации сигналов произвольной формы определяется поступлением сигнала низкого уровня (разрешение) с выхода диспетчера 1. Одновременно вводится в действие микропроцессор 82 блока 18 сравне ния и в блоке 44 памяти отображения формируются ячейки, обуславливающие замыкание цепей коммутатора 7 для контроля выходных данных проверяемого модуля

5

11

для чего выполняется анализ выходных данных, засылаемых из запоминающего блока 2 зоны выходных данных параметров модуля в блок 84 памяти. Производится последовательный опрос данных, выявляющих требуемые средства контроля выходных параметров из числа возможных: контроль средствами генератора 16 тестов по сигналам, поступающим на входы-выходы двунаправленного регистра 80, контроль с помощью измерителя 5 дискретных сигналов (например, С9-8) или измерителя 6 аналоговых сигналов, сигналы произвольной формы контролируются блоком 14 контроля сигналов произвольной формы, в котором сигналы поступают от различных цепей на группу первых входов, на аналого-цифровой преобразователь 65, - на выходные каналы которого поступают коды на регистры 66.1-66.к. Момент регистрации кода выполняется по сигналу таймера 67, прав- ляемого через общую щи ну «Адрес«Дан- ные, на второй вход которого поступают управляемые по частоте импульсы с выхода ТИ диспетчера 1. В счетчике 68 каналов происходит учет номера канала для управления адресацией записи данных в блок 70 памяти.

Формула изобретения

. Тестер контроля и диагностики электронных модулей, содержащий запоминающий блок, индикатор, измеритель дискретных сигналов, печатающий блок, коммутатор, блок сравнения, генератор дискретных сигналов, пульт ввода данных, диспетчер, щинный формирователь, выход которого соединен с входом блока сравнения, первый выход которого соединен с входом прерывания диспетчера, первая группа входов- выходов коммутатора соединена с первым входом-выходом устройства, первый выход пульта ввода данных соединен с входом ввода данных диспетчера, а второй выход соединен с входом «Пуск диспетчера, выход индикации которого соединен с входом индикатора, а выход печати - с входом печатающего блока, запоминающий блок соединен входами-выходами с входами-выходами диспетчера, отличающийся тем, что, с целью расщирения области применения и функциональных возможностей за счет возможности контроля различных типов модулей, а также повыщения производительности за счет сокращения сроков разработки испытательных программ в него введены измеритель аналоговых сигналов, блок памяти коммутатора, измеритель сопротивлений и напряжений, блок обмена, блок генерации сигналов произвольной формы, блок контроля сигналов произвольной формы, генератор последовательного кода, гейера- тор тестов, измерительный резистор, гене12

5

ратор аналоговых сигналов, причем входы- выходы общей щины генератора тестов, щин- ного формирователя, блока генерации сигналов произвольной формы, блока контроля сигналов произвольной формы и блока обмена соединены между собой, вход управления тактовой частотой диспетчера соединен с вторым выходом блока сравнения, входы прерывания по питанию диспетчера,

Q генератора тестов и блока сравнения соединены с первым входом устройства, выход тактовых импульсов диспетчера соединен с входами тактовых импульсов генератора последовательного кода, блока памяти ком- мутора, блока генерации сигналов произ5 вольной формы и блока контроля сигналов произвольной формы, выход управления - с входом управления блока памяти коммутатора, выход сброса - с входом сброса блока памяти коммутатора, выход стробирова0 ния - с первым входом блока генерации сигналов произвольной формы, выход записи, кодовый выход и информационные выходы соединены с входами записи, кодовыми входами и информационными входами блока памяти коммутатора соответственно, выход «Пуск 1 диспетчера соединен с входом «Пуск 1 генератора тестов, выход «Пуск 2 - с входом пуска блока сравнения, выход управления диспетчера - с входом щинного формирователя, а вход-вы0 ход - с в ходом-выходом генератора последовательного кода и первым входом-выходом блока сравнения, второй вход-выход которого соединен с первым входом-выходом генератора тестов, вход прерывания которого соединен с выходом прерывания бло5 ка сравнения, выход генератора последовательного кода соединен с входами последовательного кода блока памяти коммутатора и коммутатора, выход кода которого соединен с входом генератора последовательQ ного кода, вторая группа входов-выходов коммутатора соединена с соответствующей группой входов-выходов генератора тестов., первая и вторая группа входов - с первой и второй группой выходов блока памяти коммутатора соответственно, первый, вто5 рой, третий и четвертый выходы - с входами измерителя дискретных сигналов, измерителя аналоговых сигналов, блока контроля сигналов произвольной формы и измерителя сопротивлений и напряжений, первый, второй, третий и четвертый входы коммутатора соединены соответственно с первым и вторым выходами блока генерации сигналов произвольной формы, выходами генератора дискретных сигналов и генератора аналоговых сигналов, третий вход бло5 ка контроля сигналов произвольной формы соединен с общей шиной модуля и через измерительный резистор с общей щиной источника, вход блока обмена соединен с

13

управляющими выходами измерителя дискретных сигналов, измерителя аналоговых сигналов, генератора аналоговых сигналов и измерителя сопротивлений и напряжений, управляющий вход которых соединен с выходом блока обмена, а управляющие входы-выходы и входы-выходы данных соединены с первыми и вторыми входами-выходами блока обмена соответственно, а информационный вход-выход шинного формирователя соединен с вторым входом-выходом устройства.

14

управляюгцим входом блока, а вторые - соответственно с входом ввода последовательного кода блока и входом тактовых импульсов блока.

приемный регистр, первый, второй и третий блоки памяти, соединенные с первым входом-выходом блока, вход-выход первого регистра соединен с вторым входом-выходом блока, вход-выход второго регистра - с третьим входом-выходом блока, выход передающего регистра - с выходом блока, а вход приемного регистра - с входом блока.

разователя соединены с выходом блока и входами элемента ИЛИ, выход которого соединен с вторым выходом блока, первый вход которого соединен с входом стробиро- вания цифроаналогового преобразователя,

второй вход управляемых тактовых импульсов - с входами таймеров, а вход-выход блока - с входами-выходами первого и второго блоков памяти.

выходом «Адрес-Данные блока и вхоДЬм- выходом таймера, вход-выход блока соединен с входами-выходами первого и второго блоков памяти, выход таймера соединен с вторыми входами регистров и через счетчик каналов - с входом второго блока памяти, вход управляемых тактовых импульсов контроля блока - с входом таймера, а первый и второй входы блока соединены соответственно с первым и вторым входами аналого-цифрового преобразователя.

16

го регистра, вход питания модулей генератора соединен с входом регистра прерываний, первый, второй, третий и четвертый входы блока сравнения соединены соответственно с выходами второго, четвертого, пятого и шестого блоков памяти.

четвертый блоки памяти, соединенные входами-выходами с входом-выходом «Адрес- Данные блока, причем первый и второй входы элемента сравнения соединены с выходами первого и второго блоков памяти, выходы элемента сравнения и первый вход

блока соединены с первым и вторым входами регистра генерации прерываний соответственно, первые выходы регистра генерации прерываний соединены с выходами прерываний блока, вторые выходы - с первым выходом блока, выход регистра соединен с вторым выходом блока, вход «Пуск - с первым входом микропроцессора, второй вход которого соеди 1ен с входом питания модулей блока, а вход-выход тестов блока обмена - с первым входом-выходом блока.

Л маЗу/ть

фиг 2

Ma ynflagjrSHue нонтантной сгсгт.ю /юммутагпу о 7

ffp ynfloS fHaf SecHOf/rrrcfffmHoij vac/nbta OfVMyn-fcfmopcr 7 фиг. 3

O/rr S/7. numcffJifJ

f/a ex. 13,n/J flfoffy/7eu

/fa SffffH t9

УигЛ

S. Cflc/S. fS

fly с ft fffn ni/.m fTrcf /7

I1

От диспеггт /ера 1 ffm ге е/7атор у

/пестов/6 .6

Фиг. 7

У/п S/. cpaff- f8

ffflr ffuen. yc/rrfl,f

(/T7 S ffffa

tJUfrra/ UjI модулей

C S/rofi / afrrfluv faea HO/ Mymarrra/ya 7 (jOuS. 8

От S/. /7fjma/ cjf

//a Srr. Hi/gfS

//a eef e/y/yrrrop mec/77off /S

| Устройство для контроля параметров сложных систем | 1984 |

|

SU1205084A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля цифровых печатных узлов | 1983 |

|

SU1179233A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-05-15—Публикация

1986-08-14—Подача