рийного управляется синхронизирующим сигналом, который вы- деляется из сигнала, посланного от глаяного терминала. Цель достигает1

Изобретение относится к электросвязи и может быть использовано для дуплексной передачи цифровых сигналов.

Целью изобретения является обеспечение передачи сигналов по двухпроводной линии связи.

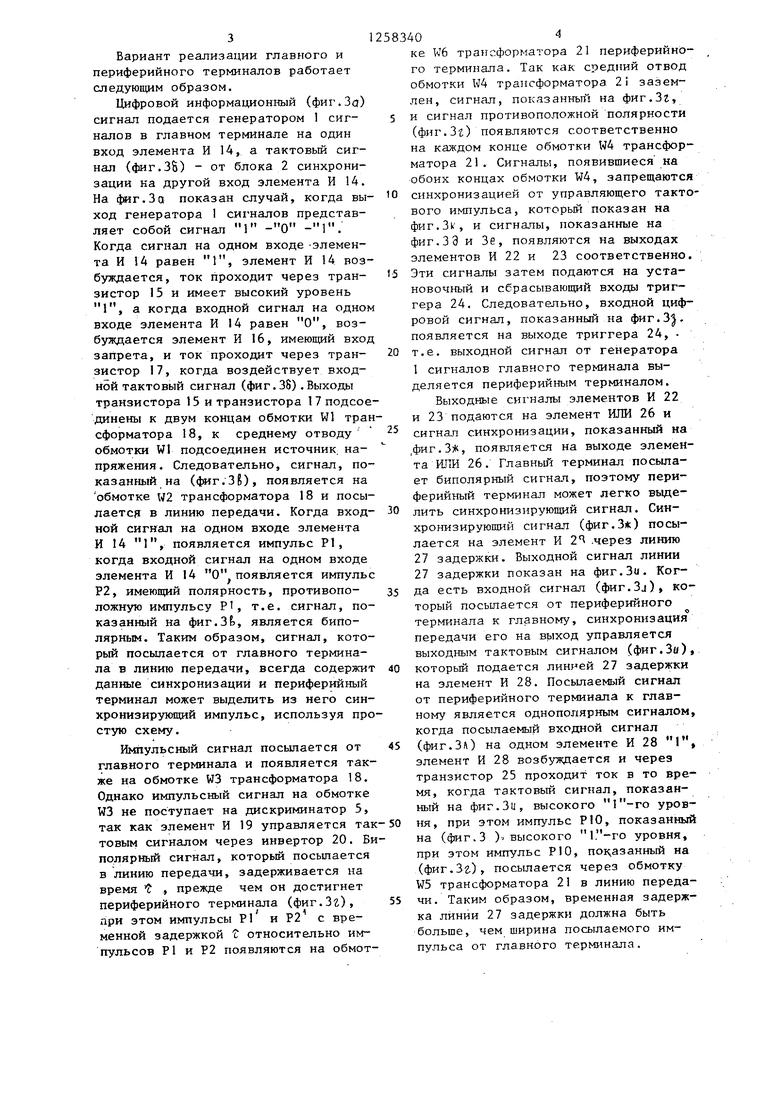

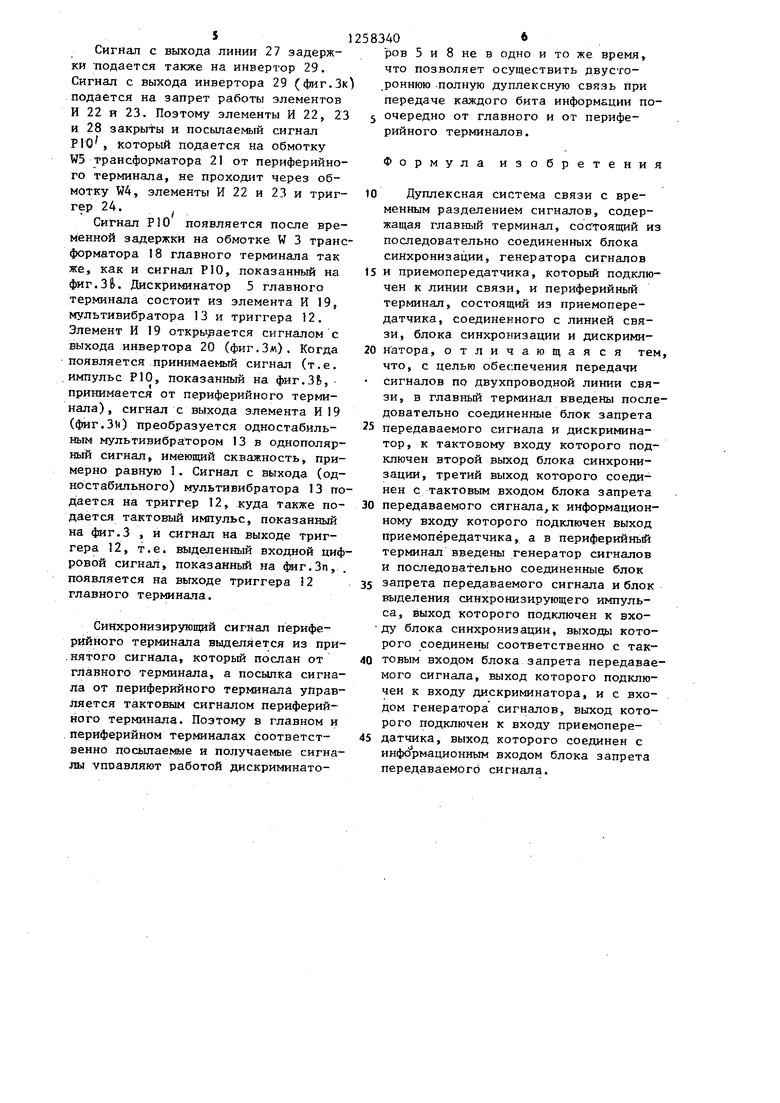

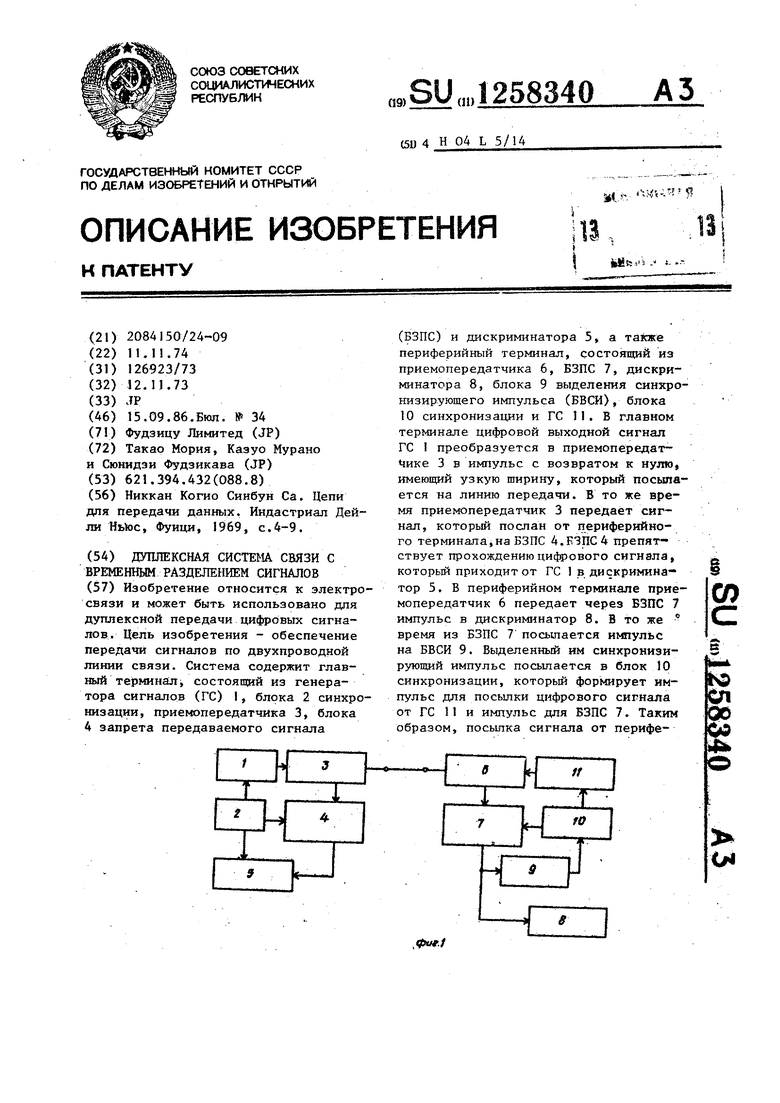

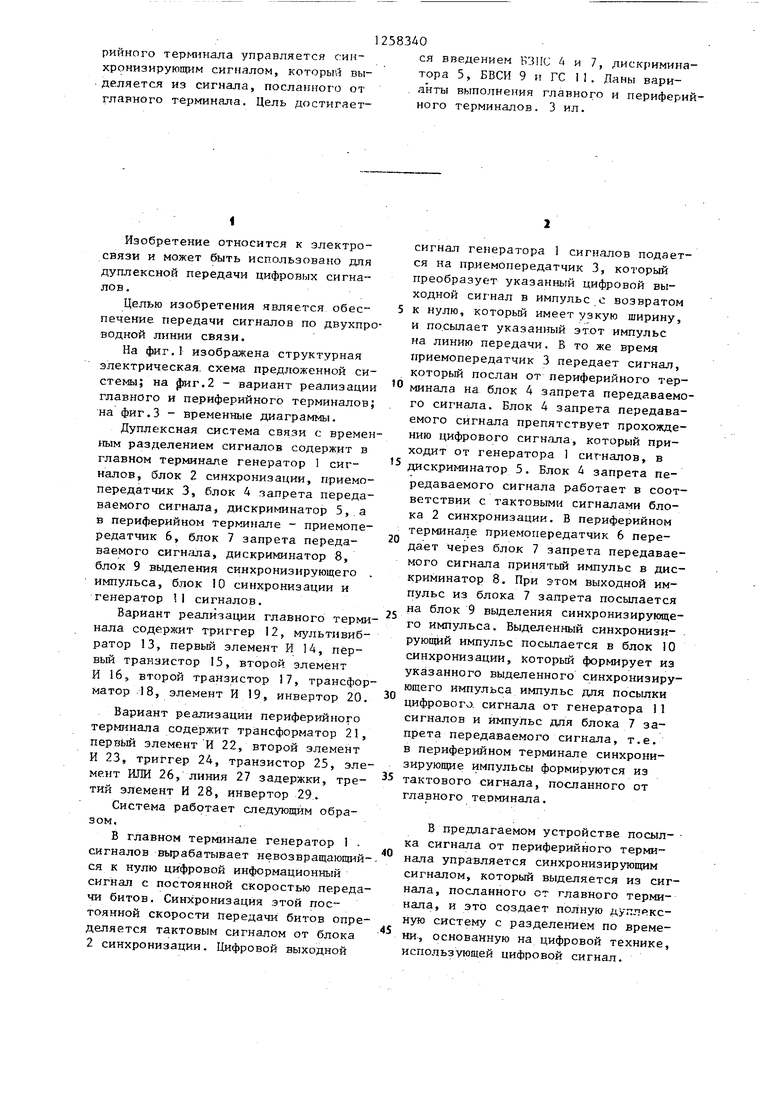

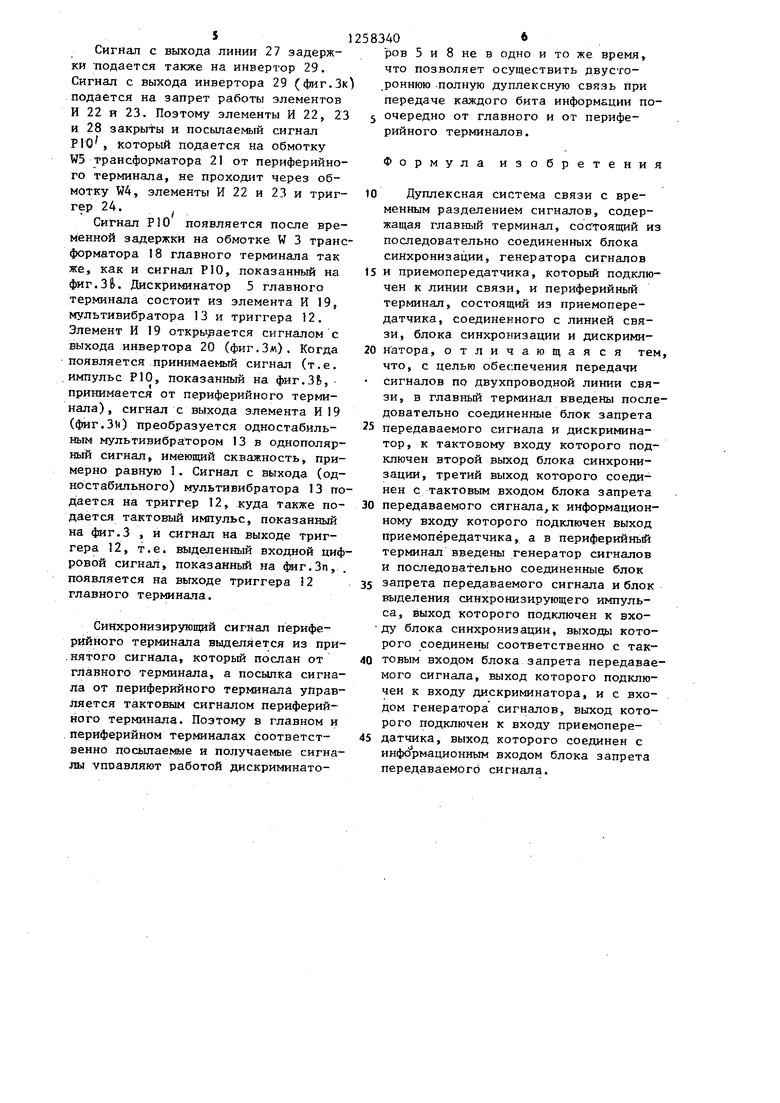

На фиг,1 изображена структурная электрическая, схема предложенной системы; на г.2 - вариант реализации главного и периферийного терминалов; на фиг.3 - временные диаграммы.

Дуплексная система связи с временным разделением сигналов содержит в главном терминале генератор 1 сигналов, блок 2 синхронизации, приемопередатчик 3, блок 4 запрета передаваемого сигнала, дискриминатор 5, а в периферийном терминале - приемопередатчик 6, блок 7 запрета передаваемого сигнала, дискриминатор 8, блок 9 выделения синхронизирующего . импульса, блок 10 синхронизации и генератор П сигналов.

Вариант реализации главного терминала содержит триггер 12, мультивибратор 13, первый элемент И 14, первый транзистор 15, второй элемент И 16, второй транзистор 17, трансформатор 18, элемент И 19, инвертор 20.

Вариант реализации периферийного термг нала содержит трансформатор 21, первьй элемент И 22, второй элемент И 23, триггер 24, транзистор 25, элемент ИЛИ 26, линия 27 задержки, третий элемент И 28, инвертор 29.

Система работает следующим образом.

В главном терминале генератор 1 - сигналов вьфабатывает невозвращающийся к нулю цифровой информационный сигнал с постоянной скоростью передачи битов. Синхронизация этой постоянной скорости передачи битов определяется тактовым сигналом от блока 2 синхронизации. Цифровой выходной

ся введением БЗИС и 7, дискриминатора 5, БВСИ 9 и ГС 11. Даны варианты выполнения главного и периферийного терминалов. 3 ил.

сигнал генератора 1 сигналов подается на приемопередатчик 3, который преобразует указанный цифровой выходной сигнал в импульс с возвратом

5 к нулю, который имеет узкую ширину, и посылает указантш этот импульс на линию передачи. В то же время приемопередатчик 3 передает сигнал, который послан от периферийного тер минала на блок 4 запрета передаваемого сигнала. Блок 4 запрета передаваемого сигнала препятствует прохождению цифрового сигнала, который приходит от генератора 1 сигналов, в

дискриминатор 5. Блок 4 запрета передаваемого сигнала работает в соответствии с тактовыми сигналами блока 2 синхронизации. В периферийном терминале приемопередатчик 6 передает через блок 7 запрета передаваемого сигнала принятый импульс в дискриминатор 8. При этом выходной импульс из блока 7 запрета посыпается на блок 9 выделения синхронизирующего импульса. Выделенный синхронизи- рующий импульс посылается в блок 10 синхронизации, который формирует из указанного выделенного синхронизирующего импульса импульс для посылки цифрового, сигнала от генератора 1 1 сигналов и импульс для блока 7 запрета передаваемого сигнала, т.е. в периферийном терминале синхронизирующие импульсы формируются из

35 тактового сигнала, посланного от главного терминала.

20

25

30

В предлагаемом устройстве посылка сигнала от периферийного терминала управляется синхронизирующим сигналом, который выделяется из сигнала, посланного от главного терминала, и это создает полную дугтлркс- ную систему с разделением по времени, основанную на цифровой технике, использующей цифровой сигнал.

3

Вариант реализации главного и периферийного терминалов работает следуюш;им образом.

Цифровой информационный (фиг.Зо) сигнал подается генератором 1 сигналов в главном терминале на один вход элемента И 14, а тактовый сигнал (фиг.Зб) - от блока 2 синхронизации на другой вход элемента И 14. На .3а показан случай, когда выход генератора 1 сигналов представляет собой сигнал 1 . Когда сигнал на одном входе -элемента И 14 равен 1, элемент И 14 воз- буткдается, ток проходит через транзистор 15 и имеет высокий уровень 1, а когда входной сигнал на одном входе элемента И 14 равен О, возбуждается элемент И 16, имеющий вход запрета, и ток проходит через транзистор 17, когда воздействует входной тактовый сигнал (фиг.38) .Выходы транзистора 15 и транзистора 1 7 подсоединены к двум концам обмотки W1 трансформатора 18, к среднему отводу обмотки WI подсоединен источник напряжения. Следовательно, сигнал, показанный на ((1иг.38), появляется на обмотке W2 трансформатора 18 и посылается в линию передачи. Когда входной сигнал на одном входе элемента И 14 1, появляется импульс Р1, когда входной сигнал на одном входе элемента И 14 0 появляется импульс Р2, имеющий полярность, противоположную импульсу Pt, т.е. сигнал, показанный на фиг.ЗЬ, является биполярным. Таким образом, сигнал, который посьшается от главного терминала в линию передачи, всегда содержит данные синхронизации и периферийный терминал может выделить из него синхронизирующий импульс, используя простую схему.

Импульсный сигнал посьшается от главного терминала и появляется также на обмотке W3 трансформатора 18. Однако импульсный сигнал на обмотке W3 не поступает на дискриминатор 5, так как элемент И 19 управляется тактовым сигналом через инвертор 20. Би полярньвй сигнал, который посыпается в линию передачи, задерживается на время , прежде чем он достигнет периферийного терминала (фиг.З,), при этом импульсы Р1 и Р2 с временной задержкой t относительно импульсов Р1 и Р2 появляются на обмот583404

ке W6 трансформатора 21 периферийного терминала. Так как средний отвод обмотки W4 трансформатора 21 заземлен, сигнал, показанный на фиг.Зг, 5 и сигнал противоположной полярности (фиг.Зг) появляются соответственно на каждом конце обмотки W4 трансформатора 21. Сигналы, появившиеся на обоих концах обмотки W4, запрещаются

10 синхронизацией от управляющего тактового импульса, который показан на фиг.Зг, и сигналы, показанные на фиг.33 и Зе, появляются на выходах элементов И 22 и 23 соответственно.

15 Эти сигналы затем подаются на установочный и сбрасывающий входы триггера 24. Следовательно, входной цифровой сигнал, показанный на фиг.З. появляется на выходе триггера 24,

20 т.е. выходной сигнал от генератора 1 сигналов главного терминала выделяется периферийным терминалом.

Выходные сигналы элементов И 22 и 23 подаются на элемент ИЛИ 26 и

сигнал синхронизации, показанный на ,фиг.3)(4, появляется на выходе элемента ИЛИ 26. Главньш терминал посылает биполярный сигнал, поэтому периферийный терминал может легко выде30 лить синхронизирующий сигнал. Синхронизирующий сигнал (фиг.З) посылается на элемент И 2 .через линию 27 задержки. Выходной сигнал линии 27 задержки показан на фиг.Зи. Ког5 да есть входной сигнал (фиг.ЗJ), который посылается от периферийного терминала к главному, синхронизация передачи его на выход управляется выходным тактовым сигналом (фиг.Зо),

0 который подается лишней 27 задержки на элемент И 28. Посыпаемый сигнал от периферийного терминала к главному является однополярным сигналом, когда посылаемый входной сигнал

5 (фиг.ЗА) на одном элементе И 28 1, элемент И 28 возбуждается и через транзистор 25 проходит ток в то время, когда тактовый сигнал, показанный на фиг.Зи, высокого Г -го уров0 ня, при этом импульс Р10, показанный на (фиг.З ) высокого 1.-го уровня, при этом импульс Р10, показанный на (фиг.Зг), посылается через обмотку W5 трансформатора 21 в линию переда5 чи. Таким образом, временная задержка линии 27 задержки должна быть больше, чем ширина посылаемого импульса от главного терминала.

Сигнал с выхода линии 27 задержи подается также на инвертор 29. игнал с выхода инвертора 29 (фиг.Зк) подается на запрет работы элементов 22 и 23. Поэтому элементы И 22, 23 и 28 закрыты и посыпаемый сигнал 10, который подается на обмотку 5 трансформатора 21 от периферийного терминала, не проходит через оботку W4, элементы И 22 и 23 и триггер 24.

Сигнал Р10 появляется после временной задержки на обмотке W 3 трансформатора 18 главного термииала так е, как и сигнал Р10, показанный на фиг.36. Дискриминатор 5 главного терминала состоит из элемента И 19, мультивибратора 13 и триггера 12. Элемент И 19 открывается сигналом с выхода инвертора 20 (фиг.3м). Когда появляется принимаемый сигнал (т.е. импульс Р10, показанный на фиг.ЗЬ,- принимается от периферийного терминала), сигнал с выхода элемента И 19 (фиг.ЗМ) преобразуется одностабиль- ным мультивибратором 13 в однополяр- ный сигнал имеющий скважность, примерно равную 1. Сигнал с выхода (од- ностабильного) мультивибратора 13 подается на триггер 12, куда также подается тактовый импульс, показанный на фиг.З , и сигнал на выходе триггера 12, т.е. выделенный входной цифровой сигнал, показанный на г.Зп, . появляется па выходе триггера 12 главного терминала.

Синхронизирующий сигнал периферийного терминала выделяется из при- .пятого сигнала, который послан от главного терминала, а посылка сигнала от периферийного терминала управляется тактовым сигналом периферийного терминала. Поэтому в главном и периферийном терминалах соответственно посылаемые и получаемые сигналы упоавляют работой дискриминато)

1258340

ров 5 и 8 не в одно и то же время, что позволяет осуществить двустороннюю .полную дуплексную связь при передаче каждого бита информации по- 5 очередно от главного и от периферийного терминалов.

Формула изобретения

10 Дуплексная система связи с временным разделением сигналов, содержащая главный терминал, сос тоящий из последовательно соединенных блока синхронизации, генератора сигналов

15 и приемопередатчика, который подключен к линии связи, и периферийный терминал, состоящий из приемопередатчика, соединенного с линией связи, блока синхронизации и дискрими20 натора, отличающаяся тем что, с целью обеспечения передачи сигналов по двухпроводной линии связи, в главньй терминал введены последовательно соединенные блок запрета

25 передаваемого сигнала и дискриминатор, к тактовому входу которого подключен второй выход блока синхронизации, третий выход которого соединен с тактовым входом блока запрета

30 передаваемого сигнала,к информационному входу которого подключен выход приемопередатчика, а в периферийньй терминал введены генератор сигналов и последовательно соединенные блок

35 запрета передаваемого сигнала и блок выделения синхронизирующего импульса, выход которого подключен к вхо- ду блока синхронизации, выходы которого соединены соответственно с так40 товым входом блока запрета передаваемого сигнала, выход которого подключен к входу дискриминатора, и с входом генератора сигналов, выход которого подключен к входу приемопере45 датчика, выход которого соединен с информационным входом блока запрета передаваемого сигнала.

74 fS

4W

1в 3 я

.8

20

н

22

F

г4

26

23

v

2

7

| название | год | авторы | номер документа |

|---|---|---|---|

| Система связи с временным разделением сигналов | 1988 |

|

SU1669081A1 |

| Дуплексная система передачи данных с временным разделением сигналов | 1990 |

|

SU1782336A3 |

| Система синхронизации цифровой сети связи | 1984 |

|

SU1582995A3 |

| ОПРЕДЕЛЕНИЕ СДВИГОВ ЧАСТОТЫ В СИСТЕМАХ СВЯЗИ | 1997 |

|

RU2195772C2 |

| СИСТЕМА ДЛЯ ИНФОРМАЦИОННОГО ОБМЕНА С ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2003 |

|

RU2264655C2 |

| Устройство для управления тиристорным преобразователем | 1975 |

|

SU549873A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| СПОСОБ (ВАРИАНТЫ) И СИСТЕМА ДЛЯ ОПРЕДЕЛЕНИЯ ПОЛОЖЕНИЯ ОБЪЕКТА | 1990 |

|

RU2084916C1 |

| УЛУЧШЕНИЕ ДЛЯ СПОСОБОВ СИНХРОНИЗАЦИИ ДЛЯ СЕТЕЙ МОБИЛЬНОЙ РАДИОСВЯЗИ С ОДНОВРЕМЕННЫМ ОДНОЧАСТОТНЫМ ВЕЩАНИЕМ | 2008 |

|

RU2461134C2 |

| Устройство для управления электропотреблением предприятия | 1984 |

|

SU1246246A1 |

Изобретение относится к электросвязи и может быть использовано для дуплексной передачи цифровых сигналов. Цель изобретения - обеспечение передачи сигналов по двухпроводной линии связи. Система содержит главный терминал, состоящий из генератора сигналов (ГС) I, блока 2 синхронизации, приемопередатчика 3, блока 4 запрета передаваемого сигнала (БЗПС) и дискриминатора 5, а также периферийный терминал, состоящий из приемопередатчика 6, БЗПС 7, дискриминатора 8, блока 9 выделения синхронизирующего импульса (ЕВСИ), блока 10 синхронизации и ГС 11. В главном терминале цифровой выходной сигнал ГС 1 преобразуется в приемопередат- 1ике 3 в импульс с возвратом к нулю, имеющий узкую ширину, который посыпается на линию передачи. В то же время приемопередатчик 3 передает сиг нал, который послан от периферийного терминала,на БЗПС 4.КЗПС 4 препятствует прохождению цифрового сигнала, который приходит от ГС 1 в дискриминатор 5. В периферийном терминале приемопередатчик 6 передает через ВЗПС 7 импульс в дискриминатор 8. В то же время из БЗПС 7 посьтается импульс на БВСИ 9. Выделенный им синхронизи- РЗгющий импульс посылается в блок 10 синхронизации, который формирует импульс для посылки цифрового сигнала от ГС 11 и импульс для БЗПС 7. Таким образом, посьшка сигнала от перифе СМ

12

13

tf

фие.2

./

г

./y

n.

JT

S

cptts.d

Составитель Б.Носов Редактор М.Недолуженко Техред Л.Сердюкова Корректор А.Тяско

Заказ 5046/61 Тираж 624 Подписное ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

r/

n

Г1

,pfff

Jl

n.

LJ

| Никкан Когио Синбун Са | |||

| Цепи для передачи данных | |||

| Индастриал Дей- ли Hbtoc, Фуици, 1969, с.4-9. |

Авторы

Даты

1986-09-15—Публикация

1974-11-11—Подача