10

25

Изобретение относится к средствам неразрушающег о контроля материалов и изделий и может быть использовано для дефектоскопии и дефектометрии металлов в любой отрасли npoNftiianea- ности.

Цель изобретения повышение точности контроля за счет отстройки от влияния несовершенства изготовления катушек преобразователя и от влияния на результат электрофизических параметров изделия. ,

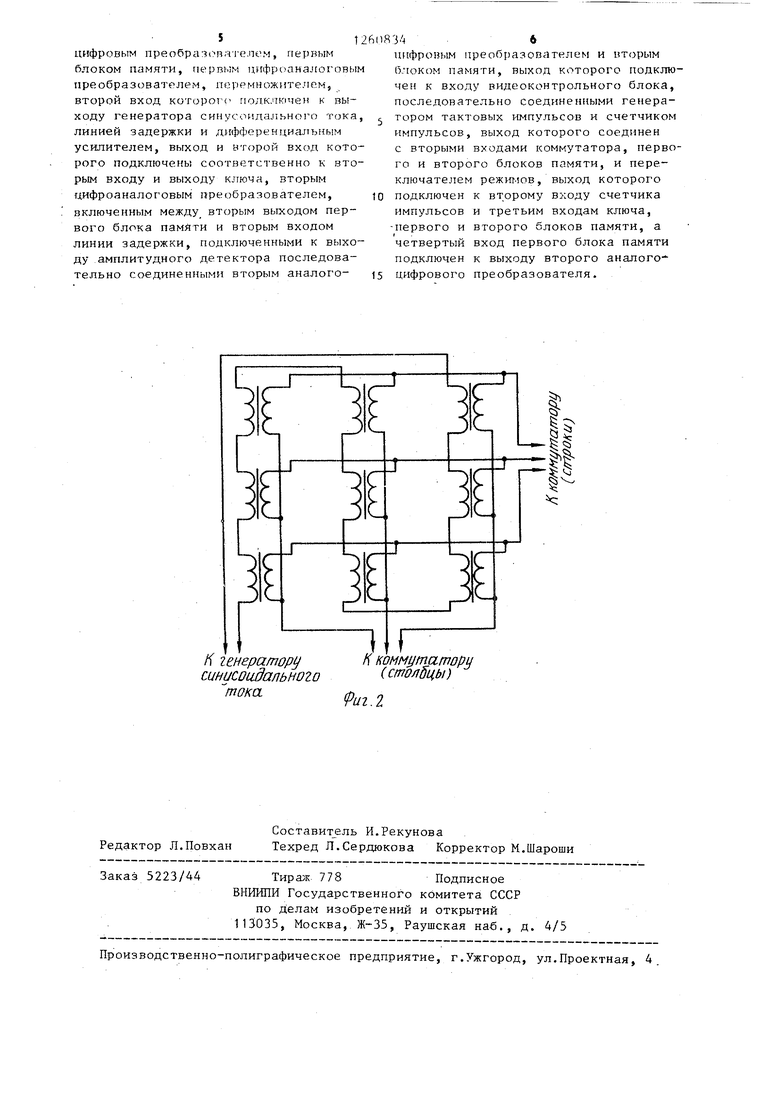

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 - конструкция матричного преобразователя. I

Устройство содержит последователь но соединенные генератор 1 синусо- идального тока, вихретоковый матрич- ный преобразователь 2, коммутатор 3, ключ 4, усилитель 5, амплитудный детектор 6, второй аналогоцифровой преобразователь (АЦП) 7, последовательно соединенные перемножитель 8, вторым входом соединенный с генератором 1, линию 9 задержки, управляемую напряжением, дифферендиальный усилитель 10, подключенный выходом к второму входу ключа 4, а вторым Входом - к второму выходу ключа 4, последовательно соединенные фазометр 11, подключенный первым входом к выходу генератора 1, а вторым входом - к первому выходу коммутатора 3, первый АЦП 12, а также первый дифро- аналоговый преобразователь (ЦАП) 13, подключенный выходом к второму входу перемножителя 8, второй ЦАП 14, подключенный выходом к второму управляющему входу линии 9 задержки, последовательно соединенные генератор 15 импульсов и счетчик 16 импульсов, подключенный выходом к второму (управляющему) входу коммутатора, переключатель 17 режимов, подключенный к третьему (управляющему) входу ключа 4 и второму (управляющему) входу счетчика 16 импульсов, первый блок 18 памяти, подключенньш первым (информадионным) входом к выходу пер- 50 зого аналого-дифрового преобразователя 12, вторым (информационным) входом - к выходу второго АЦП 7, третьим (адресным) входом - к выходу счетчика 16 импульсов, четвертым (управляющим) входом - к переключателю 17 режимов, первым (информадионным) выходом - к входу первого

15

20

35

55

30

40

45

5

0

ЦАП 13, вторым (информационным) выходом - к входу второго иди 14, второй блок 19 памяти, подключенный вторым (адресным) входом к выходу счетчика 16 импульсов, третьим (управляющим) входом - к переключателю 17 режимов, первым (информационным) входом - к выходу второго АЦП 7, видеоконтрольный блок (ВКБ) 20, подключенный к выходу второго блока 19 памяти.

Матричный преобразователь (фиг.2) выполнен в виде матрицы пхп преобразователей трансформаторного типа.

5 Возбуждающая и измерительная обмотки из п преобразователей расположены на ферритовом стержне. Возбуждающие обмотки преобразователей включены последовательно, концы

0 измерительных обмоток объединены в строки и столбцы.

Устройство работает в двух режимах: режиме компенсации и режиме измерения .

Ь режиме компенсации матричный преобразователь 2 устанавливают на бездефектный участок контролируемого изделия. Переключатель 17 режимов переводят в состояние, соответст- вз ющее режиму компенсации, при этом переключатель 17 режимов формирует сигнал, под управлением которого ключ 4 замыкает первый вход с первым выходом, счетчик 16 обнуляется, пер5 вый блок 18 памяти работает в режиме записи информации с первого и второго АЦП 7 и 12. Под управлением счетчика 16 импульсов, на вход которого подается тактовая частота с генератора 15 импульсов, коммутатор 3 подключает строку матричного преобразователя 2 к первому входу ключа 4, а столбец - к общей шине матрицы, тем самым происходит выбор преобра- зователя. С первого выхода ключа 4 напряжение с преобразователя матрицы 2 подается на усилитель 5, ампли- - тудный детектор 6 и второй АЦП 7, где происходит преобразование аналогового сигнала в цифровой вид. В ячейке памяти блока 18 памяти про - исходит запоминание цифрового кода амплитуды сигнала, поступающего с АЦП 7, адрес которой выбирается

5 счетчиком 16 импульсов.

Одновременно напряжение с генератора 1 подается на первый вход фа- , зом етра II, на второй вход которого

0

0

5

подается напряжение с преобразова-- теля матрицы матричного преобразователя 2, на выходе фазометра 11 получаем напряжение, пропорциональное сдвигу фаз между опорным напряжением (напряжение генератора 1) и напряжением с преобразователя матрицы. АЦП 12 приводит аналоговое напряжение с выхода фазометра 11 в цифровой вид, которое запоминается в ячейке памяти блока 18 памяти. После этого, при поступлении на. вход счетчика 16 следующего тактового импульса с тактового генератора 15 коммутатор 3 выбирает другой преобразователь матрицы, а напряжения в цифровом виде, пропорциональные амплитуде и фазе сигнала с этого преобразователя, выше описанным способом запоминаются в следующей ячейке памяти блока 18 памяти. И так далее пока не снимутся и запомнятся коды фазы и амплитуды с последнего преобразователя матрицы матричного преобразователя 2. На этом режим компенсации закончен.

В режиме измерений преобразователь 2 устанавливают на контролируемый участок объекта контроля. Пере- ключатель 17 режимов переводят в состояние, соответствующее режиму измерений, при этом переключатель 1 7 режимов формирует сигнал, под управлением кото jporo ключ 4 замыкает первый вход

с вторым выходом, а второй вход - с первым выходом, счетчик 16 обнуляется, первый блок 18 памяти работает в режиме выдачи информации на первый и второй ЦАП 13 и 14, а второй блок 19 памяти - в режиме записи информации с АЦП 7. Под управлением счетчика 16 коммутатор 3 выбирает первый преобразователь матрицы, напряжение с которого подается через ключ 4 на второй вход дифференциального усилителя 10.

Из ячейки памяти блока 18 памяти, соответствующей первому преобразователю матричного преобразователя 2, извлекаются коды амплитуды и фазы компенсирующего напряжения и подаются соответственно на первый и второй ЦАП 13 и 14, на выходе первого ЦАП 1 формируется напряжение, пропорциональное амплитуде компенсирующего напряжения первого преобразователя матрицы, подаваемое на первый вход перемножителя 8, на второй Вход которого подается напряжение генератора 1. На

выходе перемножителя 8 получается напряжение синусоидальной формы с амплитудой, равной амплитуде напряжения с первого преобразователя в режиме компенсации. Это напряжение подается на первый вход линии 9 задержки, на второй вход которой подано напряжение с выхода ЦАП 14, пропорциональное фазе напряжения с пер-

вого преобразователя матрицы в режиме компенсации. На выходе линии 9 задержки, управляемой напряжением, получают синусоидальное напряжение, амплитуда и фаза которого равны амплитуде и фазе напряжения с первого преобразователя матричного преобразователя 2 в режиме компенсации. Это напряжение подается на первый вход дифференциального усилителя 10. При

отсутствии дефекта под первым преобразователем на выходе диф4)еренциаль- ного усилителя 10 получают минимальное напряжение, определяемое точностью компенсации, при наличии дефекта на выходе дифференциального усилителя 10 присутствует разбаланс, который через ключ 4, усилитель 5 и детектор 6 подается на АЦП 7, где переводится в цифровой вид, после

чего запоминается в ячейке памяти блока 19 памяти, с выхода которого подается на видеоконтрольный блок 20 в виде точки яркость, пропорциональная напряжению разбаланса.

Аналогичные операции происходят при выборе всех остальных преобразователей матрицы, при этом на экра не блока 20 получают картину распределения дефектов на контролируемом

40

участке,

Формула изобретения

Устройство для вихретокового контро- ля содержащее последовательно соединенные генератор синусоидального тока, вихретоковый матричный преобразователь и коммутатор, последовательно соединенные усилитель и амплитудный детектор, и видеоконтрольный блок, отличающееся тем, что, с целью повьшения точности контроля, оно снабжено включенным между выходом коммутатора и входом усилителя ключом, последовательно соединенными фазометром, первый и второй входы которого подключены соответственно к выходам генератора синусоидального тока и коммутатора, первым аналоге5t2fti)8

цифровым преобра: оп;ч ге.пем, первым блоком памяти, «ервым цнфроаналоговым преобразователем, перемножите.пем, второй вход которогс подключен к ходу генератора синуслчидального тока, линией задержки и дифференциа тьным усилителем, выход и второй вход которого подключены соответственно к вторым входу и выходу ключа, вторым цифроаналоговым преобразователем, tO включенным между вторым выходом первого блока памяти и вторым входом линии задержки, подключенными к ду .амплитудного детектора последовательно соединенными вторым аналого- 15

цифровым преобразователем и вторым (х юком памяти, выход которого подключен к входу видеоконтрольного блока, последовательно соединенными генератором тактовых импульсов и счетчиком импульсов, выход которого соединен с вторыми входами коммутатора, первого и второго блоков памяти, и переключателем режимов, выход которого подключен к второму входу счетчика импульсов и третьим входам ключа, первого и второго блоков памяти, а четвертый вход первого блока памяти подключен к выходу второго аналого- цифрового преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| БОРТОВОЙ ОБНАРУЖИТЕЛЬ С КОМПЕНСАЦИЕЙ ВАРИАЦИЙ МАГНИТНЫХ ПОЛЕЙ | 2019 |

|

RU2710363C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА-ВЫВОДА ИЗОБРАЖЕНИЙ | 1993 |

|

RU2066928C1 |

| Измерительное устройство для геоэлектроразведки | 1980 |

|

SU868676A1 |

| УСТРОЙСТВО ДЛЯ СПЕКТРАЛЬНОГО АНАЛИЗА | 1991 |

|

RU2011966C1 |

| УЛЬТРАЗВУКОВОЕ ДИАГНОСТИЧЕСКОЕ УСТРОЙСТВО | 2002 |

|

RU2221494C2 |

| Широкополосный цифровой фазометр | 1990 |

|

SU1746325A1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ РАЗБРОСА ПАРАМЕТРОВ ФОТОЧУВСТВИТЕЛЬНЫХ ЭЛЕМЕНТОВ МНОГОЭЛЕМЕНТНОГО ПРИЕМНИКА | 1992 |

|

RU2025905C1 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| Анализатор частотного спектра | 1980 |

|

SU900209A1 |

| Анализатор амплитудно-временных параметров случайных сигналов | 1989 |

|

SU1624346A1 |

Изобретение относится к средствам неразрушающего контроля материалов и изделий и.может быть использовано для дефектоскопии и дефектомет- рии металлов в любой отрасли промышленности. Цель изобретения - повышение точности контроля за счет отстройки от влияния несовершенства изготовления катушек матричного преобразователя и влияния на результаты электрофизических параметров изделия. Устройство содержит последовательно соединенные генератор 1 , вихретоко- вый матричный преобразователь 2, коммутатор 3, ключ 4, ус шитель 5, детектор 6, АЦП 7, блок 19 памяти и видеоконтрольный блок 20, последовательно соединенные перемножитель 8, линию 9 задержки, дифференциальный усилитель 10, связанный в свою очередь с ключом 4. В состав устройства входят также подключенные к генератору 1 последовательно соединенные фазометр 11, АЦП 12, первый блок 18 памяти, связанный первым выходом через ЦАП 14 с линией 9, а вторым - через ЦАП 13 с перемножителем. Режим работы устройства, режим компенсации преобразователей матрицы и режим измерения устанавливают при помощи переключателя 17 режимов. Устройство позволяет автоматически скомпенсировать каждый преобразователь матрицы в отдельности и анализировать сигнал только от дефекта. 2 ил. i (Л

К генератору синисоидального

К коммутатори (столбцы}

тока

Риг.2

Редактор Л.Повхан

Составит ель И.Рекунова

Техред Л.Сердюкова Корректор М.Шароши

Заказ 5223/44

Тира;к 778Подписное

ВИНИЛИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| Матричный преобразователь магнитных полей | 1979 |

|

SU862060A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-09-30—Публикация

1985-04-15—Подача