Изобретение относится к радиотехнике и может быть использовано в устройствах когерентной обработки сигналов на фоне помех с неизвестной доплеровской частотой.

Цель изобретения повышение эффективности выделения сигналов на фоне помех с неизвестной доплеровской частотой.

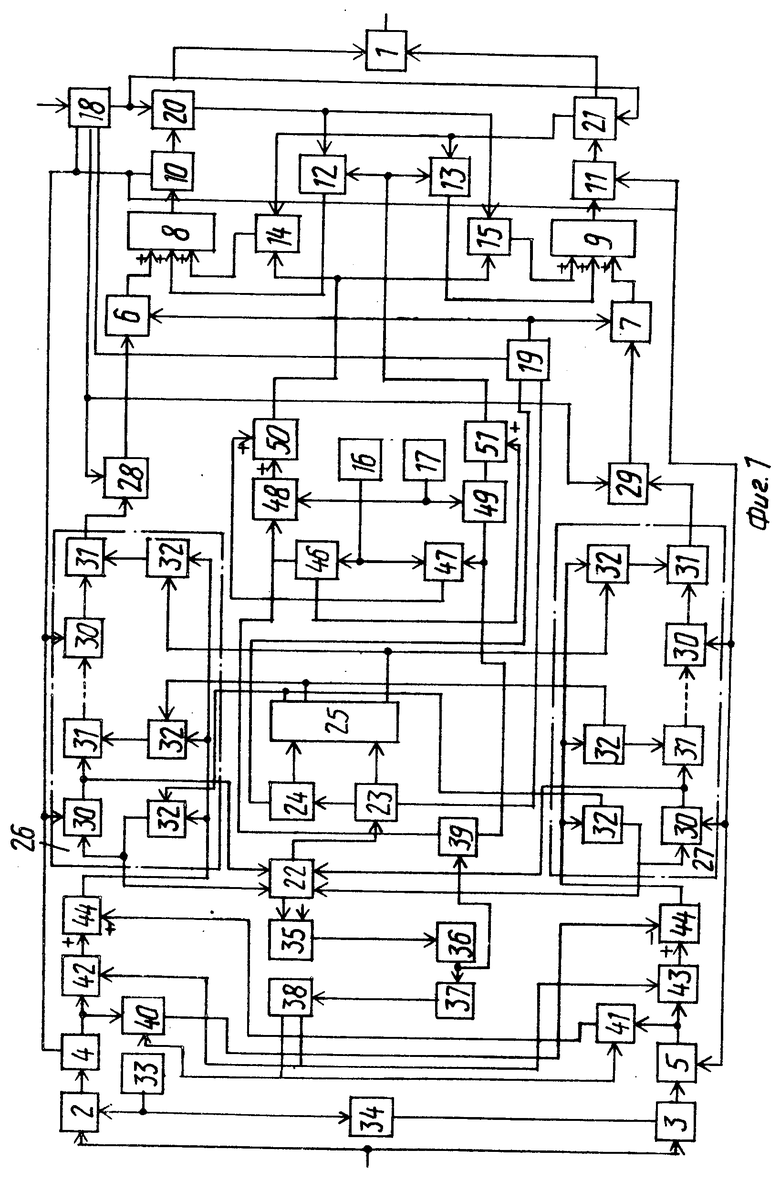

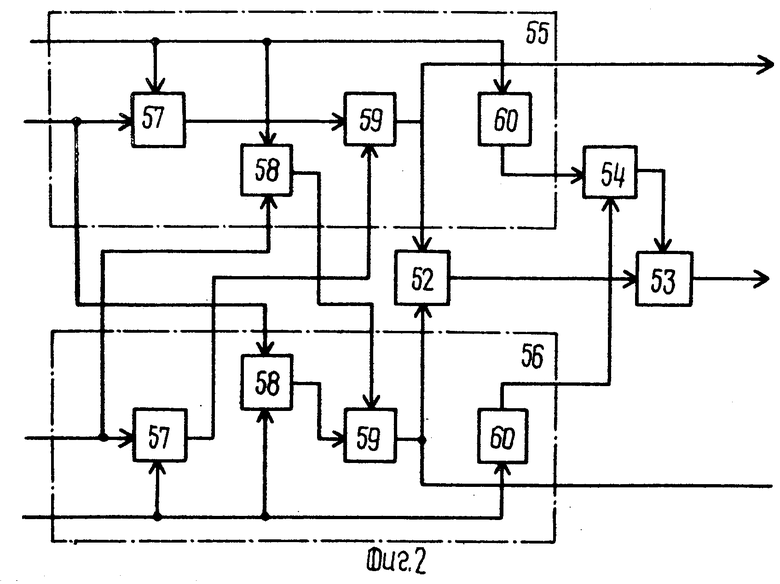

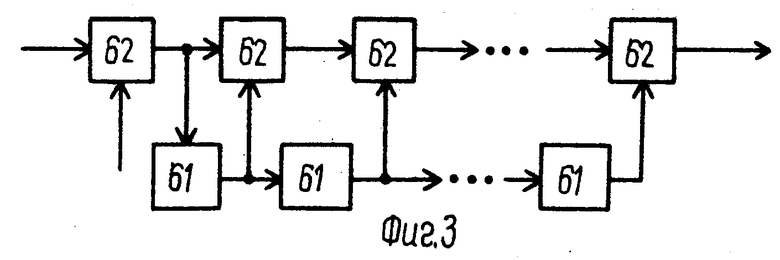

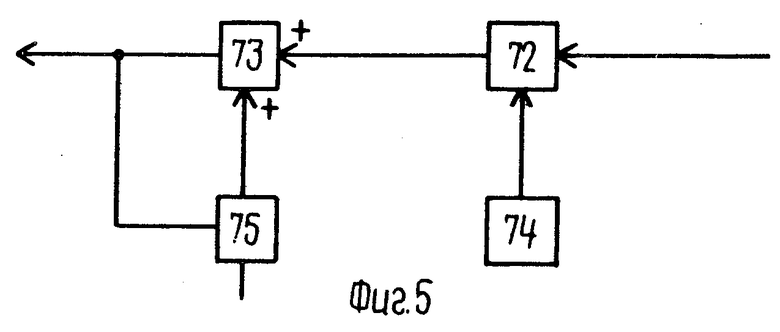

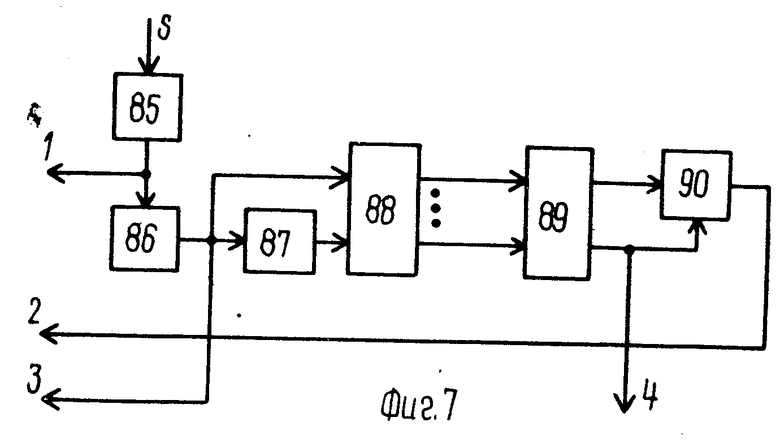

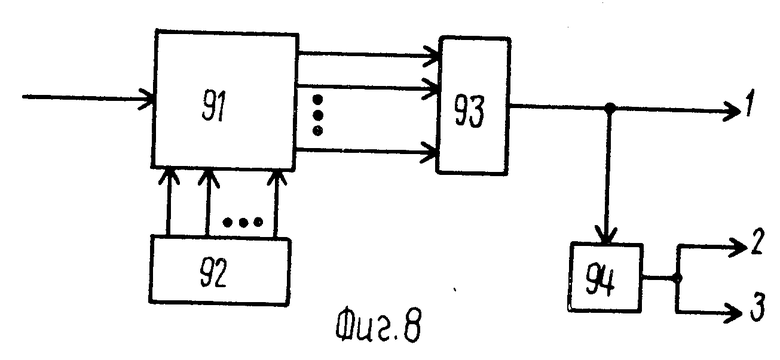

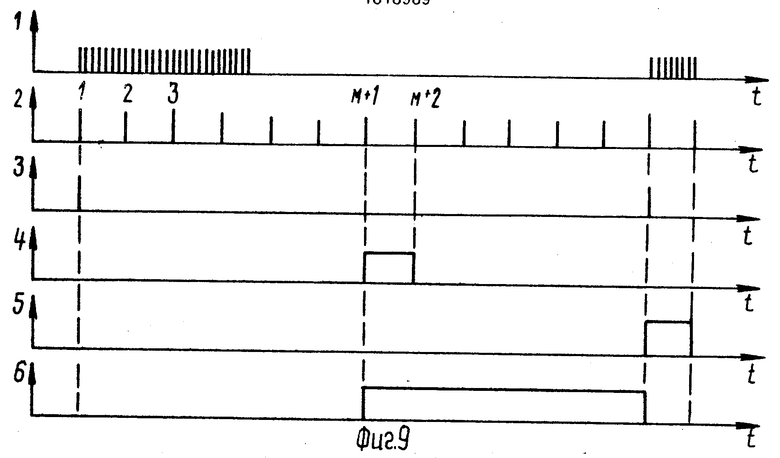

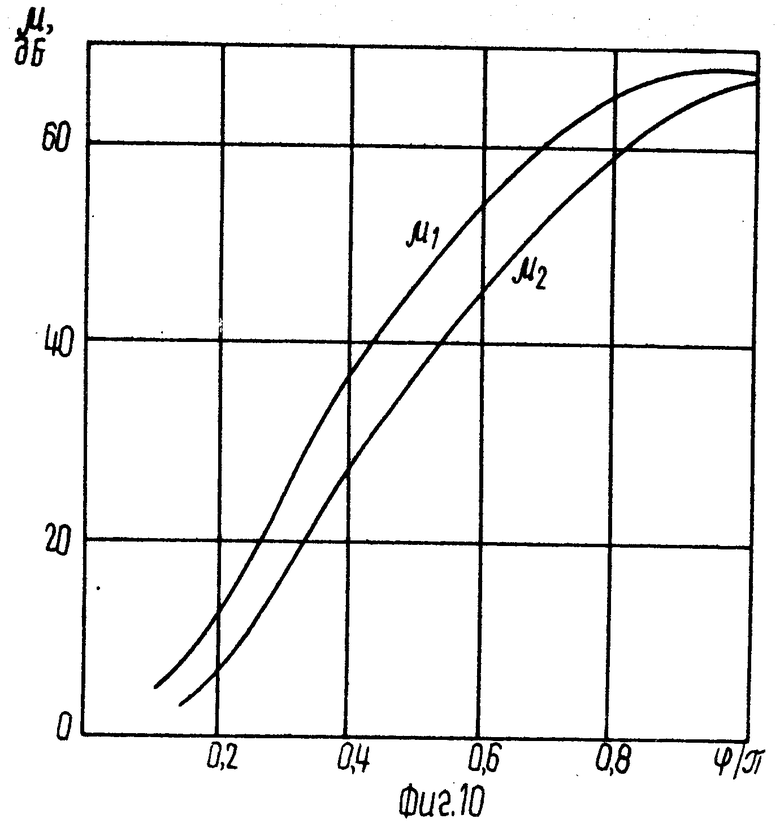

На фиг. 1 изображена структурная электрическая схема устройства цифровой когерентной обработки сигналов: на фиг. 2 схема анализатора помех: на фиг. 3 схема усредняющего сумматора: на фиг. 4 схема измерителя доплеровской расстройки частоты; на фиг. 5 схема интегратора; на фиг. 6 схема блока вычисления полного набега фазы: на фиг. 7 схема блока управления; на фиг. 8 -схема решающего блока: на фиг. 9 эпюры напряжений, поясняющие работу блока управления: на фиг. 10 зависимости эффективности прототипа и предложенного устройства.

Из блоков, входящих в прототип, устройство цифровой когерентной обработки сигналов содержит вычислитель 1, выход которого является выходом устройства, два канала, каждый из которых содержит последовательно включенные фазовый детектор 2 (3) и аналого-цифровой преобразователь 4 (5) (АЦП), а также последовательно включенные первый перемножитель б (7), сумматор 8 (9), блок памяти 10 (1 1) и первый коммутатор 20 (21), выход которого подключен к одному из входов вычислителя 1, причем первый выход блока управления 18 соединен со вторым входом АЦП 4 первого канала и со вторым входом АЦП 5 второго канала, а также со вторыми входами блоков памяти 10 и 11 первого и второго каналов, второй выход блока управления 18 соединен с управляющими входами вторых коммутаторов 28 (29) обоих каналов, выход первого 20 коммутатора первого канала соединен с первым входом второго 13 перемножителя второго канала, выход которого подключен ко второму входу сумматора 9 второго канала, кроме того, выход первого 20 коммутатора первого канала соединен с первым входом третьего 14 перемножителя первого канала, выход которого подключен ко второму входу сумматора 8 первого канала, выход первого 21 коммутатора второго канала соединен с первым входом второго 12 перемножителя первого канала, второй вход которого объединен со вторым входом второго 13 перемножителя второго канала, а выход соединен с третьим входом сумматора 8 первого канала, выход первого 21 коммутатора второго канала также соединен с первым входом третьего 15 перемножителя второго канала, выход которого подключен к третьему входу сумматора 9 второго канала, второй вход третьего 15 перемножителя второго канала объединен со вторым входом третьего 14 перемножителя первого канала, первые входы первых 6, 7 перемножителей обоих каналов подключены к выходу блока 19 весовых коэффициентов, ко второму входу первого 6, (7) перемножителя каждого канала подключен выход второго 20 (21) коммутатора, вход которого подключен к первому входу режекторного фильтра 26 (27), второй выход режекторного фильтра 26 подключен к первому входу анализатора 22 помех (фиг. 2), второй выход режекторного фильтра 27 второго канала подключен к второму входу анализатора 22 помех, третий выход режекторного фильтра 26 первого канала подключен к третьему входу анализатора 22 помех, третий вход режекторного фильтра 27 второго канала подключен к четвертому входу анализатора 22 помех, первый вход дополнительного блока 25 весовых коэффициентов соединен с первыми входами режекторных фильтров 26 (27) обоих каналов, второй, третий и т.д. до (М + 1)-го выхода дополнительного блока 25 весовых коэффициентов соединен соответственно со вторыми, третьими и т.д. до (М + 1)-ых входов режекторных фильтров 26, 27 обоих каналов, первый вход дополнительного блока 25 весовых коэффициентов и второй вход блока 19 весовых коэффициентов соединены соответственно с первым и вторым выходами постоянного запоминающего блока 24, вход которого соединен с первым выходом решающего блока 23, второй выход которого соединен со вторым входом дополнительного блока 25 весовых коэффициентов, третий выход решающего блока 23 соединен с третьим входом блока 19 весовых коэффициентов, первый выход анализатора 22 помех соединен с входом решающего блока 23, а также содержит первый 16 и второй 17 регистры числа.

Помимо блоков, содержащихся в прототипе, данное устройство содержит дополнительно генератор 33 опорного напряжения, выход которого соединен со вторым входом фазового детектора 2 первого канала и через фазовращатель 34 со вторым входом фазового детектора 3 второго канала, а также последовательно соединенные измеритель 35 доплеровской расстройки частоты (ИДРЧ), интегратор 36, блок 37 вычисления полного набега фазы (БВПНФ) и первый синусно-косинусный функциональный преобразователь 38 (СКФП), а также второй 39 СКФП, вход которого соединен с выходом интегратора 36 (фиг. 5), а в каждый из каналов введены первый 40 (41), второй 42 (43), третий 46 (47) и четвертый 48 (49) дополнительные перемножители, первый 44 (45) и второй 50 (51) дополнительные сумматоры, при этом второй и третий выходы анализатора 22 помех соединены с первым и вторым входами ИДРЧ 35 соответственно, первый и второй выходы первого 38 СКФП соединены с первыми входами соответственно первого 40 (41) и второго 44 (43) дополнительных перемножителей каждого канала, первый и второй выходы второго 39 СКФП соединены с первыми входами третьего 46 (47) и четвертого 48 (49) дополнительных перемножителей каждого из каналов, в каждом канале последовательно включенные выход аналого-цифрового преобразователя 4 (5), второй 42 (43) дополнительный перемножитель и первый 44 (45) дополнительный сумматор соединены с четвертым входом режекторного фильтра 26 (27) соответствующего канала, второй вход первого 40 (41) дополнительного перемножителя каждого канала соединен с выходом АЦП 4 (5) своего канала, выход первого 40 (41) дополнительного перемножителя каждого канала соединен со вторым входом первого 45 (44) дополнительного сумматора другого канала, кроме того, выходы первого 16 и второго 17 регистров числа соединены со вторыми входами соответственно третьего 46 (47) и четвертого 48 (49) дополнительных перемножителей каждого канала, при этом выходы второго 50 (51) дополнительного сумматора первого и второго каналов соединены соответственно со вторыми входами вторых 12 (13) и третьих 14 (15) перемножителей каждого канала.

Измеритель 35 доплеровской расстройки частоты (фиг. 4) содержит делитель 63, функциональный преобразователь 64 арктангенса (ФПА), два ключа 65, 66, два сумматора 67, 68, блок 69 присвоения знака (БПЗ), блок 70 памяти и инвертор 71 причем первый и второй входы делителя 63 являются входами ИДРЧ, выход делителя 63 через ФПА 64 соединен с первыми входами первого 65 ключа и первого 67 сумматора, второй вход первого 67 сумматора соединен с выходом блока 70 памяти, выход первого 67 сумматора соединен с первым входом БПЗ 69, второй вход которого объединен с вторым входом делителя 63, вход БПЗ 69 соединен с первым входом второго 66 ключа, второй вход которого соединен с выходом инвертора 71, вход которого объединен со вторым входом первого 65 ключа и первым входом делителя 63, выходы первого 65 и второго 66 ключей соединены соответственно с первым и вторым входами второго 68 сумматора, выход которого является выходом ИДРЧ.

Интегратор 36 (фиг. 5) содержит последовательно включенные перемножитель 72, первый вход которого является входом интегратора, и сумматор 73, выход которого является выходом интегратора, а также блок 74 памяти, выход которого соединен со вторым входом перемножителя 72, и блок 75 задержки, вход которого соединен с выходом сумматора 73. второй вход которого соединен с выходом блока 75 задержки. Блок 37 вычисления полного набега фазы (фиг. 6) содержит три сумматора 76, 77. 78, компаратор 79, инвертор 80, два ключа 81, 82, блок 83 памяти и блок 84 задержки, причем первый вход первого 76 сумматора является входом БВПНФ, выход первого 76 сумматора соединен с первым входом компаратора 79, первым входом первого 81 ключа "первым входом второго 77 сумматора, второй вход компаратора 79 соединен с выходом блока 83 памяти, выход компаратора 79 соединен со вторым входом первого 81 ключа непосредственно, а с первым входом второго 82 ключа через инвертор, второй вход второго 82 ключа соединен с выходом второго 77 сумматора, второй вход которого соединен с выходом блока 83 памяти, выходы первого 81 и второго 82 ключей соединены соответственно с первым и вторым входами третьего 78 сумматора, выход которого соединен через блок 84 задержки со вторым входом первого 76 сумматора и является также выходом БВПНФ.

Блок 18 управления (фиг. 7) содержит последовательно включенные генератор 85 импульсов дальности, первый 86 и второй 87 делители, счетчик 88, дешифратор 89, а также триггер 90, причем вход генератора 85 импульсов дальности является входом блока управления, а выход его является первым выходом блока управления, выход первого 86 делителя подключен также ко второму входу счетчика 88, первый и второй входы дешифратора 89 подключены к соответствующим входам триггера 90, выход которого является вторым выходом блока управления, выход первого 86 делителя является третьим выходом блока управления, второй выход дешифратора 89 является четвертым выходом блока управления.

Устройство работает следующим образом.

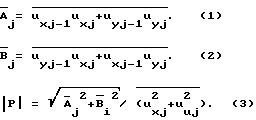

При электронном управлении антенным лучом осуществляется дискретное сканирование диаграммы направленности. После очередного скачкообразного перемещения луча в пределах его диаграммы оказывается цель и движущееся под действием ветра облако пассивных помех. Квадратурные составляющие суммы сигнала и помехи или только одной помехи с выходов фазовых детекторов 2, 3 поступают в АЦП 4, 5, где квантуются no времени и амплитуде. Далее, через перемножители 40-43 и сумматоры 44, 45, в которых осуществляется компенсация доплеровской скорости пассивной помехи путем двумерных поворотов на соответствующий угол исходных квадратурных составляющих, цифровые коды поступают в режекторные фильтры 26, 27. Со входа и выхода первых элементов 30 памяти режекторных фильтров 26, 27 не задержанные и задержанные на один период составляющие Uxj-l, UyJ-l, UxJ, UyJ, комплексных величин Uj-1, Uj поступают на входы анализатора 22 помех. В соответствии со структурой этого блока (фиг. 2) на его выходах 5, 6, и 7 образуются соответственно следующие величины:

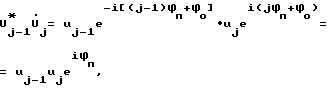

Величины Aj и Bj представляют собой усредненные по дальности соответственно действительную и мнимую части произведения комплексных величин аргумент которого Φп является доплеровским набегом фазы помехи за период повторения ввиду ее протяженного характера и значительного превышения по мощности по сравнению с сигналом.

аргумент которого Φп является доплеровским набегом фазы помехи за период повторения ввиду ее протяженного характера и значительного превышения по мощности по сравнению с сигналом.

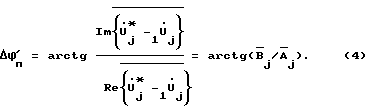

Для вычисления Φ величины  и

и  поступают в измеритель 35 доплеровской расстройки частоты. Делитель 63 (фиг. 4) вычисляет величину отношения

поступают в измеритель 35 доплеровской расстройки частоты. Делитель 63 (фиг. 4) вычисляет величину отношения  , которая поступает далее в функциональный преобразователь 64 арктангенса, вычисляющий.

, которая поступает далее в функциональный преобразователь 64 арктангенса, вычисляющий.

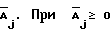

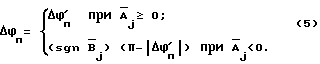

Далее величина  поступает на ключ 65 и на сумматор 67, в котором происходит вычитание этой величины из постоянного числа π,, хранящегося в блоке 70 памяти. Результаты вычисления через блок 69 присвоения знака, в котором ему присваивается знак

поступает на ключ 65 и на сумматор 67, в котором происходит вычитание этой величины из постоянного числа π,, хранящегося в блоке 70 памяти. Результаты вычисления через блок 69 присвоения знака, в котором ему присваивается знак  , поступает на вход ключа 66. Ключи 65 и 66 открываются знаковым разрядом величины

, поступает на вход ключа 66. Ключи 65 и 66 открываются знаковым разрядом величины  ключ 65 открыт, а ключ 66 закрыт, так как величина Аj подается на него через инвертор 71. В этом случае на сумматор 68 проходит величина

ключ 65 открыт, а ключ 66 закрыт, так как величина Аj подается на него через инвертор 71. В этом случае на сумматор 68 проходит величина  . При

. При  на сумматор 68 через ключ 66 проходит величина с выхода блока 69 присвоения знака.

на сумматор 68 через ключ 66 проходит величина с выхода блока 69 присвоения знака.

Таким образом, реализуется логическая операция

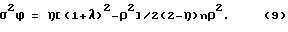

Цифровой код величины ΔΦп поступает в интегратор 36. Блок 72 (фиг. 5) производит умножение входной величины на хранящийся в блоке 74 памяти весовой коэффициент η... Величина h., хранящаяся в блоке 74, определяет коэффициент передачи разомкнутой петли автокомпенсатора, фактически образованного блоками 22, 35, 36, 38, 40-45, и влияет на его динамические свойства и флюктуационную ошибку. Анализ точности компенсации можно провести на основе известного выражения для дисперсии флюктуационной ошибки:

σ

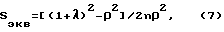

где Sэкв эквивалентная спектральная плотность флюктуаций:

Δfэф эффективная полоса пропускания автокомпенсатора.

Эквивалентная спектральная плотность флюктуаций определяется

где n число усредняемых элементов разрешения по дальности:

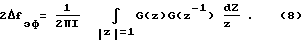

ρ коэффициент междупериодной корреляции соседних поступающих отсчетов: l отношение шум/помеха. Эффективную полосу пропускания Dfэф = можно определить:

где G(z) Н(z)/[1+ Н(z)] H(z) системная функция сглаживающего фильтра в z-плоскости. Учитывая, что H(z) = η/(z-1),, после вычисления интеграла (8) найдем 2Δfэф= η/(2-η).. Окончательно получим:

Определяя полюс zp системной функции G(z), можно найти, что условию устойчивости zp| < 1 соответствует 0<η<2, что и является критерием выбора. В общем случае величина η может выбираться из условия обеспечения заданной точности компенсации. В частности, h= 1 соответствует минимальной длительности переходного процесса.

Далее взвешенные значения входных величин в сумматоре 73 суммируются с суммой значений hDv всех предыдущих периодов, задержанной на период повторения в блоке 75 задержки. Таким образом, в интеграторе 36 происходит раздельное по каждому элементу разрешения по дальности накопление выходных величин измерителя 35 с последующим раздельным хранением накопленных сумм в соответствующих ячейках блока 75 памяти. При этом в установившемся режиме а каждой ячейке памяти образуется усредненная величина исходного доплеровского сдвига фазы помехи за последний (j-тый) период повторения  .

.

В блоке 37 вычисления полного набега фазы θj производится накопление выходных величин интегратора 36 путем суммирования их в сумматоре 76 (фиг. 6) с суммой значений всех предыдущих периодов, полученной в этом же сумматоре и задержанной на период повторения в блоке 84 задержки. Если суммарный сдвиг θj по абсолютней величине превышает 2π,, производится его нормализация. В этом случае на выходе компаратора 79, в котором происходит сравнение θj с постоянным значением 2π,, хранящимся в блоке 83 памяти, появляется сигнал логического нуля, в результате чего ключ 81 закрывается, а ключ 82 открывается логической единицей, поступающей с выхода инвертора 80. Поэтому на третий сумматор 78 поступает через ключ 82 величина суммарного сдвига за вычетом значения 2π.. Вычитание производится во втором сумматоре 77.

Далее цифровой код нормализованной величины суммарного фазового сдвига θj поступает в СКФП 38, который вырабатывает величины sinθj и cos θj.. С помощью перемножителей 40, 41, 42, 43 и сумматоров 44, 45 осуществляется компенсация полного доплеровского сдвига θj путем двумерного поворота исходных квадратурных составляющих uxj и uyj в противоположном направлении на тот же угол.

В результате этого квадратурные составляющие на выходе сумматоров 44, 45 определяются в соответствии с выражениями и в установившемся режиме практически не содержит доплеровской модуляции.

и в установившемся режиме практически не содержит доплеровской модуляции.

Сигнал, соответствующий измеренной в анализаторе 22 помех величине коэффициента междупериодной короеляции, поступает на решающий блок, который сравнивает его в компараторе 91 (фиг. 8) с имеющимся в постоянном запоминающем устройстве 92 набором постоянных величин. В зависимости от результата сравнения дешифратор 93 выдает код адреса, а формирователь 94 команды записи, в результате чего осуществляется запись из постоянного запоминающего блока 24 в блок 19 весовых коэффициентов и в дополнительный блок 25 весовых коэффициентов тех групп предварительно рассчитанных коэффициентов, которые обеспечивают наилучшее выделение сигналов на фоне помех с данным коэффициентом корреляции.

Число групп весовых коэффициентов для режекторных фильтров и накопителя определяется предполагаемым диапазоном изменения коэффициента корреляции и целесообразной степенью адаптации к его изменению. Число весовых коэффициентов в каждой группе определяется количеством импульсов в пачке. В перемножителях 32 происходит взвешивание квадратурных составляющих каждого импульса пачки, которые суммируются в сумматорах 31 с соответствующими суммами квадратурных составляющих, задержанных элементами памяти 30 импульсов пачки. Остатки режектирования с выходов режекторных фильтров 26, 27 после окончания в нем переходного процесса коммутируются дополнительными коммутаторами 28, 29 на входы первых перемножителей 6, 7, где умножаются на соответствующий весовой коэффициент. Значения этих коэффициентов определяют не только полосу пропускания когерентного накопителя, но также и уровень боковых лепестков АЧХ в каждом из каналов, требования к которому и необходимо учесть в соответствии с оценкой коэффициента корреляции помехи. Аналитическое выражение, связывающее весовые коэффициенты когерентного накопителя с параметрами помехи, получено на основе формулы для коэффициента улучшения отношения сигнал/помеха в j-том канале

где ωj= {W

где  преобразования матриц Rn и Rc, а μmax определяется решением характеристического уравнения. Из выражения (12) следует, что оптимальный вектор W

преобразования матриц Rn и Rc, а μmax определяется решением характеристического уравнения. Из выражения (12) следует, что оптимальный вектор W

Порядок всех коммутаций в устройстве когерентной обработки сигналов определяется блоком 18 управления (фиг. 7). Эпюры напряжений, поясняющие работу блока управления, приведены на фиг. 9. На вход блока из системы синхронизации станции поступают импульсы с периодом следования То, соответствующим элементу разрешения по дальности. С генератора 85 импульсов дальности импульсы с периодом следования, соответствующим элементу разрешения по дальности, поступают на АЦП 4, 5, блоки 10, 11, 30, 70, 74, 83 памяти и блоки 75, 84 задержки для синхронизации их работы, а также на вход первого делителя 86. На выходе первого делителя 86 частоты имеем импульсную последовательность с периодом Тп, равным периоду зондирования. Отсюда импульсы поступают на блок 19 весовых коэффициентов, обеспечивая переключение в нем весовых коэффициентов с частотой следования импульсов пачки. Отсюда же импульсы с периодом Тп поступают на счетчик 88 и на второй делитель 87, который снижает частоту их следования до частоты, равной частоте переключения антенного луча Fc. С приходом (М + 1)-го импульса на выходе 1 дешифратора 89 появляется логическая единица, которая переводит триггер 90 в единичное состояние. В нулевое состояние триггер сбрасывается логической единицей на втором выходе дешифратора 80, которая устанавливается с приходом последнего N-ro импульса пачки. Выходным напряжением триггера 81 коммутируются коммутаторы 28, 29. Напряжением со второго выхода дешифратора, соответствующим концу цикла накопления, замыкаются, кроме того, коммутаторы 20, 21, подключающие квадратурные сигналы ко входам вычислителя 1.

Эффективность предложенного устройства будем характеризовать коэффициентом улучшения отношения сигнал/помеха μ,, который определим в результате моделирования прохождения через устройство сигналов и помехи с ненулевой доплеровской фазой  .

.

На фиг. 10 приведены зависимости μ1 (предложенное устройство) и μ2 (прототип) от доплеровской фазы сигнала при наличии доплеровской расстройки Φп= 0,05 π;; N 8, М 3 дружных флюктуациях сигнала, гауссовской аппроксимации спектра помехи с нормированной шириной по уровню 0,5, равной 0,1. Приведенные зависимости показывают, что эффективность предложенного устройства выше эффективности прототипа на величину от 6 до 10 дБ.

Таким образом, предложенное устройство по сравнению с прототипом позволяет существенно повысить эффективность выделения сигналов на фоне помех с априори неизвестной доплеровской фазой. ЫЫЫ2 ЫЫЫ4 ЫЫЫ6 ЫЫЫ8 ЫЫЫ10

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| УСТРОЙСТВО АДАПТИВНОЙ РЕЖЕКЦИИ ПАССИВНЫХ ПОМЕХ | 1981 |

|

SU1098399A1 |

| КОРРЕЛЯЦИОННО-ФИЛЬТРОВОЕ УСТРОЙСТВО СЕЛЕКЦИИ ДВИЖУЩИХСЯ ЦЕЛЕЙ | 2003 |

|

RU2254594C1 |

| АДАПТИВНЫЙ РЕЖЕКТОРНЫЙ ФИЛЬТР | 2015 |

|

RU2579998C1 |

| УСТРОЙСТВО ДЛЯ ПОДАВЛЕНИЯ ПАССИВНЫХ ПОМЕХ | 1980 |

|

SU875960A2 |

| ВЫЧИСЛИТЕЛЬ ДЛЯ РЕЖЕКТОРНОЙ ФИЛЬТРАЦИИ ПОМЕХ | 2017 |

|

RU2646330C1 |

| ВЫЧИСЛИТЕЛЬ ДЛЯ РЕЖЕКТОРНОЙ ФИЛЬТРАЦИИ ПОМЕХ | 2017 |

|

RU2686634C1 |

| АДАПТИВНЫЙ РЕЖЕКТОРНЫЙ ФИЛЬТР | 2017 |

|

RU2660645C1 |

| УСТРОЙСТВО ДЛЯ АДАПТИВНОЙ РЕЖЕКЦИИ ПОМЕХ | 1982 |

|

SU1050405A1 |

| ВЫЧИСЛИТЕЛЬ ДЛЯ РЕЖЕКТОРНОЙ ФИЛЬТРАЦИИ ПОМЕХ | 2017 |

|

RU2686633C1 |

Использование: в устройстве обработки сигналов на фоне помех с неизвестной доплеровской частотой. Сущность изобретения: устройство содержит вычислитель, два фазовых детектора, два аналого-цифровых преобразователя, перемножители, два сумматора, два блока памяти, два регистра числа, блок управления, блок весовых коэффициентов, четыре коммутатора, анализатор помех, решающий блок, постоянный запоминающий блок, дополнительный блок весовых коэффициентов, два режекторных фильтра, генератор опорного напряжения, фазовращатель, измеритель доплеровской расстройки частоты, интегратор, блок вычисления набега фазы, два синусно-косинусных функциональных преобразователя, дополнительные перемножители, дополнительные сумматоры, что позволяет повысить эффективность выделения сигналов на фоне помех путем улучшения отношения сигнал/помеха. 1 с.п. ф-лы, 4 з.п. ф-лы, 10 ил.

| Авторское свидетельство СССР N 932894, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1996-06-27—Публикация

1990-07-16—Подача