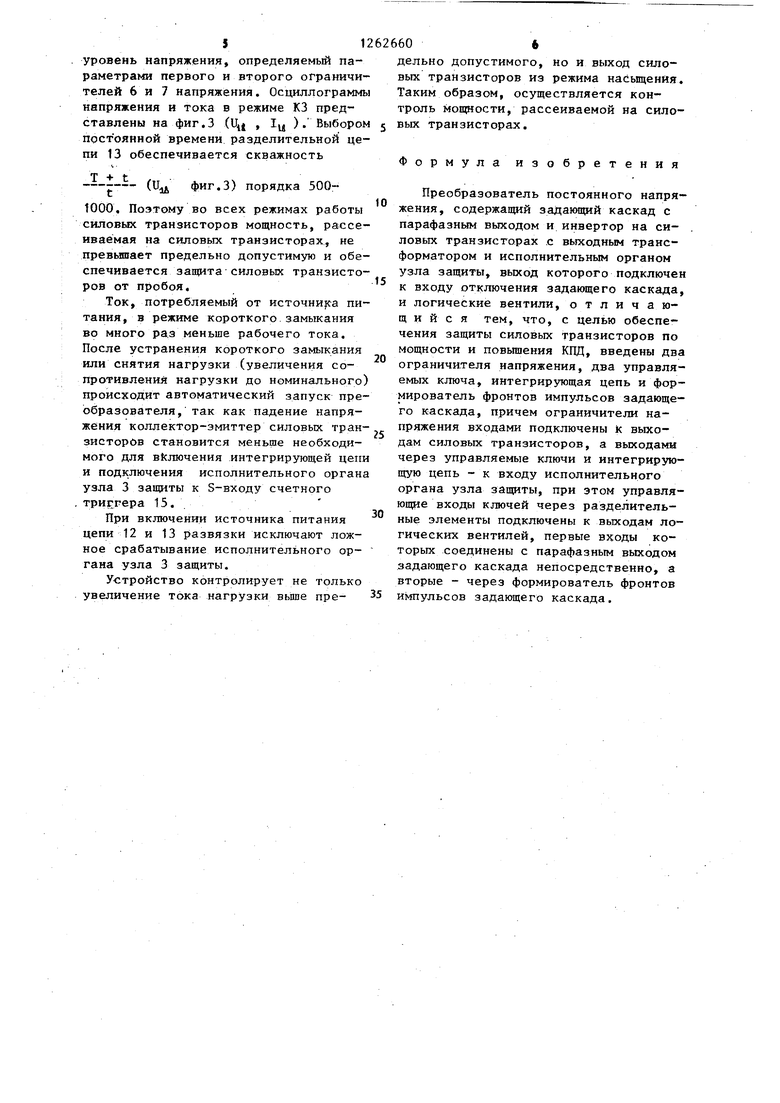

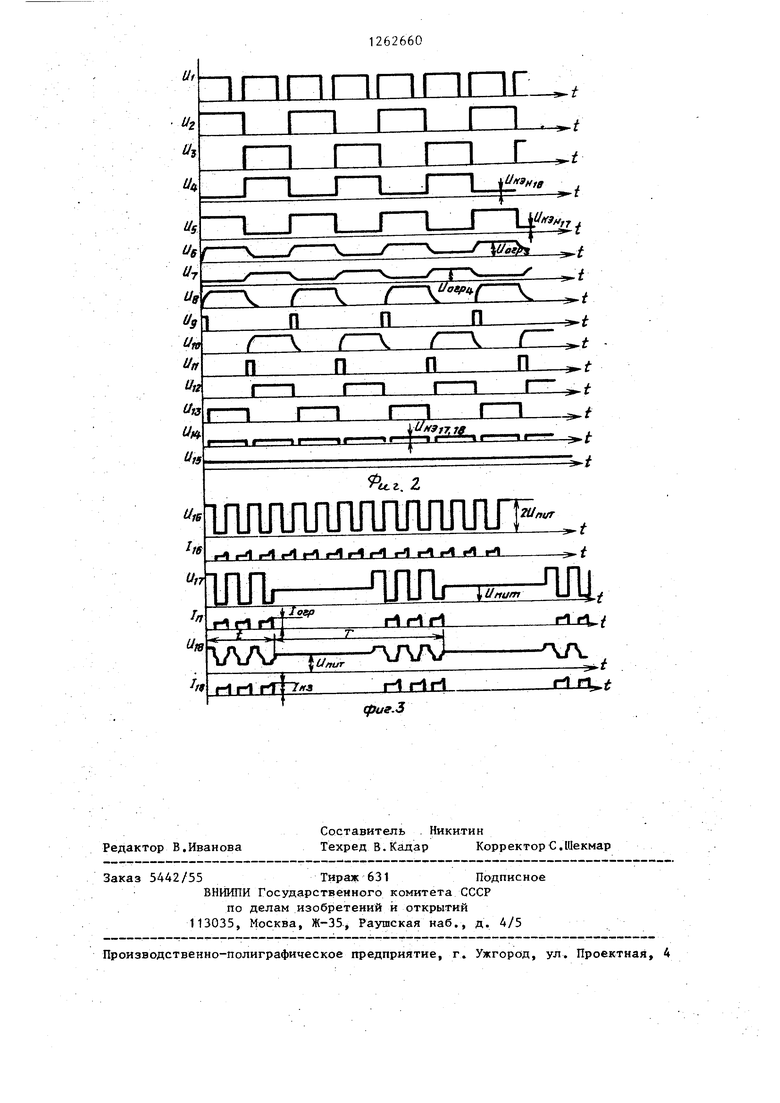

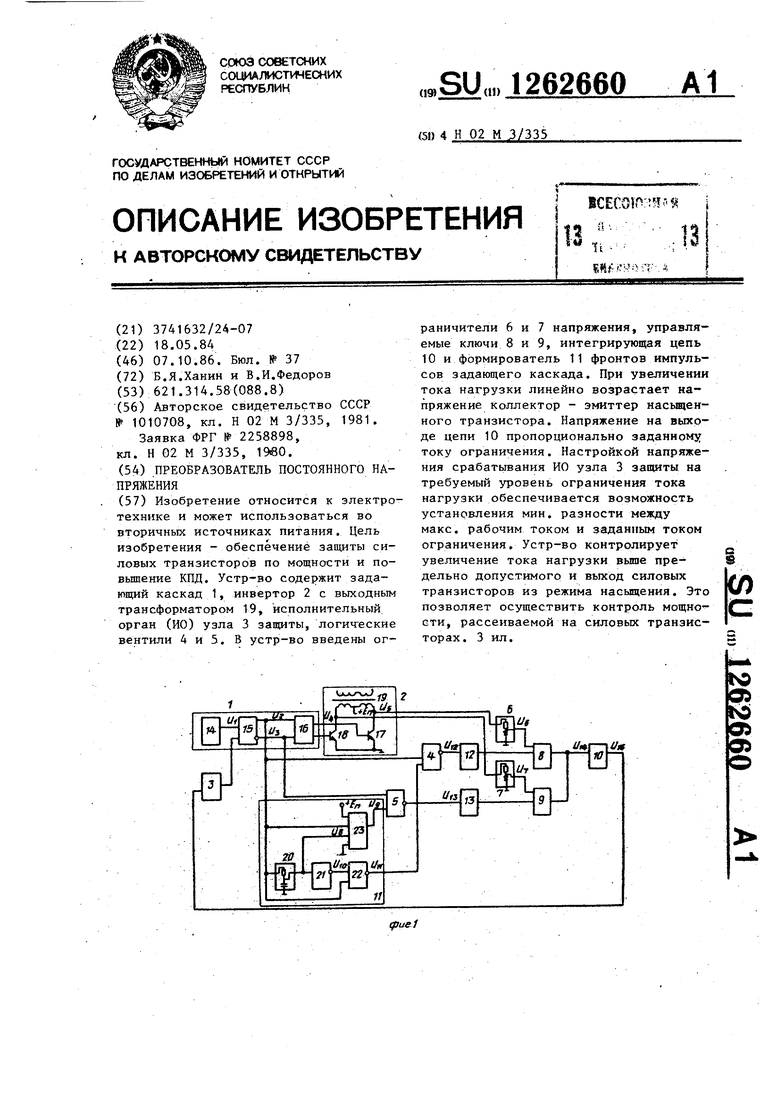

Изобретение относится к преобразрвательной технике и может использоваться в качестве вторичного источника питания в различных устройствах автоматики и вычислительной техники. Цель изобретения - обеспечение защиты силовых транзисторов по мощности и повышение КПД, На фиг«1 приведена функциональная схема преобразователя, на фиг.2 и 3времен«ые диаграммы, поясняющие его работу. Преобразователь постоянного напряжения содержит задающий каскад с парафазным выходом 1, инвертор на силовых транзисторах с выходным трансформатором 2, исполнительный орган узла 3 защиты, логические вентили 4 и 5, первый ограничитель 6 напряжения, второй ограничитель 7 напряжения, первый управляемый ключ 8, второй управляемый ключ 9, интегрирующую цепь 10, формирователь фронтов импульсов . задающего каскада 11, разделительные элементы 12 и 13. Задающий каскад с нарафазным выходом и разделительным трансформатором 1 состоит из генератора 1А импульсов .счетного триггера 15, схемы 16 развязки . Инвертор 2 содержит силовые транзисторы 17 и 18 и выходной трансформатор 19. Формирователь фронтов импульсов задающего каскада содержит цепь 20 задержки, инвертор 21, схему ИЛИ-НЕ 22, D-триггер 23. Преобразователь постоянного напряжения работает следую дим образом. Задающий генератор 14 вырабатывает несимметричные прямоугольные.импульсы {и фиг.2), поступающие на счетный вход триггера 15. На прямом выходе счетного триггера 15 возникают симметричные прямоугольные импульсы (U фиг.2) со скважностью, равной двум. На инверсном выходе счетного триггера 15 возникают симметричные прямоугольные импульсы (Uj фиг.2) со скважностью, равной двум. Через схему 16 развязки на управляющие входы силовых транзисторов 17 и 18 двухконтактного транзисторного инвертора с трансформаторным выходом 19 поступает двухполярное напряжение Транзисторы 17 и 18 поочередно отпираются, обеспечивая передачу в цепь нагрузки мощности источника питания. Трансформатор 19 работает в ненасыщенном режиме. В течение времени открытого состояния транзисторов 17 и 18 напряжение между коллектором и эмиттером каждого транзистора где Tjj и г,,- сопротивление эмиттерного и коллекторного слоев транзисторов, 1 Ci; 1э приведенный к первичной цепи ток нагрузки. В течение времени закрытого состояния транзисторов 17 и 18 напряжение между коллектором и эмиттером .каждого транзистора равно удвоенному напряжению питания. Осциллограмма напряжения между коллектором и эмиттером транзисторов 17 и 18 представлена в виде напряжения U, Uj (фиг.2). В течение времени закрытого состояния транзистора 17 первый ограничитель & 6 напряжения открывается и напряжение закрытого транзистора 17 на выходе ограничителя 6 ограничивается на уровне UoppS (Uo фиг.2). Практически величина Uopp выбирается равной прямому падению напряжения на одном или двух диодах (в зависимости от требуемого ограничения рассеиваемой мощности транзистора при перегрузке). Аналогично, в течение времени закрытого состояния транзистора 18 второй ограничитель 7 напряжения открывается и напряжение , закрытого транзистора 18 на выходе ограничителя 7 ограничивается на уровне UOPP (фиг.2). В течение времени открытого состояния транзисторов 17 и 18 напряжение насыщения, меньшее по абсолютной величине напряжения ограничения, не ограничивается соответствующим ограничителем. Вследствие инерционности ограничителей напряжения 6 и 7 фронты импульсов, поступающих на входы ключей 8 и 9 (Уф и и фиг.2), возрастают. С целью исключения всплесков напряжения на выходе ключей 8 и 9 от фронтов импульсов % и Uy в устройство введена схема формирования фронтов импульсов задающего каскада, работающая следующим образом. D-вход D-триггера 23 подключен к положительной шине источника питания преобразователя. Поэтому при поступлении на С-вход D-триггера уровня логической единицы с прямого выхода счетного триггера 15 на прямом выходе D-триггера 23 возникает уровень логической единицы. При поступлении на Р-вход D-триггера 23 уровня логической единицы (фиг.2), задержанного относительно уровня логической единицы на С-входе цепью 20 задержки на прямом выходе D-триггера, возникает уровень логического нуля. Таким образом, на прямом выходе D-триггера 23 возникают импульсы (и, фиг.2), длительность которых определяется постоянной времени цепи 2 задержки.- Величина постоянной времен цепи 20 задержки выбирается из условия перекрытия длительности фронтов напряжений U, и U7 . Благодаря действию на входах второго логического вентиля Ш1И-НЕ 5 напряжений из и Ug на входе ключа 1 действуют положительные импульсы U (фиг.2). В течение времени действий положительных импульсов U,j на вход интегрирующей цепи 10 поступает напряжение насыщения U транзистора 18 На входы логического элемента ИЛИ-НЕ 20 поступают напряжение U2 с прямого выхода счетного триггера 15 и напряжение и,о , представляющее собой проинвертированное напряжение Uj с выхо да цепи 20 задержки. На выходе логического элемента ИЛИ-НЕ 22 возникают импульсы (Цц фиг.2), закрывающие первый логический вентиль 4 на время, определяемое постоянной цепи 20 задержки. Благода ря действию на входах первого логического вентиля 4 напряжений U, UIA на входе ключа 8 действуют положительные импульсы U (фиг.2) . В течение времени действия положительных импульсов на вход интегрирующей цепи 10 поступает напряжение насыщения U транзистора 17. Входное напряжение интегрирующей цепи 10 (и,4 фиг.2) представляет со бой последовательность импульсов., ам плитуда которых равна величине напря жения насьщения транзистора 17 при открытом ключе 8 и величине напряжения насьщения транзистора 18 при открытом ключе 9. На выходе интегрирующей цепи 10 напряжение пропорционально амплитуде напряжения насыщения силовьк транзис торов 1 7 и 18. 1262 04 До момента выхода транзисторов инвертора из насьпцения осуществляется контроль тока нагрузки по значению напряжения коллектор-эмиттер насыщенных транзисторов. С увеличением тока нагрузки линейно возрастает напряжение коллектор-эмиттер насьщенного транзистора. Поэтому в режиме насыщения силовых транзисторов напряжение на выходе интегрирующей цепи пропорционально заданному току ограничения . Настройкой напряжения срабатывания исполнительного органа узла 3 защиты на требуемый уровень ограничения тока нагрузки обеспечивается возможность установления минимальной разности между максимальным рабочим током и заданным током ограничения. При срабатывании исполнительного органа узла 3 защиты на его выходе устанавливается уровень логической единицы, поступающий на S-вход счетного триггера 15. Счетный триггер 15 блокируется, на его прямом выходе устанавливается уровень логической единицы, а на инверсном выходе - уровень логического нуля. Схема 16 развязки прекращает подачу управляющих импульсов на силовые транзисторы инвертора и силовые транзисторы закрываются. На выходе первого логического вентиля 4 устанавливается уровень логического нуля, а на выходе второго логического вентиля 5 устанавливается уровень логической единицы. Время закрытого состояния силовых транзисторов определяется постоянной времени второй разделительной цепи 13, подключенной к выходу логического вентиля 5. Время открытого состояния силовых транзисторов определяется временем отпускания исполнительного органа уз- ла защиты, на вьгходе которого при работе силовых транспа15антов устанавливается уровень логического нуля. Осциллограммы напряжения и тока нормально работающих силовых транзисторов показаны на фиг.З (U, , Ijs ). В режиме ограничения рабочего тока осциллограммы напряжения и тока представлены на фиг.З (Un , In). При коротком замыкании на выходе преобразователя транзисторы 17 и 18 выходят из насьпцения и на выходе интегрирующей цепи 10 устанавливается уровень напряжения, определяемый параметрами первого и второго ограничителей 6 и 7 напряжения. Осциллограммы напряжения и тока в режиме КЗ представлены на фиг.3 (Ц| , 1ц ). Выбором постоянной времени разделительной цепи 13 обеспечивается скважность ,, (U.I фиг.З) порядка 500t1000. Поэтому во всех режимах работы силовых транзисторов мощность, рассеиваемая на силовых транзисторах, не превьшает предельно допустимую и обеспечивается защита силовых транзисторов от пробоя. Ток, потребляемый от источника питания, в режиме короткого замыкания во много раз меньше рабочего тока. После устранения короткого замыкания или снятия нагрузки (увеличения сопротивления нагрузки до номинального) происходит автоматический запуск преобразователя, так как падение напряжения коллектор-эмиттер силовых транзисторов становится меньще необходимого для включения интегрирующей цепи и подключения исполнительного органа узла 3 защиты к S-входу счетного триггера 15. При включении источника питания цепи 12 и 13 развязки исключают ложное срабатывание исполнительного органа узла 3 защиты. Устройство контролирует не только увеличение тока нагрузки выше предельно допустимого, но и выход силовых транзисторов из режима насыщения. Таким образом, осуществляется контроль мощности, рассеиваемой на силовых транзисторах. Формула изобретения Преобразователь постоянного напряжения, содержащий задакиций каскад с парафазным выходом и инвертор на силовых транзисторах с выходньм трансформатором и исполнительным органом узла защиты, выход которого подключен к входу отключения задающего каскада, и логические вентили, о т л и ч а ющ и и с я тем, что, с целью обеспечения защиты силовых транзисторов по мощности и повышения КПД, введены два ограничителя напряжения, два управляемых ключа, интегрирующая цепь и формирователь фронтов импульсов задающего каскада, причем ограничители напряжения входами подключены к выходам силовых транзисторов, а выходами через управляемые ключи и интегрирующую цепь - к входу исполнительного органа узла защиты, при этом управляющие входы ключей через разделительные элементы подключены к выходам логических вентилей, первые входы которых соединены с парафазным выходом задающего каскада непосредственно, а вторые - через формирователь фронтов импульсов задающего каскада.

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизированный преобразователь постоянного напряжения | 1989 |

|

SU1741237A1 |

| Двухтактный преобразователь постоянного напряжения | 1984 |

|

SU1251254A1 |

| Преобразователь постоянного напряжения | 1981 |

|

SU1056390A1 |

| Радиоимпульсный электростимулятор | 1980 |

|

SU1088732A1 |

| Преобразователь напряжения с защитой от асимметрии | 1990 |

|

SU1772877A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| УСТРОЙСТВО КУЖЕКОВА-КРЫНОЧКИНА ЗАЩИТЫ ЭЛЕКТРОПРИЕМНИКОВ ОТ ПРЕВЫШЕНИЯ НАПРЯЖЕНИЯ | 2002 |

|

RU2241294C2 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

| ЭЛЕКТРОПРИВОД УДАРНОГО ДЕЙСТВИЯ | 1992 |

|

RU2017319C1 |

| Преобразователь переменного напряжения в постоянное | 1987 |

|

SU1422331A1 |

Изобретение относится к электротехнике и может использоваться во вторичных Источниках питания. Цель изобретения - обеспечение защиты силовых транзисторов по мощности и повьшение КПД. Устр-во содержит задающий каскад 1, инвертор 2 с выходньтм трансформатором 19, исполнительный. орган (ИО) узла 3 защиты, логические вентили 4 и 5. В устр-во введены ограничители 6 и 7 напряжения, управляемые ключи 8 и 9, интегрирующая цепь 10 и формирователь 11 фронтов импульсов задающего каскада. При увеличении тока нагрузки линейно возрастает напряжение коллектор - эмиттер насьщениого транзистора. Напряжение на выходе цепи 10 пропорционально заданному току ограничения. Настройкой напряжения срабатьгоания ИО узла 3 запеты на требуемый уровень ограничения тока нагрузки обеспечивается возможность установления мин. разности между макс, рабочим током и заданным током ограничения, Устр-во контролирует о S увеличение тока нагрузки выше предельно допустимого и выход силовых (/) транзисторов из режима насыщения. Это позволяет осуществить контроль мощности, рассеиваемой на силовых транзисторах. 3 ил.

| Преобразователь напряжения с защитой от перегрузок | 1980 |

|

SU1010708A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| УПРАВЛЯЕМАЯ РАКЕТА | 2004 |

|

RU2258898C1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-10-07—Публикация

1984-05-18—Подача