Изобретение относится к электротехническим средствам стабилизации параметров электрической энергии, в основном для питания устройств вычислительной техники, работающих от батарей (аккумуляторов) на автономных объектах.

Наибольший эффект может быть получен в условиях глубокого разряда батарей или провалов их напряжения, специфичных для таких объектов в некоторых режимах работы, например в автомобилях при запуске двигателя.

Удовлетворение требования к миниатюаризации аппаратуры, особенное для автономных объектов, в значительной мере зависит от весогабаритных показателей источника питания аппаратуры, в которых для решения задачи применения микросхем становится необходимым.

Известен стабилизатор постоянного напряжения, работающий в режиме широтно-импульсной модуляции, содержащий регулирующий транзистор, LCD-фильтр и блок управления, основу которого составляет микросхема К142ЕП1. Эта микросхема содержит дифференциальный усилитель (транзисторы), формирователь пилообразного напряжения (диоды), работающий с внешней емкостью от внешнего генератора прямоугольного напряжения, широтно-импульсный модулятор, согласующие транзисторы и источник опорного напряжения. Выход широтно-импульсного модулятора связан с базой первого согласующего транзистора, эмиттер второго согласующего транзистора подключен к общему проводу схемы, а коллекторы обоих согласующих транзисторов через промежуточный транзистор связан с базой регулирующего транзистора. Дифференциальный усилитель сравнивает выходное напряжение с опорным, а широтно-импульсный модулятор вырабатывает импульсы, скважность которых пропорциональна разности между входным и выходным напряжениями стабилизатора при определенном токе нагрузки [1] .

Недостатком стабилизатора является то, что он способен работать лишь при входных напряжениях 10-40 В, что определяется схемотехникой источника опорного напряжения, подключаемого к первичной сети непосредственно. Работать от более низких напряжений первичной сети чем 10 В стабилизатор принципиально не может. Тем не менее в технике электропитания радиоэлектронной аппаратуре часто возникает потребность в получении сравнительно низких напряжений (наиболее часто 5 В) при уровнях входного напряжения, максимально близко приближающихся к требуемым выходным. К недостаткам микросхемы К142ЕП1 относится также большое количество внешних навесных элементов и необходимость подключения к ней внешнего источника напряжения модуляции, к тому же изолированного.

Наиболее близким по технической сущности и взятым за прототип является импульсный стабилизатор постоянного напряжения понижающего типа, содержащий блок управления, состоящий из компаратора, логического элемента 2И, RS-триггера, источника опорного напряжения, выходом соединенного с неинвертирующим входом компаратора, выход которого подключен к первому входу логического элемента 2И, а выход - к S-входу RS-триггера, из генератора, формирующего на первом выходе отрицательные тактовые импульсы, а на втором выходе - пилообразное напряжение, причем первый выход генератора подключен к второму входу логического элемента 2И и инверсному R-вход RS= триггера, соединенные последовательно между входным и выходным выводами регулирующий транзистор и LCD-фильтр, первый конденсатор, включенный между вторым выходом генератора и общей шиной, и первый резистивный делитель, включенный между выходным выводом и общей шиной, выходом соединенный с инвертирующим входом компаратора [2] .

В микросхеме μ А78S40 выходной транзистор находится в составном включении (схема Дарлингтона) с раздельно выведенными коллекторами транзисторов. Допустимо использование и одного транзистора из пары, если тока одного (первого) достаточно для внешнего от микросхемы устройства.

В понижающем стабилизаторе постоянного напряжения коллекторы обоих выходных транзисторов соединены между собой и подключены вместе с выводом питания микросхемы к входу, а между эмиттером второго выходного транзистора и выходом устройства включен дроссель, который вместе с кондесатором и внутренним диодом микросхемы образуют LCD-фильтр.

Схема 2И выполняет функцию конъюнкции напряжения генератора и компаратора и управляет RS-триггером по S-входу, в то время как R-вход этого триггера обслуживается непосредственно с выхода генератора. Силовой ключ открывается всякий раз после установки триггера в единичное состояние от выходного сигнала логического элемента 2И. Закрывается силовой ключ по окончании импульса генератора, когда происходит релаксация генератора, занимающая 1/8 часть периода работы широтно-импульсного модулятора - его естественная пауза.

Отсюда происходит недостаток микросхемы μ А78S40 (КР1156ЕУ1), заключающийся в том, что стабилизация срывается при понижении напряжения первичной сети до величины Uпр, равной сумме выходного напряжения и остаточного напряжения, которое может достигать 2,8 В. Столь значительная величина остаточного напряжения объясняется, во-первых, включением выходных транзисторов по схеме Дарлингтона, что было вызвано необходимостью сопряжения управляющего входа силового ключа с триггером, а, во-вторых, наличием естественной паузы модулятора, а значит и ключа.

Из-за этого недостатка происходят сбои в работе питаемой аппаратуры, если напряжение первичной сети претерпевает провал, входящий в зону остаточного напряжения. С другой стороны, если напряжение первичной сети, плавно снижаясь, (разряд батареи) доходит до названной зоны, выходное напряжение становится нестабилизированным и также падает. Аппаратура преждевременно теряет работоспособность.

Цель изобретения - снижение нижнего предела входного напряжения.

Это достигается вследствие того, что в импульсный стабилизатор постоянного напряжения понижающего типа, содержащий блок управления, состоящий из компаратора, логического элемента 2И, RS-триггера, источника опорного напряжения, выходом связанного с неинвертирующим входом компаратора, выход которого подключен первому входу логического элемента 2И, а выход - к S-входу RS-триггера, из генератора, формирующего на первом выходе отрицательные тактовые импульсы, а на втором выходе - пилообразное напряжение, причем первый выход генератора подключен к второму входу логического элемента 2И и к инверсному R-входу RS-триггера, соединенные последовательно между входным и выходным выводами регулирующий транзистор и LCD-фильтр, первый конденсатор, включенный между вторым выходом генератора и общей шиной, и первый резистивный делитель, включенный между выходным выводом и общей шиной, выходом соединенный с инвертирующим входом компаратора, введены первый и второй транзисторы, соответственно p-n-p и n-p-n типа проводимости, первый диод, первый, второй, третий, четвертый, пятый резисторы и блок для формирования корректирующего импульса управления, включающий в себя третий транзистор, имеющий тип проводимости n-p-n, второй конденсатор, шестой, седьмой и восьмой резисторы, узел для выделения переднего фронта импульса, IK-триггер и исполнительный элемент, а блок управления снабжен четвертым и пятым транзисторами n-p-n типа проводимости и вторым диодом, причем в качестве регулирующего транзистора использован транзистор p-n-p типа проводимости, эмиттер которого, соединенный с эмиттером первого транзистора, подключен к входу выводу положительной полярности, а коллектор первого транзистора соединен с базой регулирующего транзистора, между базой второго транзистора и коллектором первого транзистора включены последовательно соединенные первый и второй резисторы, общая точка которых подключена к первому выходу блока управления, между эмиттером первого транзистора и коллектором второго транзистора включены последовательно соединенные третий и четвертый резисторы, общая точка которых подключена к базе первого транзистора, эмиттер второго транзистора через второй диод подключен к общей шине, а база соединена с первым выходом блока для формирования корректирующего импульса управления, второй выход которого через пятый резистор подключен к базе регулирующего транзистора, а через первый диод - к первому выходу блока управления, второй выход блока управления, в качестве которого использован коллектор пятого транзистора, подключен к первому входу блока для формирования корректирующего импульса управления, второй вход которого соединен с вторым выходом генератора, а в блоке для формирования корректирующего импульса управления в качестве первого входа использован вход узла для выделения переднего фронта импульса, который через шестой резистор подключен к цепи питания блока для формирования корректирующего импульса управления, в качестве второго входа которого использован первый вывод второго конденсатора, второй вывод которого соединен с базой третьего транзистора, эмиттер этого транзистора и К-вход IK-триггера подключены к общей шине, а коллектор - к входу синхронизации IK-триггера и через седьмой резистор к цепи питания блока для формирования корректирующего импульса управления, к которой через восьмой резистор подключен также база третьего транзистора и с которой соединен I-вход IK-триггера, выход узла для выделения переднего фронта импульса подключен к R-входу IK-триггера, к выходу которого подключен вход исполнительного элемента, первый и второй выходы которого использованы в качестве соответственно первого и второго выходов блока для формирования корректирующего импульса управления, при этом исполнительный элемент выполнен обеспечивающим соответственно на первом и втором выходах сигналов Y1=  , Y2=

, Y2=  или Y1= X2, Y2= X2, где Х1 и Х2 - сигналы соответственно на прямом и инверсном выходах IK-триггера, кроме того базы четвертого и пятого транзисторов подключен соответственно к выходу RS-триггера и эмиттеру четвертого транзистора, а эмиттер пятого транзистора соединен с общей шиной.

или Y1= X2, Y2= X2, где Х1 и Х2 - сигналы соответственно на прямом и инверсном выходах IK-триггера, кроме того базы четвертого и пятого транзисторов подключен соответственно к выходу RS-триггера и эмиттеру четвертого транзистора, а эмиттер пятого транзистора соединен с общей шиной.

В частном случае связь неинвертирующего входа компаратора с выходом источника опорного напряжения может быть выполнен непосредственно.

Узел для выделения переднего фронта импульса выполнен на логическом элементе 2И-НЕ, инверторе и интегрирующей RC-цепи, причем первый вход логического элемента 2И-НЕ использован в качестве входа узла для выделения переднего фронта импульса и через последовательно соединенные инвертор и интегрирующего RC-цепь подключен к второму входу логического элемента 2И-НЕ, выход которого использован в качестве выхода узла для выделения переднего фронта импульса.

Исполнительный элемент выполнен на первом и втором буферных элементах с открытыми коллекторами, выходы которых использованы в качестве соответственно первого и второго выходов исполнительного элемента, а входы объединены и использованы в качестве входа исполнительного элемента.

С дополнительной целью расширения диапазона по току нагрузки и входному напряжению в импульсный стабилизатор введены второй резистивный делитель, включенный между входным выводом и общей шиной, девятый и десятый резисторы, блок управления снабжен операционным усилителем, блок для формирования корректирующего импульса управления - третьим входом, а исполнительный элемент - дополнительным входом и исполнительный элемент выполнен входы которых использованы в качестве входа исполнительного элемента, причем инвертирующий выход операционного усилителя подключен к выходу второго резистивного делителя, а неинвертирующий вход через девятый и десятый резисторы соответственно - к выходу источника опорного напряжения и выходу операционного усилителя, подключенного также к третьему входу блока для формирования корректирующего импульса управления, соединенному с дополнительным входом исполнительного элемента, в качестве которого использованы объединенные вторые входы буферных элементов 2И-НЕ.

Сущность изобретения заключается в том, что из общей длительности паузы блока управления выделяется ее естественная (нерегулируемая) часть и на длительность выделенной части паузы регулирующий ключевой транзистор открывается принудительно от вводимого блока для формирования корректирующего импульса управления. Главная задача состоит в том, чтобы распознать в начальной части сигнала блока управления, характерным для паузы, момент окончания нерегулируемой части, которая переходит в регулируемую без каких-либо признаков в указанном сигнале. Выработан принцип управления внешним регулирующим ключевым транзистором, позволяющий переключать управление этим транзистором с названного блока на стандартный блок управления (в микросхемном исполнении) и наоборот. С первого выхода блока управления (коллектор четвертого транзистора) ведется управление регулирующим транзистором по известной ветви, а с второго (коллектор пятого транзистора) - через блок для формирования корректирующего импульса управления, который для выполнения своей функции анализирует также пилообразное напряжение на втором выходе генератора - регулирующий транзистор управляется на время релаксации генератора. Обработка сигналов, поступающих на входы блока для формирования корректирующего импульса управления, выполняется с помощью цифровых элементов.

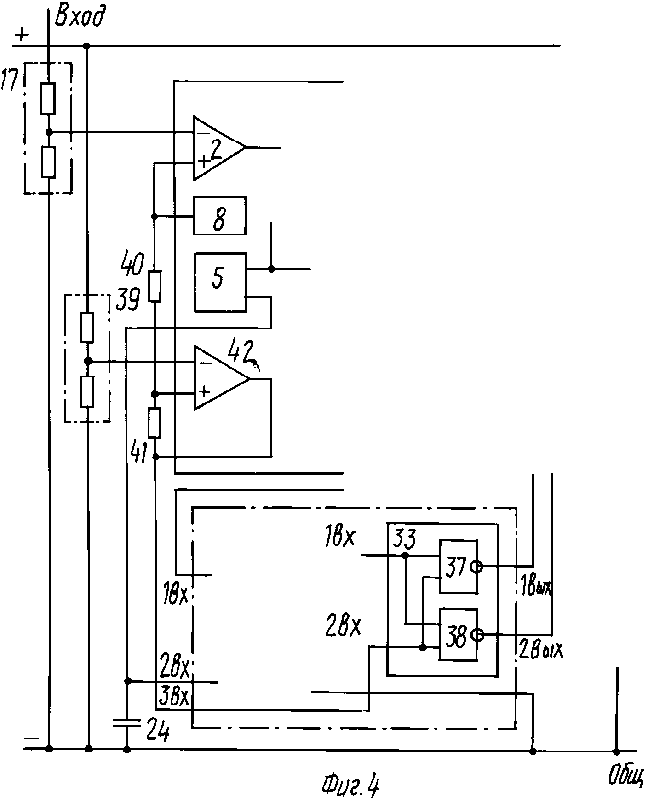

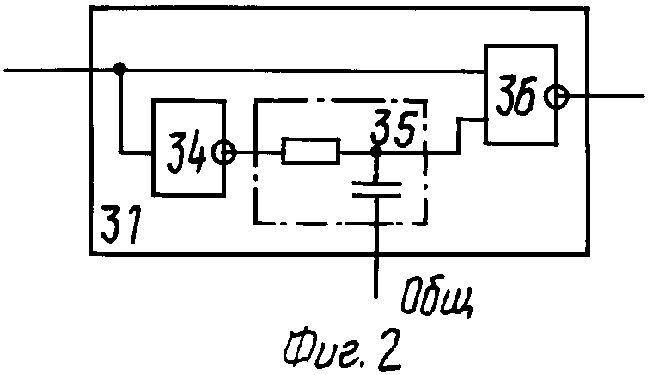

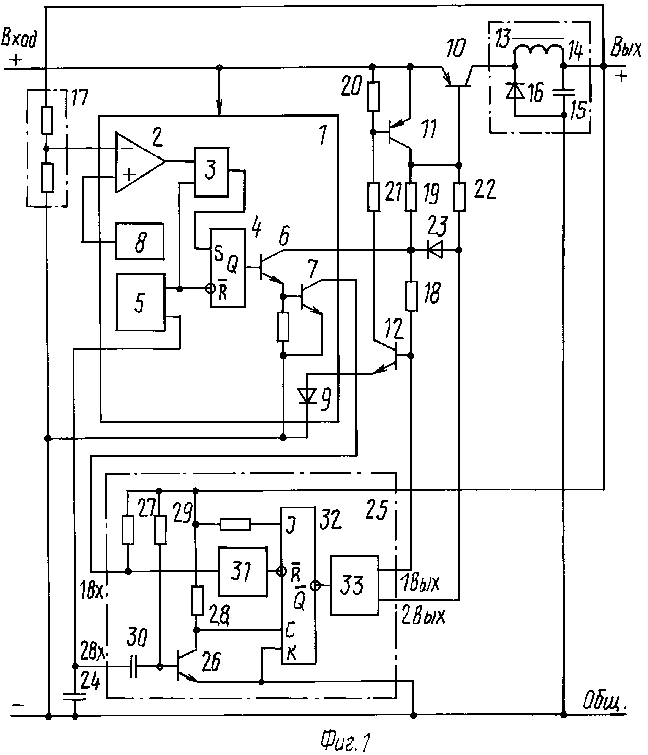

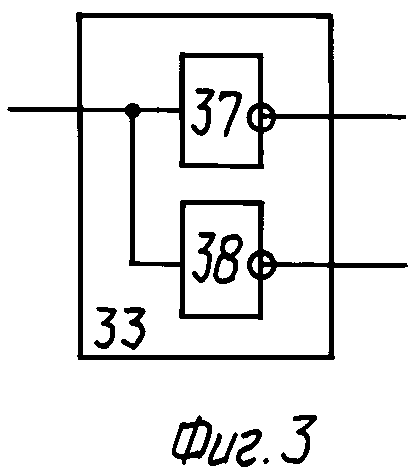

На фиг. 1 представлена схема предлагаемого стабилизатора, в котором соединение выхода источника опорного напряжения с неинвертирующим входом компаратора блока управления показано непосредственно; на фиг. 2 и 3 - варианты выполнения соответственно узла для выделения переднего фронта импульса и исполнительного элемента; на фиг. 4 - импульсный стабилизатор, способный работать в расширенном диапазоне тока нагрузки и входного напряжения (его исполнительный элемент здесь выполнен на двух двухвходовых буферных элементах 2И-НЕ).

Импульсный стабилизатор состоит (из блока 1 управления, в который входят компаратор 2, логический элемент 2И 3, первый вход которого подключен к выходу компаратора, RS-триггер 4, к S-входу которого подключен выход логического элемента 2И 3, генератор 5, первым выходом подключенный к второму входу логического элемента 2И и к R-входу RS-триггера, транзисторы 6 и 7, база транзистора 6 подключена к выходу триггера 4, а база транзистора 7 - к эмиттеру транзистора 6, коллекторы транзисторов 6 и 7 использованы в качестве первого и второго выходов блока 1 управления, а также источник 8 опорного напряжения, выход которого подключен к неинвертирующему входу компаратора 2, и диод 9, из регулирующего транзистора 10 (p-n-p), транзистора 11 (p-n-p) и транзистора 12 (n-p-n), LCD-фильтра 13, включающего в себя дроссель 14, конденсатор 15 и диод 16, из первого резистивного делителя 17, первого 18, второго 19, третьего 20, четвертого 21, пятого 22 резисторов, из диода 23, из конденсатора 24 и из блока 25 для формирования корректирующего импульса управления, содержащего транзистор 26, шестой 27, седьмой 28, восьмой 29 резисторы, конденсатор 30, узел 31 для выделения переднего фронта импульса, IK-триггер 32 и исполнительный элемент 33.

Между входом и выходом импульсного стабилизатора последовательно включены транзистор 10 и LCD-фильтр 13, причем эмиттеры транзисторов 10 и 11 подключены к входному выводу положительной полярности. Между выходом стабилизатора и инвертирующим входом компаратора 2 включен резистивный делитель 17. Цепь базового тока транзистора 12 исходит от базы транзистора 10 (см. фиг. 1). Ввиду этого соединенные последовательно между собой резисторы 18 и 19 включены между базой транзистора 12 и базой 10. Согласно такому решению базовый ток транзистора 12 одновременно является частью базового тока транзистора 10, что позволяет попутно повысить КПД. Общая точка резисторов 18 и 19 подключена к первому выходу блока 1 управления, между эмиттером транзистора 11 и коллектором транзистора 12 последовательно включены резисторы 20 и 21, общая точка которых подключена к базе транзистора 11. Эмиттер транзистора 12 через диод 9 подключен к общей шине, с которой соединены эмиттер транзистора 7 и общий провод блока 25 для формирования корректирующего импульса управления, первый и второй входы этого блока соединены соответственно с вторым выходом блока 1 управления и с вторым выходом генератора 5, к которому подключен также конденсатор 24. База транзистора 12 подключена к первому выходу блока 25, а база транзистора 10 через резистор 22 подключена к второму выходу блока 25 для формирования корректирующего импульса управления, к которому также через диод 23 подключен первый выход блока 1 управления. В блоке 25 между первым входом и цепью питания включен резистор 27 и этот вход через узел 31 для выделения переднего фронта импульса подключен к R-входу 32, второй вход блока через конденсатор 30 подключен к базе транзистора 26. К коллектору и к базе этого транзистора от цепи питания элементов блока 25 (микросхем) включены резисторы 28 и 29. Коллектор транзистора 26 соединен с входом синхронизации IK-триггера 32, эмиттер, этого транзистора и К-вход IK-триггера подключены к общей шине. Вход IK-триггера 32 связан с источником единичного уровня, а выход триггера (прямой или инверсный в зависимости от того, каким уровнем активируется исполнительный элемент 33) - к входу элемента 33.

Узел 31 для выделения переднего фронта (см. фиг. 2) состоит из инвертора 34, интегрирующей RC-цепи 35 и логического элемента 2И-НЕ 36, выход которого является выходом узла. Вход узла подключен к одному из входов логического элемента 36 и через последовательно соединенные инвертор 34 и интегрирующую цепь 35 - к другому. Исполнительный элемент 33 выполнен на первом 37 и втором 38 буферных элемента, входы которых объединены и использованы в качестве исполнительного элемента, а выходы - в качестве первого и второго выходов исполнительного элемента.

В импульсном стабилизаторе с расширенным диапазоном по току нагрузки и по входному напряжению (см. фиг. 4) дополнительно имеется второй резистивный делитель 39, девятый 40 и десятый 41 резисторы, в блоке 1 управления использован операционный усилитель 42, а в блок 25 для формирования корректирующего импульса управления введен третий вход - он же второй вход исполнительного элемента 33. Резистивный делитель 39 включен между входным выводом и общей шиной, а выходом соединен с инвертирующим входом операционного усилителя 42. К неинвертирующему входу этого усилителя через резистор 40 подключен выход источника опорного напряжения 5, а через резистор 41 - выход операционного усилителя 42, который подключен также к третьему входу блока 25. Буферные элементы 37 и 38 - двухвходовые, в данном конкретном примере выполнены они в виде логических элементов 2И-НЕ с открытыми коллекторами и повышенной нагрузочной способностью, одноименные входы которых соединены между собой и использованы в качестве соответственно первого и второго входов исполнительного элемента 33.

Работает импульсный стабилизатор следующим образом.

С подачей на него входного напряжения начинают функционировать в блоке 1 управления источник 8 опорного напряжения 8 и генератор 5, вырабатывающий на первом выходе отрицательные импульсы (исходный уровень - единичный), а на втором - пилообразное напряжение (нарастающей формы). Периоды релаксации генератора 5 приходятся на время существования импульсов первого выхода. От переднего фронта этих импульсов триггер 4 сбрасывается и транзистор 6 закрывается. При закрытом транзисторе 6 находятся в открытом состоянии транзисторы 12 и 11, а значит закрыт регулирующий ключевой транзистор 10, шунтируемый по переходу база-эмиттер промежутком коллектор-эмиттер транзистора 11. В начальный период работы до появления на выходе номинального значения напряжения на выходе компаратора 2 поддерживается единичный уровень напряжения и с окончанием импульса генератора 5 RS-триггер 4 перебрасывается от логической единицы, появляющейся на выходе логического элемента 2И 3. Открывается транзистор 6 и соответственно открывается транзистор 10, повторяющий состояние транзистора 6, имеющего обязательную паузу в работе (не меньшую времени релаксации генератора) независимо от соотношения заданного и фактического выходного напряжения. По мере приближения уровня выходного напряжения к номинальному пауза становится регулируемой, увеличиваясь относительно своей минимальной величины и скважность импульсов транзистора 10 таким образом становится по цепи обратной связи через резистивный делитель 17 в зависимость от входного напряжения и тока нагрузки. Однако при уменьшении входного напряжения транзистора 10 открывается на все большее время в течение периода. Чтобы не прекратилась стабилизация выходного напряжения, когда пауза регулирующего транзистора 10 должна стать меньшей времени релаксации генератора 5 или исчезнуть совсем, предпринята коррекция управления, т. е. автоматическое управление регулирующего транзистора на все время паузы блока управления - посредством блока для формирования корректирующего импульса управления. Регулирующий транзистор 10 на время действия этого блока открывается несмотря на то, что транзисторы 6 и 7 блока управления закрываются.

В блоке 25 для формирования корректирующего импульса управления осуществления осуществляется выделение границ паузы блока управления. В его начале узлом для выделения переднего фронта вырабатывается импульс длительностью, достаточной для сброса IK-триггера 32, но оканчивающийся раньше, чем начинается положительный импульс на коллекторе транзистора 26. С помощью этого транзистора распознается прекращение паузы блока управления путем анализа пилообразного напряжения с второго выхода генератора 5, выделяемого на конденсаторе 24 во время ниспадающей части пилообразного напряжения, подаваемого через конденсатор 30 на базу транзистора 26. Последний закрывается, а по окончании процесса релаксации генератора 5 вновь открывается и поддерживается в этом состоянии током через резистор 29, чему соответствует состояние логического нуля на коллекторе транзистора 26. IK-триггер 32 переключается в единичное состояние по синхронизирующему входу от заднего фронта импульса, снимаемого с коллектора транзистора 26, так как сигналы на I-входах и К-фиксированные, а именно: единичный и нулевой соответственно. На инверсном выходе IK-триггера получен импульс положительной полярности, на время действия которого в исполнительном элементе образуется проводимость от обоих выходов блока 25 на общую шину.

Шунтированием база-эмиттерного перехода (и последовательно включенного с ним диода 9) первым выходом исполнительного элемента обуславливается закрывание транзистора 12 и 11, а током через второй выход исполнительного элемента и резистор 22 включается транзистор 10. Паузы в работе транзистора 10 во время паузы блока управления таким образом нет. Регулирование скважности работы транзистора 10 начинается по окончании естественной паузы блока управления, если после нее (и в ее продолжение) последует регулируемая пауза, величина которой определяется обратной связью с выхода стабилизатора. Она по мере понижения входного напряжения, стремясь уменьшиться по длительности, исчезает совсем - транзистор 10 становится полностью открытым. Только теперь наступает предел стабилизации, превышающий номинальное выходное напряжение на величину падения напряжения на насыщенном регулируемом транзисторе 10 и дросселе LCD-фильтра 13 (обычно не более 0,3 В в сумме).

Передний фронт импульса для переключения IK-триггера по установочному R-входу вырабатывается (см. фиг. 2) путем операции конъюнкции и инверсии элементов 2И-НЕ 36 сигнала с второго выхода блока управления, нагрузкой которого служит резистор 27, и сигнала с инвертора 34, задеpжанного интегрирующего RC-цепь 35. Длительность импульса, получаемого на выходе узла, определяется постоянной времени RC-цепи 35.

В исполнительном элементе 33 (см. фиг. 3) на двух буферных элемента при наличии корректирующего импульса с выхода IK-триггера 32 оба буферных элементах активируются (в них открываются выходные транзисторы, коллекторы которых - суть выходы буферных элементов), благодаря чему производится коррекция управления транзистором 10.

Эта коррекция, однако, становится излишней, если входное напряжение имеет максимальную (или близкую к ней) величину, а нагрузка снижается (вплоть до холостого хода). Время работы регулирующего транзистора 10 за период работы генератора в этом случае должно стать меньшим, чем время релаксации генератора и поэтому пауза блока управления должна быть воспроизведена транзистором 10 без коррекции управления им. Поэтому при широком диапазоне изменения входного напряжения и тока нагрузки коррекцию управления транзистором 10 становится целесообразным производить лишь при пониженном входном напряжении.

Измерителем входного напряжения является (см. фиг. 4) операционный усилитель 42, сравнивающий опорное напряжение с напряжением делителя 39. Резисторы 40 и 41 служат для придания измерителю триггерной характеристик (вследствие образующейся положительной обратной связи) и гистерезиса. Выше порога переключения операционного усилителя коррекция запрещается логическим нулем на выходе операционного усилителя 42, а ниже - разрешается логической единицей на этом выходе (цепь питания операционного усилителя 42 подключается к цепям питания цифровых микросхем), которая вместе с логической единицей на выходе IK-триггера 32 приводит в действие исполнительный элемент на время естественной (нерегулируемой) паузы блока 1 управления.

Таким образом, какие-либо ограничения на диапазон изменения входного напряжения и нагрузки снимаются.

Предлагаемый импульсный стабилизатор отличается от прототипа тем, что он способен продолжать работу при снижении входного напряжения до величины, практически равной выходному напряжению, так как пауза в проводящем состоянии регулирующего ключевого транзистора в конечном счете исчезает. Это качество не вступает в противоречие с требованием по динамическому диапазону изменения входного напряжения в верхней его части и тока нагрузки, так как стабилизатор перестраивается на два режима в зависимости от уровня входного напряжения. Вместе с тем реализация перестройки не вызывает затруднений, так как операционный усилитель имеется в составе микросхемы μ А78S40 (КР1156ЕУ1) и его рационально использовать в схеме измерителя напряжения. (56) 1. Микросхемы для бытовой аппаратуры. Справочник. М. : Радио и связь, 1989, с. 50.

2. Фолкенберри Л. Применение операционных усилителей и линейных интегральных схем. М. : Мир, 1985, с. 315, рис. 10.17а.

Использование: в стабилизаторах постоянного напряжения, наиболее предпочтительно - в автономных объектах, работающих от батарей (аккумуляторов), претерпевающих глубокий разряд или провал напряжения при больших перегрузках. Сущность изобретения: стабилизатор содержит блок управления, в состав которого входят компаратор, логический элемент 2И, RS-триггер, генератор, транзисторы, источник опорного напряжения и диод, регулирующий транзистор, транзисторы, LCD-фильтр, резистивный делитель, резисторы, диод, конденсатор, блок для формирования корректирующего импульса управления, состоящий из транзистора, резисторов, конденсатора, узла для выделения переднего фронта импульса, YK-триггера и исполнительного элемента. Из общей длительности паузы блока управления выделяется ее естественная (нерегулируемая) часть и на длительность выделенной части паузы регулирующий транзистор открывается принудительно от блока для формирования корректирующего импульса управления. Такое управление регулирующим транзистором позволяет осуществлять стабилизацию выходного напряжения при пониженном входном напряжении. 4 з. п. ф-лы, 4 ил.

-входом RS-триггера, S-вход которого подключен к выходу логического элемента 2И, и первый конденсатор, включенный между вторым выходом генератора и общей шиной, отличающийся тем, что, с целью снижения нижнего предела входного напряжения, в него введены первый и второй транзисторы соответственно p - n - p - и n - p - n-типа проводимости, с первого по пятый резисторы, первый диод и блок для формирования корректирующего импульса управления, включающий в себя третий транзистор n - p - n-типа проводимости, второй конденсатор, шестой, седьмой и восьмой резисторы, узел для выделения переднего фронта импульса, JK-триггер и исполнительный элемент, а блок управления снабжен четвертым и пятым транзисторами n - p - n-типа проводимости и вторым диодом, причем в качестве регулирующего транзистора использован транзистор p - n - p-типа проводимости, эмиттер которого, соединенный с эмиттером первого транзистора, подключен к входному выводу, а коллектор первого транзистора соединен с базой регулирующего транзистора, между базой второго транзистора и коллектором первого транзистора включены последовательно соединенные первый и второй резисторы, общая точка которых подключена к первому выходу блока управления, в качестве которого использован коллектор четвертого транзистора, между эмиттером первого транзистора и коллектором второго транзистора включены последовательно соединенные третий и четвертый резисторы, общая точка которых подключена к базе первого транзистора, эмиттер второго транзистора через второй диод подключен к общей шине, а база соединена с первым выходом блока для формирования корректирующего импульса управления, второй выход которого через пятый резистор подключен к базе регулирующего транзистора, а через первый диод - к первому выходу блока управления, второй выход блока управления, в качестве которого использован коллектор пятого транзистора, подключен к первому входу блока для формирования корректирующего импульса управления, второй вход которого соединен с вторым выходом генератора, а в блоке для формирования корректирующего импульса управления в качестве первого входа использован вход узла для выделения переднего фронта импульса, который через шестой резистор подключен к цепи питания блока для формирования корректирующего импульса управления, в качестве второго входа которого использован первый вывод второго конденсатора, второй вывод которого соединен с базой третьего транзистора, эмиттер этого транзистора и K-вход JK-триггера подключены к общей шине, а коллектор - к входу синхронизации JK-триггера и через седьмой резистор - к цепи питания блока для формирования корректирующего импульса управления, к которой через восьмой резистор подключена также база третьего транзистора и с которой соединен J-вход JK-триггера, выход узла для выделения переднего фронта импульса подключен к

-входом RS-триггера, S-вход которого подключен к выходу логического элемента 2И, и первый конденсатор, включенный между вторым выходом генератора и общей шиной, отличающийся тем, что, с целью снижения нижнего предела входного напряжения, в него введены первый и второй транзисторы соответственно p - n - p - и n - p - n-типа проводимости, с первого по пятый резисторы, первый диод и блок для формирования корректирующего импульса управления, включающий в себя третий транзистор n - p - n-типа проводимости, второй конденсатор, шестой, седьмой и восьмой резисторы, узел для выделения переднего фронта импульса, JK-триггер и исполнительный элемент, а блок управления снабжен четвертым и пятым транзисторами n - p - n-типа проводимости и вторым диодом, причем в качестве регулирующего транзистора использован транзистор p - n - p-типа проводимости, эмиттер которого, соединенный с эмиттером первого транзистора, подключен к входному выводу, а коллектор первого транзистора соединен с базой регулирующего транзистора, между базой второго транзистора и коллектором первого транзистора включены последовательно соединенные первый и второй резисторы, общая точка которых подключена к первому выходу блока управления, в качестве которого использован коллектор четвертого транзистора, между эмиттером первого транзистора и коллектором второго транзистора включены последовательно соединенные третий и четвертый резисторы, общая точка которых подключена к базе первого транзистора, эмиттер второго транзистора через второй диод подключен к общей шине, а база соединена с первым выходом блока для формирования корректирующего импульса управления, второй выход которого через пятый резистор подключен к базе регулирующего транзистора, а через первый диод - к первому выходу блока управления, второй выход блока управления, в качестве которого использован коллектор пятого транзистора, подключен к первому входу блока для формирования корректирующего импульса управления, второй вход которого соединен с вторым выходом генератора, а в блоке для формирования корректирующего импульса управления в качестве первого входа использован вход узла для выделения переднего фронта импульса, который через шестой резистор подключен к цепи питания блока для формирования корректирующего импульса управления, в качестве второго входа которого использован первый вывод второго конденсатора, второй вывод которого соединен с базой третьего транзистора, эмиттер этого транзистора и K-вход JK-триггера подключены к общей шине, а коллектор - к входу синхронизации JK-триггера и через седьмой резистор - к цепи питания блока для формирования корректирующего импульса управления, к которой через восьмой резистор подключена также база третьего транзистора и с которой соединен J-вход JK-триггера, выход узла для выделения переднего фронта импульса подключен к  -входу JK-триггера, к выходу которого подключен вход исполнительного элемента, первый и второй выходы которого использованы в качестве соответственно первого и второго выходов блока для формирования корректирующего импульса управления, при этом исполнительный элемент выполнен обеспечивающим соответственно на первом и втором выходах сигналов Y1 =

-входу JK-триггера, к выходу которого подключен вход исполнительного элемента, первый и второй выходы которого использованы в качестве соответственно первого и второго выходов блока для формирования корректирующего импульса управления, при этом исполнительный элемент выполнен обеспечивающим соответственно на первом и втором выходах сигналов Y1 =  , Y2 =

, Y2 =  или Y1 = X 2, Y2 = X2, где X1 и X2-сигналы соответственно на прямом и инверсном выходах JK-триггера, кроме того, базы четвертого и пятого транзисторов подключены соответственно к выходу RS-триггера и к эмиттеру четвертого транзистора, а эмиттер пятого транзистора соединен с общей шиной.

или Y1 = X 2, Y2 = X2, где X1 и X2-сигналы соответственно на прямом и инверсном выходах JK-триггера, кроме того, базы четвертого и пятого транзисторов подключены соответственно к выходу RS-триггера и к эмиттеру четвертого транзистора, а эмиттер пятого транзистора соединен с общей шиной.

Авторы

Даты

1994-01-15—Публикация

1991-07-08—Подача