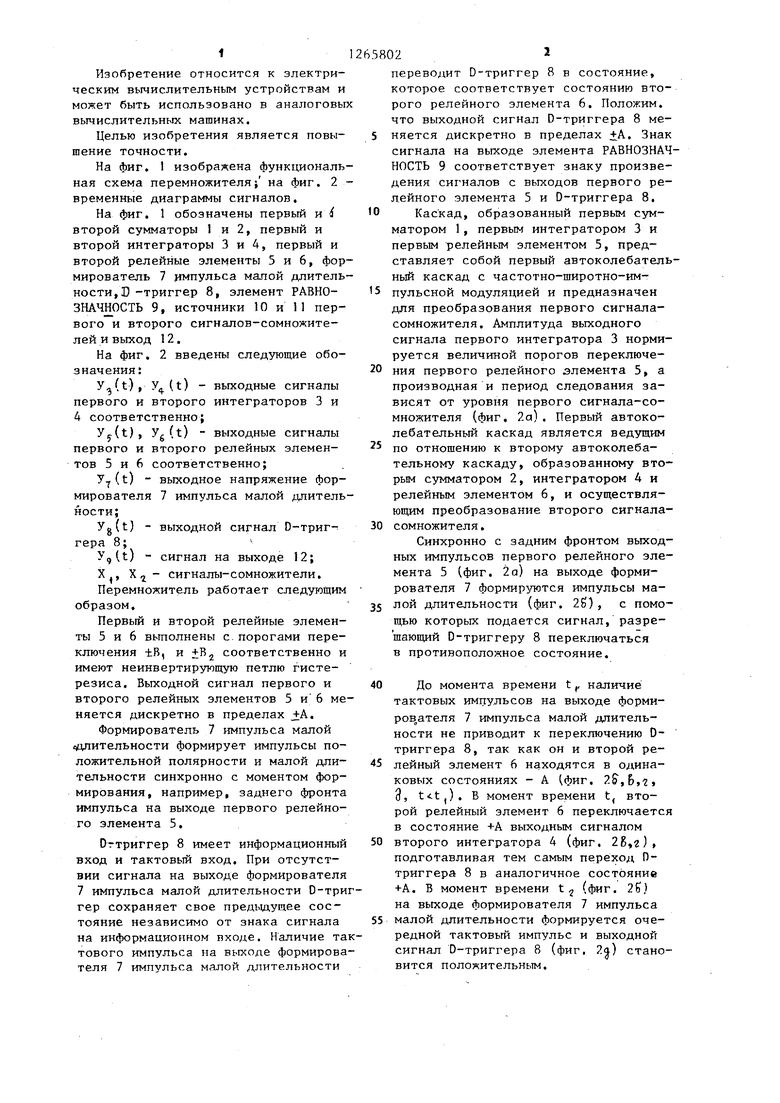

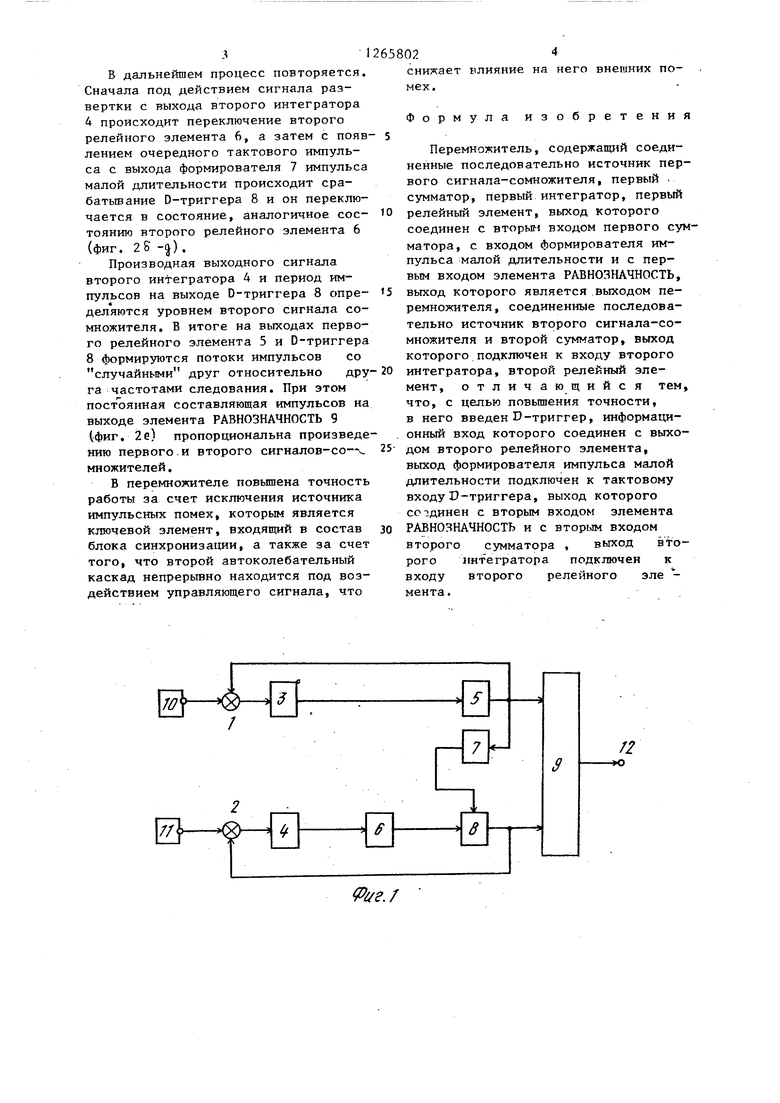

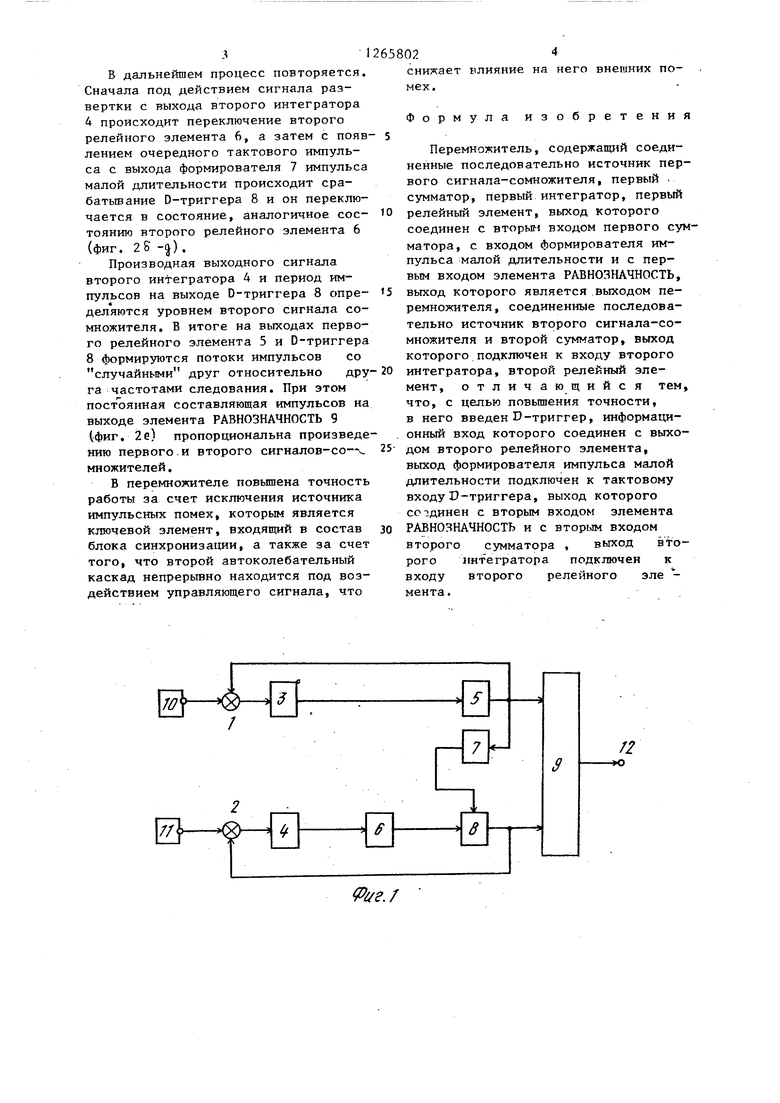

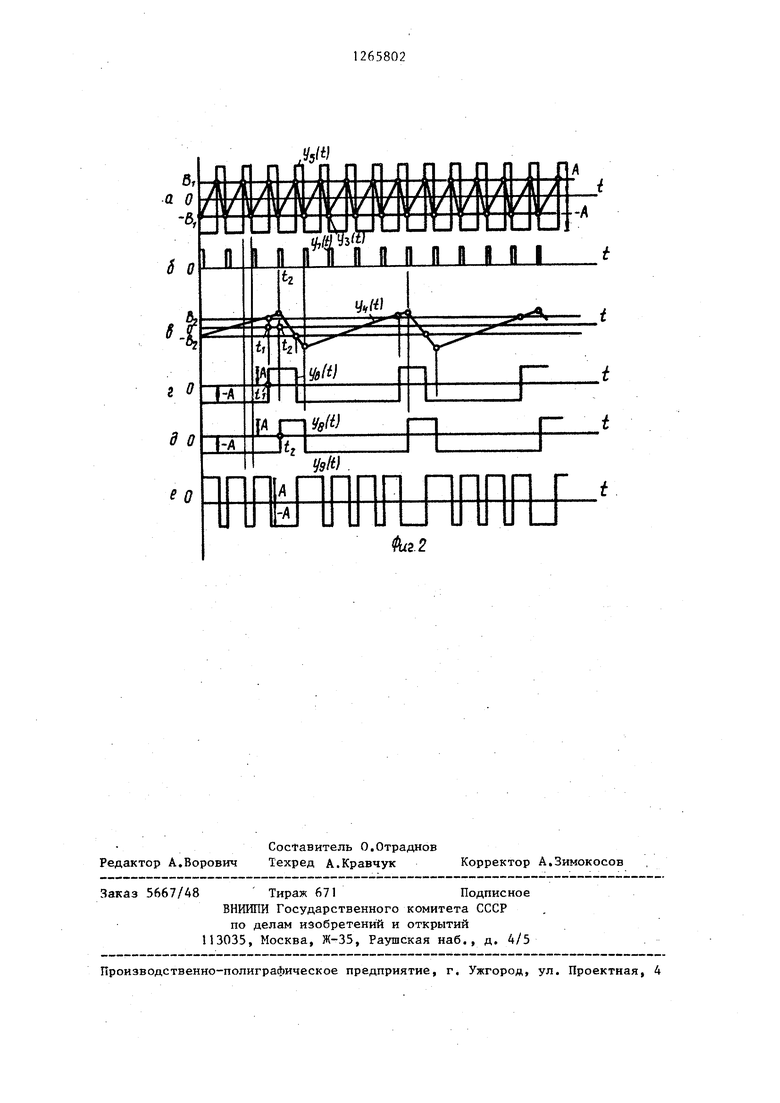

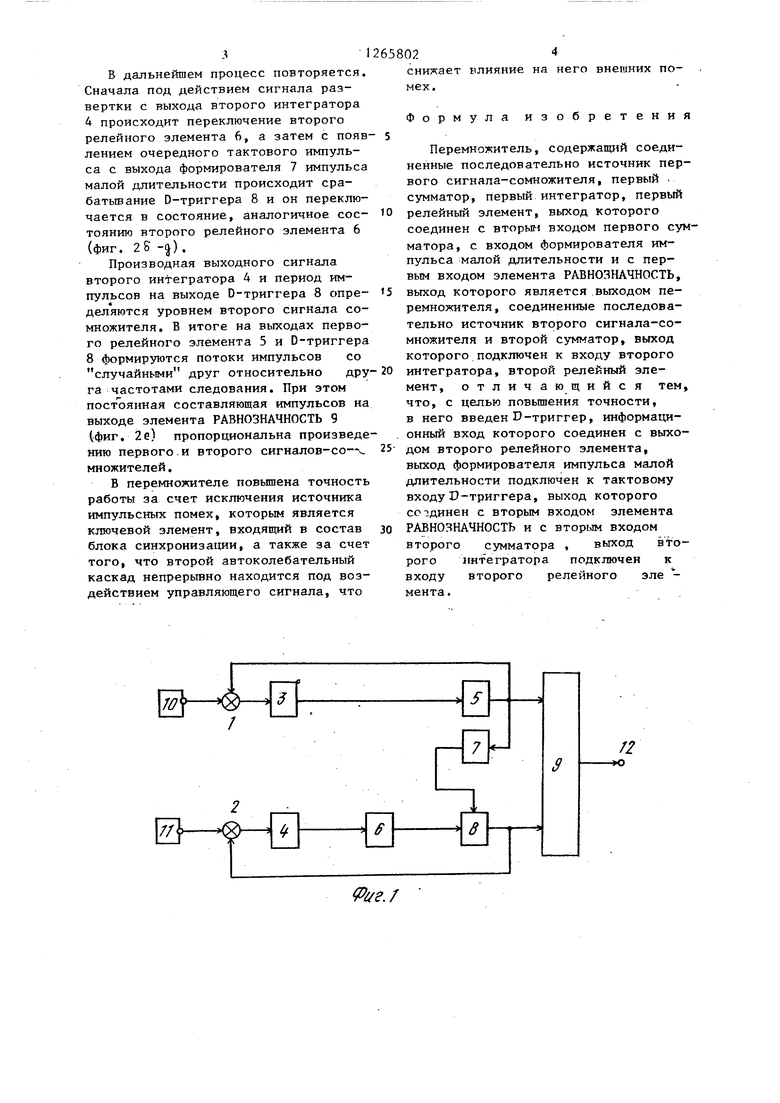

Изобретение относится к электрическим вьмислительным устройствам и может быть использовано в аналоговы вычислительных машинах. Целью изобретения является повышение точности. На фиг. 1 изображена функциональ ная схема перемножителя} на фиг. 2 временные диаграммы сигналов. На фиг, 1 обозначены первый и второй сумматоры 1 и 2, первый и второй интеграторы 3 и 4, первый и второй релейные элементы 5 и 6, фор мирователь 7 импульса малой длитель ности/) -триггер 8, элемент РАВНОЗНАЧНОСТЬ 9, источники 10 и 11 первого и второго сигналов-сомножителей и выход 12. На фиг. 2 введены следующие обозначения:y(t), y(t) - выходные сигналы первого и второго интеграторов 3 и 4 соответственно; y5(t), ) - выходные сигналы первого и второго релейных элементов 5 и 6 соответственно; y.j(t) - выходное напряжение формирователя 7 импульса малой длитель ности; yg(t} - выходной сигнал D-триггера 8;У(} сигнал на выходе 12; Х, сигналы-сомножители. Перемножитель работает следующим образом. Первый и второй релейные элементы 5 и 6 выполнены с.порогами переключения ±В, и iBj соответственно и имеют неинвертирующую петлю гистерезиса. Выходной сигнал первого и второго релейных элементов 5 и 6 ме няется дискретно в пределах +А. Формирователь 7 импульса малой «длительности формирует импульсы положительной полярности и малой длительности синхронно с моментом формирования, например, заднего фронта импульса на выходе первого релейного элемента 5. Оттриггер 8 имеет информационный вход и тактовый вход. При отсутствии сигнала на выходе формирователя 7 импульса малой длительности О-три гер сохраняет свое предыдущее состояние независимо от знака сигнала на информационном входе. Наличие та тового импульса на выходе формирова теля 7 импульса малой длительности 22 переводит D-триггер 8 в состояние, которое соответствует состоянию второго релейного элемента 6. Положим, что выходной сигнал D-триггера 8 меняется дискретно в пределах +А. Знак сигнала на выходе элемента РАВНОЗНАЧНОСТЬ 9 соответствует знаку произведения сигналов с выходов первого релейного элемента 5 и D-триггера 8. Каскад, образованный первым сумматором 1, первым интегратором 3 и первым релейным элементом 5, представляет собой первый автоколебательньй каскад с частотно-широтно-импульсной модуляцией и предназначен для преобразования первого сигналасомножителя. Амплитуда выходного сигнала первого интегратора 3 нормируется величиной порогов переключения первого релейного элемента 5, а производная и период следования зависят от уровня первого сигнала-сомножителя (фиг. 2а). Первый автоколебательный каскад является ведущим по отношению к второму автоколебательному каскаду, образованному вторым сумматором 2, интегратором А и релейным элементом 6, и осуществляющим преобразование второго сигналасомножителя. Синхронно с задним фронтом выходных импульсов первого релейного элемента 5 (фиг. 2а) на выходе формирователя 7 формируются импульсы малой длительности (фиг. 2), с помощью которых подается сигнал, разрешающий D-триггеру 8 переключаться в противоположное состояние. До момента времени t наличие тактовых имцульсов на выходе формиров ателя 7 импульса малой длительности не приводит к переключению Dтриггера 8, так как он и второй релейный элемент 6 находятся в одинаковых состояниях - А (фиг. 2В,Ь,1, 3, ,). В момент времени t, второй релейный элемент 6 переключается в состояние +А выходным сигналом второго интегратора 4 (фиг. 28,г), подготавливая тем самым переход Птриггера 8 в аналогичное состояние +А. В момент времени t (фиг. 2&) на выходе формирователя 7 импульса малой длительности формируется очередной тактовый импульс и выходной сигнал D-триггера 8 (фиг, 2) становится положительным. 3 в дальнейшем процесс повторяется. Сначала под действием сигнала развертки с выхода второго интегратора 4 происходит переключение второго релейного элемента 6, а затем с появ лением очередного тактового импульса с выхода формирователя 7 импульса малой длительности происходит срабатьшание D-триггера 8 и он переключается в состояние, аналогичное состоянию второго релейного элемента 6 (фиг. 2S -). Производная выходного сигнала второго интегратора 4 и период импульсов на выходе D-триггера 8 определяются уровнем второго сигнала сомножителя, В итоге на выходах первого релейного элемента 5 и D-триггера 8 формируются потоки импульсов со случайными друг относительно дру га частотами следования. При этом постЪянная составляющая импульсов на выходе элемента РАВНОЗНАЧНОСТЬ 9 (фиг. 2е) пропорциональна произведе ниш первого.и второго сигналов-со- множителей. В перекнокителе повышена точность работы за счет исключения источника импульсных помех, которым является ключевой элемент, входящий в состав блока синхронизации, а также за счет того, что второй автоколебательный каскад непрерьгано находится под воздействием управляющего сигнала, что 024 снижает влияние на него внешних помех. Формула изобретения Перемножитель, содержащий соединенные последовательно источник первого сигнала-сомножителя, первый . сумматор, первый интегратор, первый релейный элемент, выход которого соединен с вторым входом первого сумматора, с входом формирователя импульса ;малой длительности и с первым входом элемента РАВНОЗНАЧНОСТЬ, выход которого является выходом перемножителя, соединенные последовательно источник второго сигнала-сомножителя и второй сумматор, выход которого подключен к входу второго интегратора, второй релейный элемент, отличающийся тем, что, с целью повышения точности, в него введен D-триггер, информационный вход которого соединен с выходом второго релейного элемента, выход формирователя импульса малой длительности подключен к тактовому входуD-триггера, выход которого соединен с вторым входом элемента РАВНОЗНАЧНОСТЬ и с вторым входом второго сумматора , выход второго интегратора подключен к входу второго релейного эле мента.

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительное устройство | 1981 |

|

SU955104A1 |

| Множительное устройство | 1979 |

|

SU822204A1 |

| Аналоговый перемножитель | 1984 |

|

SU1166143A1 |

| Перемножающее устройство | 1983 |

|

SU1151995A2 |

| Устройство для определения модуля | 1982 |

|

SU1109763A1 |

| Квадратор | 1984 |

|

SU1188761A1 |

| ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО СИНХРОНИЗАЦИИ | 2009 |

|

RU2422974C1 |

| Время-импульсное множительное устройство | 1977 |

|

SU693391A1 |

| Множительное устройство | 1983 |

|

SU1120359A1 |

| Устройство для импульсно-фазового управления преобразователем | 1985 |

|

SU1257785A1 |

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повышение точности работы. Перемножитель содержит первый и второй сумматоры, первый и второй интеграторы, первый и второй релейные элементы, формирователь импульсов малой длительности,D-триггеру элемент РАВНОЗНАЧНОСТЬ. Точность работы повьшзена за счет исключения внутренних источников импульсных помех, а также за счет того, что ведомый автоколебательный каскад, образованный вторым сут-с атором, втоi рым интегратором, вторьм релейньм элементом иD-триггером, находится (Л под воздействием управляющего сигнапа, что снижает влияние на него внешних помех. 2 ил.

| Смолов В,Б | |||

| и др | |||

| Вычислительные машины непрерывного действия | |||

| М.: Высшая школа, 1964, с | |||

| Перепускной клапан для паровозов | 1922 |

|

SU327A1 |

| Железобетонный фасонный камень для кладки стен | 1920 |

|

SU45A1 |

| Множительное устройство | 1975 |

|

SU547782A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-23—Публикация

1985-03-04—Подача