ю

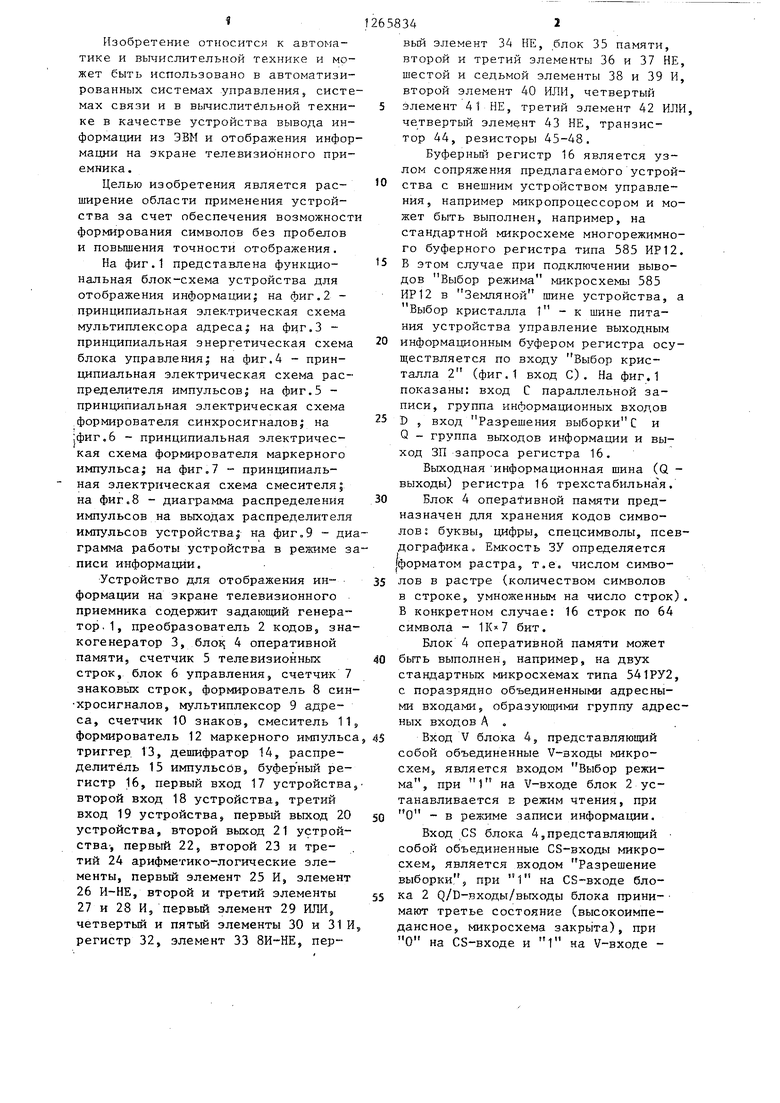

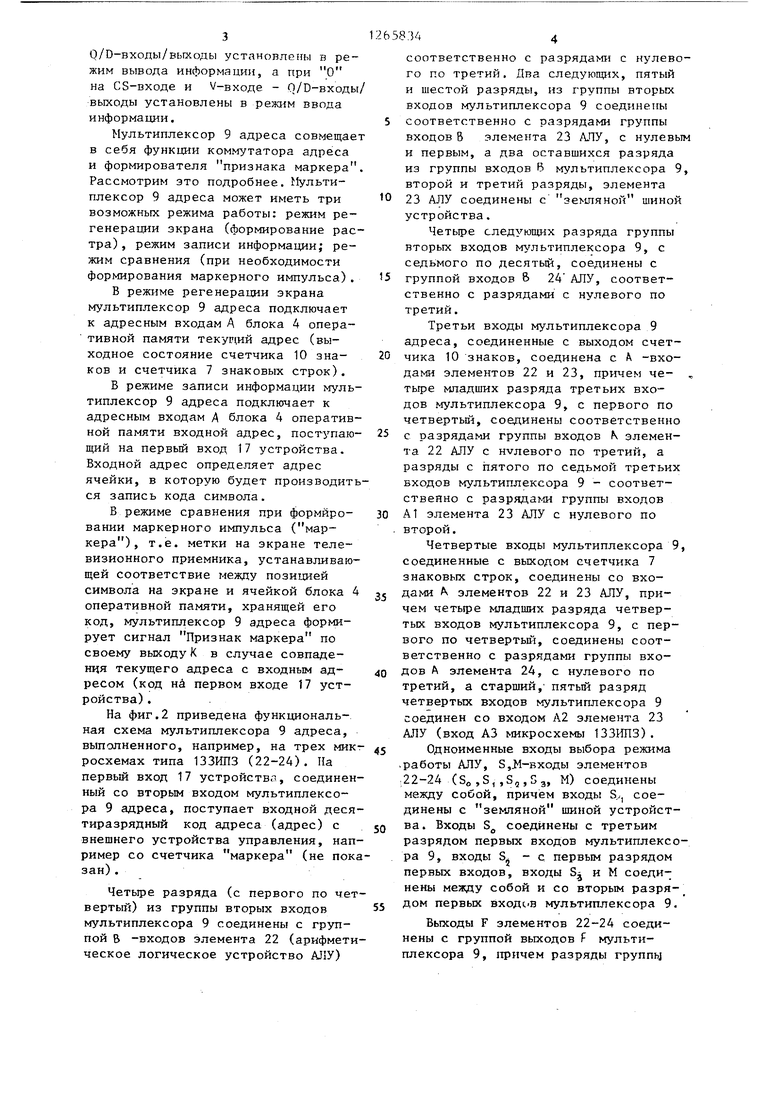

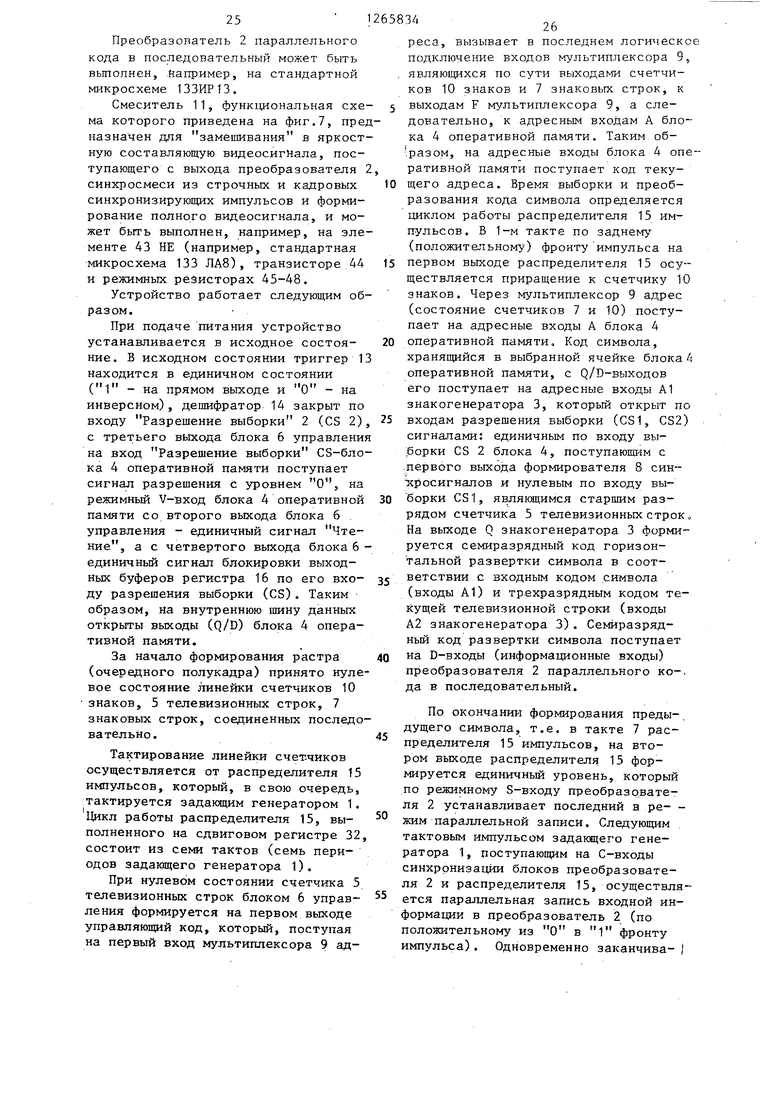

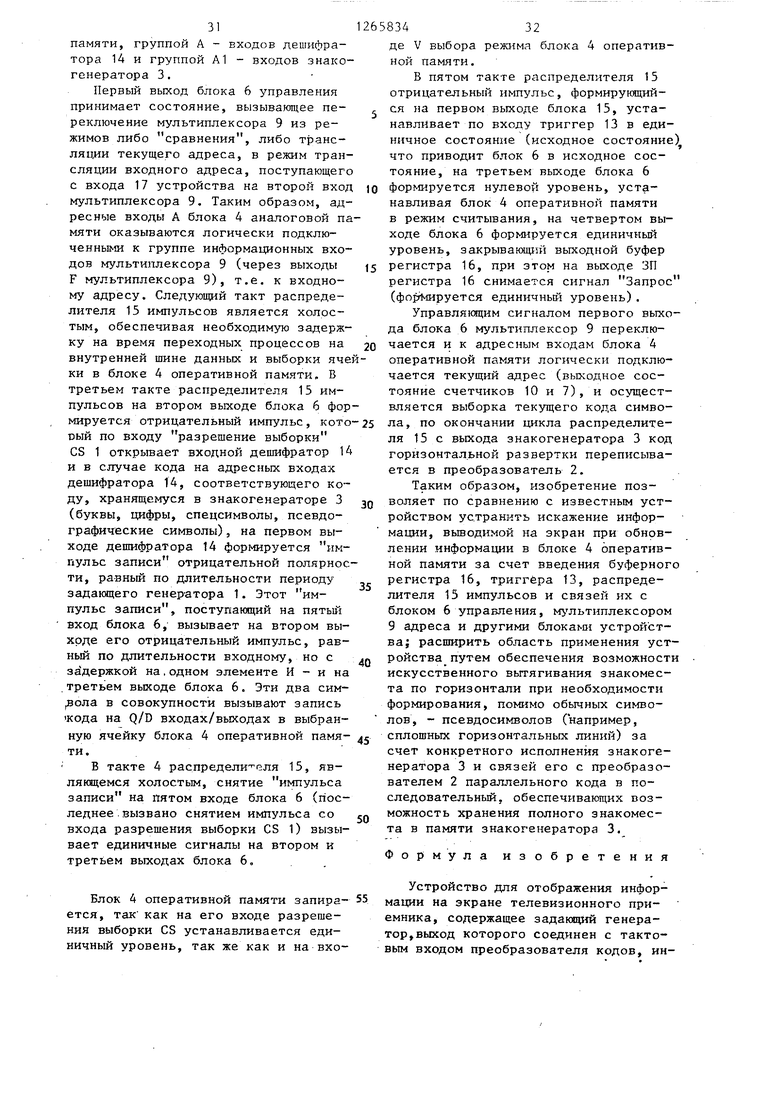

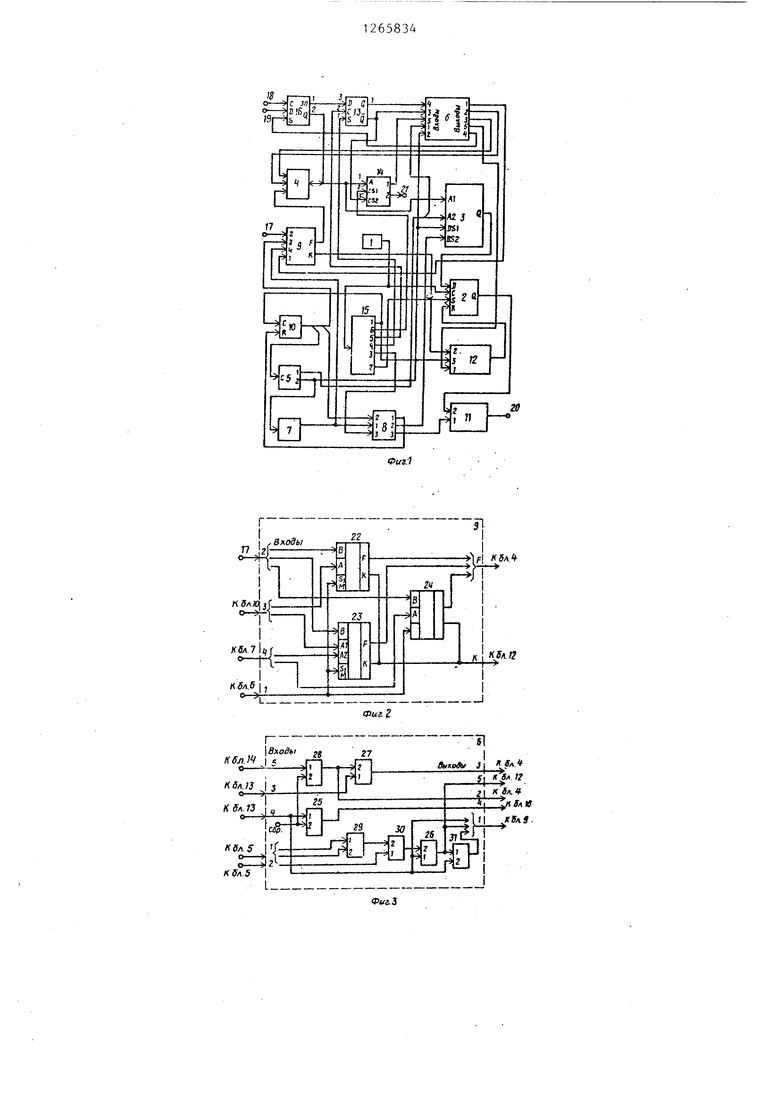

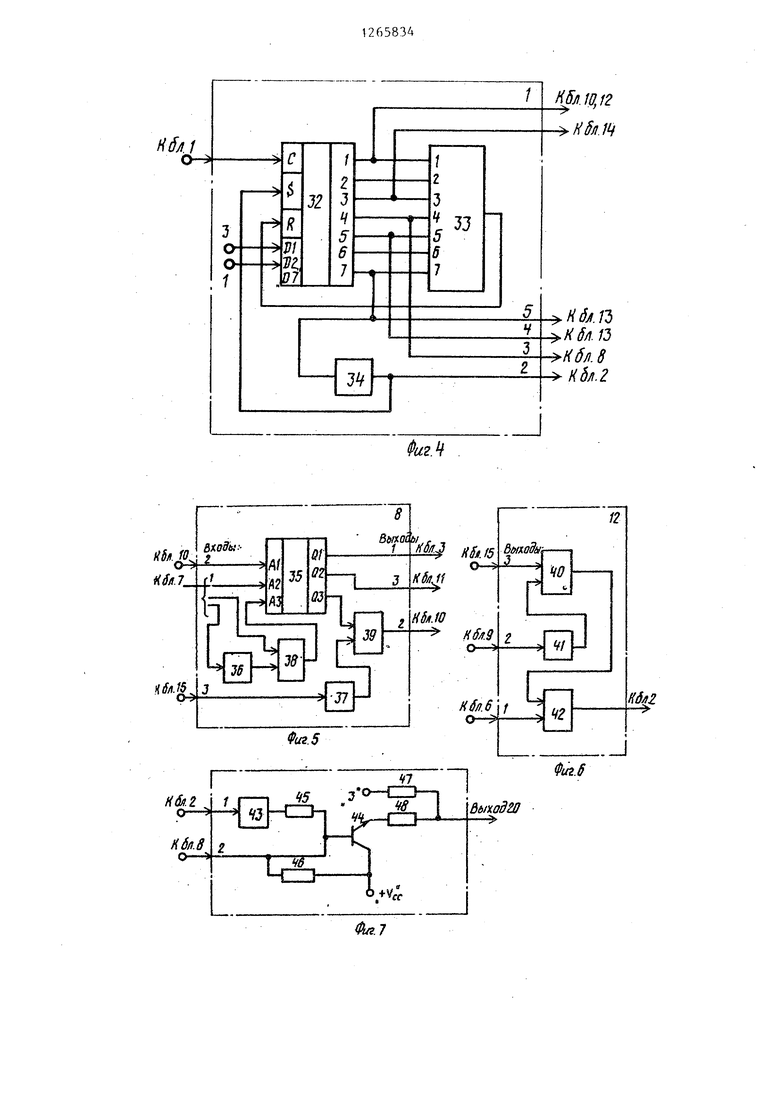

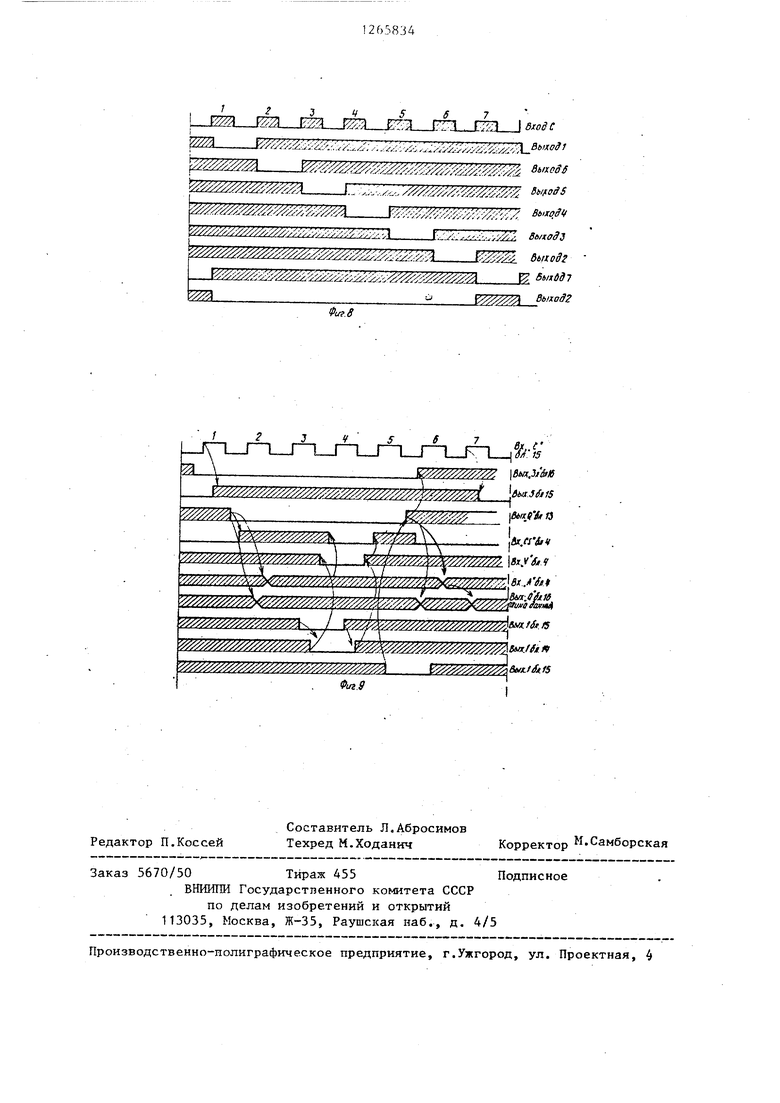

о ел Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматизированных системах управления, систе мах связи и в вычислительной технике в качестве устройства вывода информации из ЭВМ и отображения инфор мации на Экране телевизионного приемника . Целью изобретения является расширение области применения устройства за счет обеспечения возможност формирования символов без пробелов и повышения точности отображения. На фиг.1 представлена функциональная блок-схема устройства для отображения информации; на фиг.2 принципиальная электрическая схема мультиплексора адреса| на фцг.З принципиальная энергетическая схема блока управленияj на фиг,4 - принципиальная электрическая схема распределителя импульсов; на фиг,5 принципиальная электрическая схема формирователя синхросигналов; на ;фиг.6 - принципиальная электрическая схема формирователя маркерного импульса; на фиг,7 - принципиальная электрическая схема смесителя; на фиг.8 - диаграмма распределения импульсов на выходах распределителя импульсов устройства; на фиг,9 - ди грамма работы устройства в режиме з писи информации. Устройство для отображения информации на экране телевизионного приемника содержит задаюш 1й генератор,, преобразователь 2 кодов, зна когенератор 3, блок 4 оперативной памяти, счетчик 5 телевизионных строк, блок 6 управления, счетчик 7 знаковых строк, формирователь 8 син хросигналов, мультиплексор 9 адреса, счетчик 10 знаков, смеситель 11 формирователь 12 маркерного импульс триггер 13, дешифратор 14, распределитель 15 импульсов, буферный регистр 16, первый вход 17 устройства второй вход 18 устройства, третий вход 19 устройства, первый выход 20 устройства, второй выход 21 устройства, первый 22, второй 23 и третий 24 арифметико-логические элементы, первый элемент 25 И, элемент 26И-НЕ, второй и третий элементы 27и 28 И, первый элемент 29 ИЛИ, четвертый и пятый элементы 30 и 31 И регистр 32, элемент 33 8И-НЕ, пер342вый элемент 34 НЕ, блок 33 памяти, второй и третий элементы 36 и 37 НЕ, шестой и седьмой элементы 38 и 39 И, второй элемент 40 ИЛИ, четвертый элемент 41 НЕ, третий элемент 42 ИЛИ, четвертый элемент 43 НЕ, транзистор 44, резисторы 45-48. Буферньд регистр 16 является узлом сопряжения предлагаемого устройства с внешним устройством управления, например микропроцессором и может быть выполнен, например, на стандартной микросхеме многорежимного буферного регистра типа 585 ИР 12. В этом случае при подключении выводов Выбор режима микросхемы 585 ИР 12 в Земляной шине устройства, а Выбор кристалла 1 - к шине питания устройства управление выходным информационным буфером регистра осуществляется по входу Выбор кристалла 2 (фиг,1 вход С), На фиг,1 показаны; вход С параллельной записи, группа информационных входов D , вход Разрешения выборки С и Q - группа выходов информации и выход ЗП запроса регистра 16, Выходная информационная шина (Q выходы) регистра 16 трехстабильная. Блок 4 оперативной памяти предназначен для хранения кодов символов: буквы, цифры, спецсимволы, псевдографика. Емкость ЗУ определяется форматом растра, т,е. числом символов в растре (количеством символов в строке, умноженным на число строк). В конкретном 16 строк по 64 символа - 1.-7 бит. Блок 4 оперативной памяти может быть выполнен, например, на двух стандартных микросхемах типа 541РУ2, с поразрядно объединенными адресными входами, образующими группу адресных входов А Вход V блока 4, представляюшдй собой объединенные V-входы микросхем, является входом Выбор режима, при 1 на V-входе блок 2 устанавливается в режим чтения, при О - в режиме записи информации. Вход CS блока 4,представляющий собой объединенные CS-входы микросхем, является входом Разрешение выборки, при 1 на CS-входе блока 2 Q/D-входы/выходы блока прини- мают третье состояние (высокоимпедансное, микросхема закрыта), при О на CS-входе и 1 на V-входе 3O/D-входы/выходы установлены в режим вывода информации, а при О на CS-входе и V-входе - Q/D-входы выходы установлены в режим ввода информации. Мультиплексор 9 адреса совмещае в себя функции коммутатора адреса и формирователя признака маркера Рассмотрим это подробнее. Мультиплексор 9 адреса может иметь три возможных режима работы: режим регенерации экрана (формирование рас тра) , режим записи информации; режим сравнения (при необходимости формирования маркерного импульса). В режиме регенерации экрана мультиплексор 9 адреса подключает к адресным входам А блока 4 оперативной памяти текущий адрес (выходное состояние счетчика 10 знаков и счетчика 7 знаковых строк). В режиме записи информации муль типлексор 9 адреса подключает к адресным входам А блока 4 оператив ной памяти входной адрес, поступаю щий на первый вход 17 устройства. Входной адрес определяет адрес ячейки, в которую будет производит ся запись кода символа. В режиме сравнения при формировании маркерного импульса (маркера), т.е. метки на экране телевизионного приемника, устанавливаю щей соответствие между позицией символа на экране и ячейкой блока оперативной памяти, хранящей его код, мультиплексор 9 адреса формирует сигнал Признак маркера по своему выходу К в случае совпадения текущего адреса с входным адресом (код ни первом входе 17 устройства) . На фиг.2 приведена функциональная схема мультиплексора 9 адреса, выполненного, например, на трех мик росхемах типа 133ИПЗ (22-24). Па первый вход 17 устройства, соедине ный со вторым входом мультиплексора 9 адреса, поступает входной деся тиразрядный код адреса (адрес) с внешнего устройства управления, нап ример со счетчика маркера (не пок зан) . Четыре разряда (с первого по че вертый) из группы вторых входов мультиплексора 9 соединены с группой В -входов элемента 22 (арифмет ческое логическое устройство АЛУ) 344 соответственно с разрядами с нулевого по третий. Два следующих, пятый и шестой разряды, из группы вторых входов мультиплексора 9 соединены соответственно с разрядами группы входов В элемента 23 ЛЛУ, с нулевым и первым, а два оставшихся разряда из группы входов В мультиплексора 9, второй и третий разряды, элемента 23 АЛУ соединены с земляной шиной устройства. Четьфе следуюшлх разряда группы вторых входов мультиплексора 9, с седьмого по десятый, соединены с группой входов & 24 АЛУ, соответственно с разрядами с нулевого по третий. Третьи входы мультиплексора 9 адреса, соединенные с выходом счетчика 10 знаков, соединена с Л -входами элементов 22 и 23, причем че- , тыре младших разряда третьих входов мультиплексора 9, с первого по четвертьш, соединены соответственно с разрядами группы входов N элемента 22 АЛУ с нvлeвoгo по третий, а разряды с пятого по седьмой третьих входов мультиплексора 9 - соответственно с разрядами группы входов А1 элемента 23 АЛУ с нулевого по второй. Четвертые входы мультиплексора 9, соединенные с выходом счетчика 7 знаковых строк, соединены со входами Л элементов 22 и 23 АЛУ, причем четьфе младших разряда четвертых входов мультиплексора 9, с первого по четвертьш, соединены соответственно с разрядами группы вхоДОН А элемента 24, с нулевого по третий, а старший, пятый разряд четвертых входов мультиплексора 9 соединен со входом А2 элемента 23 АЛУ (вход A3 микросхемы 133ИПЗ). Одноименные входы выбора режима .работы АЛУ, S,1-входы элементов :22-24 (So,S,,S,,,S3, М) соединены между собой, причём входы S,., соединены с земляной шиной устройстна. Входы S соединены с третьим разрядом первых входов мультиплексора 9, входы Sj - с первым разрядом первых входов, входы Sj и М соединены между собой и со вторым разря- дом первых входс-в мультиплексора 9. Выходы F элементов 22-24 соединены с группой выходов F мультиплексора 9, причем разряды группь

5

выходов f с первого по четвертый

мультиплексора 9 соединены соответственно с разрядами группы выходов элементов 22 с нулевого по третий, а пятый и шестой разряды группы выходов F мультиплексора 9 соединены с разрядами группы выходов F элементов 24 с нулевого по третий.

Выходы К (равно) элементов 22-24 соединены между собой и являются вторым выходом мультиплексора 9.

В режиме регенерации экрана на первые входы мультиплексора 9 с блока 6 управления поступает код режима А (1 - во всех трех разрядах первых входов мультиплексора 9), При этом на выходы F всех элементов 22-24 мультиплексора 9 транслируется состояние А входов, т.е. код текущего адреса (состояние выходов счетчиков 7 и 10),

В режиме записи информации на первые входы мультиплексора 9 поступает код режима 6 (в первом разряде - О, во втором - 1, а третьем - О) и на выходы F элементов 22-24 транслируется состояние 6 -входов микросхем - входной адрес устройства (на первый вход 17 устройства) .

При поступлении на первые входы мультиплексора 9 кода Сравнение (1-й разряд - 1, 2-й - О, 3-й ) от блока 6 управления элементами 22-24 сравниваются коды на входах А и В ив случае цх совпадения во всех разрядах на втором выходе мультиплексора 9 формируется сигнал Признак маркера уровнем логической 1.

При наличии сигналов уровня логической 1 в одном из старших разрядов второй или третьей группы входных сигналов, т.е. седьмого разряда во второй или пятого разряда в третьей (разряды А2, A3 микросхемы 23), на выходе К элемента 23, а соответственно и на втором выходе К мультиплексора 9 формируется сигнал с уровнем логического О (нет Признака маркера), что обусловлено несовпадением кодов, так как соответствующие Б-входы элемента 23 подсоединены к земляной шине. Таким образом, осуществляется запрет -фор мирования признака маркера в пассивных частях формируемого растра.

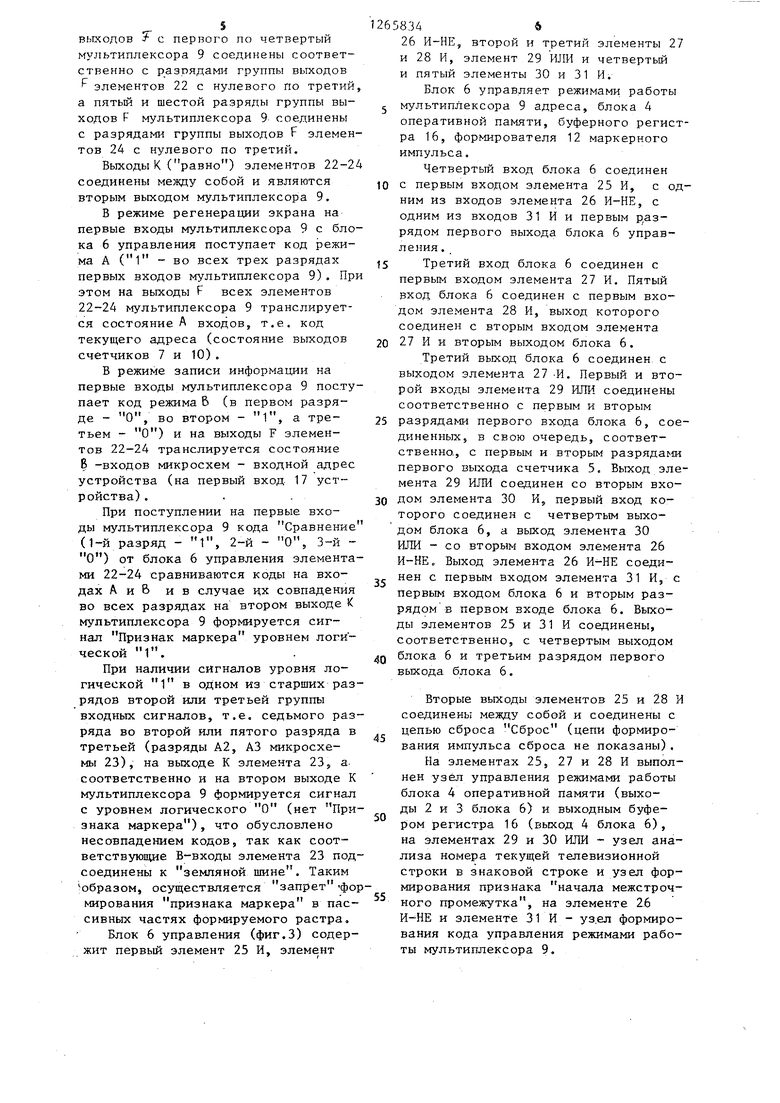

Блок 6 управления (фиг.З) содержит первый элемент 25 И, элемент

265834&

26 И-НЕ, второй и третий элементы 27 и 28 И, элемент 29 ИЛИ и четвертый и пятый элементы 30 и 31 И.

Блок 6 управляет режимами работы 5 мультиплексора 9 адреса, блока 4

оперативной памяти, буферного регистра 16, формирователя 12 маркерного импульса.

Четвертый вход блока 6 соединен

10 с первым входом элемента 25 И, с одним из входов элемента 26 И-НЕ, с одним из входов 31 И и первым разрядом первого выхода блока 6 управления .

15 Третий вход блока 6 соединен с первым входом элемента 27 И. Пятый вход блока 6 соединен с первым входом элемента 28 И, выход которого соединен с вторым входом элемента

0 27 И и вторым выходом блока 6.

Третий выход блока 6 соединен, с выходом элемента 27 -И. Первый и второй входы элемента 29 ИЛИ соединены соответственно с первым и вторым

5 разрядами первого входа блока 6, соединенных, в свою очередь, соответственно., с первым и вторым разрядами первого выхода счетчика 5. Выход элемента 29 ИЛИ соединен со вторым вхо0 дом элемента 30 И, первый вход которого соединен с четвертым выходом блока 6, а выход элемента 30 ИЛИ - со вторым входом элемента 26 И-НЕ. Выход элемента 26 И-НЕ соеди, нен с первым входом элемента 31 И, с первым входом блока 6 и вторым разрядом в первом входе блока 6. Выходы элементов 25 и 31 И соединены, соответственно, с четвертым выходом

Q блока 6 и третьим разрядом первого выхода блока 6.

Вторые выходы элементов 25 и 28 И соединены между собой и соединены с цепью сброса Сброс (цепи формирования импульса сброса не показаны).

На элементах 25, 27 и 28 И выполнен узел управления режимами работы блока 4 оперативной памяти (выходы 2 и 3 блока 6) и выходным буфеpioM регистра 16 (выход 4 блока 6), на элементах 29 и 30 ИЛИ - узел анализа номера текущей телевизионной строки в знаковой строке и узел формирования признака начала межстрочного промежутка, на элементе 26 И-НЕ и элементе 31 И - уз.ел формирования кода управления режимами работы мультиплексора 9. В режиме регенера1Ц1и экрана (сканирования ЗУ) на четвертом и пятом (Входах блока бив цепи сброса Сбор сформированы сигналы логической 1, а на входе 2 при этом с уровнем логического О. На втором и четвертом выходах- блока 6, соединенных соответственно с выходами элементов 28 и 23 И, формируются уровни логической 1, так как на первом и втором входах этих элементов присутствуют логическая 1. На третьем выходе блока 6 будет сигнал с уровнем логи 0ческого , вызванный нулевым уровнем на первом входе элемента 27 И (с третьего входа блока 6). Такое состояние этих трех выходов определяет: логическая 1 на третьем выходе блока ,6 - режим считывания из блока 4 оперативной памяти; логическая 1 на четвертом выходе блока 6 - блокировку буферного регистра 16,- логический О на третьем выходе блока 6 - разрешение выборки блока 4 оперативной памяти. Состояние первого и пятого выхода блока 6 определяется в режиме регенерации экрана состоянием первых и вторых входов блока 6. При состоянии логический О на втором входе блока 6 (старший разряд счетчика 5, фиг,1) независимо от состояния 1-го и 2-го разрядов первого входа блока 6, на выходе элемента 30 И формируется уровень логического О, обус ловленный уровнем логического О на первом его входе. Сигнал с уровнем ло гического О на третьем входе элемента 26 И-НЕ вызывает формирование на его выходе уровня логической 1 На выходе элемента 31 И также формируется логическая 1, так как на первом и втором его входах - уровни логической 1, Таким образом, на всех разрядах первого выхода блока 6 управления сформированы логическая 1, что соответствует коду режима А, мультиплексора 9, а логическая 1 на пятом выходе блока 6 является сиг налом запрета формирования маркерноге импульса. При состоянии второго входа блока 6 и первог и второго разрядов четвертого входа блока 6 выходы блока 6 свое состояни не меняют, так как из-за наличия логического О на первом и втором входах элемента 29 ИЛИ на его выходе формируется уровень логического О, 34 которьш возбуждая элемент 30 И по второму входу, вызывает на его выходе формирование сигнала с уровнем логического О. Описанное состояние блока 6 характеризует режим регенерации экрана в течение 9 телевизионных строк (с 0-й по 8-ю). При появлении логической 1 на любом из разрядов первого входа блока 6 и наличии логической 1 на втором входе блока б на выходе элемента 30 И формируется уровень логической 1, так как единичное состояние любого из двух входов элемента 29 ИЛИ вызывает состояние логической 1 на его выходе, т.е. на втором входе элемента 30 И, а так как на первом его входе - уровень логической 1, то и выход его принимает состояние . Совпадение двух логических 1 на входе элемента 26 И-НЕ вызывает формирование на его выходе логичес,кого О, который, воздействуя по ;первому входу на элемент 31 И, вызы:вает на его выходе формирование уровня логического О. Таким образом, на питом выходе блока 6 сформирован уровень логического О, что является разрешением формирования маркерного импульса, а состояние, которое принимает первый вьгход блока 6, логическая 1 - в первом разряде и логический О - во втором и третьем, является кодом режима Сравнение . При переходе устройства в режим записи на четвертом входе блока 6 формируется уровень логического О, а на третьем входе его - уровень логической 1. Уровень логической 1 на третьем входе блока 6 вызывает формирование уровня логической 1 на выходе элемента 27 И и соответственно на третьем выходе блока 6, что является сигналом запирания блока 4 оперативной памяти. Логический О на четвертом входе блока 6 вызывает формирование О на выходе элемента 25 И и соответственно - на четвертом выходе блока 6, что является сигналом отпирания выходных буферов регистра 16. Логический О на первом входе элемента буферов регистра 16, логический О на первом входе элемента 26 И-НЕ и втором входе элемента 31 И вызывает формирование на их выходах совтветственно логической 1 и логического О, Это состояние не зависит от кодовой.комбинации на входах элемента 29 ИЛИ и элемента 30, так как элемент 26 И-НЕ удерживается в соетоянии логической 1 на выходе за счет логического О на первом входе. Таким образом, на пятом выходе блоа 6 сформирован сигнал уровнем логической 1 - запрет формирования Ю маркера, а состояние первого выхода блока 6 (разряд 1-й - логический О, азряд 2-й - логическая 1 и .разряд 3-й - логический О) соответствует оду В режима мультиплексора 9, 15

При поступлении сигнала уровнем огического О на пятый вход блоа 6 на выходе элемента 28 И и втором выходе блока 6 формируется уроень логического О, а с задерж- 20 ой на элементе 27 И и на третьем ыходе блока 6, что соответствует одаче сигналов, - соответственно Запись и Разрешение выборки на блок 4 оперативной памяти,25

Триггер 13 предназначен для осуществления временной привязки цикла записи в блок 4 оперативной памяти в процессе ассинхронного обмена предлагаемого устройства с внешним управ- зо ляющим устройством к циклу регенерации экрана и может быть выполнен, например, на стандартной микросхеме 133 ТМ2.

Задаклдий генератор 1 вырабатывает последовательность импульсов, посту.пающих на С-входы распределителя 15 и преобразователя 2, осуществляющего преобразование параллельного |сода в последовательный. 4Q

Период следования импульсов задающего генератора 1 определяет длительность одной точки в формировании горизонтальной развертки символа. Задакяций генератор 1 может быть 45 вьтолнен, например, на двух элементах НЕ стандартной микросхемы 133 ЛИ1 с кварцевым резонатором в цепи обра;тной связи.

Частота задаквцего генератора 1 в конкретном случае 10 мГц.

Дешифратор 14 предназначен для анализа кода входного слова в режиме записи и может быть вьтолнен, например, на стандартной микросхеме 55 ПЗУ 556РТ5.

В случае соответствия входного кода на адресных входах дешифратора 14 группа входов А (фиг.1) коду символа (буква, цифры, псевдографические символы) и наличия сигналов Разрешение выборки (входы С 1 и С 2) на первом выходе дешифратора 1 формируется сигнал Запись с уровнем логического О. В случае соответствия входного кода коду комады управления (управление, например счетчиком маркера не показанным на фиг.1, позицией метки на экране сдвиг влево, вправо, вверх, вниз и т.д.) формируется одна из команд управления на втором выходе дешифратора 14.

Счетчик 10 знаков является счетчиком текущего адре.са горизонтальной развертки знаковой строки и своим выходным состоянием (кодовой комбинацией н.а выходе) определяет позицию символа на экране телевизионного приемника по горизонтали. Счетчик 10 может быть вьтолнен, например, на двух стандартных микросхемах типа 133ИЕ 7. На одной микросхеме 133ИЕ7 вьтолнен двоичный счетчикделитель на 16, соединенный своим выходом переноса (15) со счетчиком (+1) следукщего счетчика.

Входы сброса счетчиков (R-входы) соединены между собой и с вторым выходом формирователя 8 синхросигналов

Счетчик 5 телевизионных строк является счетчиком текущего адреса вертикальной развертки знаковой строки и своим выходным состоянием определяет номер текущей телевизионной строки в знаковой строке, и может быть вьтолнен, например, на стандартной микросхеме 133ИЕ5 (133ИЕ7).

В конкретном случае на микросхеме 133ИЕ5 реализован счетчик на 13 введением обратных связей с выходов счетчика. Вход установки в О (вход R) микросхем 133 ИЕ5 (ИЕ7) соединен с младшим разрядом 1 счетчика, а второй вход установки в О - 8 соединен с выходом элемента И, первый вход которого соединен с разрядом 8 счетчика (старший), а второй вход с разрядом 4 счетчика. Вход С2 микросхемы соединен с выходом 1, а вход С1 микросхемы является счетным входом счетчика 5.

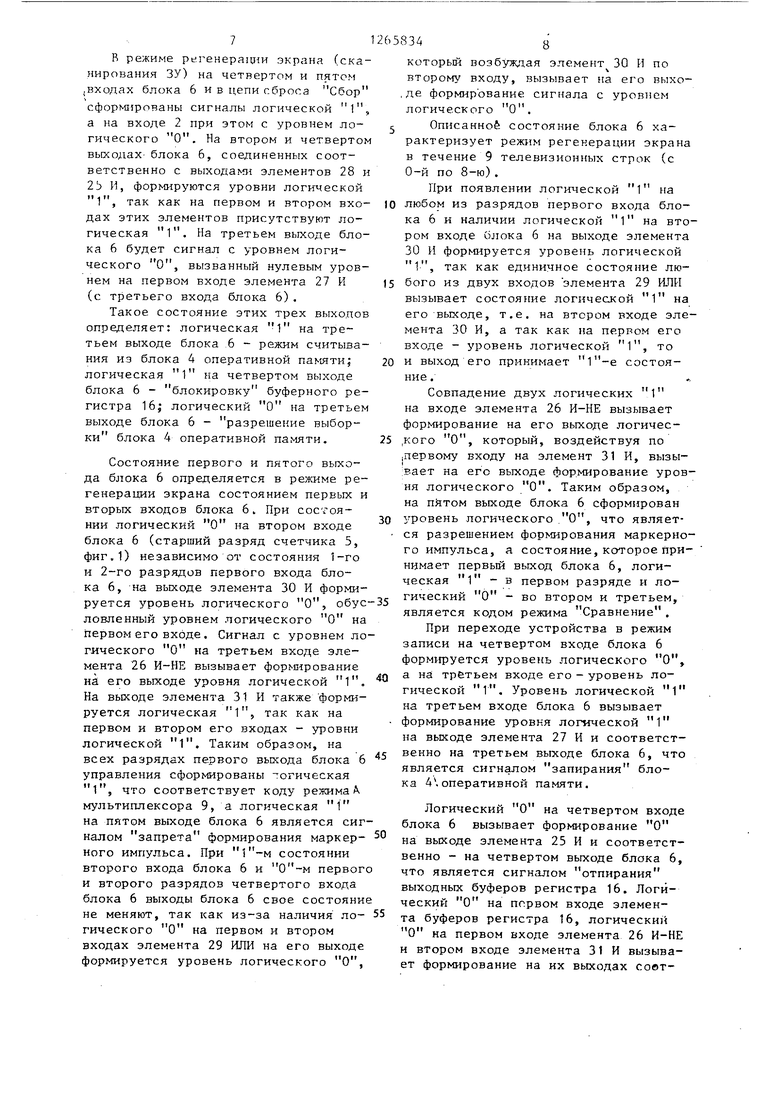

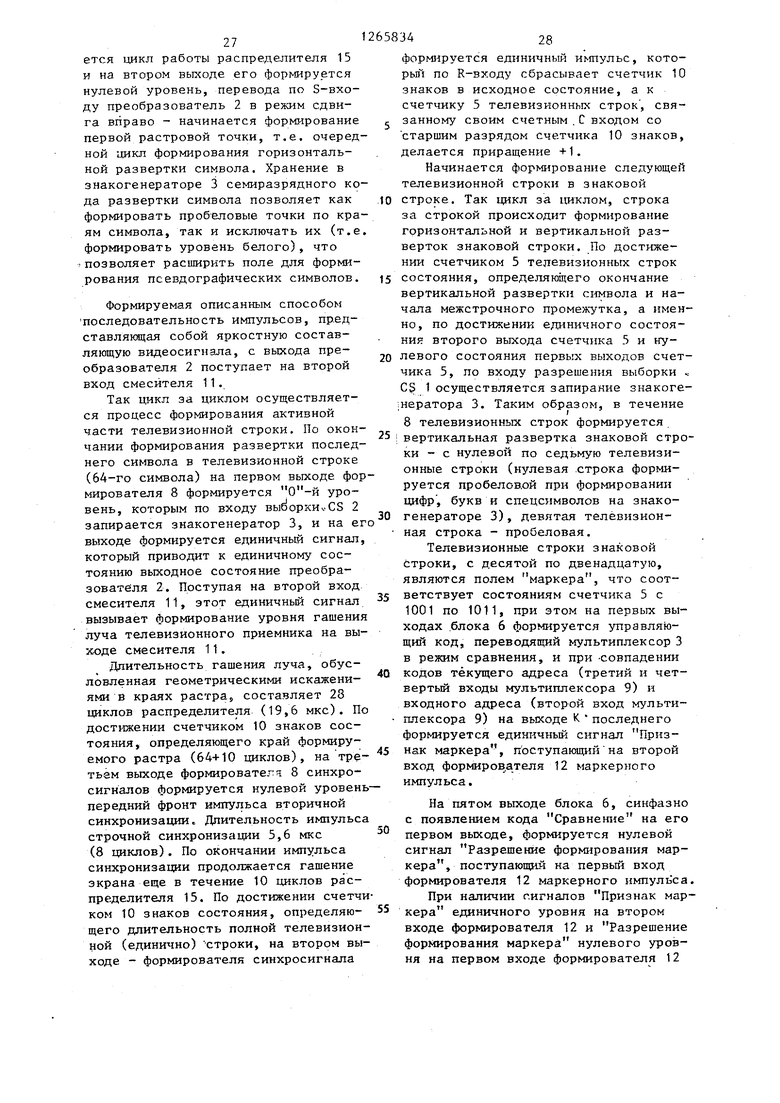

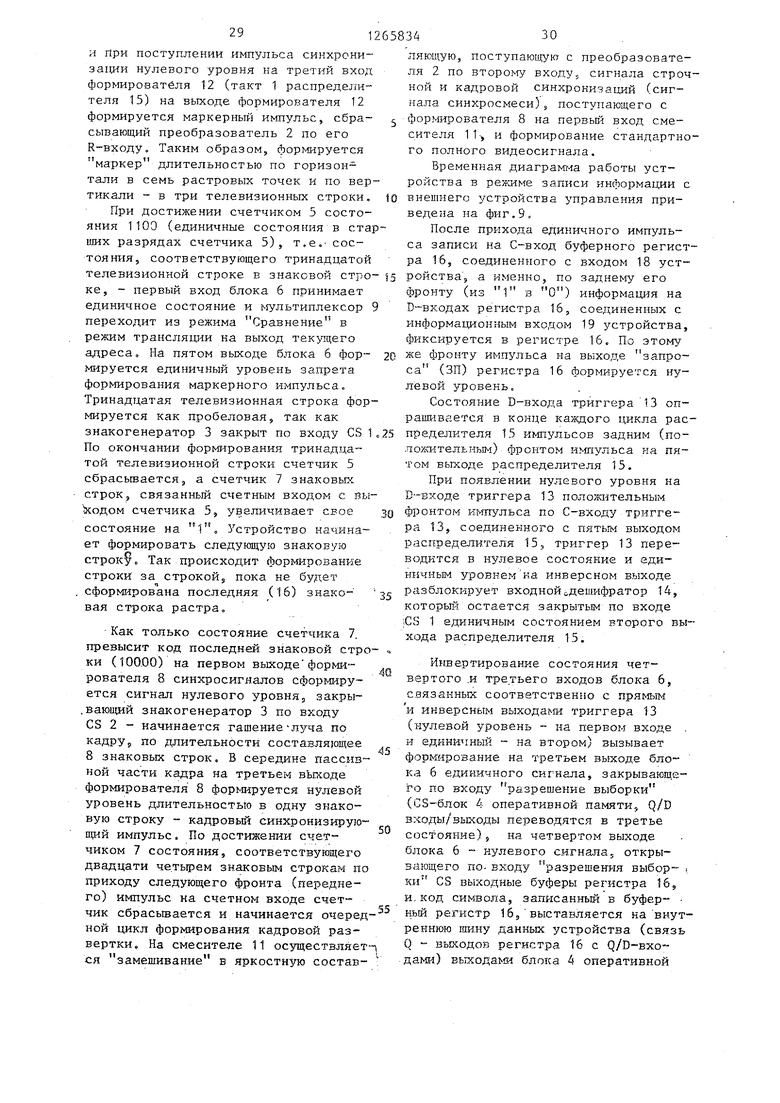

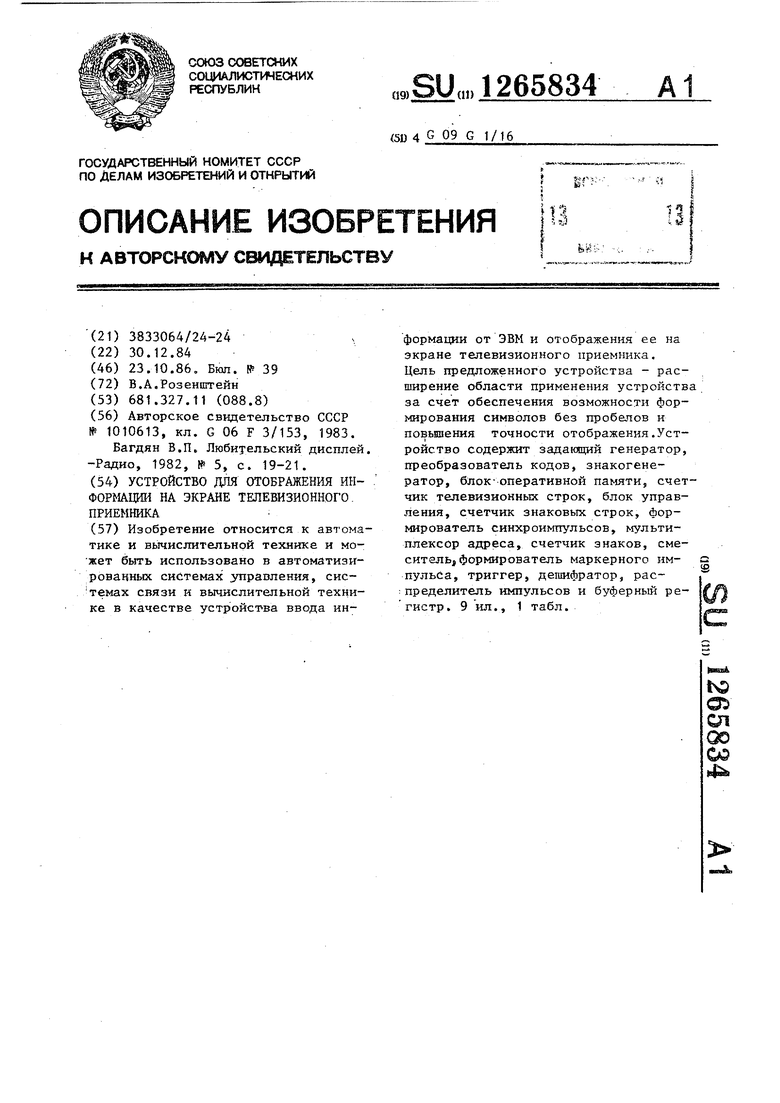

Счетчик 7 знаковых строк своим выходным состоянием определяет номер текущей знаковой строки и может быть реализован, например, на двух стандартных микросхемах 133 ИЕ5. Первая из них, соединенная fexoдом С1 (вход :t счетчика 7 знаковых строк, фиг.1) с выходом счетчика 5 телевизионных строк используется ка счетчик-делитель на 2, а вторая росхема, соединенная входом С1 с вы ходом 1 первой микросхемы - как счетчик-делитель на 12, что достигается введением обратных связей с двух старших разрядов выхода микросхемы на входы установки в О и соединением счетного входа С2 микросхемы с выходом разряда 1 этой же микросхемы (вторая половина первой микросхемы используется как делитель на четыре для формирования импульсов частотой следования 12,5 Г используемых в устройстве, например для реализации режима повтора - н показано). Распределитель 15 импульсов, так тируемый задающим генератором 1, осуществляет общую синхронизацию всех узлов и блоков устройства. На фиг.4 приведена функциональная схема распределителя 15, выполненного на сдвиговом регистре 32, в качестве которого может быть использ-ована например, стандартная микросхема ти па 133 ИР 13 на элементах 33 8И-НЕ и 34 НЕ, в качестве которых могут быть использованы, например, стан|Дартные микросхемы 133ЛА2 и 133ЛН1 соответственно. Ин(5ормационный Dl-вход регистра Подключен к земляной шине устройс.тва 3 (фиг.4), а остальные информа ционные D-входы и не показанные на схеме: вход режима и информацион ные последовательные входы D и D подключены к логической 1 устройс ва (1, фиг,4). Цикл работы регистра 32 начинает ся с режима параллельной записи, т,е, когда на выходе 7 г гистра 32 сформируется уровень логического О уровень логического О на входе злемента 34 НЕ, соединенного с выходом регистра 32, вызывает на его выходе АорШрование сигнала уровнем логической 1, который по ,входу S управления режимом регистра 32 (физически вход S конкретной микросхемы 133ИР13) устанавливает регистр 32 в параллельной записи. Следующим тактовым импульсом .на С-входе, связанным с С-входок распределителя 15 импульсов, а именно его положительным фронтом информавди с D-входов распределителя, переписывается в регистр. Таким образом, на выходе 1 регистра 32 формируется логический О, а на остальных шести - логическая Г. Сигнал уровнем логической 1 на 7-м выходе регистра 32 вызывает формирование логического О на выходе 34 НЕ, которьш, в свою очередь, по Sвходу регистра 32 переводит последний в режим сдвига вправо. Временная диаграмма работы регистра 32 (распределителя 15) приведена на фиг.8. Длительность цикла работы распределителя, представляющая собой семь тактов (семь периодов) задающего генератора 1, определяет длительность горизонтальной развертки символа. В такте Т1 импульс отрицательной полярности (перепад из 1 в О) формируется на выходе регистра 32 и соответственно распределителя 15 импульсов.. Б такте ТЗ (такт Т2 - холостой) импульс формируется на втором выходе распределителя, Т4 на третьем выходе, Т5 - на четвертом выходе. В такте Т7 (такт Т6 - холостой) импульс отрицательной полярности появляется на пятом выходе распределителя 15, а импульс положительной полярности - на втором выходе распределителя 15, равный по длительности импульсу на пятом выходе. Импульсом на первом выходе распределиделя 15 осуществляется приращение к линейке счетчиков 5, 7, 10 и тактирование формирователя 12. Импульсом на втором выходе распределителя 15 осуществляется тактирование входного дешифратора 14. Импульсом на пятом выходе распределителя 15 осуществляется тактирование по С-входу триггера 13. Импульсом на четвертом выходе распределителя 15 осуществляется сброс по S-входу триггера 13. Импульсом на третьем выходе распределителя 15 осуществляется тактирование формирователя 8 синхросигналов. Импульсом на втором выходе распределителя 15 осуществляется управление режимом работы распределителя 2,

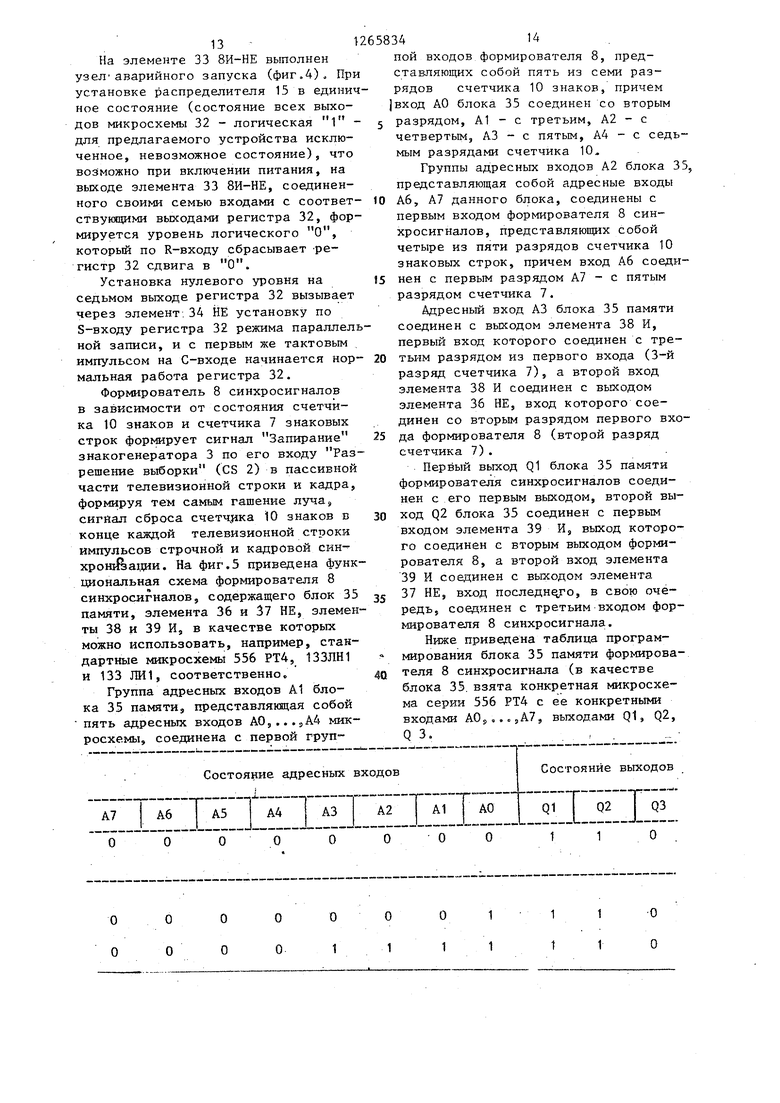

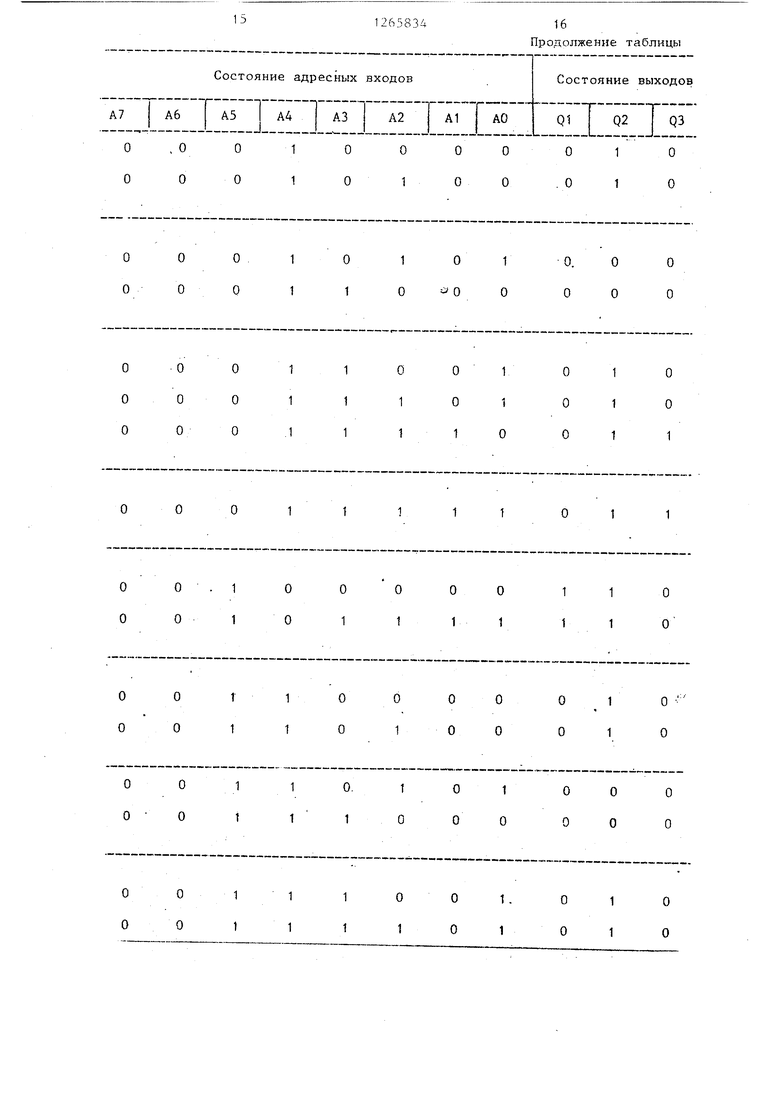

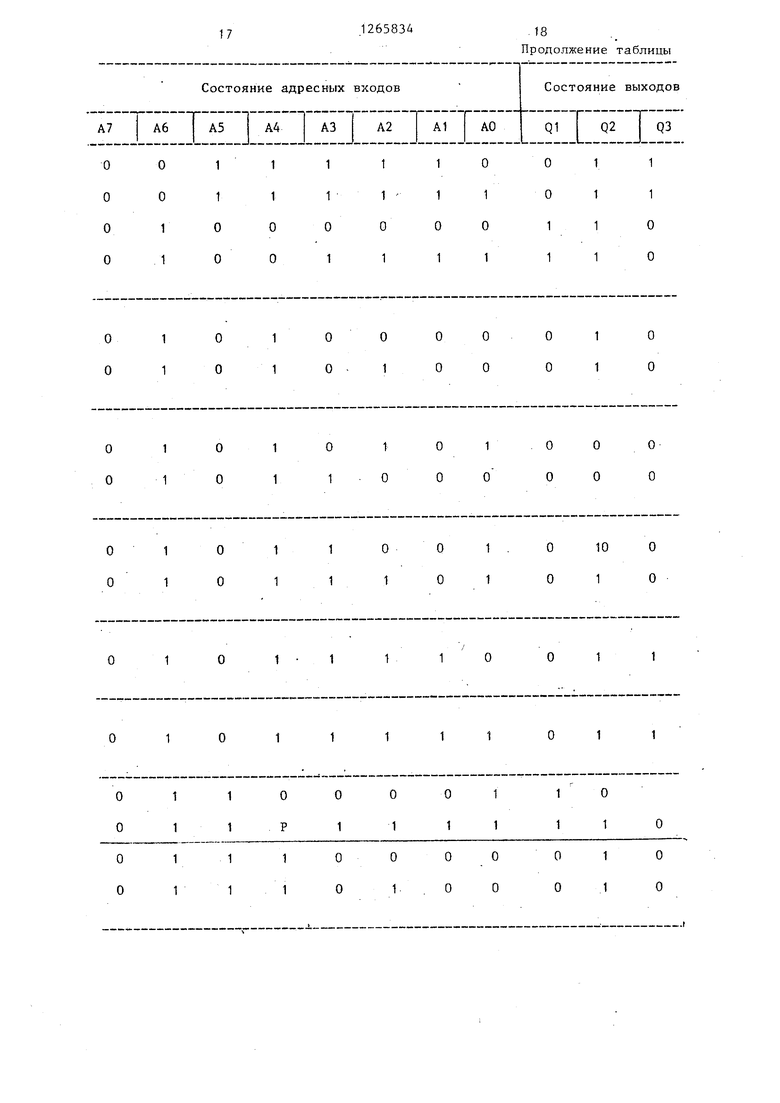

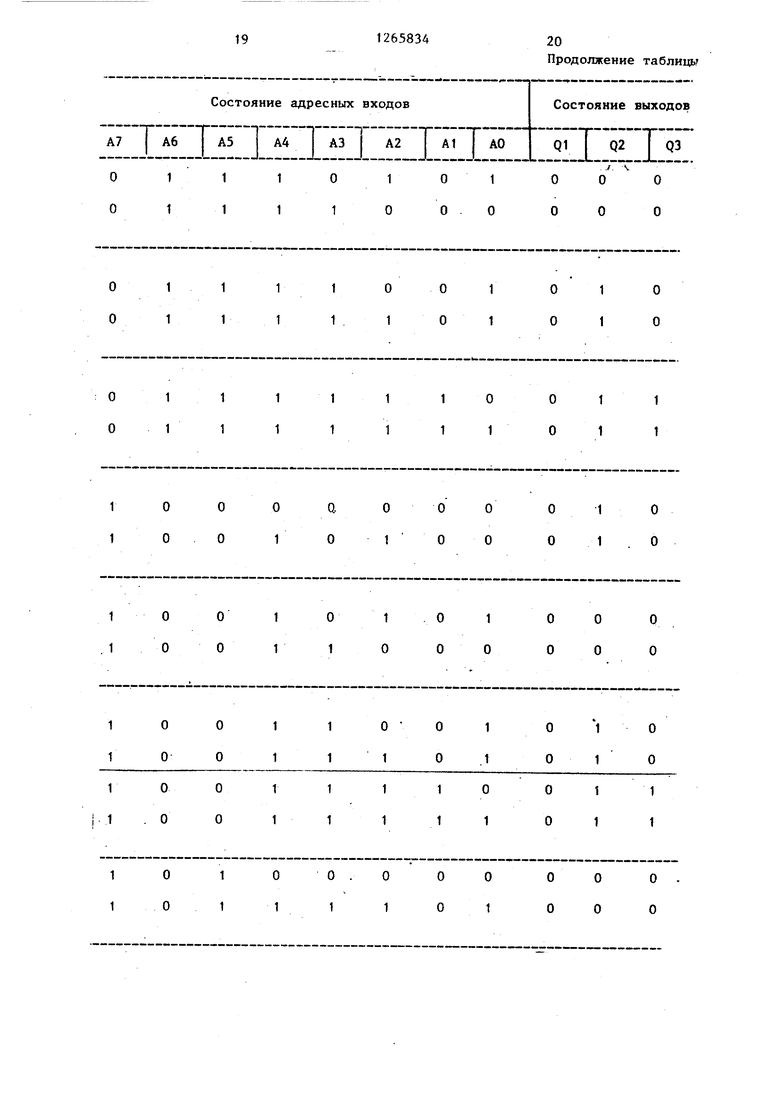

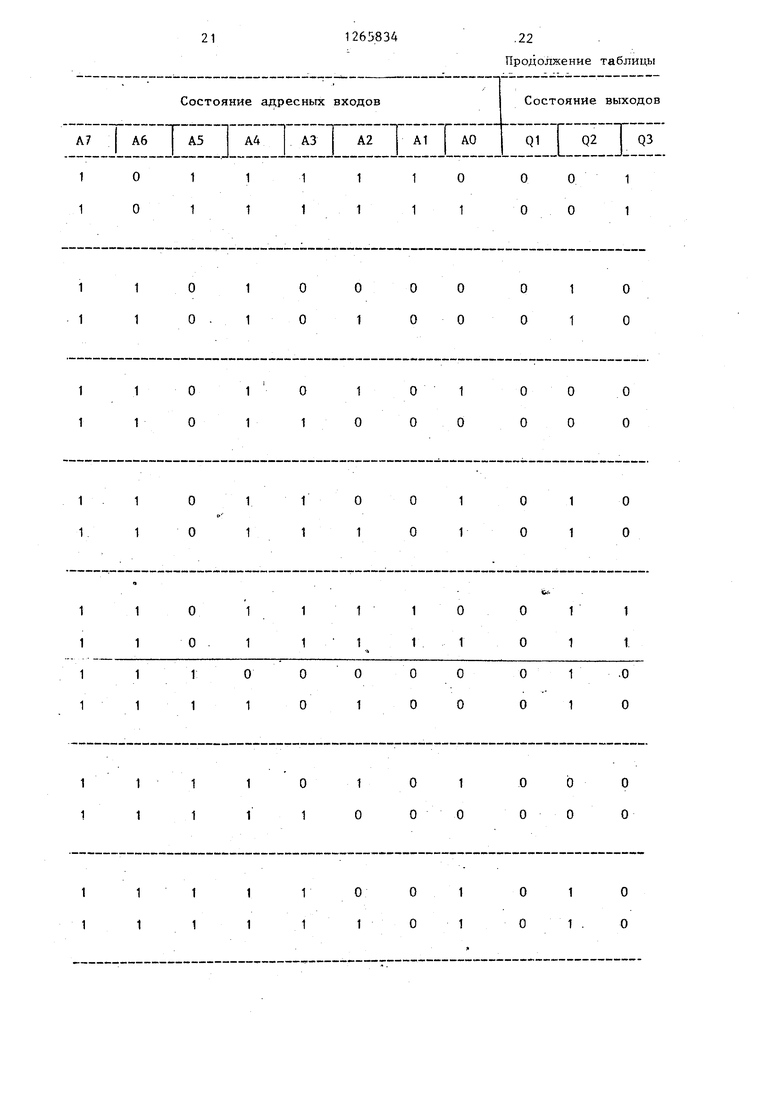

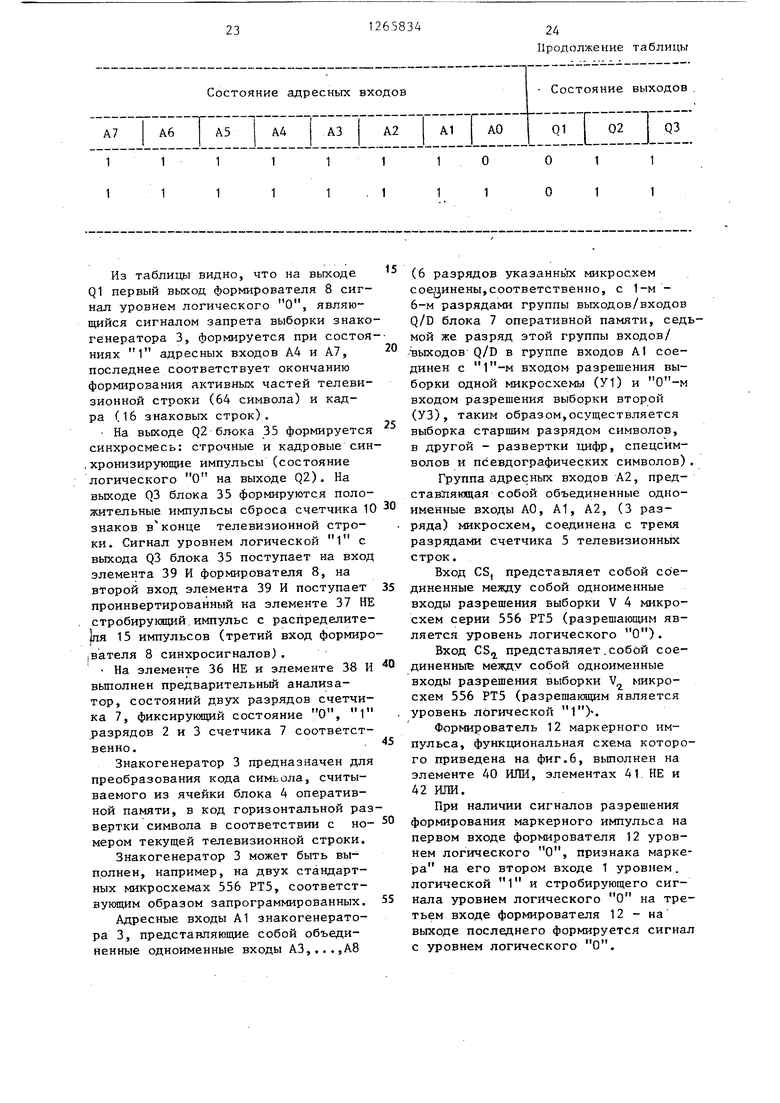

На элементе 33 8И-НЕ выполнен пой входов формирователя 8, предузелаварийного запуска (фиг.4). При ставляющих собой пять из семи разустановке распределителя 15 в единич- рядов счетчика 10 знаков, причем ное состояние (состояние всех выхо- |вход АО блока 35 соединен со вторым дов тиикросхемы 32 - логическая 1 для предлагаемого устройства исключенное, невозможное состояние), что возможно при включении питания, на выходе элемента 33 8И-НЕ, соединенного своими семью входами с соответствукхцими выходами регистра 32, формируется уровень логического О, который по R-входу сбрасывает регистр 32 сдвига в О. Установка нулевого уровня на седьмом выходе регистра 32 вызывает через элемент.34 НЕ установку по S-входу регистра 32 режима параллел ной записи, и с первым же тактовым импульсом на С-входе начинается нор мальная работа регистра 32. Формирователь 8 синхросигналов в зависимости от состояния счетчика 10 знаков и счетчика 7 знаковых строк формирует сигнал Запирание знакогенератора 3 по его входу Раз решение выборки (CS 2) в пассивной части телевизионной строки и кадра, формируя тем самым гашение луча, сигнал сброса счетч,ика 10 знаков в конце каждой телевизионной строки импульсов строчной и кадровой синхрош ации. На фиг.5 приведена функ циональная схема формирователя 8 синхросигналов, содержащего блок 35 памяти, элемента 36 и 37 НЕ, элемен ты 38 и 39 И, в качестве которых можно использовать, например, стандартные микросхемы 556 РТ4, 133ЛН1 и 133 ЛИ1, соответственно. Группа адресных входов А1 блока 35 памяти, представлякацая собой пять адресных входов А05...эАА микросхемы, соединена с первой груп126583414разрядом, А1 - с третьим, А2 - с четвертым, A3 - с пятым, А4 - с седьмым разрядами счетчика 10.. Группы адресных входов А2 блока 35, представляющая собой адресные входы А6, А7 данного блока, соединены с первым входом формирователя 8 синхросигналов, представляющих собой четыре из пяти разрядов счетчика 10 знаковых строк, причем вход А6 соединен с первым разрядом А7 - с пятым разрядом счетчика 7. Адресный вход A3 блока 35 памяти соединен с выходом элемента 38 И, первый вход которого соединен с третьим разрядом из первого входа (3-й разряд счетчика 7), а второй вход элемента 38 И соединен с выходом элемента 36 НЕ, вход которого соединен со вторым разрядом первого входа формирователя 8 (второй разряд счетчика 7). Первый выход Q1 блока 35 памяти формирователя синхросигналов соединен с его первым выходом, второй выход Q2 блока 35 соединен с первьш входом элемента 39 И, выход которого соединен с вторым выходом формирователя 8, а второй вход элемента 39 И соединен с выходом элемента 37 НЕ, вход последн о, в свою очередь, соединен с третьим входом формирователя 8 синхросигнала. Ниже приведена таблица программирования блока 35 памяти формирователя 8 синхросигнала (в качестве блока 35. взята конкретная микросхема серии 556 РТ4 с ее конкретными входами AOsa.c5A7, выходами Q1, Q2, Q 3.

О О

О

о

о о

о о

о

о о о о . о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для формирования знаков на экране телевизионного приемника | 1982 |

|

SU1191934A2 |

| Устройство для отображения информации | 1987 |

|

SU1441451A1 |

| Устройство для формирования знаков на экране телевизионного приемника | 1982 |

|

SU1073793A2 |

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1988 |

|

SU1509985A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1522272A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1984 |

|

SU1288750A1 |

| Устройство для отображения символьной информации на экране видеоконтрольного блока | 1987 |

|

SU1499331A1 |

| Устройство для формирования знаков на экране телевизионного индикатора | 1991 |

|

SU1833916A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1474635A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматизированных системах з равления, системах связи к вычислительной технике в качестве устройства ввода информации от ЭВМ и отображения ее на экране телевизионного приемника. Цель предложенного устройства - расширение области применения устройства за счет обеспечения возможности формирования символов без пробелов и повьвдения точности отображения.Устройство содержит задакяций генератор, преобразователь кодов, знакогенератор, блок-оперативной памяти, счетчик телевизионных строк, блок управления, счетчик знаковых строк, формирователь синхроимпульсов, мультиплексор адреса, счетчик знаков, смеситель, формирователь маркерного имS пульса, триггер, дешифратор, рас:пределитель импульсов и буферный регистр. 9 шт., 1 табл. rfSBKB «шю

о о

о

о

о о о

о о о

о о о

о о

о

о 1

1 о

0.

о

о

о

0

о о о

о

о о 1

о 1

о 1

17

О1

1

1 1

01

1 о 1

1о

о о 1о

о о

о о о о

о 1

о о

о о

о

о о

о

1265834

18 Продолжение таблицы

1о

о о 1

11

11

11

0о

1о

11

1о

1

о о

о о

о о

о о

о о

о

о о

о о

1 о

о

о

о о

о о

10

о

1265834

21

О

О

о о

о о

о о

о 1

о о

1 1 о о

о о 1 1

о

1

о

1

.22 Продолжение таблицы

о

о о

о о

1

о о

о о

о о

о

о

о о

1 о

о о

о о

о о

о о

о 1

о о

о о

tu

о 1

о 1 о о

1 1

о о о

о о

.0

о

о о

о о

о о

о о

1 о

о о

о

о о

о Из таблиць видно, что на выходе Q1 первый выход формирователя 8 сигнал уровнем логического О, являющийся сигналом запрета выборки знако генератора 3, формируется при состоя ниях 1 адресных входов А4 и А7, последнее соответствует окончанию фopмIipoвaния активных частей телевизионной строки (64 символа) и кадра (16 знаковьж строк). На выходе Q2 блока 35 формируется синхросмесь: строчные и кадровые син .хронизирующие импульсы (состояние логического О на выходе Q2), На выходе Q3 блока 35 формируются положительные импульсы сброса счетчика 10 знаков в конце телевизионной строки. Сигнал уровнем логической 1 с выхода Q3 блока 35 поступает на вход элемента 39 И формирователя 8, на второй вход элемента 39 И поступает проинвертированный на элементе 37 НЕ стробирукщий.импульс с распределите|ля 15 импульсов (третий вход формиро 1вателя 8 синхросигналов). На элементе 36 НЕ и элементе 38 И вьшолнен предварительный анализатор, состояний двух разрядов счетчика 7, фиксирующий состояние О, 1 разрядов 2 и 3 счетчика 7 соответственно. Знакогенератор 3 предназначен для преобразования кода символа, считываемого из ячейки блока 4 оперативной памяти, в код горизонтальной раз вертки символа в соответствии с номером текущей телевизионной строки. Знакогенератор 3 может быть выполнен, например, на двух стандартных микросхемах 556 РТ5, соответствующим образом запрограммированных. Адресные входы А1 знакогенератора 3, представляющие собой объединенные одноименные входы АЗ,...,А8 (6 разрядов указаннь1Х микросхем соединены,соответственно, с 1-м 6-м разрядами группы выходов/входов Q/D блока 7 оперативной памяти, седьмой же разряд этой группы входов/ выходов Q/D в группе входов А1 соединен с входом разрешения выборки одной микросхемы (У1) и входом разрешения выборки второй (УЗ), таким образом,осуществляется выборка старшим разрядом символов, в другой - развертки цифр, спецсимволов и псевдографических символов). Группа адресных входов А2, представляющая собой объединенные одноименные входы АО, А1, А2, (3 разряда) микросхем, соединена с тремя разрядами счетчика 5 телевизионных строк. Вход CS, представляет собой соединенные между собой одноименные входы разрешения выборки V 4 микросхем серии 556 РТ5 (разрешающим является уровень логического О). Вход CS,j представляет .собой соединенные между собой одноименные входы разрешения выборки V микросхем 556 РТ5 (разрешаклцим является уровень логической 1). Формирователь 12 маркерного импульса, функциональная схема которого приведена на фиг.6, выполнен на элементе 40 ИЛИ, элементах 41. НЕ и 42 ИЛИ. При наличии сигналов разрешения формирования маркерного импульса на первом входе формирователя 12 уровнем логического О, признака маркера на его втором входе 1 уровнем, логической 1 и стробирующего сигнала уровнем логического О на третьем входе формирователя 12 - на выходе последнего формируется сигнал с уровнем логического О. Преобразователь 2 параллельного кода в последовательный может быть выполнен, .например, на стандартной микросхеме 133ИР13. Смеситель 11, функциональная схе ма которого приведена на фиг.7, пре назначен для замешивания в яркост ную составляющую видеосигнала, поступающего с выхода преобразователя синхросмеси из строчных и кадровых синхронизирующих импульсов и формирование полного видеосигнала, и может быть выполнен, например, на эле менте 43 НЕ (например, стандартная микросхема 133 ЛА8), транзисторе 4А и режимных резисторах 45-48. Устройство работает следующим об разом. При подаче питания устройство устанавливается в исходное состояние. В исходном состоянии триггер 1 находится в единичном состоянии (1 - на прямом выходе и О - на инверсном), дешифратор 14 закрыт по входу Разрешение выборки 2 (CS 2) с третьего выхода блока 6 управлени на вход Разрешение выборки CS-бло ка 4 оперативной памяти поступает сигнал разрешения с уровнем О, на режимный V-вход блока 4 оперативной памяти со второго выхода блока 6 . управления - единичный сигнал Чтение, а с четвертого выхода блока 6 единичный сигнал блокировки выходных буферов регистра 16 по его входу разрешения выборки (CS). Таким образом, на внутреннюю шину данных открыты выходы (Q/D) блока 4 оперативной памяти. За начало формирования растра (очередного полукадра) принято нуле вое состояние линейки счетчиков 10 знаков, 5 телевизионных строк, 7 знаковых строк, соединенных последо вательно. Тактирование линейки счет-чиков осуществляется от распределителя 15 импульсов, который, в свою очередь, тактируется задающим генератором 1. Цикл работы распределителя 15, выполненного на сдвиговом регистре 32 состоит из семи тактов (семь периодов задающего генератора 1). При нулевом состоянии счетчика 5 телевизионных строк блоком 6 управления формируется на первом выходе управляющий код, который, поступая на первый вход мультиплексора 9 адреса, вызывает в последнем логическое подключение входов мультиплексора 9; являющихся по сути выходами счетчиков 10 знаков и 7 знаковых строк, к выходам F мультиплексора 9, а следовательно, к адресньм входам А блока 4 оперативной памяти. Таким об(разом, на адреснь е входы блока 4 оперативной памяти поступает код текущего адреса. Время выборки и преобразования кода символа определяется циклом работы распределителя 15 импульсов. В 1-м такте по заднему (положительному) фронту импульса на первом выходе распределителя 15 осуществляется приращение к счетчику 10 знаков. Через мультиплексор 9 адрес (состояние счетчиков 7 и 10) поступает на адресные входы А блока 4 оперативной памяти. Код символа, хранящийся в выбранной ячейке блока 4 оперативной памяти, с Q/D-выходов его поступает на адресные входы А1 знакогенератора 3, который открыт по входам разрешения выборки (CS1, CS2) сигналами: единичным по входу вы:борки CS 2 блока 4, поступающим с ,первого выхода формирователя 8 синхросигнапов и нулевым по входу выборки CS1, являкщимся старшим разрядом счетчика 5 телевизионных строк На выходе Q знакогенератора 3 формируется семиразрядный код горизонтальной развертки символа в соответствии с входным кодом символа (входы А1) и трехразрядным кодом текущей телевизионной строки (входы А2 знакогенератора 3). Семиразрядный код развертки символа поступает на D-входы (информационные входы) преобразователя 2 параллельного ко-, да в последовательный. По окончании формирования преды-, дущего символа, т.е. в такте 7 распределителя 15 импульсов, на втором выходе распределителя 15 формируется единичный уровень, который по режимному S-входу преобразо.вателя 2 устанавливает последний в ре- жим параллельной записи. Следующим тактовым импульсом задающего генератора 1, поступающим на С-входы синхронизации блоков преобразователя 2 и распределителя 15, осуществляется параллельная запись входной информации в преобразователь 2 (по положительному из О в 1 фронту импульса), Одновременно заканчивается цикл работы распределителя 15 и на втором выходе его формиру ется нулевой уровень, перевода по S-входу преобразователь 2 в режим сдвига вправо - начинается формирование первой растровой точки, т.е. очеред ной цикл формирования горизонтальной развертки символа. Хранение в знакогенераторе 3 семиразрядного ко да развертки символа позволяет как формировать пробеловые точки по кра ям символа, так и исключать их (т.е формировать уровень белого), что позволяет расширить поле для формирования псевдографических символов. Формируемая описанным способом последовательность импульсов, представлякяцая собой яркостную составляющую видеосигнала, с выхода преобразователя 2 поступает на второй вход смесителя 11. Так цикл за циклом осуществляется процесс формирования активной части телевизионной строки. По окончании формирования развертки последнего символа в телевизионной строке (64-го символа) на первом выходе фор мирователя 8 формируется уровень, которым по входу выЙорки.СЗ 2 запирается знакогенератор 3, и на ег выходе формируется единичный сигнал который приводит к единичному состоянию выходное состояние преобразователя 2. Поступая на второй вход смесителя 11, этот единичный сигнал вызывает формирование уровня гашения луча телевизионного приемника на выходе смесителя 11. Длительность гашения луча, обусловленная геометрическими искажениями в краях растра, составляет 28 циклов распределителя (19,6 мкс). По достижении счетчиком 10 знаков состояния, определяющего край формируемого растра (64+10 циклов), на тре тьам выходе формирователе 8 синхросигналов формируется нулевой уровен передний фронт импульса вторичной синхронизации. Дпительность импульс строчной синхронизации 5,6 мкс (8 циклов). По окончании импульса синхронизации продолжается гашение экрана еще в течение 10 циклов распределителя 15. По достижении счетч ком 10 знаков состояния, определяющего длительность полной телевизион ной (единично) строки, на втором вы ходе - формирователя синхросигнала формируется единичный импульс, которьш по R-входу сбрасывает счетчик 10 знаков в исходное состояние, а к счетчику 5 телевизионных строк, связанному своим счетным , С входом со старшим разрядом счетчика 10 знаков, делается приращение +1. Начинается формирование следующей телевизионной строки в знаковой строке. Так цикл за циклом, строка за строкой происходит формирование горизонтальной и вертикальной разверток знаковой строки. По достижении счетчиком 5 телевизионных строк состояния, определяющего окончание вертикальной развертки символа и начала межстрочного промежутка, а именно, по достижении единичного состояния второго выхода счетчика 5 и нулевого состояния первь х выходов счетчика 5, по входу разрешения выборки , eg 1 осуществляется запирание знакогеНератора 3. Таким образом, в течение 8 телевизионных строк формируется вертикальная развертка знаковой строки - с нулевой по седьмую телевизионные строки (нулевая строка формируется пробелов.ой при формировании цифр, букв и спецсимволов на знакогенераторе 3), девятая телевизионная строка - пробеловая. Телевизионные строки знаковой строки, с десятой по двенадцатую, являются полем маркера, что соответствует состояниям счетчика 5 с 1001 по 1011, при этом на первых выходах блока 6 формируется управляющий код, переводящий мультиплексор 3 в режим сравнения, и при -совпадении кодов текущего адреса (третий и четвертый входы мультиплексора 9) и входного адреса (второй вход мультиплексора 9) на выходе К последнего формируется единичный сигнал Признак маркера, поступающийна второй вход формирователя 12 маркерного импульса. На пятом выходе блока 6, синфазно с появлением кода Сравнение на его первом выходе, формируется нулевой сигнал Разрешение формирования маркера, поступающий на nepBbrii вход формирователя 12 маркерного импульса. При наличии сигналов Признак маркера единичного уровня на втором входе формирователя 12 и Разрешение формирования маркера нулевого ypoiBня на первом входе формирователя 12 29 и При поступлении импульса синхронизации нулевого уровня на третий вход формирователя 12 (такт 1 распределителя 15) на выходе формирователя 12 формируется маркерный импульс, сбрасывающий преобразователь 2 по его R-входу. Таким образом, формируется маркер длительностью по горизонтали в семь растровых точек и по вер тикали - в три телевизионных строки При достижении счетчиком 5 состояния 1100 (единичные состояния в ста ишх разрядах счетчика 5), т.е.- состояния, соответствующего тринадцатой телевизионной строке в знаковой стро ке, - первый вход блока 6 принимает единичное состояние и ьгультиплексор переходит из режима Сравнение в режим трансляции на выход текущего адреса. На пятом выходе блока 6 формируется единичный уровень запрета формирования маркерного импульса. Тринадцатая телевизионная строка фор мнруется как пробеловая,, так как знакогенератор 3 закрыт по входу CS По окончании формирования тринадцатой телевизионной строки счетчик 5 сбрасьшается, а счетчик 7 знаковых строк, связанный счетным вкодом с йы Ысдом счетчика 5, увеличивает свое состояние на 1, Устройство начинает формировать следующую знаковунз строк о Так происходит фор1«ирование строки за строкойэ пока не будет сформирована последняя (16) знакевая строка растра, Как только состояние счетчика 7, превысит код последней знаковой стр ки (100.00) на первом выходефop шрователя 8 синхросигналов сформируется сигнал нулевого уровняj закры,веющий знакогенератор 3 по входу CS 2 - начинается гашение-луча по кадруS, по длительностн составля ощее 8 знаковых строк. В середине пассив ной части кадра, на третьем выходе формирователя 8 формируется нулевой уровень длительностью в одну знако вуга строку - кадровый синхронизирую щий импульс, По достижении счетчиком 7 состояния, соответствующего двадцати четырем знаковьм строкам п приходу следующего фронта (переднего) импульс на счетном входе счетчик сбрасьшается и начинается очеред ной цикл формирования кадровой развертки. На смесителе It осуществляе ся замещивание в яркостную состав 34 ляющую, поступающую с преобразователя 2 по втopo fy входу, сигнала строчной и кадровой синхронизации (сигнала синхросмеси), поступающего с формирователя 8 на первьй вход смесителя 11 и формирование стандартного полного видеосигнала. Временная диаграмма работы устройства в рексиме записи информации с внешнего устройства управления приведена на фиг,9. После прихода единичного импульса записи на С-вход буферного регистра 16, соединенного с входом 18 устройства, а именно, по заднему его фронту (из Г в О) информация на D-входах регистра 16, соединенных с информационным входом 19 устройства, фиксируется в регистре 16, По этому же фронту импульса на выходе запроса (ЗП) регистра 16 формируется нулевой уровень. Состояние D-входа триггера 13 опрашивается в конце каждого цикла распределителя 15 импульсов задним (положительным) фронтом импульса на пятом выходе распределителя 15, При появлении нулевого уровня на В-Еходе триггера 13 положл-тельным фронтом кьгпулъса по С-входу триггера 13, соединенного с пятым выходом распределителя 15, триггер 13 переводится в нулевое состояние и единичным уровнемка инверсном выходе разблокирует входной дешифратор 14, который остается закрытым по входе iCS 1 единичным состоянием второго выхода распределителя 15, Инвертирование состояния четвертого .и третьего входов блока 6, связанных соответственно с и инверсным выходами триггера 13 (нулевой уровень - на первом входе . и единичный - на втором) вызывает формирование на третьем выходе блоединичного сигнала, закрывающекаit ,- «, го по входу разрешение выборки (CS-блок 4 оперативной памяти, Q/D входы/выходы переводятся в третье состояние), на четвертом выходе блока 6 - нулевого сигнала; открывающего по- входу разрешения выбор- . ки CS выходные буферы регистра 16, и,код символа, записанный в буфер- ный 16, выставляется кавнутреннюю шину данных устройства (связь Q - выходов регистра 16 с Q/D-BXo дами) блока 4 оперативной памяти, группой А - входов дешифратора 14 и группой А1 - входов знако генератора 3. Первый выход блока 6 управления принимает состояние, вызывающее переключение мультиплексора 9 из режимов либо сравнения, либо трансляции текущего адреса, в режим тран сляции входного адреса, поступающег с входа 17 устройства на второй вход мультиплексора 9. Таким образом, ад ресные входы А блока 4 аналоговой п мяти оказываются логически подключенными к группе информационных входов мультиплексора 9 (через выходы F мультиплексора 9), т.е. к входному адресу. Следующий такт распределителя 15 импульсов является холостым, обеспечивая необходимую задержку на время переходных процессов на внутренней шине данных и выборки яче ки в блоке 4 оперативной памяти. В третьем такте распределителя 15 импульсов на втором выходе блока 6 фор мируется отрицательный импульс, кото вый по входу разрешение выборки CS 1 открьгоает входной дешифратор 1 и в случае кода на адресных входах дешифратора 14, соответствующего коду, хранящемуся в знакогенераторе 3 (буквы, цифры, спецсимволы, псевдографические символы)э на первом выходе дешифратора 14 формируется импульс записи отрицательной полярнос ти, равный по длительности периоду задающего генератора 1. Этот импульс записи, поступающий на пятьй вход блока 6, вызывает на втором выходе его отрицательный импульс, равный по длительности входному, но с задержкой на,одном элементе И - и на третьем выходе блока 6. Эти два сим,вола в совокупности вызывает запись кода на Q/D входах/выходах в выбранную ячейку блока 4 оперативной памяти. В такте 4 распредели- еля 15, являиядемся холостым, снятие импульса записи на пятом входе блока 6 (последнее . вызвано снятием импульса со входа разрешения выборки CS 1) вызывает единичные сигналы на втором и третьем выходах блока 6, Блок 4 оперативной памяти запирается, так как на его входе разрешения выборки CS устанавливается единичный уровень, так же как и на входе V выбора режима блока 4 оперативной памяти. В пятом такте распределителя 15 отрицательный импульс, формирукщийся на первом выходе блока 15, устанавливает по входу триггер 13 в единичное состояние (исходное состояние) что приводит блок 6 в исходное состояние, на третьем выходе блока 6 формируется нулевой уровень, устанавливая блок 4 оперативной памяти в режим считывания, на четвертом выходе блока 6 формируется единичный уровень, закрывающий выходной буфер регистра 16, при зтом на выходе ЗП регистра 16 снимается сигнал Запрос (фор шруется единичный уровень). Управлягацим сигналом первого выхода блока 6 мультиплексор 9 переключается и к адресным входам блока 4 оперативной памяти логически подключается текущий ад.рес (выходное состояние счетчиков 10 и 7), и осуществляется выборка текущего кода символа, по окончании цикла распределителя 15 с выхода знакогенератора 3 код горизонтальной развертки переписывается в преобразователь 2. Таким образом, изобретение позволяет по сравнению с известным устройством устранить искажение информации, вьшодимой на экран при обновлении информации в блоке 4 оперативной памяти за счет введения буферного регистра 16, триггера 13, распределителя 15 импульсов и связей их с блоком 6 управления, мультиплексором 9 адреса и другими блокакш устройства} расширить область применения устройства путем обеспечения возможности искусственного вытягивания знакоместа по горизонтали при необходимости формирования, помимо обычных символов, - псевдосимволов (например, сплошных горизонтальных линий) за счет конкретного исполнения знакогенератора 3 и связей его с преобразователем 2 параллельного кода в последовательный, обеспечивающих возможность хранения полного знакоместа в памяти знакогенератора 3. Формула изобретения Устройство для отображения информации на экране телевизионного приемника, содержащее задакяций генератор, выход которого соединен с тактовым входом преобразователя кодов, ин33126583А

формамлонные входы которого соединены с информационны выходами знакогенератора-, адресные входы первой группы которого соединены с информационными входами - выходами блока one-j ративнои памяти, адресные входы второй группы знакогенератора - с выходами первой группы счетчика телевизионных строк, соединенных с первым входом блока управления, второй вход которого подключен к выходам второй группы счетчика телевизионных строк, соединенным с входом счетчиказнаковых строк и первым входом разрешения выборки знакогенератора, второй вход разрешения выборки которого подключен к первому выходу формирователя синхросигналов, первый вход которого подключен к выходу счетчика знаковых строк, соединенному с входами первой группы входов мультиплексора адреса, входы второй группы входов которого являются первым входом устройства, входы третьей группы входов мультиплексора адреса подключены к выходу счетчика знаков, соединенному с входом счетчика телевизионных строк и вторым входом формирователя синхросигналов, входы четвертой группы входов мультиплексора подключены к первым выходам блока управления,, информационный выход мультиплексора адреса подключен к адресному входу блока оперативной памяти, вход выбора режима и вход разрешения выбор- jc ки блока оперативной пАмяти подключены соответственно к вторым и третьим выходам блока управления, первый вход счетчика знаков подключен к второму выходу формирователя синхро- Q

сигналов, третий выход которого подключен к первому входу смесителя, второй вход которого подключен к выходу преобразователя кодов, выход смесителя является первым выходом устройства, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения возможности формирования символов без пробелов и повьпления точности, в устройство введены формирователь маркерного импульса, тригдешифратора подключен к первому выходу триггера, соединенному с третьим входом блока управления, четвертый , вход которого подключен к второму выходу триггера5 пятый вход блока управления - к первому выходу дешифратора, второй которого является вторым выходом устройства. гер, дешифратор, распределитель импульсов и буферный регистр, первый и второй входы которого являются соответственно вторым и третьим входами устройства, третий вход буферного регистра подключен к четвертому выходу блока управления, пятый выход которого подключен к первому входу формирователя маркерного импульса, второй вход которого подключен к управляющему выходу мультиплексора адреса, третий вход формирователя маркерного импульса подключен к первому выходу распределителя импульсов, соединенному с вторым входом счетчика знаков, выход формирователя маркерного и гпульса подключен к первому управляющему входу преобразователя кодовэ второй управляющий вход которого подключен к второму выходу распределителя импульсов, вход которого подключен к выходу задающего генератора, третий выход распределителя импульсов подключен к третьему входу формирователя синхросигналов; четвертый и пятьш выходы распределителя импульсов подключены соответственно к первому и второму входам триггера, третий вход которого подключен к первому выходу буферного регистра. второй выход которого подключен информационным входам.- выходам блока памяти, подключенным к первому входу дешифратора, второй вход которого подключен к шестому выходу распределителя импульсов, третий вход

8жоди JJ

-б1

н&1.г

Ф1Л.6

dbtwdlO

.. /. ivii; vii.::: iiii 5;iii;;ii :;l

. «

Й5 й 5 й%йх/Йй

.

i2Miiii 3 iiiiii i;- J ; i ;si: g52

/-rJу i77. . ,.JA/5

V/ 7/// ////,i e////7 / ///M йд../ %

g

g ; ;pf ; -f%%; a /

Й1

%е айййй :; %

I dfodC

.. .-. x:%:% 2 %; c iSS 5$ .

ВмоЗЗ

n

J &ьподг

Выхбд Вы1Ч1д2

Лг /5

J |А«г,зЛ-«

Шй; й% ;; %гйййй ; . лг

1

.fAtS

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1010613A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Багдян В.П | |||

| Любительский дисплей | |||

| -Радио, 1982, № 5, с | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1986-10-23—Публикация

1984-12-30—Подача