сд

00

оэ со оэ

Изобретение относится к автоматике1 и вычислительной технике и может быть не- пользовано и автоматизированных системах управления, системах связи и вычислительной технике в качестве устройства вывода информации на экран телевизионного приемника.

Цель изобретения - повышение информативности устройства.

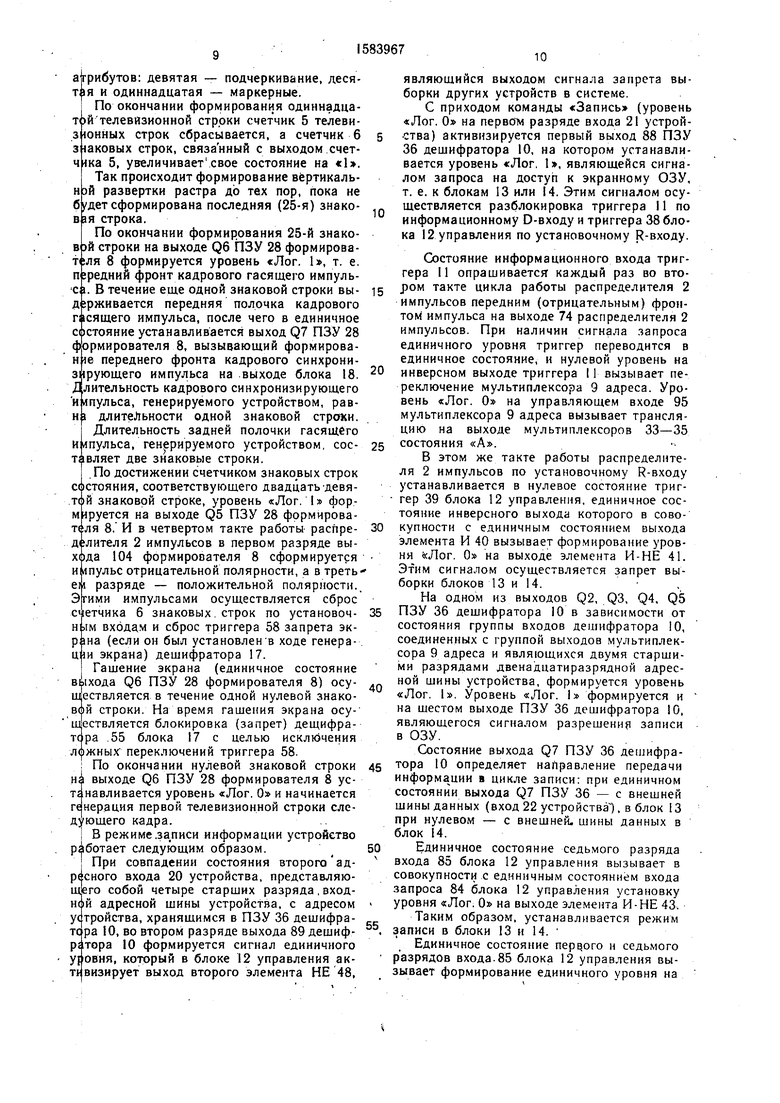

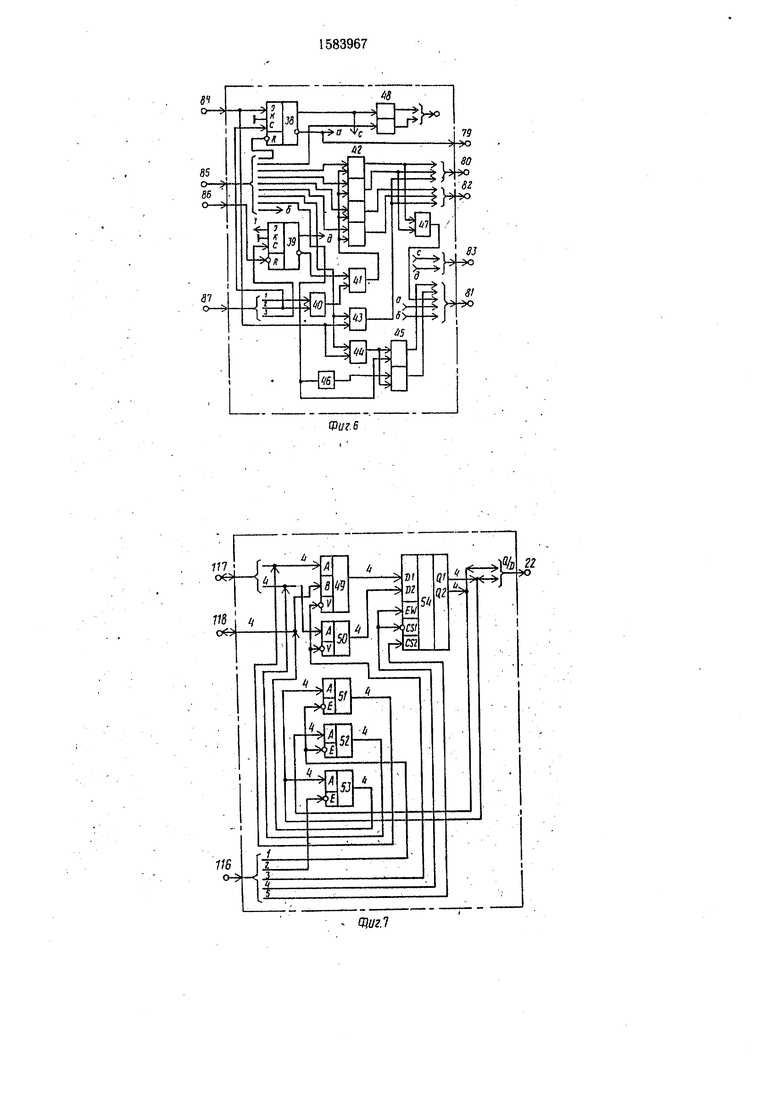

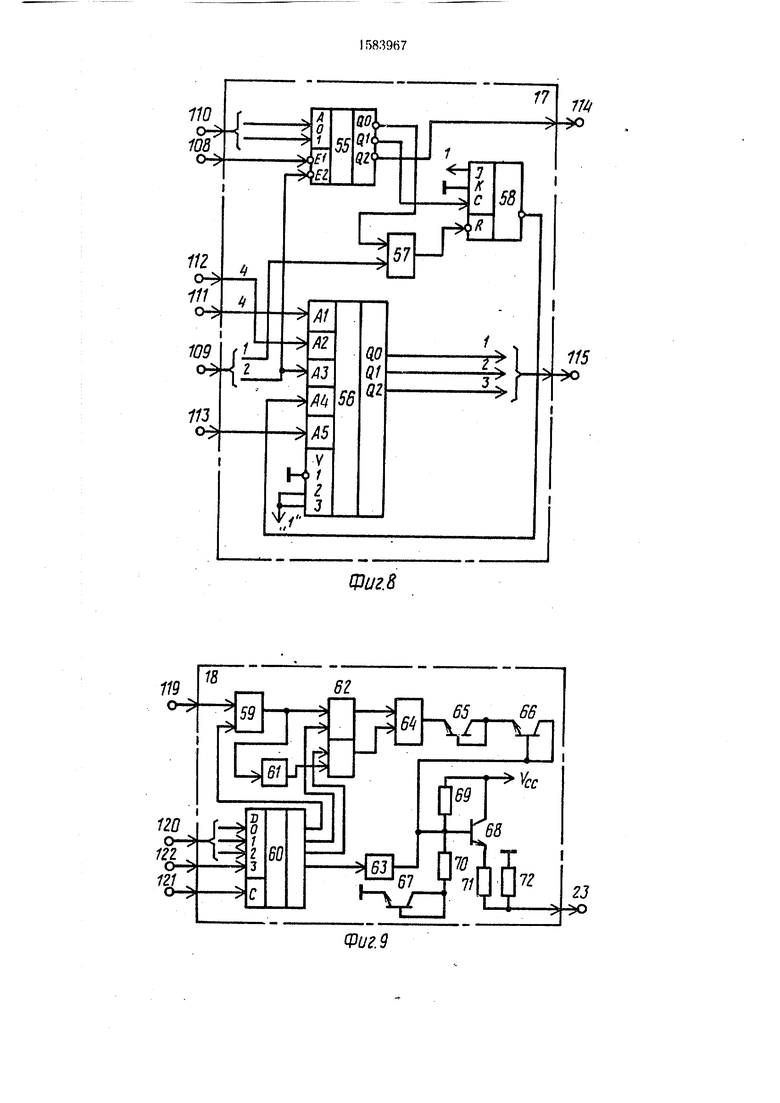

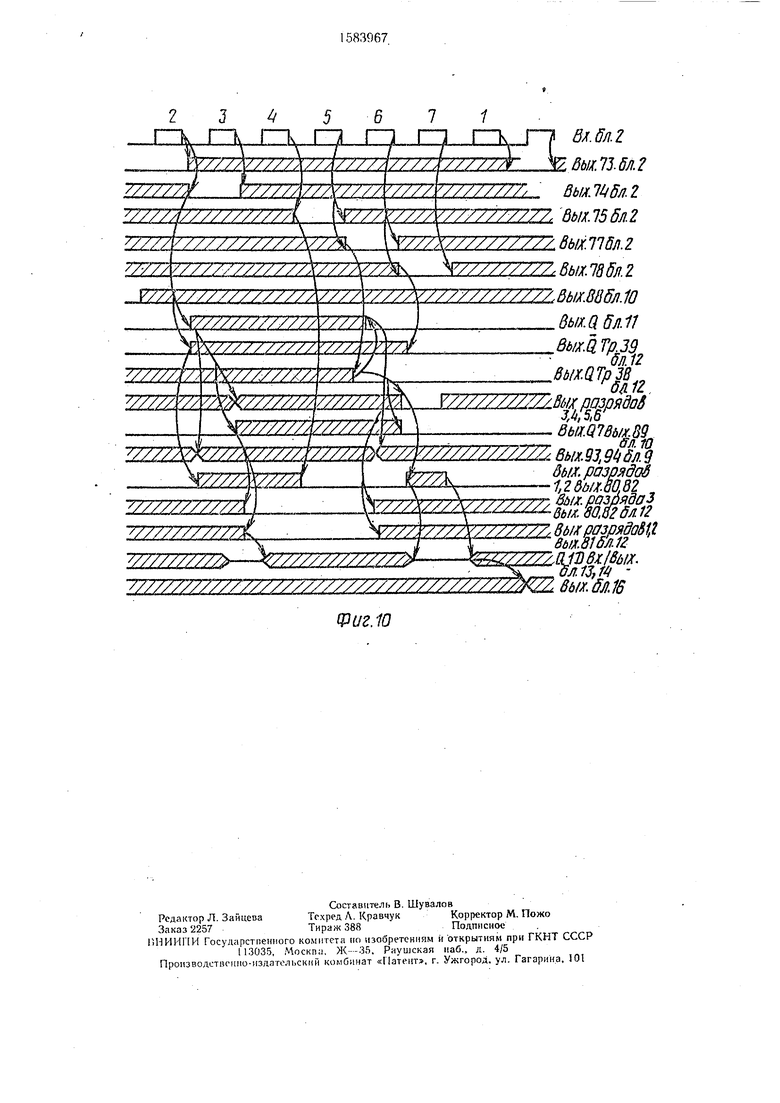

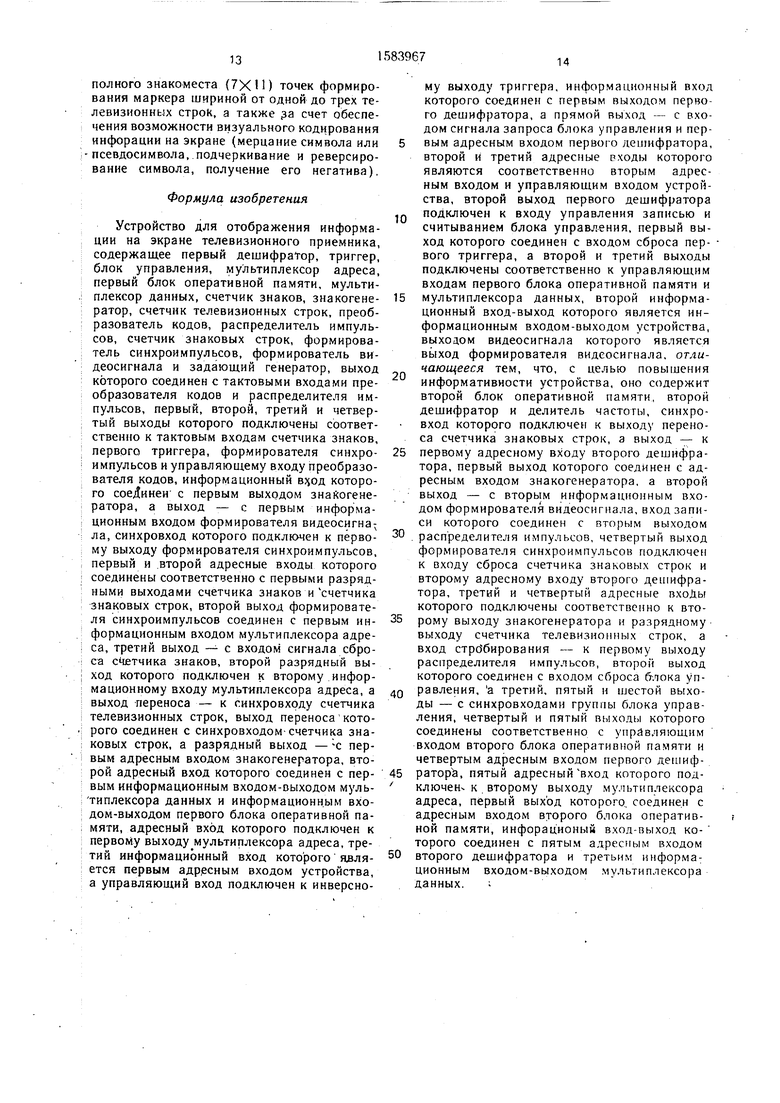

Па фиг. 1 представлена функциональная блок-схема устройства; на фиг. 2 принципиальная электрическая схема счетчика знаков; на фиг. 3 - принципиальная электрическая схема формирователя синхроимпульсов; на фиг. 4 - принципиальная электрическая схема мультиплексора адреса; на фиг. 5 - принципиальная электрическая схема первого дешифратора; на фиг. 6 - принципиальная электрическая схема блока управления; на фиг, 7 - принципиальная электрическая схема мультиплексора данных; па фиг. 8 - принципиальная электрическая схема второго дешифратора; па фиг. 9 - принципиальная электрическая схема формирователя видеосигнала (ФВС); на фиг. 10 - диаграмма работы устройства.

Устройство для отображения информации на экране, телевизионного приемника содержит задающий генератор 1, распределитель 2,импульсов, преобразователь 3 кодов, счетчик 4 знаков, счетчик 5 телевизионных строк, счетчик б знаковых строк, делитель 7 частоты, формирователь 8 синхроимпульсов, Мультиплексор 9 адреса, первый дешифратор 10, первый триггер 11, блок 12 управле- .ния, первый 13 и второй 14 блоки оперативной памяти, мультиплексор 5 данных, знакогенератор-16, второй дешифратор 17, формирователь 18 видеосигнала, первый адресный вход 19 и второй адресный вход 20 устройства, управляющий вход 21 устройства, управляющий вход 21 устройства, информационные входы-выходы 22 устройства, выход 23 видеосигнала устройства.

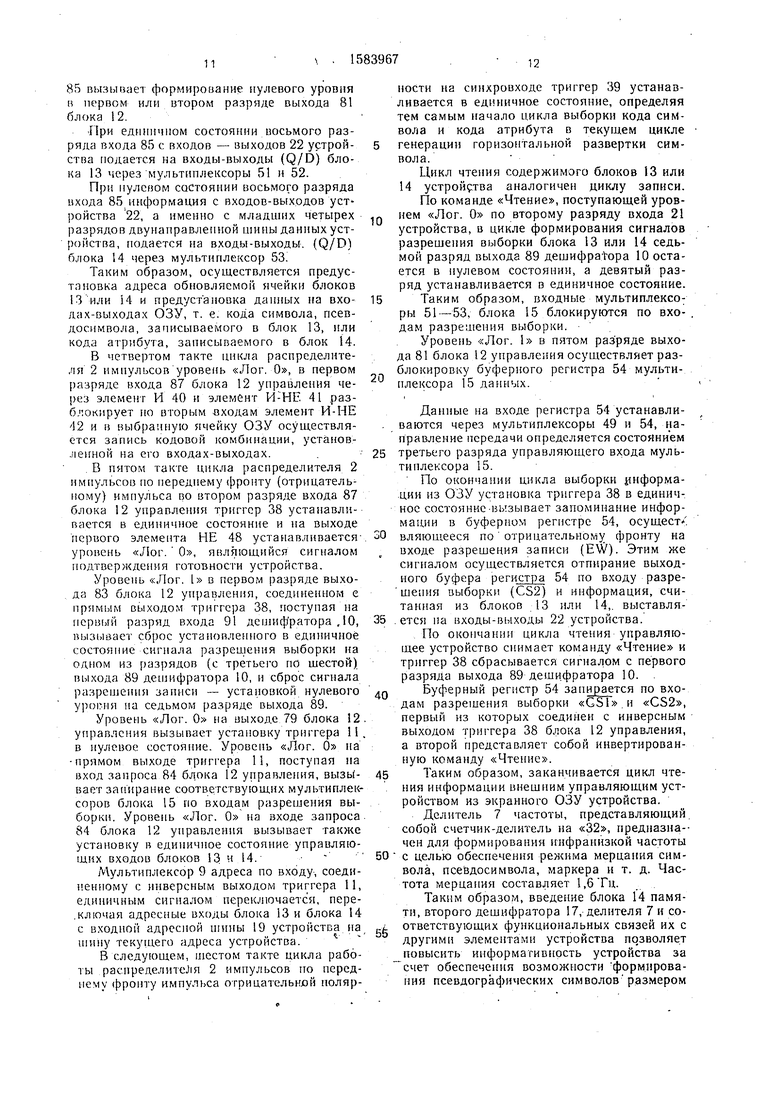

Счетчик 4 знаков содержит первый 24 и второй 25 счетчики, первый блок 26 элементов НЕ, первый элемент НЕ 27.

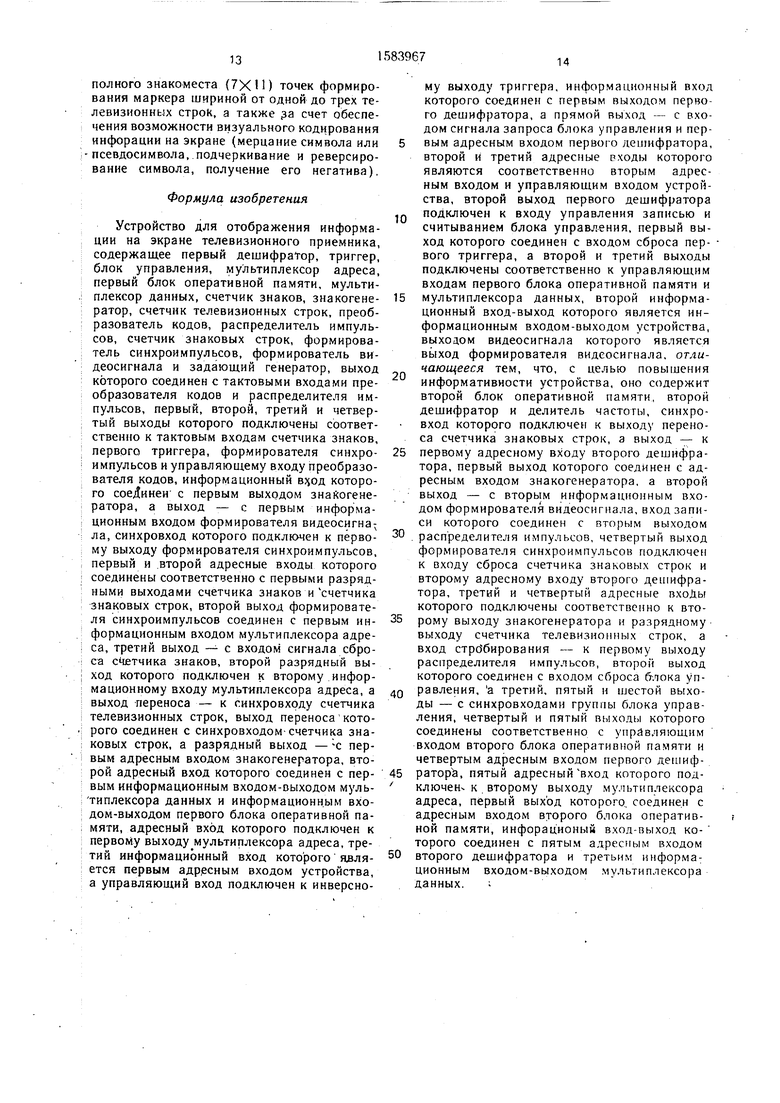

Формирователь синхроимпульсов содержит первый блок 28 постоянной памяти (ПЗУ), второй элемент НЕ 29, первый 30 и второй 31 блоки элементов И, третий элемент НЕ 32.

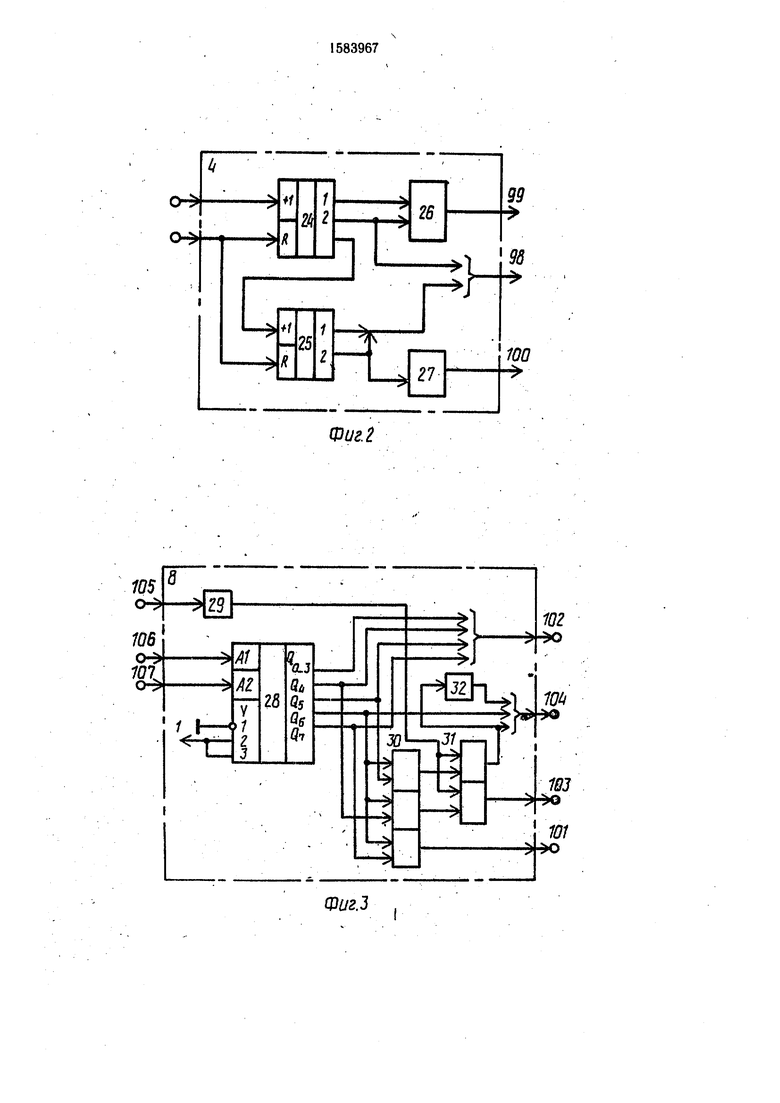

Мультиплексор 9 адреса содержит первый 33, второй 34 и третий 35 мультиплексоры.

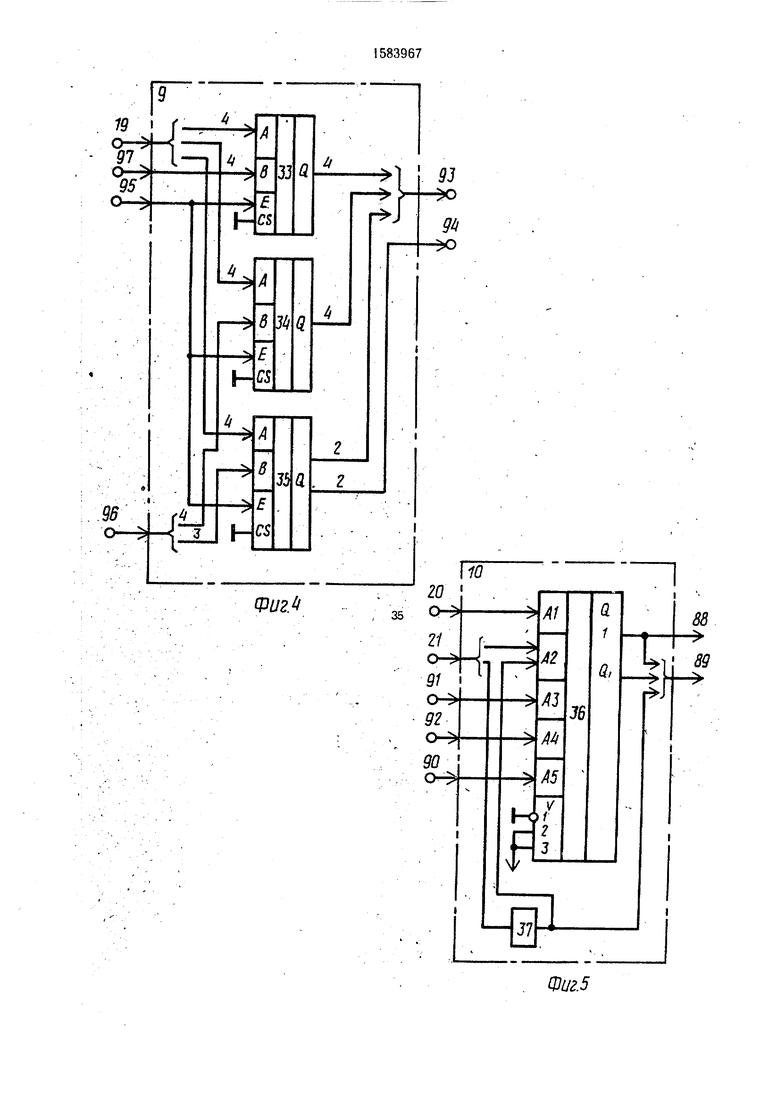

Первый дешифратор 10 содержит второй блок 36 постоянной памяти (ПЗУ), четвертый элемент НЕ 37.

Блок 12 управления содержит второй 3Ј| п третий 39 триггеры, первый элемент И 40, первый элемент И-НЕ 41, первую группу 43 элементов И-НЕ, второй элемент И-НЕ 43, второй элемент И 44, вторую труппу 45 эле- ментов И-НЕ, пятый элемент НЕ 46, третям элемент И 47, второй блок 48 элементов НЕ.

Мультиплексор 15 данных содержит четвертый 4е), питый 50, шестой 51, седьмой 52, восьмой 53 мультиплексоры, первый регистр 54..

Второй дешифратор 17 содержит дешифратор 55, третий блок 56 постоянной памяти (ПЗУ), четвертый элемент И 57, четвертый триггер 58.

Формирователь 18 видеосигнала содер- жнт третий элемент И-НЕ 59, второй регистр 60, шестой элемент НЕ 61, третью группу 62 элементов И-НЕ, седьмой элемент НЕ 63, четвертый элемент И-НЕ 64, ключи на транзисторах 65- (н м нагрузочные элементы на резисторах 69-72. Позициями 72-122 обозначены входы и

выходы соответствующих блоков устройства.

0

Устройство работает следующим образом.

В исходном состоянии устройства выходы дешифратора 10 принимают состояние, соответствующее циклу (режиму) регенерации экрана, а именно: первый выход 88 устанавливается в нулевое состояние, в пулевом

5 состоянии также первый, второй, седьмой, восьмой и девятый разряды второго выхода 89 дешифратора 10, представляющего собой девятнразрядную типу. Состояние третьего-шестого разрядов второго выхода 89 дешифратора 10 определяется текущим адре0 сом сканирования или адресом ячейки блоков 13 и 14, хранящих код текущего символа и атрибута символа соответственно. Триггер 11 устанавливается в нулевое состояние, п единичное состояние инверсного выхода триггера, соединенного с управляю5 . щнм входом мультиплексора 9, вызывает подключение к адресным входам блоков 13 и 14 текущего десятиразрядного адреса отображаемого символа, а к первому адресному входу 90 дешифратора 10 - адрес

Q выбираемого блока в составе блоков 13 и 14. Старшин разряд адресной шины в режиме регенерации всегда принимает нулевое состояние, так как выборка блоков 13 и 14 осуществляется сннфазно.

Нулевое состояние входа 84 запроса

5 блока 12 управления, а также нулевое состояние седьмого, восьмого и .девятого разрядов управляющего входа 85, представляющего собой девятиразрядпую шину, приводит к блокировке мультиплексора 15 данных, так как единичное состояние первого

0 и второго разрядов третьего выхода 81 блока 12 управления блокирует мультиплексоры 51-53 блока 15, а пулевое состояние пятого разряда третьего выхода 51 блокирует регистр 54 мультиплексора 15. Кроме того, единичное состояние третьих разрядов

ч второго 80 и четвертого 82 выходов блока 12 управления устанавливает режим считывания информации из блоков 13 и- 14 памяти.

За начало формирования растра (очередного полукадра) принято нулевое состояние линейки счетчиков знаков 4 и телевизионный строк 5 и единичное состояние (00001) счетчика 6 знаковых строк. Тактирование л-ийейки счетчиков осуществляется от распределителя 2 импульсов. Цикл работы рас- пр делителя 2, выполненного на сдвиговом регистре, состоит из семи тактов {семи пе- задающего генератора 1) и определяет длительность горизонтальной развертки символа (фиг. 10).

В первом такте цикла работы распреде- 2 по заднему (положительному) фрэнту импульса на первом выходе 73 распределителя 2 осуществляется увеличение на единицу содержимого счетчика 4 знаков. При этом- второй выход 99 счетчика 4 зна- кои представляет собой четыре младших разряда, а второй выход 103 формирователя 8 -j- семь старших разрядов адресной шины од ннадцатиразрядного кода текущего ад- реаа сканирования.

|Выход б ПЗУ 28 формирователя 8 принимает состояние «Лог. О и через блок 30 элементов И вызывает блокировку формирования импульсов сброса счетчика 4 знаков и счетчика 6 знаковых строк по входам элементов И 31 формирователя 8. Кроме того, уровень «Лог. О во втором разряде четвертого выхода 104 формирователя 8 является признаком формирования активной части строки (кадра), а уровень «Лог. О на первом выходе 101 формирователя 8 соответствует отсутствию синхронизирующего импульса в составе полного видеосигнала.

|Во втором такте цикла работы распределителя 2 импульсов импульсом отрица- ной полярности по выходу 74 распредели-. 1 2 осуществляется установка в нулевое ояние триггера 39 блока 12 управления.

тел тел: сое

вызывая формирование единичного состояния в первом и втором разрядах выходов 80 |И 82 блока 12 управления, являющихся сигналами разрешения выборки блоков 13 i 14..

/ровень «Лог. О, формирующийся во вто юм разряде пятого выхода 83 блока 12, поступая на адресный вход 91 дешифратор 10, вызывает установку в нулевое состоя 1ие третьего, четвертого, пятого и шестого разрядов второго выхода 89 дешифратора 10, соответствующего отсутствию сигналов разрешения выборки блоков 13 и 14.

Третий такт цикла работы распределителя 2 импульсов является холостым для все:( режимов работы устройства.

В четвертом и пятом тактах цикла работы распределителя 2 импульсы отрицатель- . ной; полярности, формирующиеся соответ- на выходах 75 и- 77 распределителя 2 и поступающие на первый, и второй разряды группы синхровходов 87 блока 12 управления,вызывают формирование сигналов опроса положительной полярности формирователей сигналов разрешения выборки, выполненных на элементах И-НЕ 42.

Выходы элементов И-НК 42 блока 12 уп- 5 равления удерживаются в единичном состоянии сигналами запрета выборки нулевого уровня по входу 85.

Таким образом, четыре такта работы распределителя 2 импульсов (такты е атороQ го по пятый включительно) являются подготовительными (предустановочными).

В шестом такте цикла работы распределителя 2 импульсов по переднему фронту импульса отрицательной полярности на шестом выходе 78 распределителя 2 триг5 гер 39 блока 12 управления устанавливается в единичное состояние по синхровходу. Уровень «Лог. О на инверсном выходе триггера 39 блока 12 через элемент И-НЕ 41 разблокирует элементы И-НЕ 42.

Единичное состояние второго разряда пятого выхода 83 блока 12 управления вызывает разблокировку соответствующих выходов разрешения выборки ОЗУ дешифратора 10.

Переход в единичное состояние третьего,

5 четвертого, пятого и шестого разрядов второго выхода дешифратора 10 осуществляется попарно: третий и четвертый при выборе первой половины блоков 13 и 14; а пя- тый и шестой при выборе второй половины блоков 13 и 14.

0Единичное состояние этих разрядов вызывает формирование нулевого состояния на соответствующем выходе блока 42 элементов И-НЕ, который вызывает отпирание по входу разрешения выборки соответствующее го банка в составе блоков 13 и 14.

5Код символа, хранящийся в выбранной

ячейке блока, с Q/D-выходов его поступает на адресные входы знакогенератора .16, а код атрибута, хранящийся в выбранной ячейке блока 14, с Q/-D-вы ходов его поступает на

Q адресные входы 112 дешифратора 17.

-На первом выходе знакогенератора 16 формируется код горизонтальной развертки символа в соответствии с входным кодом символа и четырехразрядным кодом текущей телевизионной строки. На втором выхо5 де знакогенератора 16 формируется двух- разрядньш признак, несущий информацию о состоянии первой растровой точки в горизонтальной рачвертке символа или о наличии команд - гашение луча (экрана), активизация луча. На выходах дешифратора 17 фор0 мируются сигналы засветки (формирование уровня белого), разрешения прямого или инверсного сигналов яркостной составляющей. Седьмой такт цикла работы распределителя 2 импульсов является холостым.

еВ первом такте цикла распределителя 2

импульс отрицательной полярности, формирующийся на выходе 73 распределителя 2, стробирует дешифратор 55 дешифратора 17. . на одном из выходов которого формируется уровень «Лог. О. Активизация выхо да Q1 дешифратора 55 вызывает установку в единичное состояние триггера 58 гашения экрана («О на инверсном выходе - гашение). Активизация выхода QO дешифратора 55 вызывает сброс по R-входу в нулевое состояние триггера 58, соответствующее разрешению засвечивания экрана. Активизация выхода Q2 дешифратора -58 вызывает засвечивание первой растровой точки горизон- талькой развертки символа.,

В этом же первом такте цикла распределителя 2 импульсов на выходе 76 его фор- мируется положительный сигнал, который по режимному входу преобразователя 3 устанавливает последний в режим параллельной записи. Следующим тактовым импульсом задающего генератора I, поступающим на синхровход преобразователя 3, осуществляется параллельная запись входной информации в преобразователь 3 (по отрицательному фронту импульса). Одновременно на выходе 73 распределителя 2 устанавливается уровень «Лог. 1, а на выходах1 74 и 76 - уровень «Лог. О. Уровень «Лог. О, устанавливающийся на входе режима преобра- зовапеля 3, переводит последний в режим сдвига, а по переднему фронту (отрицательному) импульса на выходе 74 распределителя 2 импульсов атрибутные признаки за- по инаются в регистре 60 формирователя 18.

Таким образом, заканчивается цикл выборки кода горизонтальной развертки сим- пола и кода, соответствующего символу атрибутивного признака, и, начиная с окончания первого такта работы распределителя 2 импульсов, начинается генерация горизонталыюй развертки символа в соответствии с установленным атрибутивным признаком (т. е. генерация первой растровой точки) на экране телевизионного .приемника.

Одновременно осуществляется п рираще- ние счетчика 4 знаков, т. е. начинается очередной цикл выборки кода развертки и кода атрибута. Характер горизонтальной раз- верткн символа (код горизонтальной развертки в матрице символа 5X7 и в матрице псевдосимвола 7Х 11 точек) определяется номером текущей телевизионной строки, поступающим на первую группу входов знако- генератора 16 со счетчика 5 телевизионных строк.

Формируемая описанным способом по- следователь носгышпульсов на выходе преобразователя 3, представляющая собой пози- тивную яркостную составляющую, с выхода преобразователя 3 поступает на вход формирователя 18, где в зависимости от атрибутивных признаков модифицируется (инвертируется, блокируется, МОДуЛИруеТСЯ, ДО-

полняется) и замешивается с синхросмесыо, поступающей из блока формирователя 8. Таким образом, цикл за циклом осуществляется процесс формирования активной части телевизионной строки. По екенчании формирования развертки последнем символа в телевизионной строке (80-го символа) на выходе Q6 ПЗУ 28 формирователя 8 синхроимпульсов устанавливается уровень «Лог. 1, а на остальных выходах ПЗУ 28 - уровень «Лог. О.

По окончании последнего цикла генерации активной части телевизионной строки (80-го символа) в регистре 60 блока 18 выходы QI и Q2 регистра устанавливаются в состояние «Лог. О и вызывают блокировку прямой и инверсной яркостных-составляющих по входам элементов И-НЕ 62.

быходы элементов И-НЕ 62 устанавливаются в единичное состояние, вызывая тем самым активизацию (установление уровня «Лог. 0) выхода элемента И-НЕ 64, что обуславливает формирование на выходе блока 18 уровня гасящего импульса.

Длительность гашения луча составляет 20 циклов работы распределителя 2 импульсов. По достижении счетчиком 4 знаков состояния, определяющего правый край формируемого растра 80-2, цикла, на выходе Q7 ПЗУ 28 формирователя 8 формируется единичный уровень, вызывающий формирование единичного уровня на выходе третьего элемента И 30 и соответственно на гыходе 101 формирователя 8.

Единичное состояние входа блока 18, соединенного с выходом формирователя 8, запоминается в регистре 60. Уровень «Лог. 1 на входе элемента НЕ 63 блока 18 обуславливает формирование на выходе блока 18 переднего фронта импульса строчной синхронизации. Длительность формируемого импульса строчной синхронизации составляет восемь циклов работы распределителя 2 им- -пульсов.

По окончании импульса синхронизации продолжается гашение экрана еще в течение десяти циклов работы распределителя 2 импульсов. По достижении счетчиком 4 знаков состояния, определяющего длительность полной телевизионной строки, на выходе Q4 ПЗУ 28 формирователя 8 формируется единичный уровень, который в свою очередь вызывает формирование единичного уровня на выходе Элемента блока 30 элементов И.

В четвертом такте работы распределителя 2 импульсов отрицательный импульс по тактовому входу 105 формирователя 8 возбуждает на выходе элемента НЕ 29 фор- мирование единичного импульса, который че- рез второй элемент блока И 31 осуществляет сброс счетчика 4 знаков.

Вертикальная развертка знаковой строки составляет одиннадцать телевизионных строк причем знакоместо символа занимает семь телевизионных строк - с второй по восьмую (нулевая - пробел), а знакоместо псевдосимвола - все одиннадцать. Телевизионные строки знаковой строки- с девятой по одиннадцатую являются также полем

атрибутов: девятая - подчеркивание, деся- и одиннадцатая - маркерные.

По окончании формирования одиннадцатой телевизионной строки счетчик 5 телеви- з юнных строк сбрасывается, а счетчик 6 з лаковых строк, связанный с выходом счет- ч-«ка 5, увеличивает свое состояние на «1.

Так происходит формирование вертикаль- нэй развертки растра до тех пор, пока не будет сформирована последняя (25-я) знако- взя строка.

По окончании формирования 25-й знако- в эй строки на выходе Q6 ПЗУ 28 формирователя 8 формируется уровень «Лог. 1, т. е. передний фронт кадрового гасящего импуль- чм. В течение еще одной знаковой строки вы- дфживается передняя полочка кадрового гасящего импульса, после чего в единичное состояние устанавливается выход Q7 ПЗУ 28 формирователя 8, вызывающий формирована переднего фронта кадрового синхронизирующего импульса на выходе блока 18. Длительность кадрового синхронизирующего и лпульса, генерируемого устройством, рав- HJ длительности одной знаковой строки. | Длительность задней полочки гасящего импульса, генерируемого устройством, сое- т вляет две знаковые строки.

, По достижении счетчиком знаковых строк состояния, соответствующего двадцать-девятой знаковой строке, уровень «Лог. I формируется на выходе Q5 ПЗУ 28 формирователя 8. И в четвертом такте работы распределителя 2 импульсов в первом разряде выхода 104 формирователя 8 сформируется импульс отрицательной полярности, а в третьем разряде - положительной полярности. Этими импульсами осуществляется сброс счетчика 6 знаковых строк по установочном входам и сброс триггера 58 запрета эк- рлна (если он был установлен в ходе генерации экрана) дешифратора 17.

Гашение экрана (единичное состояние выхода Q6 ПЗУ 28 формирователя 8) осуществляется в течение одной нулевой знаковой строки. На время гашения экрана осу- шествляется блокировка (запрет) дешифратора 55 блока 17 с целью исключения ложных переключений триггера 58.

По окончании нулевой знаковой строки нф выходе Q6 ПЗУ 28 формирователя 8 устанавливается уровень «Лог. О и начинается генерация первой телевизионной строки следующего кадра.

В режиме .записи информации устройство работает следующим образом.

При совпадении состояния второго адресного входа 20 устройства, представляющего собой четыре старших разряда.входной адресной шины устройства, с адресом устройства, хранящимся в ПЗУ 36 дешифра- тс ра 10, во втором разряде выхода 89 дешиф- рг.тора 10 формируется сигнал единичного

У1 п

овня, который в блоке 12 управления ак визирует выход второго элемента НЕ 48,

0

0

5 5

0

5

0

5

0

5

являющийся выходом сигнала запрета выборки других устройств в системе.

С приходом команды «Запись (уровень «Лог. О на первом разряде входа 21 устройства) активизируется первый выход 88 ПЗУ 36 дешифратора 10, на котором устанавливается уровень «Лог. 1, являющейся сигналом запроса на доступ к экранному ОЗУ, т. е. к блокам 13 или 14. Этим сигналом осуществляется разблокировка триггера II по информационному D-входу и триггера 38 блока 12 управления по установочному R-входу.

Состояние информационного входа триггера II опрашивается каждый раз во втором такте цикла работы распределителя 2 импульсов передним (отрицательным) фронтом импульса на выходе 74 распределителя 2 импульсов. При наличии сигнала запроса единичного уровня триггер переводится в единичное состояние, и нулевой уровень на инверсном выходе триггера И вызывает переключение мультиплексора 9 адреса. Уровень «Лог. О на управляющем входе 95 мультиплексора 9 адреса вызывает трансляцию на выходе мультиплексоров 33-35 состояния «А.

В этом же такте работы распределителя 2 импульсов по установочному R-входу устанавливается в нулевое состояние триг- гер 39 блока 12 управления, единичное состояние инверсного выхода которого в совокупности с единичным состоянием выхода элемента И 40 вызывает формирование уровня «Лог. О на выходе элемента И-НЕ 41. Этим сигналом осуществляется запрет выборки блоков 13 и 14.

На одном из выходов Q2, Q3, Q4, Q5 ПЗУ 36 дешифратора 10 в зависимости от состояния группы входов дешифратора 10, соединенных с группой выходов мультиплексора 9 адреса и являющихся двумя старшими разрядами двенадцатиразрядной адресной шины устройства, формируется уровень «Лог. I. Уровень «Лог. 1 формируется и на шестом выходе ПЗУ 36 дешифратора 10, являющегося сигналом разрешение записи в ОЗУ.

Состояние выхода Q7 ПЗУ 36 дешифратора 10 определяет направление передачи информации в цикле записи: при единичном состоянии выхода Q7 ПЗУ 36 - с внешней шины данных (вход 22 устройства), в блок 13 при нулевом - с внешней, шины данных в блок 14.

Единичное состояние седьмого разряда входа 85 блока 12 управления вызывает в совокупности с единичным состоянием входа запроса 84 блока 12 управления установку уровня «Лог. О на выходе элемента И-НЕ 43.

Таким образом, устанавливается режим записи в блоки 13 и 14.

Единичное состояние первого и седьмого разрядов входа.85 блока 12 управления вызывает формирование единичного уровня на

85 вызывает формирование нулевого уровня в первом или втором разряде выхода 81 блока 12

При единичном состоянии восьмого разряда входа 85 с входов - выходов 22 устройства подается на входы-выходы (Q/D) блока 13 через мультиплексоры 51 и 52.

При нулевом состоянии восьмого разряда входа 85 информация с входов-выходов уст ройства 22, а именно с младших четырех разрядов двунаправленной шины данных устройства, подается на входы-выходы. (Q/D) блока 14 через мультиплексор 53.

Таким образом, осуществляется предустановка адреса обновляемой ячейки блоков И или 14 и предустановка данных на входах-выходах ОЗУ, т. е. кода символа, псевдосимвола, записываемого в блок 13, или кода атрибута, записываемого в блок 14. В четвертом такте цикла распределителя 2 импульсов уровень «Лог. О, в первом разряде входа 87 блока 12 управления через элемент И 40 и элемент И-НЕ 41 разблокирует но вторым входам элемент И-НЕ 12 и в выбранную ячейку ОЗУ осуществляется запись кодовой комбинации, установленной на его входах-выходах.

Е5 пятом такге цикла распределителя 2 импульсов по переднему фронту (отрицательному) импульса во втором разряде входа 87 блока 12 управления триггер 38 устанавливается в единичное состояние и на выходе первого элемента НЕ 48 устанавливается уровень «Лог 0, являющийся сигналом подтверждения готовности устройства.

Уровень «Лог. 1 в первом разряде выхода 83 блока 12 управления, соединенном е прямым выходом триггера 38, поступая на первый разряд входа 91 дешифратора JO, вызывает сброс установленного в единичное состояние сигнала разрешения выборки на одном из разрядов (с третьего по шестой) выхода 89 дешифратора 10, и сброс сигнала разрешения записи - установкой нулевого урогня на седьмом разряде выхода 89.

Уровень «Лог. О на выходе 79 блока 12 управления вызывает установку триггера II. в пулевое состояние. Уровень «Лог. О на прямом выходе триггера 11, поступая на вход запроса 84 блока 12 управления, вызывает запирание соответствующих мультиплексоров блока 15 по входам разрешения выборки. Уровень «Лог. О на входе запроса 84 блока 12 управления вызывает также установку в единичное состояние управляющих входов блоков 3 ч 14.

Мультиплексор 9 адреса по входу, соединенному с инверсным выходом триггера 11, единичным сигналом переключается, переключая адресные входы блока 13 и блока 14 с входной адресной шины 19 устройства на шину текущего адреса устройства.

В следующем, шестом такте цикла работы распределителя 2 импульсов по переднему фронту импульса отрицательней полярности на синхровходе триггер 39 устанавливается в единичное состояние, определяя тем самым начало цикла выборки кода символа и кода атрибута в текущем цикле генерации горизонтальной развертки символа.

Цикл чтения содержимого блоков 13 или 14 устройства аналогичен циклу записи.

По команде «Чтение, поступающей уров- нем «Лог. О по второму разряду входа 21 устройства, в цикле формирования сигналов разрешения выборки блока 13 или 14 седьмой разряд выхода 89 дешифратора 10 остается в пулевом состоянии, а девятый разряд устанавливается в единичное состояние. Таким образом, входные мультиплексоры 51 -53, блока 15 блокируются по входам разрешения выборки.

Уровень «Лог. 1 в пятом разряде выхода 81 блока 12 управления осуществляет разблокировку буферного регистра 54 мульти- плексора 15 данных.

Данные на входе регистра 54 устанавливаются через мультиплексоры 49 и 54, направление передачи определяется состоянием

5 третьего разряда управляющего входа мультиплексора 15.

По окончании цикла выборки информации из ОЗУ установка триггера 38 в единичное состояние вызывает запоминание информации в буферном регистре 54, осущест

0 вляюшееся по отрицательному фронту на входе разрешения записи (EW). Этим же сигналом осуществляется отпирание выходного буфера регистра 54 по входу разрешения выборки (CS2) и информация, считанная из блоков 13 или 14, выставля5 ется па входы-выходы 22 устройства.

По окончании цикла чтения управляющее устройство снимает команду «Чтение и триггер 38 сбрасывается сигналом с первого разряда выхода 89 дешифратора 10.

0 Буферный регистр 54 запирается по входам разрешения выборки «GS1 и «CS2, первый из которых соединен с инверсным выходом триггера 38 блока 12 управления, а второй представляет собой инвертированную команду «Чтение.

5 Таким образом, заканчивается цикл чтения информации внешним управляющим устройством из экранного ОЗУ устройства.

Делитель 7 частоты, представляющий собой счетчик-делитель на «32, предназначен для формирования ннфраиизкой частоты

0 с целью обеспечения режима мерцания символа, псевдосимвола, маркера и т. д. Частота мерцания составляет 1,6 Гц.

Таким образом, введение блока 14 памяти, второго дешифратора 17, делителя 7 и со- L ответствующих функциональных связей их с другими элементами устройства позволяет повысить информативность устройства за счет обеспечения возможности формирования псевдографических символов размером

полного знакоместа {7X11) точек формирования маркера шириной от одной до трех те- евизионнь х строк, а также за счет обеспечения возможности визуального кодирования инфорации на экране (мерцание символа или псевдосимвола, подчеркивание и реверсирование символа, получение его негатива).

Формула изобретения

Устройство для отображения информации на экране телевизионного приемника, содержащее первый дешифратор, триггер, блок управления, мультиплексор адреса, первый блок оперативной памяти, мультиплексор данных, счетчик знаков, знакогенератор, счетчик телевизионных строк, преобразователь кодов, распределитель импульсов, счетчик знаковых строк, формирователь синхроимпульсов, формирователь видеосигнала и задающий генератор, выход которого соединен с тактовыми входами преобразователя кодов и распределителя импульсов, первый, второй, третий и четвертый выходы которого подключены соответственно к тактовым входам счетчика знаков, первого триггера, формирователя синхроимпульсов и управляющему входу преобразователя кодов, информационный которого соеДинен с первым выходом знакогенератора, а выход - с первым информационным входом формирователя видеосигнала, синхровход которого подключен к первому выходу формирователя синхроимпульсов, первый и второй адресные входы которого соединены соответственно с первыми разрядными выходами счетчика знаков и счетчика знаковых строк, второй выход формирователя синхроимпульсов соединен с первым информационным входом мультиплексора адреса, третий выход - с входом сигнала сброса счетчика знаков, второй разрядный выход которого подключен к второму информационному входу мультиплексора адреса, а выход переноса - к гинхровходу счетчика телевизионных строк, выход переноса которого соединен с синхровходом счетчика знаковых строк, а разрядный выход - :с первым адресным входом знакогенератора, второй адресный вход которого соединен с первым информационным входом-выходом мульиплексора данных и информационным входом-выходом первого блока оперативной памяти, адресный вход которого подключен к первому выходу мультиплексора адреса, третий информационный вход которого является первым адресным входом устройства, а управляющий вход подключен к инверсному выходу триггера, информационный вход которого соединен с первым выходом перво го дешифратора, а прямой выход - с входом сигнала запроса блока управления и пер5 вым адресным входом первою дешифратора, второй и третий адресные РЧОДЫ которого являются соответственно вторым адресным входом и управляющим входом устройства, второй выход первого дешифратора

0 подключен к входу управления записью и считыванием блока управления, первый выход которого соединен с входом сброса первого триггера, а второй и третий выходы подключены соответственно к управляющим входам первого блока оперативной памяти и

5 мультиплексора данных, второй информационный вход-выход которого является информационным входом-выходом устройства, выходом видеосигнала которого является выход формирователя видеосигнала, отличающееся тем, что, с целью повышения

0

информативности устройства, оно содержит

второй блок оперативной памяти, второй дешифратор и делитель частоты, синхровход которого подключен к выходу переноса счетчика знаковых строк, а выход - к

5 первому адресному входу второго дешифратора, первый выход которого соединен с адресным входом знакогенератора, а второй выход - с вторым информационным входом формирователя видеосигнала, вход записи которого соединен с вторым выходом

0 распределителя импульсов, четвертый выход формирователя синхроимпульсов подключен к сходу сброса счетчика знаковых строк и второму адресному входу второго дешифратора, третий и четвертый адресные входы которого подключены соответственно к вто5 рому выходу знакогенератора и разрядному выходу счетчика телевизионных строк, а вход стрббирования - к первому выходу распределителя импульсов, второй выход которого соеди-нен с входом сброса блока упС) равления, а третий, пятый и шестой выходы - с синхровходамн группы блока управления, четвертый и пятый выходы которого соединены соответственно с управляющим входом второго блока оперативной памяти и четвертым адресным входом первого дешиф5 ратор а, пятый адресный вход которого подключей- к второму выходу мультиплексора адреса, первый выход которого соединен с адресным входом второго блока оперативной памяти, инфорационын вход-выход которого соединен с пятым адресным входом

0 второго дешифратора и третьим информационным входом-выходом мультиплексора данных.

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Устройство для формирования знаков на экране телевизионного приемника | 1982 |

|

SU1073793A2 |

| Устройство для отображения информации на экране телевизионного приемника | 1985 |

|

SU1367035A1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

| Устройство для формирования видеосигнала | 1988 |

|

SU1675930A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1984 |

|

SU1288750A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1522272A1 |

| Устройство для формирования знаков на экране телевизионного приемника | 1982 |

|

SU1191934A2 |

| Устройство для отображения информации | 1987 |

|

SU1441451A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1984 |

|

SU1256084A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматизированных системах управления, системах связи и вычислительной технике в качестве устройства вывода информации на экран телевизионного приемника. Целью изобретения является повышение информативности устройства. Устройство содержит задающий генератор 1, распределитель 2 импульсов, преобразователь 3 кодов, счетчик 4 знаков, счетчик 5 телевизионных строк, счетчик 6 знаковых строк, делитель 7 частоты, формирователь 8 синхроимпульсов, мультиплексор 9 адреса, первый дешифратор 10, первый триггер 11, блок 12 управления, первый 13 и второй 14 блоки оперативной памяти, мультиплексор 15 данных, знакогенератор 16, второй дешифратор 17, формирователь 18 видеосигнала с соответствующими связями. Введение второго блока 14 оперативной памяти, второго дешифратора 17 и делителя 7 частоты позволило повысить информативность устройства за счет обеспечения возможности формирования псевдографических элементов размером полного знакоместа, формирования маркера шириной от 1 до 3 телевизионных строк и осуществления мерцания, реверсирования и подчеркивания символов. 10 ил.

Фиг.З

Фиг.5

b JIz4J M

99S9

т

6S

81

Ј-o

Ш

9 гпй

Z96f8fiI

2 J it 5 6 ПУ l К П I 3

JLLiL

ZZZZZA

у///

bLtZL

ZZZZZZZZZA/Z.

s/yy/

J222

V7ZZ

3

7ZZZZZZZZ2Z7Z,

ЈZZZ

7ZZ7ZL

7&77777777 /777У-.

Ш.

77/77//7Л//////Л

777777ZA/7Z///A

:ZZZZ2 ZZZ ZZZZIZZZZL.

7/7/7/777/,

Фиг.Ю

7

S

1

zzzzz

1

в км г

Вых.П5л.2

///

v//

.

//У/.

VZ/x

выхльбл.г

Z, Вш.15бл.2 ,0Ш.77Ял.2

Z

У-.

Z

77/

I

z.

//Л

//A

L.

S///////ZZ Вых. 185ft. 2 Z22ZZZZZZZZ дыхМбл. 10 Вых. 0. 5л. 11

YZZZZZZZZZZZBbixpamdoS

3,ч, 5о Bbff.Q7B6/fij9

Ю

WZZZY//////MZЈZZi вых.93,. 9

ъдаб

1,г&ых.Ш2 ,

r777- :7////77 7-s рОЗОЯОаЗ

. дш %о$ёЛ 12

у-ь- - - - - - ° --Qbix. ou.Qt ал it

- ZZ ZZZZZZZZZZZZ. №хиыхйЛ

OblX.Ql ОЛ.1&

№Ъ8116ЫХ.

щелШ4 J&tZZTT/T/..

:ж

вых.Шб

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1990-08-07—Публикация

1988-04-07—Подача