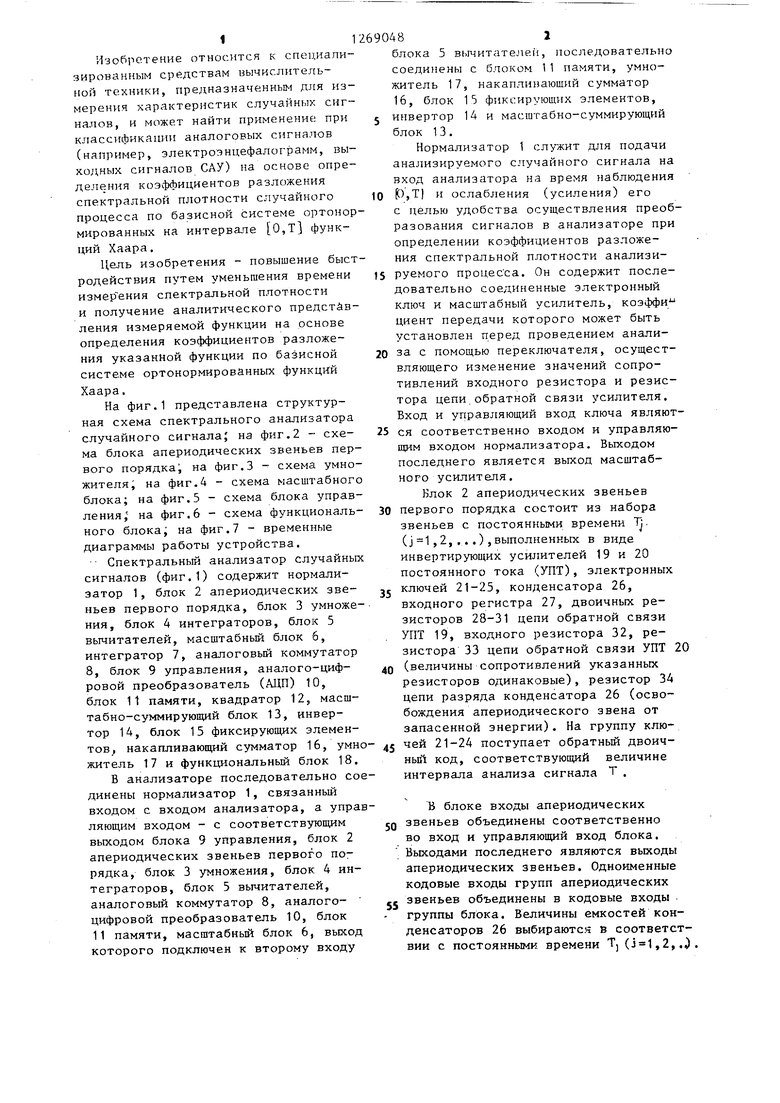

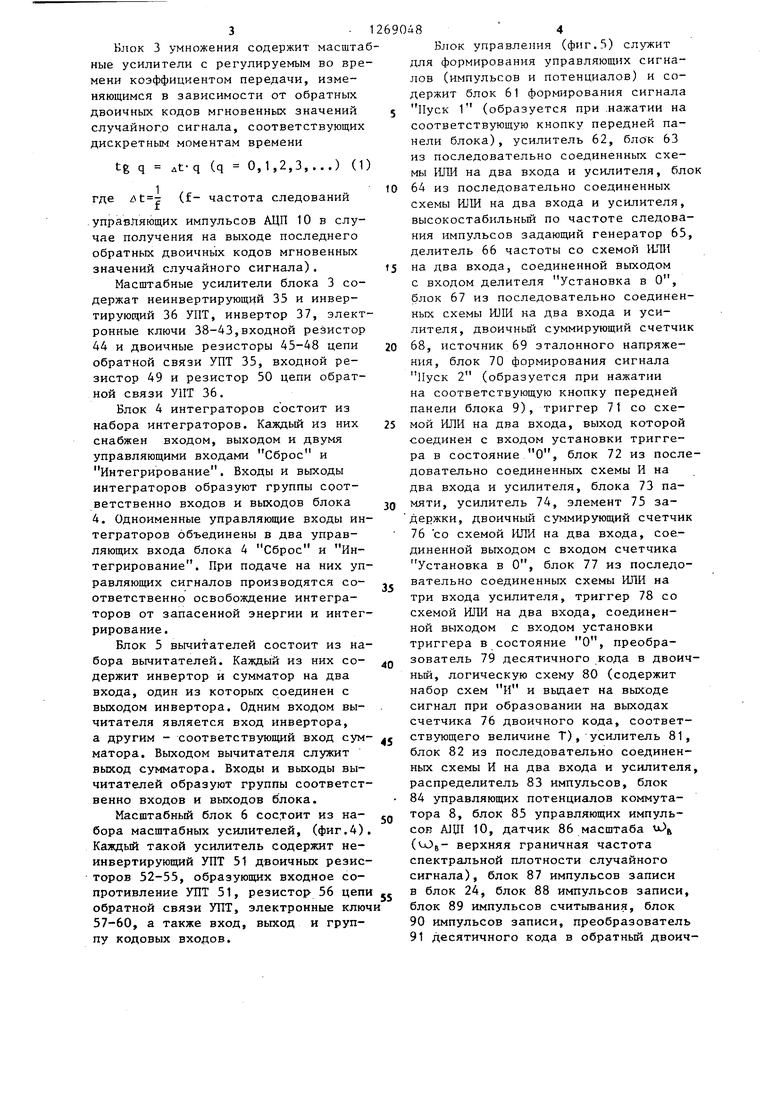

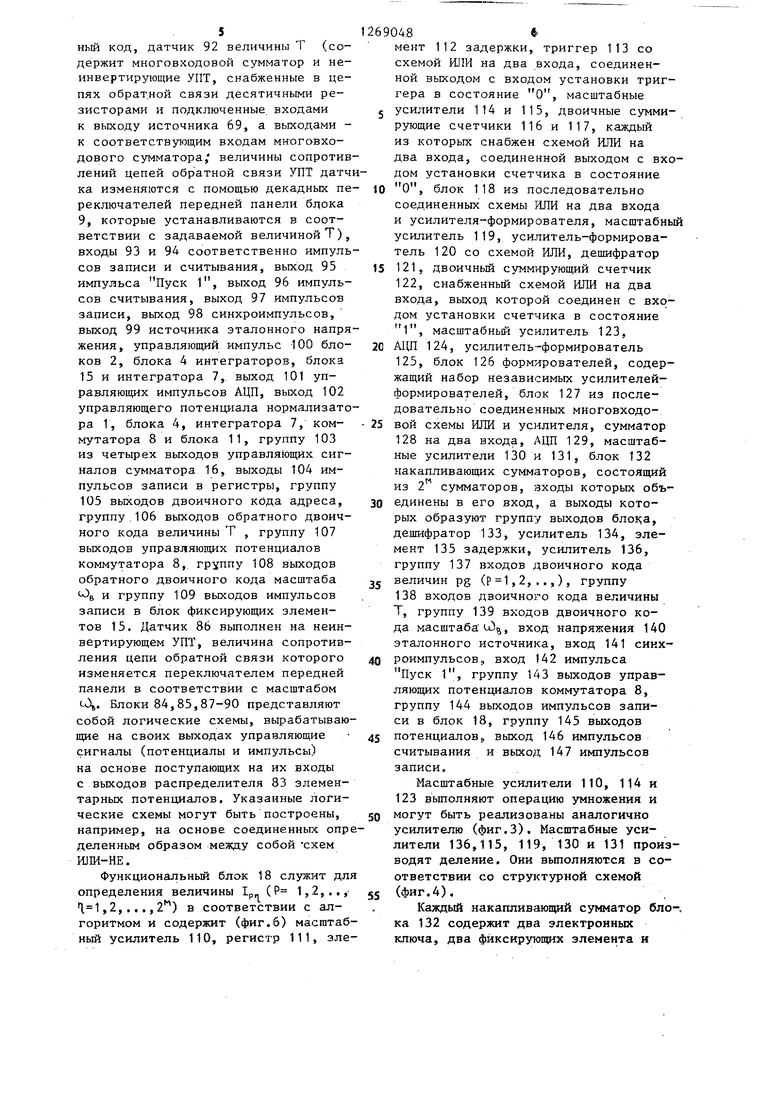

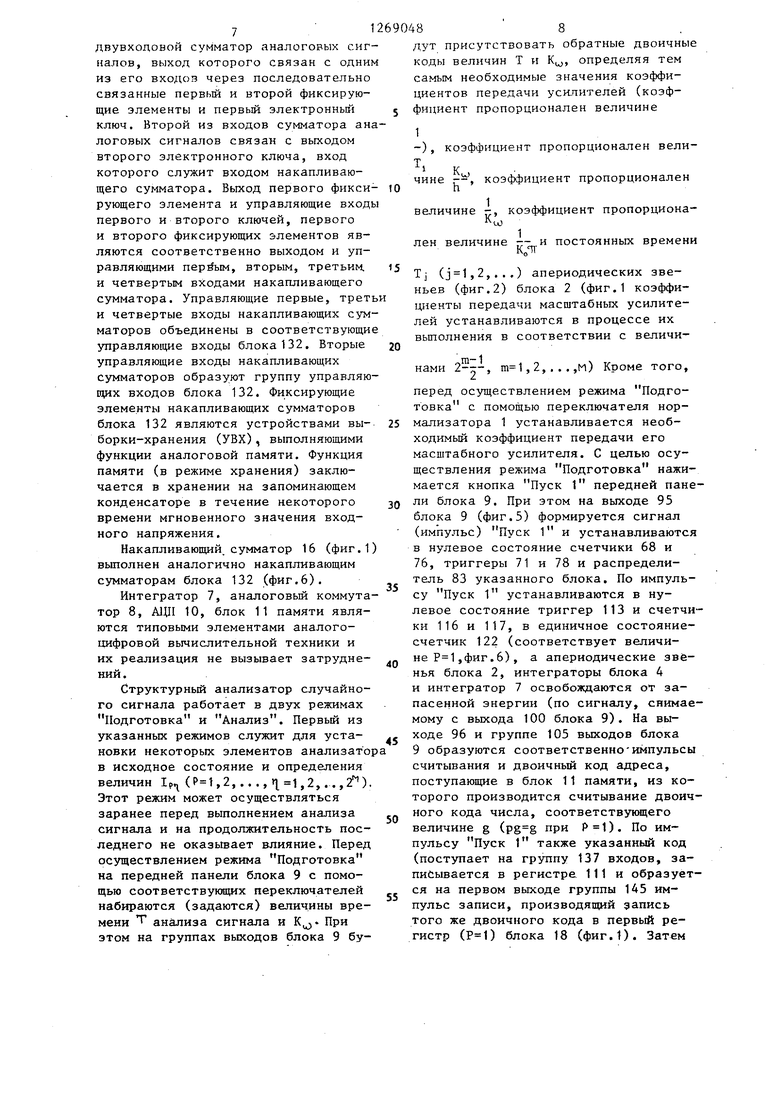

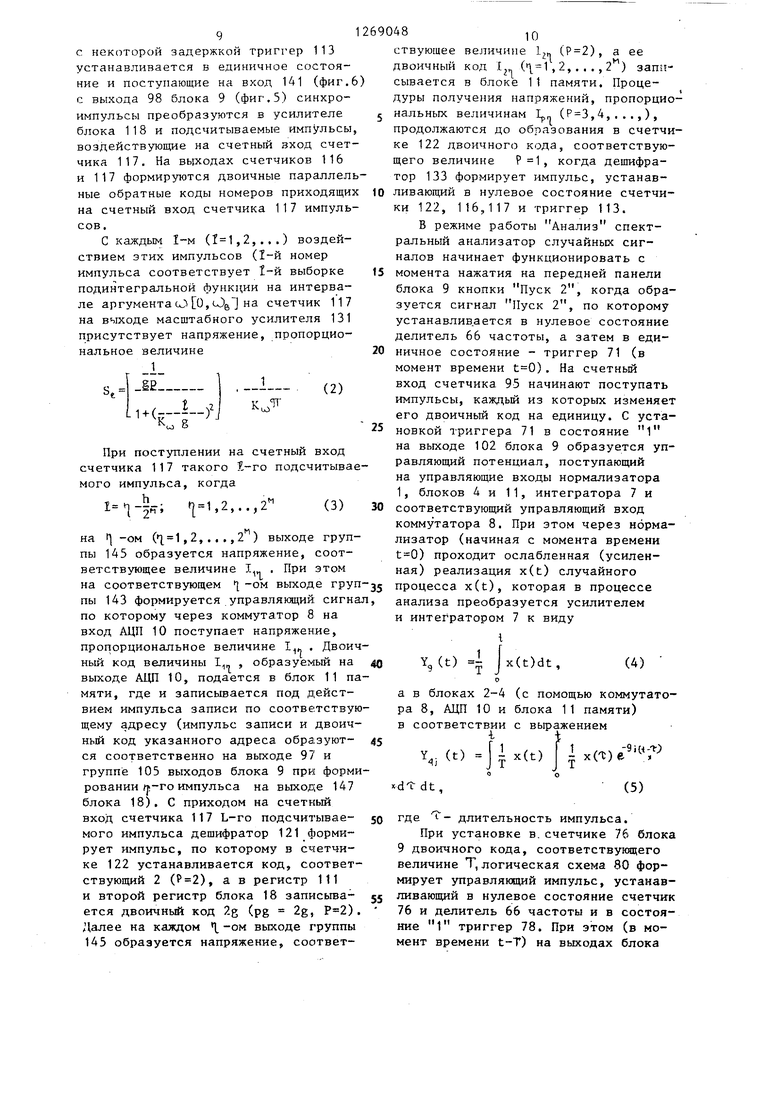

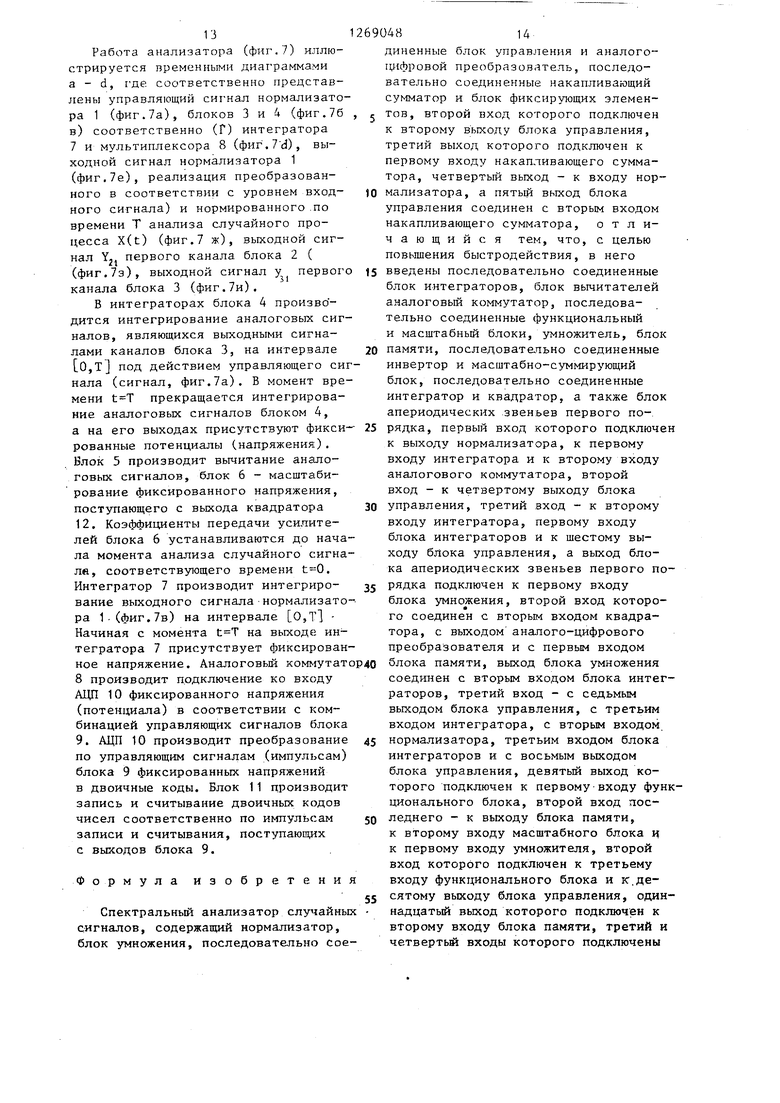

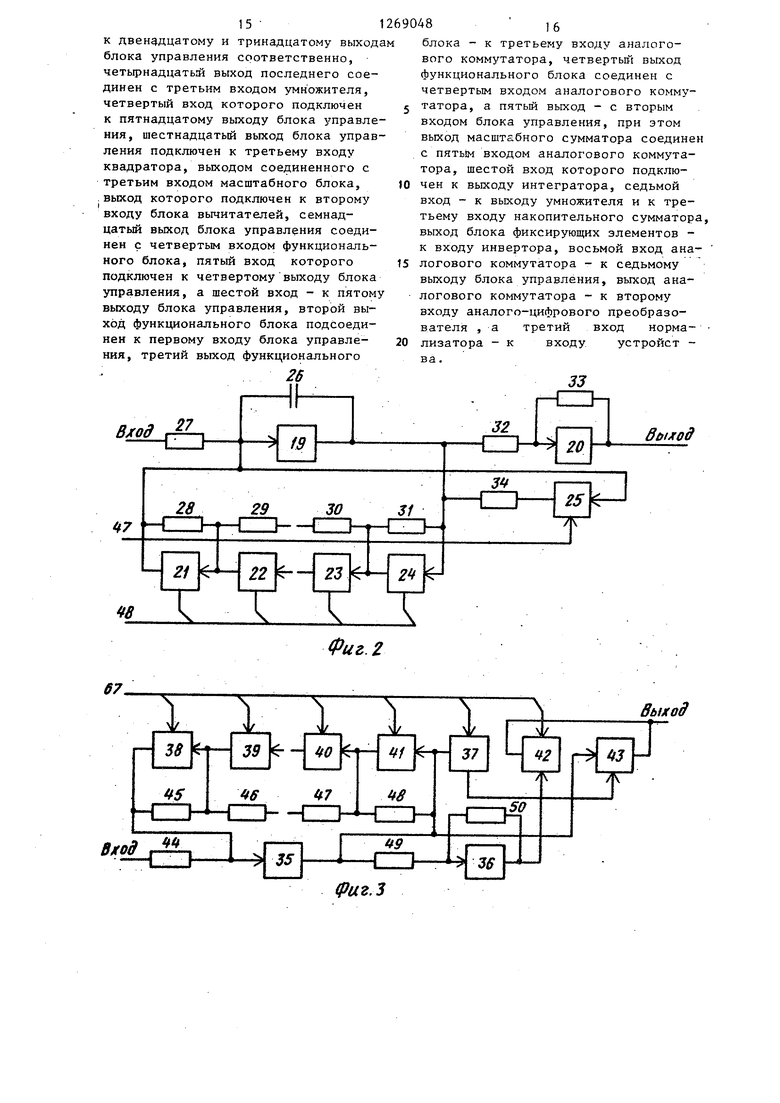

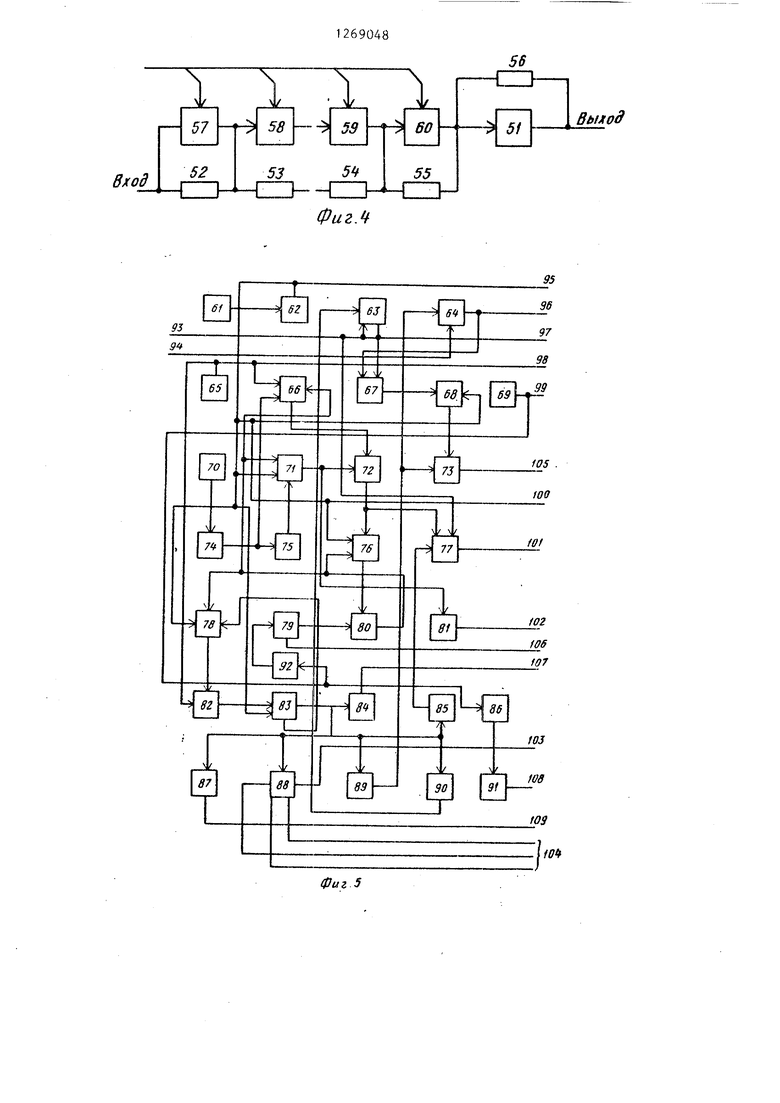

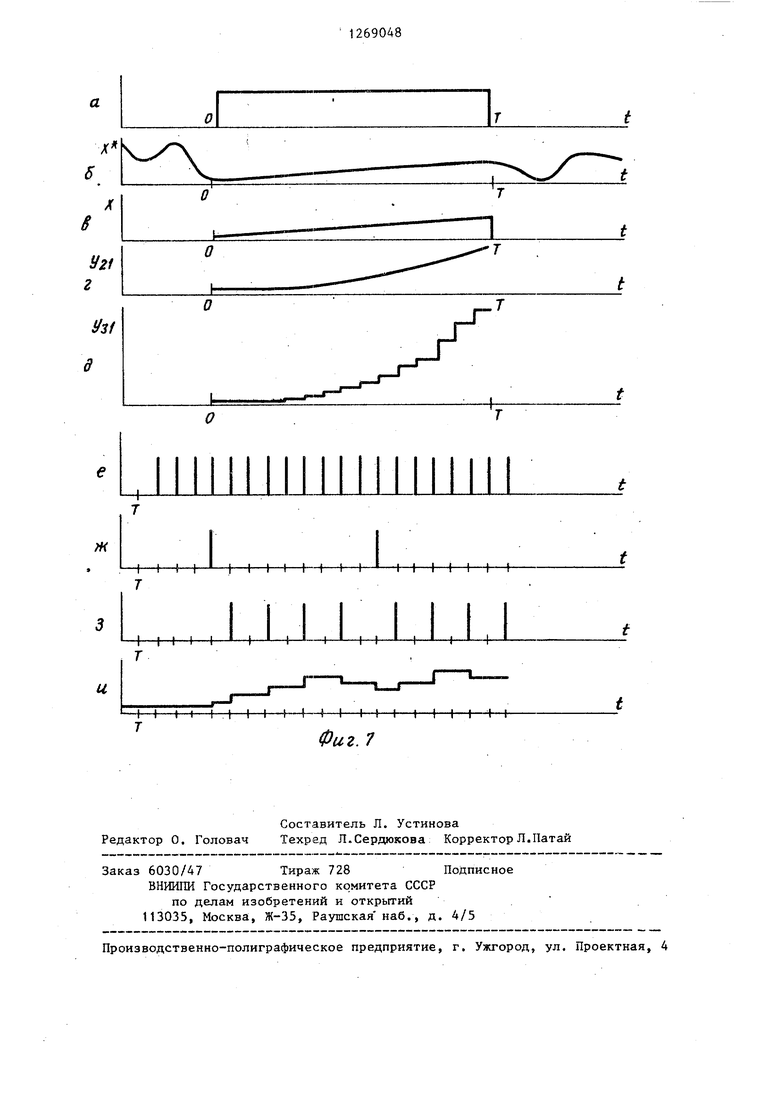

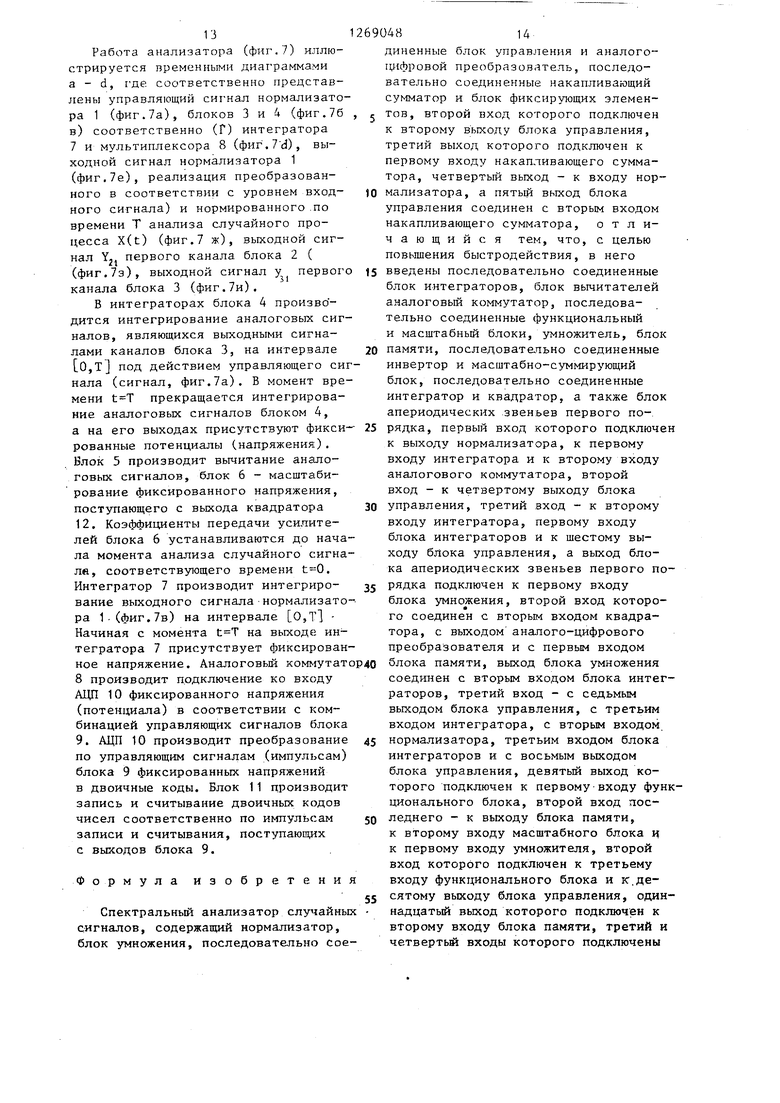

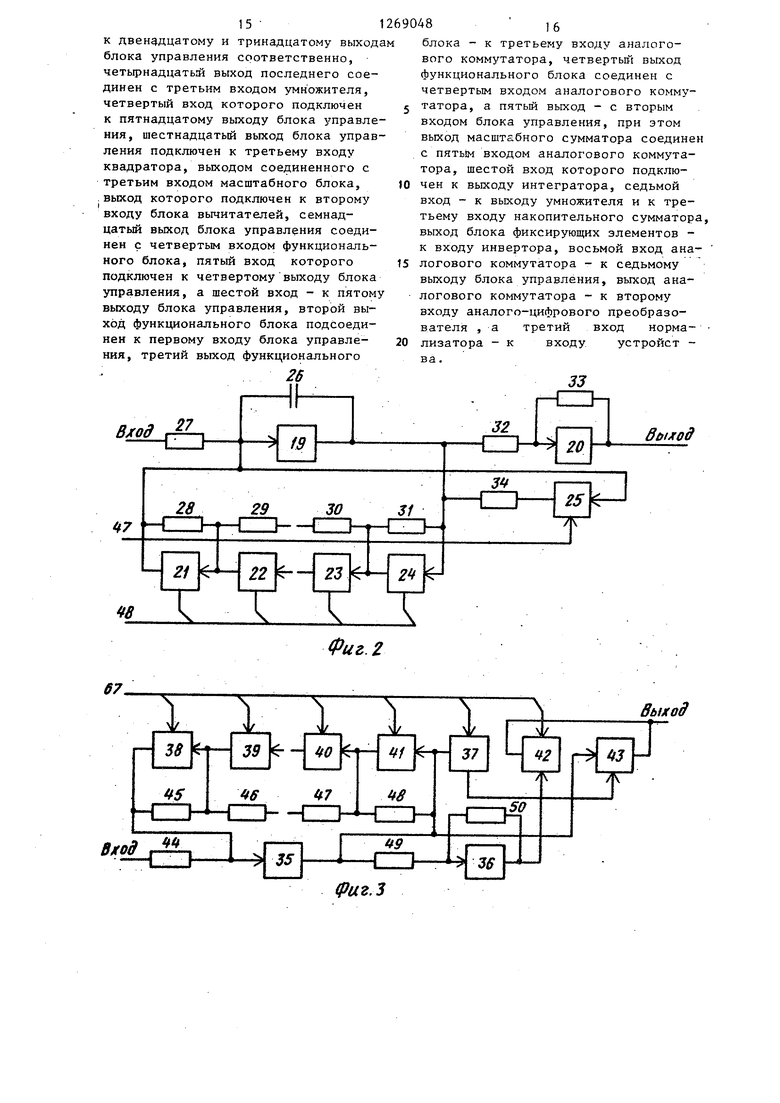

i Изобретение относится к специализированным средствам вычислительной техники, предназначенным для измерения характеристик случайных сигналов, и може.т найти применение при классификации аналоговых сигналов (например, электроэнцефалограмм, выходных сигналов САУ) на основе определения коэффициентов разложения спектральной плотности случайного процесса по базисной системе ортонор мированных на интервале 0,Т функций Хаара. Цель изобретения - повышение быст родействия путем уменьшения времени измерения спектральной плотности и получение аналитического предстйвления измеряемой функции на основе определения коэффициентов разложения указанной функции по базисной системе ортонормироваиных функций Хаара. На фиг.1 представлена структурная схема спектрального анализатора случайного сигнала; на фиг.2 - схема блока апериодических звеньев пер вого порядка; на фиг.З - схема умно жителя; на фиг.4 - схема масштабног блока; на фиг.З - схема блока управ ления, на фиг.6 - схема функциональ ного блока; на фиг.7 - временные диаграммы работы устройства. Спектральный анализатор случайны сигналов (фиг.1) содержит нормализатор 1, блок 2 апериодических звеньев первого порядка, блок 3 умноже ния, блок 4 интеграторов, блок 5 вычитателей, масштабный блок 6, интегратор 7, аналоговый коммутатор 8, блок 9 управления, аналого-цифровой преобразователь (АЦП) 10, блок 11 памяти, квадратор 12,, масштабно-суммирующий блок 13, инвертор 14, блок 15 фиксирующих элементов, накапливающий сумматор 16, умн житель 17 и функциональный блок 18. В анализаторе последовательно со динены нормализатор 1, связанньй входом с входом анализатора, а упра ляющим входом - с соответствующим выходом блока 9 управления, блок 2 апериодических звеньев первого порядка, блок 3 умножения, блок 4 интеграторов, блок 5 вычитателей, аналоговый коммутатор 8, аналогецифровой преобразователь 10, блок 11 памяти, масштабньй блок 6, выход которого подключен к второму входу 482 блока 5 вычитателей, последовательно соединены с блоком 11 памяти, умножитель 17, накапливающий сумматор 16, блок 15 фиксирующих элементов, инвертор 14 и масштабно-суммирующий блок 13. Нормализатор 1 служит для подачи анализируемого случайного сигнала на вход анализатора на время наблюдения PjT) и ослабления (усиления) его с целью удобства осуществления преобразования сигналов в анализаторе при определении коэффициентов разложения спектральной плотности анализируемого процесса. Он содержит последовательно соединенные электронный ключ и масштабный усилитель, коэффи циент передачи которого может быть установлен перед проведением анализа с помощью переключателя, осуществляющего изменение значений сопротивлений входного резистора и резистора цепи.обратной связи усилителя. Вход и управляющий вход ключа являются соответственно входом и управляющим входом нормализатора. Выходом последнего является выход масштабного усилителя. Блок 2 апериодических звеньев первого порядка состоит из набора звеньев с постоянными времени П. (j 1, 2, ...) ,выполненкьгх в виде инвертирующих усилителей 19 и 20 постоянного тока (УПТ), электронных ключей 21-25, конденсатора 26, входного регистра 27, двоичных резисторов 28-31 цепи обратной связи УПТ 19, входного резистора 32, резистора 33 цепи обратной связи УПТ 20 (величины сопротивлений указанных резисторов одинаковые), резистор 34 цепи разряда конденсатора 26 (освобождения апериодического звена от запасенной энергии). На группу клю й 21-24 поступает обратньш двоичный код, соответствующий величине интервала анализа сигнала Т. В блоке входы апериодических звеньев объединены соответственно во вход и управляющий вход блока. Выходами последнего являются выходы апериодических звеньев. Одноименные кодовые входы групп апериодических звеньев объединены в кодовые входы группы блока. Величины емкостей конденсаторов 26 выбираются в соответствии с постоянными времени Tj (,2,.. Клок 3 умножения содержит масшта ные усилители с регулируемым во вре мени коэффициентом передачи, изменяющимся в зависимости от обратных двоичных кодов мгновенных значений случайного сигнала, соответствующих дискретным моментам времени tg q дt q (q 0,1,2,3,...) (1 где йС (f- частота следований управляющих импульсов АЦП 10 в случае получения на выходе последнего обратных двоичных кодов мгновенных значений случайного сигнала). Масштабные усилители блока 3 содержат неинвертирующий 35 и инвертирующий 36 УПТ, инвертор 37, элект ронные ключи 38-43,входной резистор 44 и двоичные резисторы 45-48 цепи обратной связи УПТ 35, входной резистор 49 и резистор 50 цепи обратной связи УПТ 36. Блок 4 интеграторов состоит из набора интеграторов. Каждый из них снабжен входом, выходом и двумя управляющими входами Сброс и Интегрирование, Входы и вьпсоды интеграторов образуют группы соответственно входов и выходов блока 4. Одноименные управляющие входы ин теграторов объединены в два управляющих входа блока 4 Сброс и Интегрирование. При подаче на них уп равляющих сигналов производятся соответственно освобождение интеграторов от запасенной энергии и интег рирование. Блок 5 вычитателей состоит из на бора вьмитателей. Каждый из них содержит инвертор и сумматор на два входа, один из которых соединен с выходом инвертора. Одним входом вычитателя является вход инвертора, а другим - соответствуюпщй вход сум матора. Выходом вычитателя служит выход сумматора. Входы и выходы вычитателей образуют группы соответст венно входов и выходов блока. Масштабный блок 6 сос.тоит из набора масштабных усилителей, (фиг.4) Каждый такой усилитель содержит неинвертирующий УПТ 51 двоичных резис торов 52-55, образующих входное сопротивление УПТ 51, резистор 56 цеп обратной связи УПТ, электронные клю 57-60, а также вход, выход и группу кодовых входов. Блок управления (фиг.5) служит для формирования управляющих сигналов (импульсов и потенциалов) и содержит блок 61 формирования сигнала Пуск 1 (образуется при .нажатии на соответствующую кнопку передней панели блока), усилитель 62, блок 63 из последовательно соединенных схемы Ш1И на два входа и усилителя, блок 64 из последовательно соединенных схемы ИЛИ на два входа и усилителя, высокостабильньй по частоте следования импульсов задающий генератор 65, делитель 66 частоты со схемой ИЛИ на два входа, соединенной выходом с входом делителя Установка в О, блок 67 из последовательно соединенных схемы ИЛИ на два входа и усилителя, двоичный суммирующий счетчик 68, источник 69 эталонного напряжения, блок 70 формирования сигнала Пуск 2 (образуется при нажатии на соответствующую кнопку передней панели блока 9), триггер 71 со схемой Ш1И на два входа, выход которой соединен с входом установки триггера в состояние О, блок 72 из последовательно соединенных схемы И на два входа и усилителя, блока 73 памяти, усилитель 74, элемент 75 задержки, двоичный суммирующий счетчик 76 со схемой ИЛИ на два входа, соединенной выходом с входом счетчика Установка в О, блок 77 из последовательно соединенных схемы ИЛИ на три входа усилителя, триггер 78 со схемой ИЛИ на два входа, соединенной выходом с входом установки триггера в состояние О, преобразователь 79 десятичного кода в двоичный, логическую схему 80 (содержит набор схем И и вьдает на выходе сигнал при образовании на выходах счетчика 76 двоичного кода, соответствующего величине Т), усилитель 81, блок 82 из последовательно соединенных схемы И на два входа и усилителя, распределитель 83 импульсов, блок 84 управляющих потенциалов коммутатора 8, блок 85 управляющих импульсов 10, датчик 86 масштаба ь (W)- верхняя граничная частота спектральной плотности случайного сигнала), блок 87 импульсов записи в блок 24, блок 88 импульсов записи, блок 89 импульсов считьшания, блок 90импульсов записи, преобразователь 91десятичного кода в обратный двоич5

ный код, датчик 92 величины Т (содержит многовходовой сумматор и неинвертирующие УНТ, снабженные в цепях обрат.ной связи десятичными резисторами н подключенные, входами к выходу источника 69, а выходами к соответствующим входам мн-огавходового сумматора, величины сопротивлений цепей обратной связи УПТ датчка изменяются с помощью декадных переключателей передней панели бдока 9, которые устанавливаются в соответствии с задаваемой величиной), входы 93 и 94 соответственно импульсов записи и считывания, выход 95 импульса Пуск 1, выход 96 импульсов считывания, выход 97 импульсов записи, выход 98 синхроимпульсов, выход 99 источника эталонного напряжения, управляющий импульс 100 блоков 2, блока 4 интеграторов, блока 15 и интегратора 7, выход 101 управляющих импульсов АЦП, выход 102 управляющего потенциала нормализатора 1, блока 4, интегратора 7, коммутатора 8 и блока 11, группу 103 из четырех выходов управляющих сигналов сумматора 16, выходы 104 импульсов записи в регистры, группу 105 выхрдов двоичного кода адреса, группу. 106 выходов обратного двоичного кода величины Т , группу 107 выходов управляющих потенциалов коммутатора 8, группу 108 выходов обратного двоичного кода масштаба в и группу 109 выходов импульсов записи в блок фиксирующих Элементов 15. Датчик 86 выполнен на неинвертирующем УПТ, величина сопротивления цепи обратной связи которого изменяется переключателем передней панели в соответствии с масштабом и. Блоки 84,85,87-90 представляют собой логические схемы, вырабатывающие на своих выходах управляющие сигналы (потенциалы и импульсы.) на основе поступающих на их входы с выходов распределителя 83 элементарных потенциалов. Указанные логические схемы могут быть построены, например, на основе соединенньпс определенным образом между собой схем ШШ-НЕ.

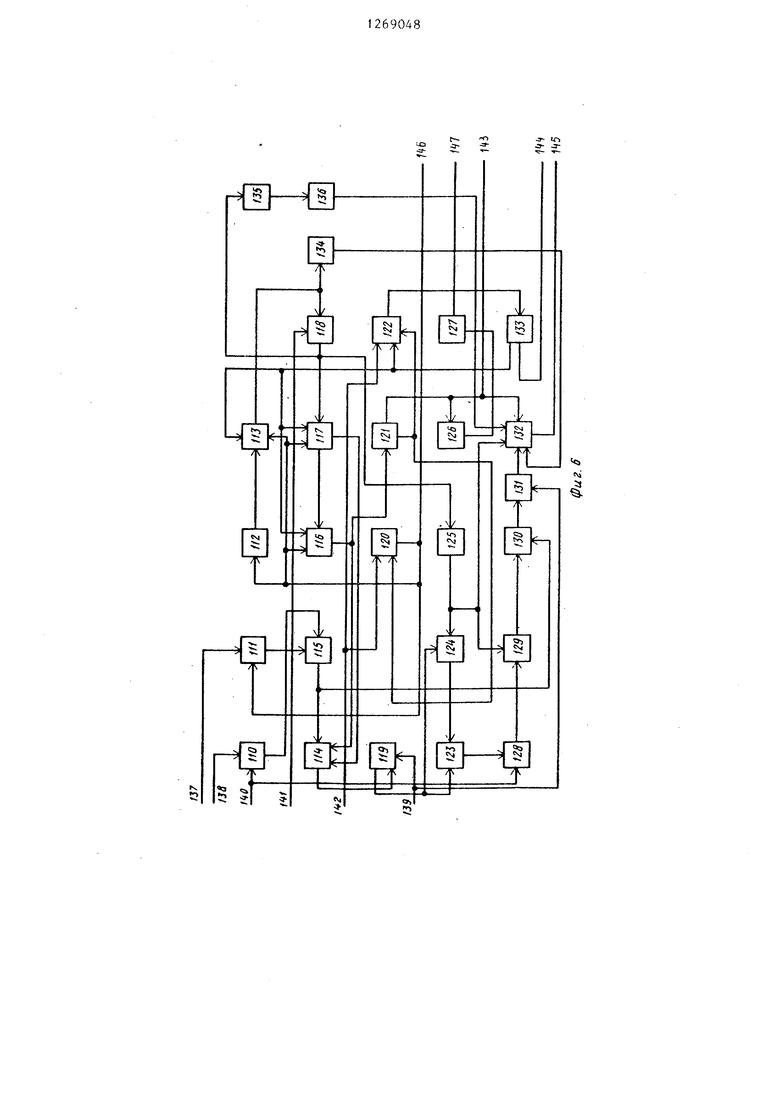

Функциональный блок 18 служит для определения величины 1р (Р 1,2,..,,2,...,2) в соответствии с алгоритмом и содержит (фиг,6) масштабный усилитель 110, регистр 111, зле048«.

мент 112 задержки, триггер 113 со схемой ИЛИ на два входа, соединенной выходом с входом установки триггера в состояние О, масштабные усилители 114 и 115, двоичные суммирующие счетчики 116 и 117, каждый из которых снабжен схемой ИЛИ на два входа, соединенной выходом с входом установки счетчика в состояние О, блок 118 из последовательно соединенных схемы ИЛИ на два входа и усилителя-формирователя, масштабный усилитель 119, усилитель-формирователь 120 со схемой ИЛИ, дешифратор 121, двоичный суммирующий счетчик 122, снабженный схемой ИЛИ на два входа, выход которой соединен с входом установки счетчика в состояние 1, масштабньм усилитель 123,

А1Щ 124, усилитель-формирователь

125, блок 126 формирователей, содержащий набор независимых усилителейформирователей, блок 127 из последовательно соединенных многовходовой схемы ШШ и усилителя, сумматор 128 на два входа, АЦП 129, масштабные усилители 130 и 131, блок 132 накапливающ11х сумматоров, состоящий из 2 сумматоров, входы которых объединены в его вход, а выходы которых образуют группу выходов блока, дещифратор 133, усилитель 134, элемент 135 задержки, усилитель 136, группу 137 входов двоичного кода

величин pg (,2,,,,), группу

138 входов двоичного кода величины Т, группу 139 входов двоичного кода масщтабаиЗ, вход напряжения 140 эталонного источника, вход 141 сикхроимпульсов,, вход 142 импульса

Пуск 1, группу 143 выходов управляющих потенциалов коммутатора 8, группу 144 выходов импульсов записи в блок 18, группу 145 выходов

потенциалов,, выход 146 импульсов считывания и выход 147 импульсов записи,

Масщтабные усилители 110, 114 и 123 выполняют операцию умножения и

могут быть реализованы аналогично усилителю (фиг,Э). Масштабные усилители 136,115, 119, 130 и 131 производят деление. Они выполняются в соответствии со структурной схемой

(фиг.4).

Каждый накапливающий сумматор блока 132 содержит два электронных ключа, два фиксирующих элемента и двувходовои сумматор аналоговых сиг налов, выход которого связан с одни из его входов через последовательно связанные перв(1й и второй фиксирующие элементы и первьй электронньш ключ. Второй из входов сумматора ан логовых сигналов связан с выходом второго электронного ключа, вход которого служит входом накапливающего сумматора. Вькод первого фикси рующего элемента и управляющие вход первого и второго ключей, первого и второго фиксирующих элементов являются соответственно выходом и управляющими первым, вторым, третьим, и четвертым входами накапливающего сумматора. Управляющие первые, трет и четвертые входы накапливающих сум маторов объединены в соответствующи управляю1цие входы блока 132. Вторые управляющие входы накапливающих сумматоров образуют группу управляю щих входов блока 132. Фиксирующие элементы накапливающих сумматоров блока 132 являются устройствами выборки-хранения (УВХ), выполняющими функции аналоговой памяти. Функция памяти (в режиме хранения) заключается в хранении на запоминающем конденсаторе в течение некоторого времени мгновенного значения входного напряжения. Накапливающий, сумматор 16 (фиг.1 выполнен аналогично накапливающим сумматорам блока 132 (фиг.6). Интегратор 7, аналоговый коммута тор 8, АЦП 10, блок 11 памяти являются типовыми элементами аналогоцифровой вычислительной техники и их реализация не вызывает затруднений. Структурный анализатор случайного сигнала работает в двух режимах Подготовка и Анализ. Первый из указанных режимов служит для установки некоторых элементов анализато в исходное состояние и определения величин Ip. (,2,...,,2,..,) Этот режим может осуществляться заранее перед выполнением анализа сигнала и на продолжительность последнего не оказывает влияние. Перед осуществлением режима Подготовка на передней панели блока 9 с помощью соответствующих переключателей набираются (задаются) величины времени анализа сигнала и . При этом на группах выходов блока 9 будут присутствовать обратные двоичные коды величин Т и К, определяя тем самьм необходимые значения коэффициентов передачи усилителей (коэффициент пропорционален величине -), коэффициент пропорционален величине г коэффициент пропорционален h величине -, коэффициент пропорционален величине --ч постоянных времени Tj (,2,...) апериодических звеньев (фиг.2) блока 2 (фиг.1 коэффициенты передачи масштабных усилителей устанавливаются в процессе их выполнения в соответствии с величинами 2---, ,2,...,м) Кроме того, перед осуществлением режима Подготовка с помоЩью переключателя нормализатора 1 устанавливается необходимый коэффициент передачи его масштабного усилителя. С целью осуществления режима Подготовка нажимается кнопка Пуск 1 передней панели блока 9. При этом на выходе 95 блока 9 (фиг.5) формируется сигнал (импульс) Пуск 1 и устанавливаются в нулевое состояние счетчики 68 и 76, триггеры 71 и 78 и распределитель 83 указанного блока. По импульсу Пуск 1 устанавливаются в нулевое состояние триггер 113 и счетчики 116 и 117, в единичное состояниесчетчик 122 (соответствует величине ,фиг.6) , а апериодические звенья блока 2, интеграторы блока 4 и интегратор 7 освобождаются от запасенной энергии (по сигналу, снимаемому с выхода 100 блока 9). На выходе 96 и группе 105 выходов блока 9 образуются соответственно-импульсы считывания и двоичный код адреса, поступающие в блок 11 памяти, из которого производится считывание двоичного кода числа, соответствующего величине g ( при Р 1) . По импульсу Пуск 1 также указанный код (поступает на группу 137 входов, записывается в регистре 111 и образуется на первом выходе группы 145 импульс записи, производящий запись того же двоичного кода в первый регистр () блока 18 (фиг.1). Затем 91 с некоторой задержкой триггер 113 устанавливается в единичное состояние и поступающие на вход 141 (фиг,6 с выхода 98 блока 9 (фиг.5) синхроимпульсы преобразуются в усилителе блока 118 и подсчитываемые импульсы, воздействующие на счетный вход счетчика 117, На выходах счетчиков 116 и 117 формируются двоичные параллель ные обратные коды номеров приходящих на счетный вход счетчика 117 импульС каждым 1-м (,2,,,.) воздействием этих импульсов (1-й номер импульса соответствует 1-й выборке подинтегральной функции на интервале аргумента О О, OB на счетчик 117 на выходе масштабного усилителя 131 присутствует напряжение, пропорциональное величине 1 ,, qy Lu(При поступлении на счетный вход счетчика 117 такого ,-го подсчитывае мого импульса, когда 1.2,,,,2 на f -ом (1 1,2, ,. . ,2) выходе группы 145 образуется напряжение, соответствующее величине 1,„ . При этом на соответствующем выходе rpyn пы 143 формируется управляющий сигна по которому через коммутатор 8 на вход АЦП 10 поступает напряжение, пропорциональное величине 1, . Двоич ный код величины , образуемый на выходе АЦП 10, подается в блок 11 па мяти, где и записывается под действием импульса записи по соответствую щему адресу (импульс записи и двоичный код указанного адреса образуются соответственно на выходе 97 и группе 105 выходов блока 9 при форми ровании fj;-ro импульса на выходе 147 блока 18). С приходом на счетный вход счетчика 117 L-ro подсчитываемого импульса дешифратор 121 формирует импульс, по которому в счетчике 122 устанавливается код, соответ ствующий 2 (), а в регистр 111 и второй регистр блока 18 записывается двоичный код 2g (pg 2g, ) Далее на каждом , -ом выходе группы 145 образуется напряжение, соответ48ствующее величине 1.„ (Р 2), а ее двоичный код I (1 , 2,, . ,, 2) записывается в блоке 11 памяти. Процедуры получения напряжений, пропорциональных величинам 1р„ (,4,,,,,), продолжаются до образования в счетчике 122 двоичного кода, соответствующего величине Р 1, когда дешифратор 133 формирует импульс, устанавливающий в нулевое состояние счетчики 122, 116,117 и триггер 113. В режиме работы Анализ спектральный анализатор случайных CHI- налов начинает функционировать с момента нажатия на передней панели блока 9 кнопки Пуск 2, когда образуется сигнал Пуск 2, по которому устанавливается в нулевое состояние делитель 66 частоты, а затем в единичное состояние - триггер 71 (в момент времени ) , На счетньш вход счетчика 95 начинают поступать импульсы, каждый из которых изменяет его двоичный код на единицу. С установкой триггера 71 в состояние 1 на выходе 102 блока 9 образуется управляющий потенциал, поступающий на управляющие входы нормализатора 1, блоков 4 и 11, интегратора 7 и соответствующий управляющий вход коммутатора 8, При этом через нормализатор (начиная с момента времени ) проходит ослабленная (усиленная) реализация x(t) случайного процесса x(t), которая в процессе анализа преобразуется усилителем и интегратором 7 к виду 1 Y, (t) x(t)dt. а в блоках 2-4 (с помощью коммутатора 8, АЦП 10 и блока 11 памяти) в соответствии с вьфажением (t) ||x(t) -) df dt. где I- длительность импульса. При установке в. счетчике 76 блока 9 двоичного кода, соответствукядего величине Т, логическая схема 80 формирует управляющий импульс, устанавливающий в нулевое состояние счетчик 76 и делитель 66 частоты и в состояние 1 триггер 78. При этом (в момент времени t-T) на выходах блока пряжения, пропорциональные величина соответственно 1 .. . f 1 (Т) 1 x(t) ™ х(т)е J t -( Y, (Т) J x{t)dt Ha выходе 102 блока 9 исчезает управляющий потенциал и прекращается прохождение через нормализатор 1 си нала x(t). На этом этап анализа указанного сигнала, осуществляемый на интервале 10,т заканчивается. Дальше производятся быстро выполнимые операции при единичном состоянии триггера 78, скорость осуществл ния которых определяется частотой следования импульсов задающего гене ратора 65 блока 9, При этом на вход распределителя 83 с выхода усилител 82 поступают импульсы. На выходах указанного распределителя образуются элементарные сигналы (потенциалы поступающие на входы блоков 84,85,8 90. На основе элементарных сигналов распределителя формируются управлящие работой анализатора сигналы (импульсы и потенциалы) на выходах блоков 84,87 и 88 и импульсы, из которых с помощью блоков 63,64 и 77 обра зуются импульсы записи, считывания и управляющие импульсы АЦП 10, на вы ходах блоков соответственно 85,89 и 90. Импульсы записи и считывания через схему ИЛИ и усилитель (блок 7) поступают на счетный вход счетчика 68. При этом на выходах группы 105 формируются двоичные коды адресов. Сразу же после образования напряжений (6), (7), напряжение (7) через коммутатор 8 поступает на вход АЦП 10, где преобразуется в двоичный код. При этомна выходах блоков 6 и образуются напряжения, соответствующие величинам Y. Yg (Т) (Т) - Y Напряжения (10) через коммутатор 8 последовательно подаются на вход АЦП 10, где преобразуются в двоичные коды. Последние записываются в соотпамяти. Далее в анализаторе случайных сигналов производится выполнение операций в соответствии с алгоритмом. При этом вначале для каждого ,2,...,1 определяются произведения, двоичные коды которых считываются из ячеек памяти блока 11 памяти и записываются в регистры, обеспечивая тем самым соответствующие значения коэффициентов передачи усилителей. Напряжения (пропорциональные величинам Р.р (,2,..,, j 1,2,...,i, р 1,2,...,i), образуемые на выходе усилителя, через коммутатор 8 поступают на вход АДП 10. Полученные в нем двоичные коды записываются в соответствующие ячейки блока 11 памяти. Затем для f 1 и каждого ,2,...1 вьиислятся произведения 1,2,...i, (11) р 1,2-,.. . i сомножителей Р, jp 1 j-p, , двоичные коды которых считываются из блока 11 памяти и записываются в регистры. Каждое из полученных на выходе напряжений (соответствующих величинам PUPI) последовательно поступает на вход накопительного сумматора 16. После поступления на вход сумматора 16 напряжения произведения (, , ) на его выходе формируется напряжение, пропорциональное величине Ij. Это напряжение запоминается в первом фиксирующем элементе блока 15. Аналогично напряжению 1 формируются и записьшаются в соответствующих элементах блока 15 и напряжения, пропорциональные величинам 1 (,3,...,2). блоке 15 На основе запомненных в напряжений 1„ (1,2,. . 2 ) на выходах формируются напряжения, пропорциот нальные значениям коэффициентов разложения S,K (,2,...,К) спектральной плотности S (О) стационарного эргодического случайного процесса x(t) по базису ортонормированных на интервале О,иЗ функций Хаара. Напряжения 3| (,2,.. . ,К) через коммутаторы 8 последовательно подаются на вход АЦП 10 и преобразуются там в двоичные коды, которые затем записываются в соответствующие ячейки блока 11 памяти. Работа анализатора (фиг.7) иллюстрируется временными диаграммами а - d, где соответственно представлены управляющий сигнал нормализато ра 1 (фиг.7а), блоков 3 и 4 (фиг.76 в) соответственно (Г) интегратора 7 и мультиплексора 8 (фиг.7с1), выходной сигнал нормализатора 1 (фиг,7е), реализация преобразованного в соответствии с уровнем входного сигнала) и нормированного по времени Т анализа случайного процесса X(t) (фиг.7 ж), выходной сигнал YJJ первого канала блока 2 ( (фиг.7з), выходной сигнал у первог канала блока 3 (фиг.7и). В интеграторах блока 4 производится интегрирование аналоговых сиг налов, являющихся выходными сигналами каналов блока 3, на интервале о,т под действием управляющего си нала (сигнал, фиг.7а). В момент вре мени прекращается интегрирование аналоговых сигналов блоком 4, а на его выходах присутствуют фикси рованные потенциалы (напряжения). Блок 5 производит вычитание аналоговых сигналов, блок 6 - масштабирование фиксированного напряжения, поступающего с выхода квадратора 12. Коэффициенты передачи усилителей блока 6 устанавливаются до нача ла момента анализа случайного сигна ле, соответствующего времени . Интегратор 7 производит интегрирование выходного сигнала-нормализато ра 1.(фиг.7в) на интервале 0,Т1 Начиная с момента на выходе интегратора 7 присутствует фиксирован ное напряжение. Аналоговый коммутат 8 производит подключение ко входу АЦП 10 фиксированного напряжения (потенциала) в соответствии с комбинацией управляющих сигналов блока 9. АЦП 10 производит преобразование по управляющим сигналам (импульсам) блока 9 фиксированных напряжений в двоичные коды. Блок 11 производит запись и считывание двоичных кодов чисел соответственно по импульсам записи и считывания, поступаюпщх с выходов блока 9. Формула изобретени Спектральный анализатор случайны сигналов, содержащий нормализатор, блок умножения, последовательно сое диненные блок управления и аналого1Ц1фровой преобразователь, последовательно соединенные накапливающий сумматор и блок фиксирующих элементов, второй вход которого подключен к второму выходу блока управления, третий выход которого подключен к первому входу накапливающего сумматора, четвертый выход - к входу нормализатора, а пятый выход блока управления соединен с вторым входом накапливающего сумматора, отличающийся тем, что, с целью повьппения быстродействия, в него введены последовательно соединенные блок интеграторов, блок вьтитателей аналоговый коммутатор, последовательно соединенные функциональный и масщтабный блоки, умножитель, блок памяти, последовательно соединенные инвертор и масштабно-суммирующий блок, последовательно соединенные интегратор и квадратор, а также блок апериодических звеньев первого порядка, первый вход которого подключен к выходу нормализатора, к первому входу интегратора и к второму входу аналогового коммутатора, второй вход - к четвертому выходу блока управления, третий вход - к второму входу интегратора, первому входу блока интеграторов и к шестому выходу блока управления, а выход блока апериодических звеньев первого порядка подключен к первому входу блока умножения, второй вход которого соединен с вторым входом квадратора, с выходом аналого-цифрового преобразователя и с первым входом блока памяти, выход блока умножения соединен с вторым входом блока интеграторов, третий вход - с седьмым выходом блока управления, с третьим входом интегратора, с вторым входом нормализатора, третьим входом блока интеграторов и с восьмым выходом блока управления, девятый выход которого подключен к первому-входу функционального блока, второй вход последнего - к выходу блока памяти, к второму входу масштабного блока и к первому входу умножителя, второй вход которого подключен к третьему входу функционального блока и к.десятому выходу блока управления, одиннадцатый выход которого подключен к второму входу блока памяти, третий и четвертьй входы которого подключены к двенадцатому и тринадцатому выход блока управления соответственно, четьфнадцатьш выход последнего соединен с третьим входом умножителя, четвертый вход которого подключен к пятнадцатому выходу блока управле ния, шестнадцатый выход блока управ ления подключен к третьему входу квадратора, вькодом соединенного с третьим входом масштабного блока, .выход которого подключен к второму входу блока вычитателей, семнадцатый выход блока управления соединен с четвертым входом функционального блока, пятый вход которого подключен к четвертому выходу блока управления, а шестой вход - к пятом выходу блока управления, второй выход функционального блока подсоединен к первому входу блока управления, третий выход функционального

Af2./

ff7.

Выход 816 блока - к третьему входу аналогового коммутатора, четвертый выход функционального блока соединен с четвертым входом аналогового коммутатора, а пятый выход - с вторым входом блока управления, при этом выход масштабного сумматора соединен с входом аналогового коммутатора, шестой вход которого подключен к выходу интегратора, седьмой вход - к выходу умножителя и к третьему входу накопительного сумматора, выход блока фиксирующих элементов к входу инвертора, восьмой вход аналогового коммутатора - к седьмому выходу блока управления, выход аналогового коммутатора - к второму входу аналого-цифрового преобразователя , а третий вход норма- устроист лизаторава.

фиг.З

фиг 5

.3- to

2 5:

-Э- JЛ

У21

| Домарацкий А.Н | |||

| и др | |||

| Многоцел вой статистический анализ случайных сигналов | |||

| Новосибирск: -Наука, 1975, рис.15.17. |

Авторы

Даты

1986-11-07—Публикация

1984-01-27—Подача