1

Изобретение относится к техншсе контроля н может быть использовано при контроле систем автоматизированного и автоматического управления.

Цель изобретения - расширение функциональных возможностей устройства.

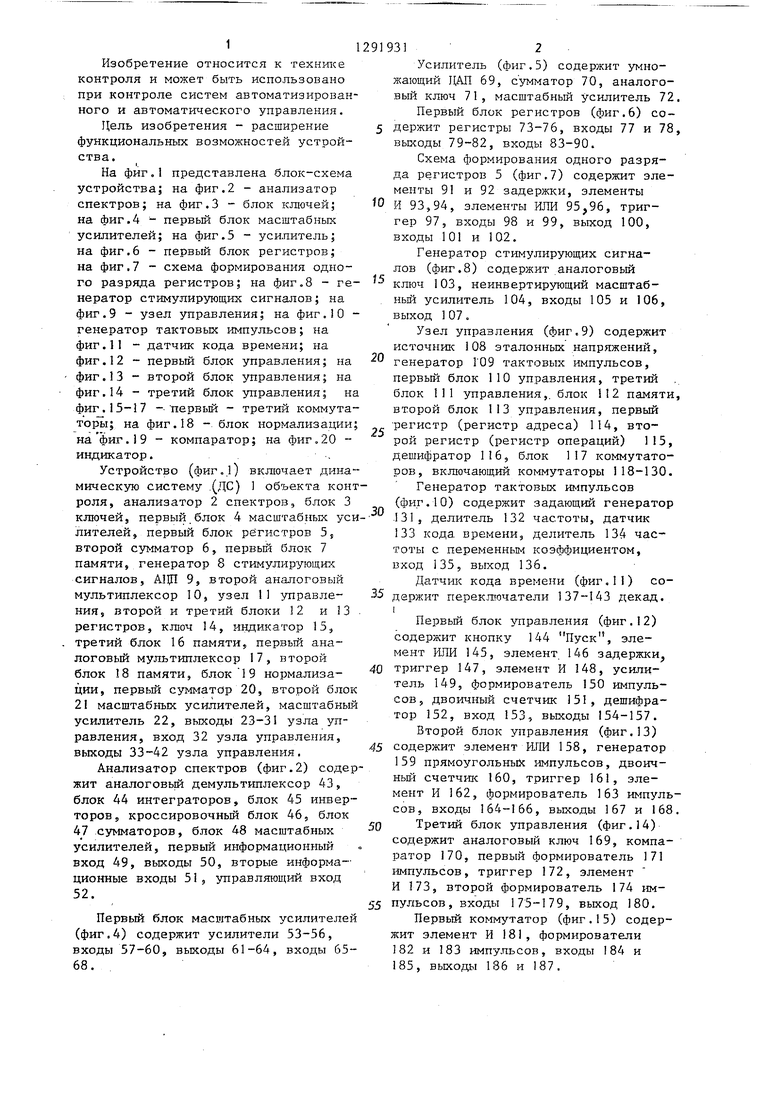

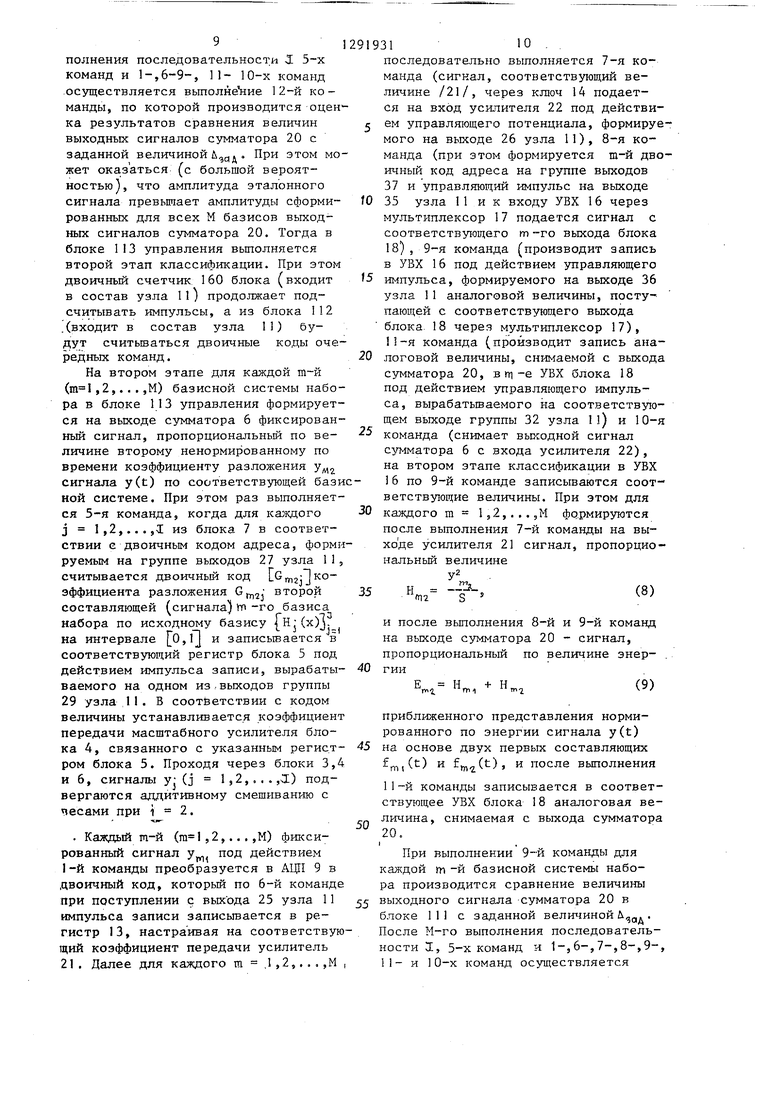

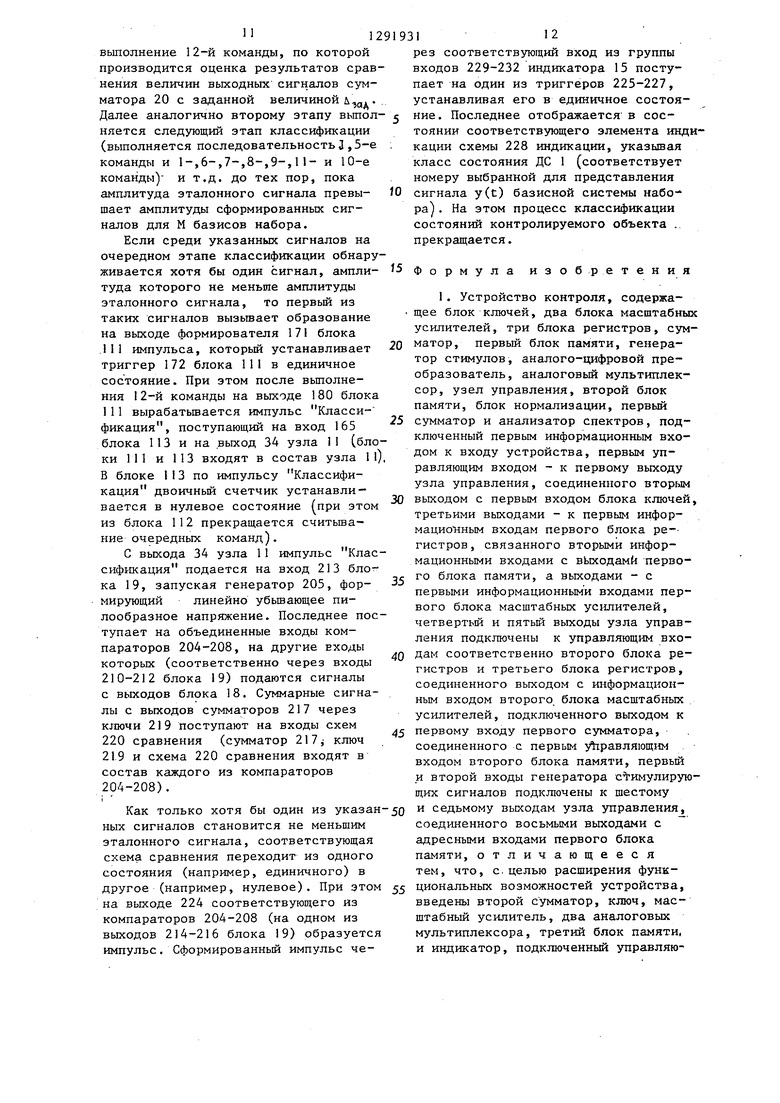

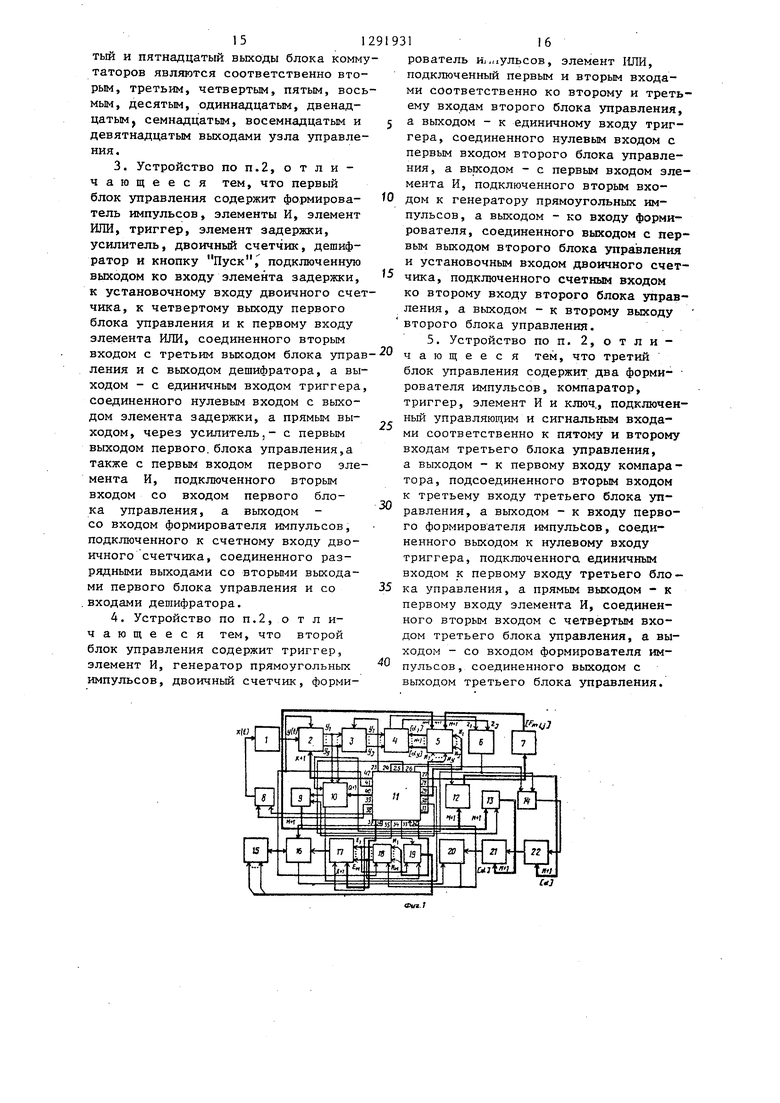

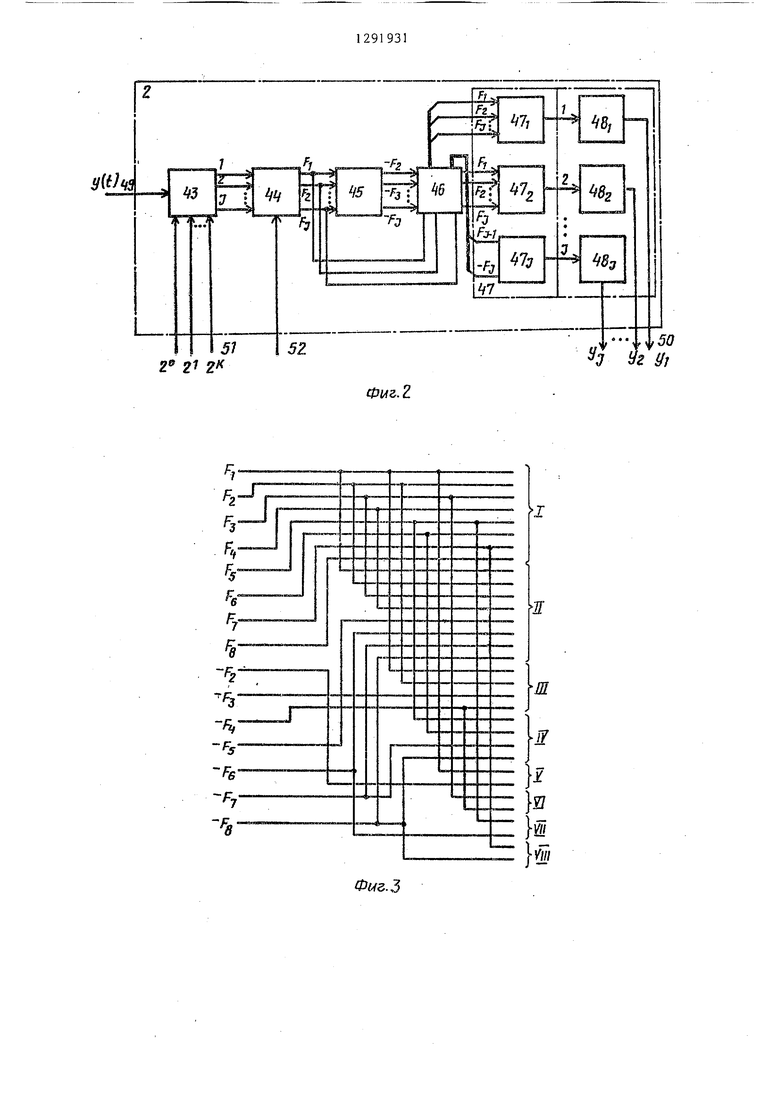

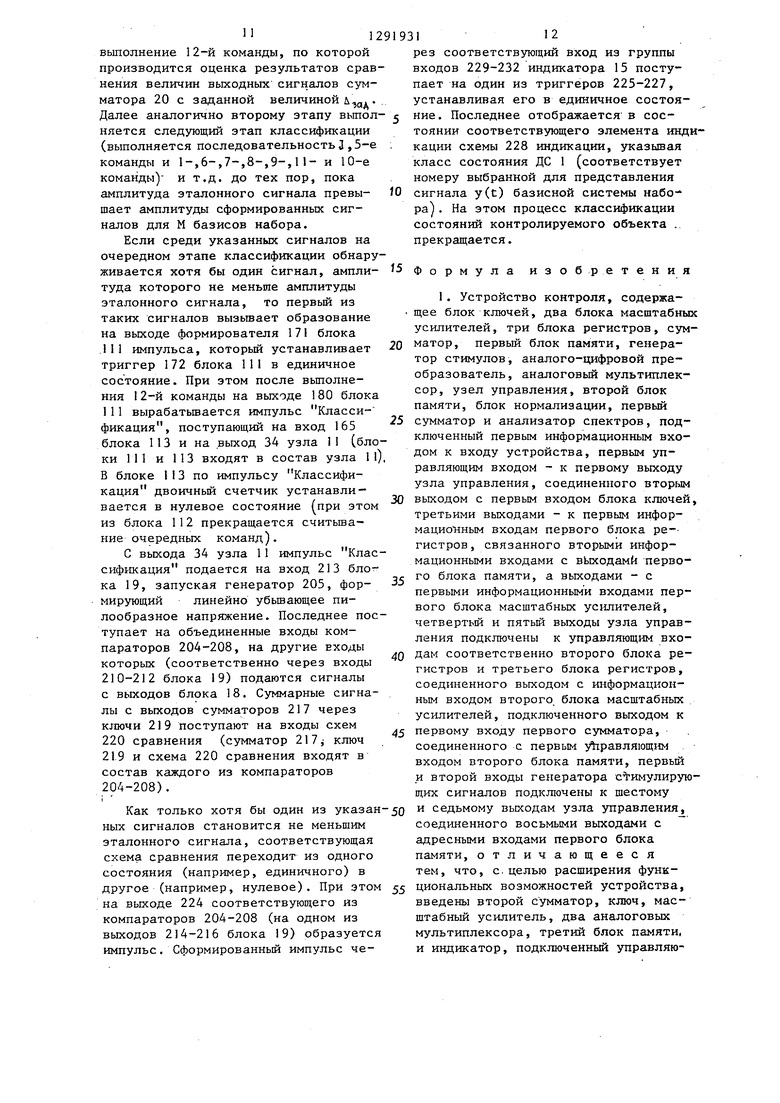

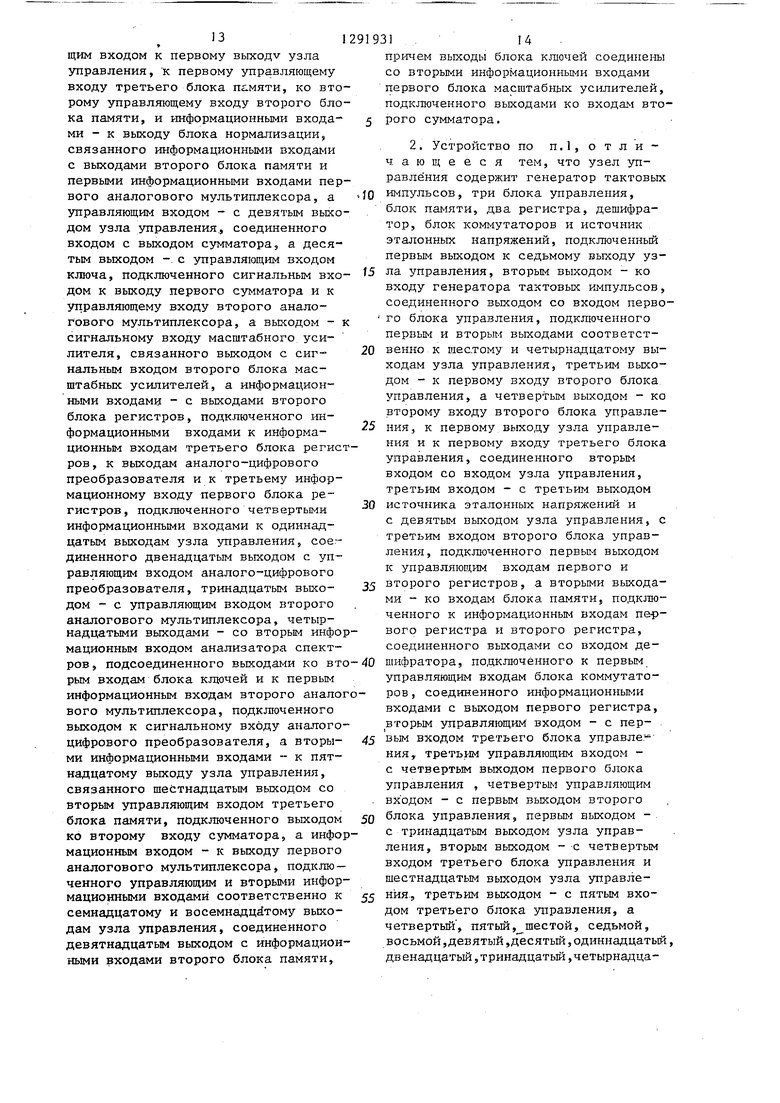

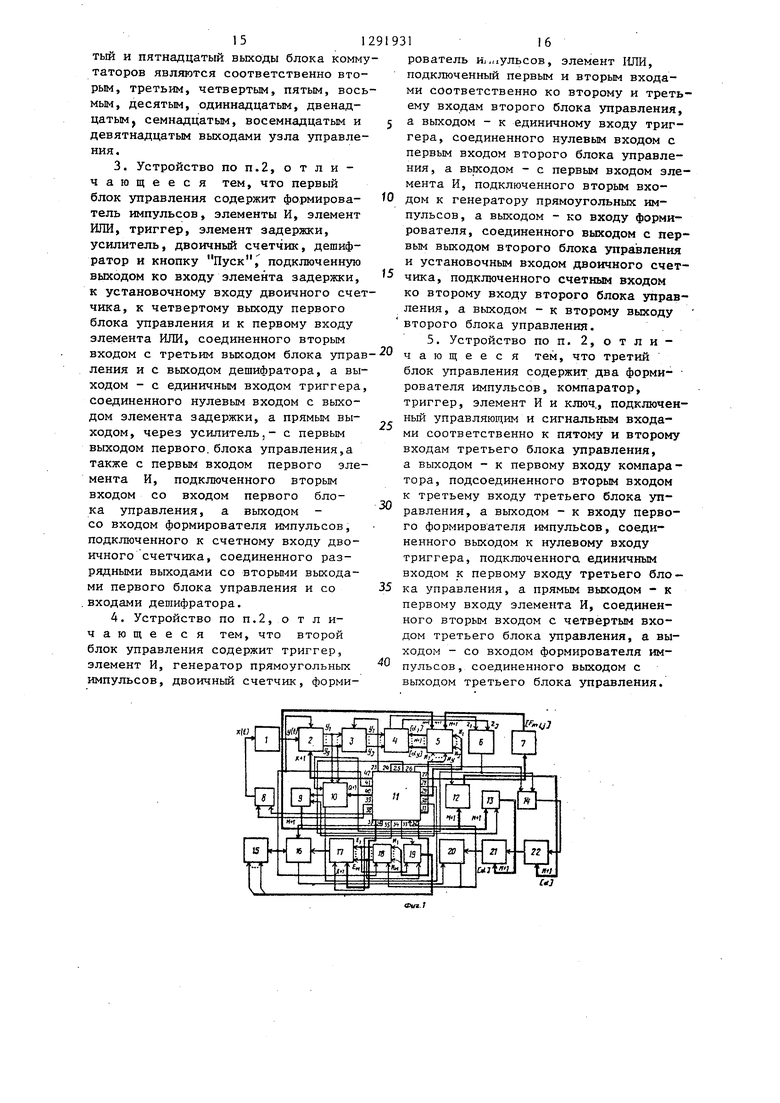

На фиг.1 представлена блок-схема устройства; на фиг.2 - анализатор спектров; на фиг.З - блок ключей; на фиг,4 - первый блок масштабных усилителей; на фиг.З - усилитель; на фиг.6 - первый блок регистров; на фиг.7 схема формирования одного разряда регистров; на фиг,8 - генератор стимулирующих сигналов; на фиг.9 - узел управления; на фиг.1 О - генератор тактовых импульсов; на фиг.1I - датчик кода времени; на фиг.12 - первый блок управления; на фиг.13 - второй блок управления; на фиг.14 - третий блок управления; на фиг. 15-17 - первьй - третий коммутаторы; на фиг.18 -- блок нормализации; на фиг.19 - компаратор; на фиг,20 - индикатор.

Устройство (фиг..О включает динамическую систему .(ЛС) 1 объекта контроля, анализатор 2 спектров, блок 3 ключей, первый,блок 4 масштабных усилителей первый блок регистров 5, второй сумматор 6, первьй блок 7 памяти, генератор 8 стимулирующих сигналов, А1Щ 9, второй аналоговый мультиплексор 10, узел 11 управления, второй и третий блоки 12 и 13 регистров, ключ 14, индикатор 15, третий блок 16 памяти, первый ана логовьй мультиплексор 17, второй блок 18 памяти, блок 19 нормализации, первьй сумматор 20, второй блок 21 масштабных усилителей, масштабньш усилитель 22, выходы 23-31 узла управления, вход 32 узла управления, выходы 33-42 узла управления.

Анализатор спектров (фиг.2) содержит аналоговьй демультиплексор 43, блок 44 интеграторов, блок 45 инверторов, кроссировочньй блок 46, блок 47 сумматоров, блок 48 масштабных усилителей, первый информационный вход 49, выходы 50, вторые информационные входы 51, управляющий вход 52.

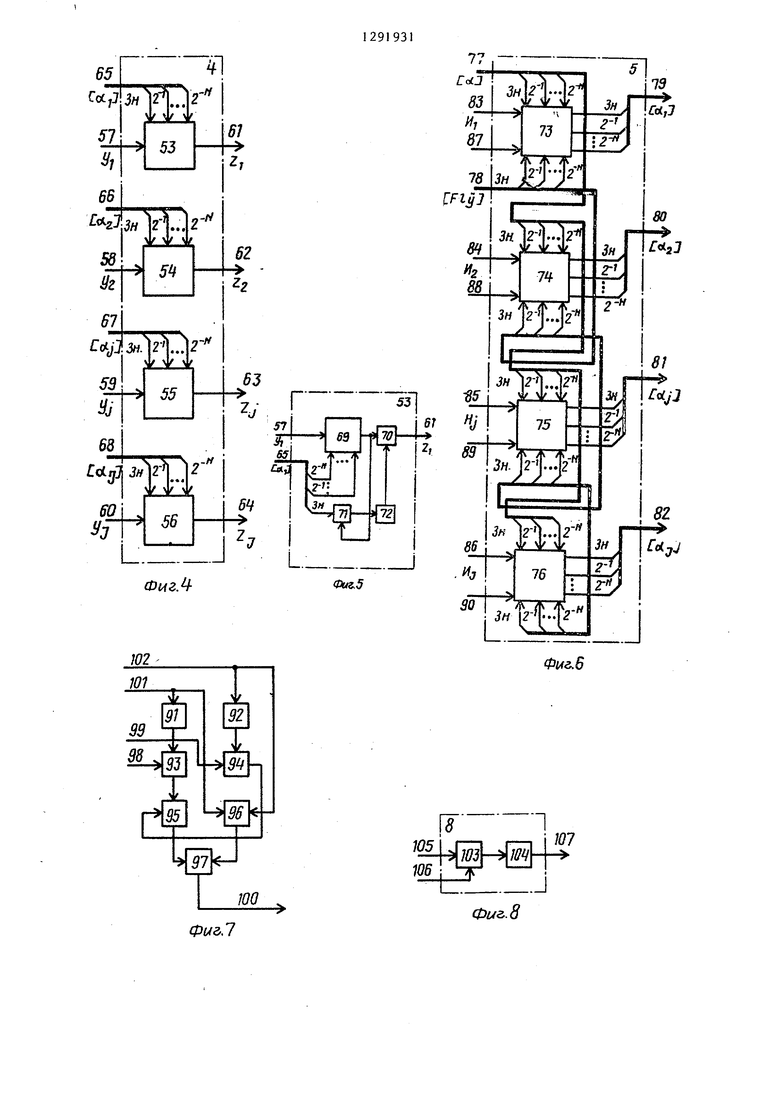

Первый блок масштабных усилителей (фиг.4) содержит усилители 53-56, входы 57-60, выходы 61-64, входы 65- 68.

to

15

20

25

919312

Усилитель (фиг.З) содержит умножающий ДАЛ 69, с умматор 70, аналоговый ключ 71, масштабньй усилитель 72.

Первый блок регистров (фиг.6) со- 5 держит регистры 73-76, входы 77 и 78, выходы 79-82, входы 83-90.

Схема формирования одного разряда регистров 5 (фиг.7) содержит элементы 91 и 92 задержки, злементы И 93,94, злементы ИЛИ 95,96, триггер 97, входы 98 и 99, выход 100, входы 101 и 102.

Генератор стимулирующих сигналов (фиг.8) содержит аналоговьй ключ 103, неинвертирующий масштабньй усилитель 104, входы 105 и 106, выход 107,

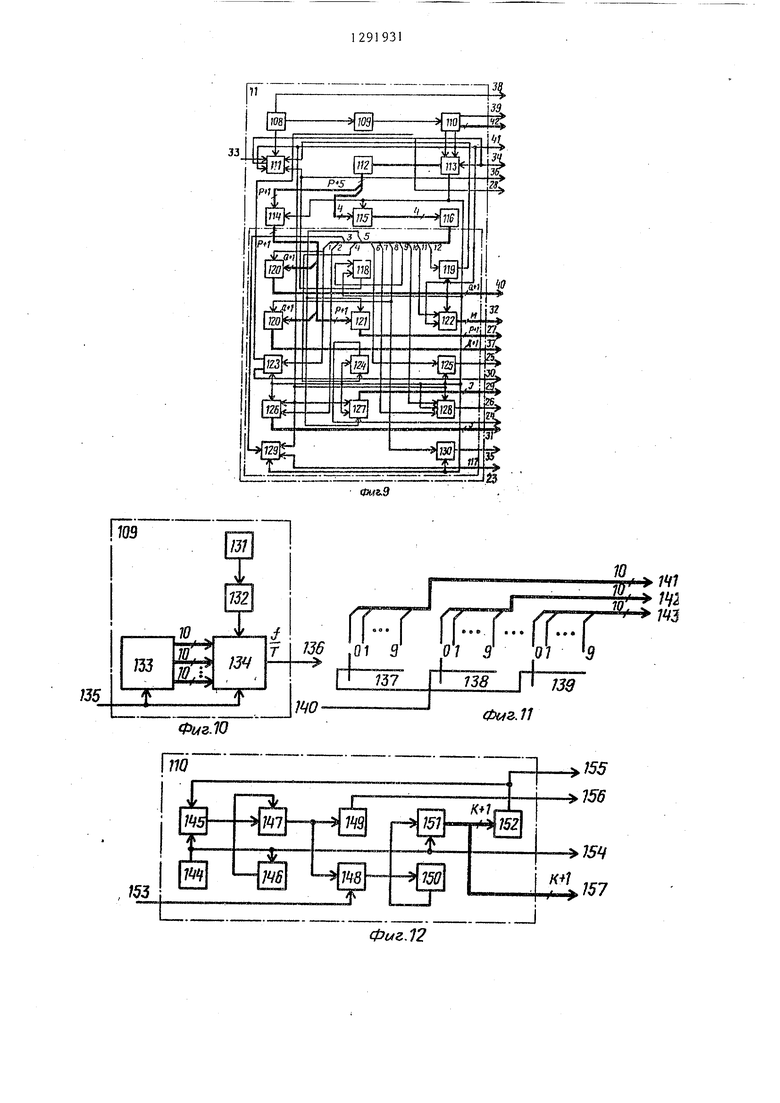

Узел управления (фиг.9) содержит источник 108 эталонных напряжений, генератор 109 тактовых импульсов, первьй блок 110 управления, третий блок 111 управления,, блок 112 памяти, второй блок 113 управления, первый регистр (регистр адреса) 114, второй регистр (регистр операций) П5, дешифратор 116, блок 117 коммутаторов, вкл очающий коммутаторы 118-130.

Генератор тактовых импульсов (фиг.10) содержит задающий генератор J3, делитель 132 частоты, датчик 133 кода времени, делитель 134 частоты с переменным коэффициентом, вход 135, выход 136.

Датчик кода времени (фиг.11) со35 держит переключатели 137-143 декад. 1

Первьй блок управления (фиг.12)

содержит кнопку 144 Пуск, элемент ИЛИ 145, элемент. 146 задержки,

40 триггер 147, элемент И 148, усилитель 149, формирователь 150 импульсов, двоичный счетчик 151, дешифратор 152, вход 153, выходы 154-157. Второй блок управления (фиг.13)

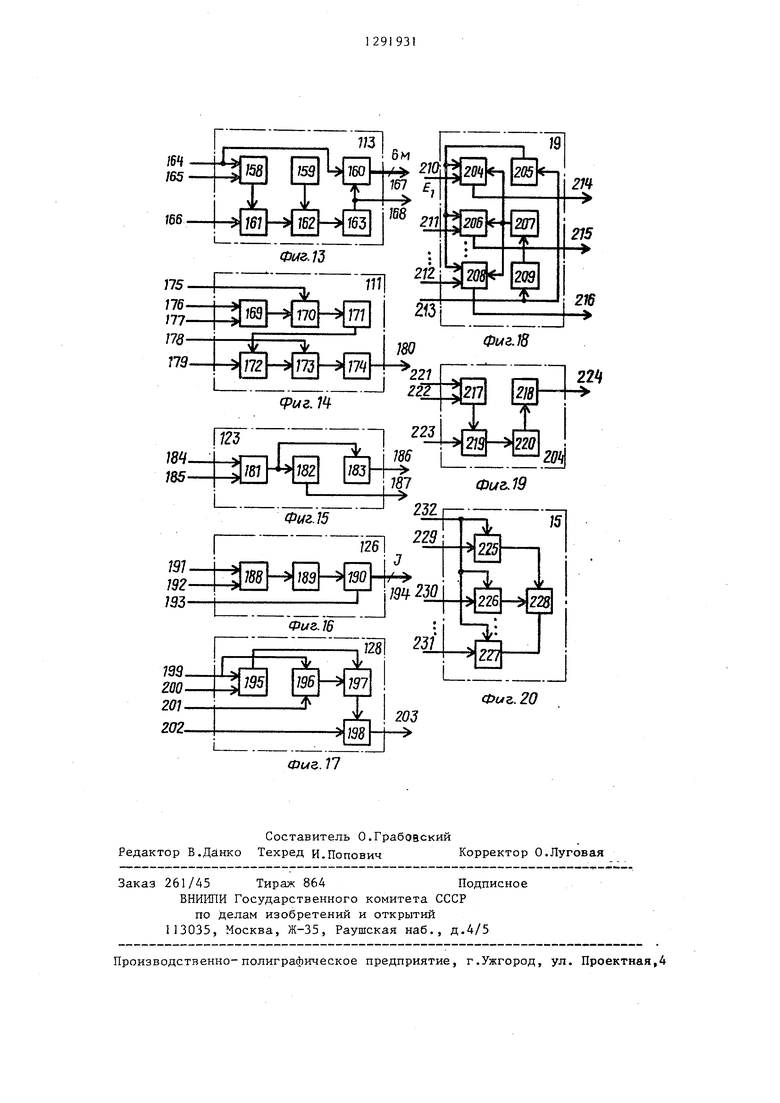

45 содержит элемент ИЛИ 158, генератор 159 прямоугольных импульсов, двонч- ньй счетчик 160, триггер 161, элемент И 162, формирователь 163 импульсов, входы 164-166, выходы 167 и 168.

50 Третий блок управления (фиг.14) содержит аналоговый ключ 169, компаратор 170, первый формирователь 171 импульсов, триггер 172, элемент И 173, второй формирователь 174 им55 пульсов, входы 175-179, выход 180.

Первый ком чутатор (фиг. 15) содержит элемент И 181, формирователи 182 и 183 импульсов, входы 184 и 185, выходы 186 и 187.

.30

1

Второй коммутатор (фиг.16) содержит элемент И 188, формирователь 189 импульсов, распределитель 190 импульсов , входы 191-193, выход 194.

Третий коммутатор (фиг.17) со- держит элементы И 195, 196, элемент ИЛИ 197, триггер 198, входы 199-202, выход 203.

Блок нормализации (фиг.18) содержит компараторы 204, генератор 205 пилообразного .напряжения, компаратор 206, формирователь 207 импульсов компаратор 208, элемент 209 задержки, входы 210-213,, выходы 214-216.

Компаратор (фиг.19) содержит сумматор 217, формирователь 218 импульсов, аналоговый ключ 219, схему 220 сравнения, входы 221-223, выход 224.

Индикатор (фиг.20) содержит триг- геры 225-227, схему 228 индикации, входы 229-232.

Устройство работает следующим образом.

Перед производством контроля на передней панели блока 11 с помощью переключателей 137-139 (фиг.П) устанавливается время Т анализа сигналов - тем самым задается частота следования импульсов, формируемьк на выходе 136 генератора 109 (фиг.10).

При нажатии на кнопку Пуск блока 11 на его выходе 41 (фиг.9) и выходе 154 блока ПО (фиг. 12) выра- батывается сигнал импульс Исходное состояние. При этом освобождаются от запасенной энергии интеграторы анализатора 2, УВХ блока 16 и УВХ блока 18, а также устанавливают- ся в нулевое состояние триггеры блока 15, триггеры, двоичные счетчики и распределители импульсов блока 11 (фиг.9). На выходе 39 блока II также образуется высокий потенциал Ана лиз (момент образования этого потенциала соответствует t 0), приводящий к формированию на выходе 107 генератора 8 фиг.З) стимулирующего воздействия x(t) типа скачок напря- жения, которое поступает на вход ДС1 . Fla выходе объекта контроля появляется реакция y(t) (переходная характеристика), а счетчик 151 блока ПО (фиг.9,12) подсчитьшает им- пульсы, формируемые на основе импульсов генератора 109, вырабатывая на группе 157 (42) К+1 выходов блока 11 О двоичные коды адресов, управляю1291931

щие работой демультиплексора 43 анализатора 2 (фиг.1,2).

Образуемая на выходе ДС 1 реакция y(t) подвергается на интервале о, Т ортогональному разложению (анализу) по исходной базисной системе H-(t)j: 1, при котором анализатор 2 определяет ненормированные по времени коэффициенты Фурье- Хаара у (j 1,2,...,). Затем в момент времени t Т прекращается поступление двоичных кодов адреса на группу входов 51 анализатора 2 (фиг.2) и воздействие входного сигнла на ДС 1 (прекращается поступление потенциала Анализ, его уровень понижается), и в анализаторе 2 фиксируются значения коэффициентов разложения у ( 1,2,....,). Процедуры ортогонального разложения (анализа) сигнала y(t) по исходному базису заканчиваются. Причем напряжения на выходах (группе выходов) 50 анализатора 2, соответствующие ;значениям коэффициентов разложения У, (J ) будут сохраняться до момента поступления на управ- ляющий вход 52 анализатора 2 нового управляющего сигнала.

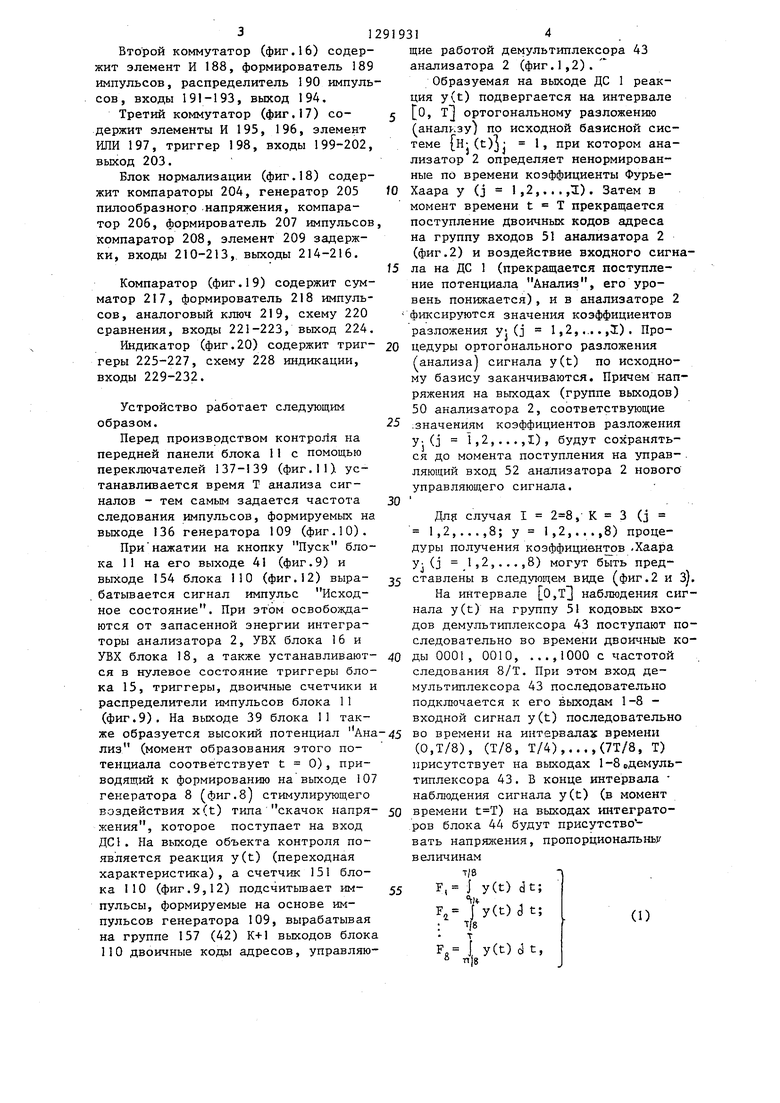

Для случая I ,- К 3 (j 1,2,...,8; у 1,2,...,8) процедуры получения коэффициентов -Хаара у (j 1,2,...,8) могут быть представлены в следующем виде (фиг.2 и

На интервале 0,Т наблюдения синала y(t) на группу 51 кодовых входов демультиплексора 43 поступают пследовательно во времени ДВОИЧНЫЕ кды 0001, 0010, ...,1000 с частотой следования 8/Т. При этом вход демультиплексора 43 последовательно подключается к его выходам 1-В - входной сигнал y(t) последовательно во времени на интервалах времени

(О,Т/8), (Т/8, Т/4)(7Т/8, Т)

присутствует на выходах 1-8 вДЬмуль- типлексора 43. Б конце интервала наблюдения сигнала y(t) (в момент времени ) на выходах интеграторов блока 44 будут присутство - вать напряжения, пропорциональны величинам

т;а y(t) dt;

°t) j y(t) a t;

ffs

T

f y(t) ( t, njg

(1)

которые подаются на соотве.--:твую- щие прямые входы блока 46 (фиг.З), на инверсные входы которых с выходов инверторов блока 45 поступают напряжения, соответствующие величинам -F ,-F,,, -F , . . . ,-Fg .

В момент времени t Т на группах выходов блока 46 Гфиг.З) будут присутствовать сигналы: на группе 1 - (F, ,F,.. . ,Fg), на группе 2 (( - 5 б 9 на группе 3 - (F, ,F ,-F, .-F ) , на

группе 4 - (Fj.F,-F,-Fg), на группе 5 - (F, j-Fj), на группе 6 - (F, Д) «а группе 7 - (Ffj-F), на группе 8 - (F ,-Fg ),которые в блках 47 и 48 преобразуются в сигналы у-(J 1,2,...,8)

у, F, +F2 +F, +F, +F5 +F6 +F, +Fg ; y,j F,+F,(Fj+F6+F,+Fg);

(2)

8

(F,FS)

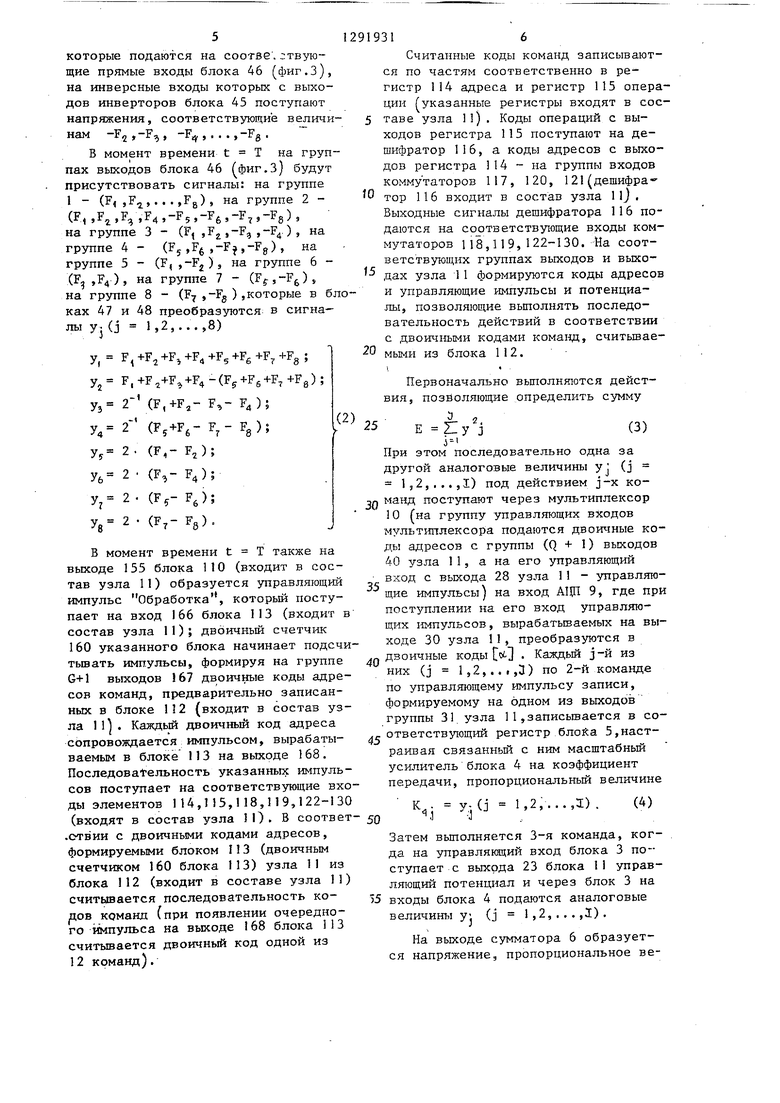

В момент времени t Т также на выходе 155 блока 110 (входит в состав узла 11) образуется управляющий импульс Обработка, который поступает на вход 166 блока 113 (входит в состав узла 11); двоичньш счетчик 160 указанного блока начинает подсчи тьшать импульсы, формируя на группе G+1 выходов 67 двоичные коды адресов команд, предварительно записанных в блоке 112 (входит в состав узла 1 1 . Каждьгй двоичный код адреса сопровождается импульсом, вырабатываемым в блоке 113 на выходе 168. Последовательность указанных импульсов поступает на соответствующие входы элементов 114,115,118,119,122-130 (входят в состав узла 5 О. В соответ .отвии с двоичными кодами адресов, формируемыми блоком I13 (двоичным счетчиком 160 блока 113) узла 11 из блока 12 (входит в составе узла 11) считывается последовательность кодов команд (при появлении очередного импульса на выходе 168 блока 113 считывается двоичный код одной из 12 команд).

2919316

Считанные коды команд записываются по частям соответственно в регистр 114 адреса и регистр 115 операции указанные регистры входят в сос- 5 таве узла 1) . Коды операций с выходов регистра 115 поступают на дешифратор 116, а коды адресов с выходов регистра 14 на группы входов коммутаторов 117, 120, 121(дешифратор 116 входит в состав узла 1 1 j . Выходные сигналы дешифратора 116 подаются на соответствующие входы коммутаторов 118,119,122-130. На соответствующих группах выходов и выходах узла 11 формируются коды адресов и управляющие импульсы и потенциалы, позволяющие выполнять последовательность действий в соответствии с двоичными кодами команд, считьшае- мыми из блока 112.

10

15

20

Первоначально выполняются действия, позволяющие определить сумму

Е Zly j(3)

j-- При этом последовательно одна за

другой аналоговые величины у: (j 1,2,,..,) под действием j-x команд поступают через мультиплексор 10 (на группу управляющих входов мульт1тлексора подаются двоичные коды адресов с группы (Q + 1) выходов 40 узла 11, а на его управляющий вход с выхода 28 узла 11 - управляющие импульсы) на вход А1Ц1 9, где при поступлении на его вход управляющих импульсов, вырабатьшаемых на выходе 30 узла 11, преобразуются в

двоичные коды 1 . Каждый j-й из них (j Ij2,...,3) по 2-й команде по управляющему импульсу записи, формируемому на одном из выходов группы 31 узла 11,записьшается в соответствующий регистр блойа 5,настраивая связанный с ним масштабный усилитель блока 4 на коэффициент передачи, пропорциональный величине

0

YjCJ 1,2,...Д). (4)

Затем вьшолняется 3-я команда, когда на управлякщий вход блока 3 поступает с выхода 23 блока П управляющий потенциал и через блок 3 на 55 входы блока 4 подаются аналоговые величины у (j 1,2,,..,).

На выходе сумматора 6 образуется напряжение, пропорциональное ве7

личине Е. По 1-и команде полученная аналоговая величина преобразуется в двоичный код ссЗ который при выполнении 4-й команды записьшается по управляющему импульсу записи, вырабатьшаемому на выходе 24 узла 11, в регистр I2. Масштабный усилитель 22 при этом настраивается на коэффициент передачи, соответствующий .

К

22

1 Ё

(5)

Далее на основе напряжений, присутствующих на выходах группы 50 анализатора 2, осуществляется опре- деление класса состояний контролируемой ДС 1 в несколько этапов.

На первом этапе классификации для каждой т-й (га 1 ,2,...,М) системы набора (количеством М базисов набора (4) определяется количество распознаваемых классов состояний контролируемой ДС) формируется на выходе сумматора 6 фиксированный сигнал, пропорциональньш по величине первому ненормированному по времени коэффициенту разложения у реакции системы y(t) по соответствующей базисной системе. При этом I раз вьшолняется 5-я команда, когда для каждого j 1,2,,..,1 из блока 7 в соответствии с двоичным кодом адреса, формируемым на группе выходов 27 узла 11, считьтается двоичный код GTO,J коэффициента разложения первой составляющей первого сигнала т-го базиса набора по исходному базису Гн(х)| , на интервале Го, и записьшается в соответствуюи;ий j-й регистр блока 5 под действием импульса записи, вырабатьшаемого на одном из вькодов группу 29 узла 11. В соответствии с кодом устанавливается коэффициент передачи масштабного усилителя блока 4, связанного с ука-

занньм регистром блока 5. I

Проходя через блоки 3,4 и 6 сигналы У (J 1,2,..,,) подвергаются аддитивному смешиванию с весами.

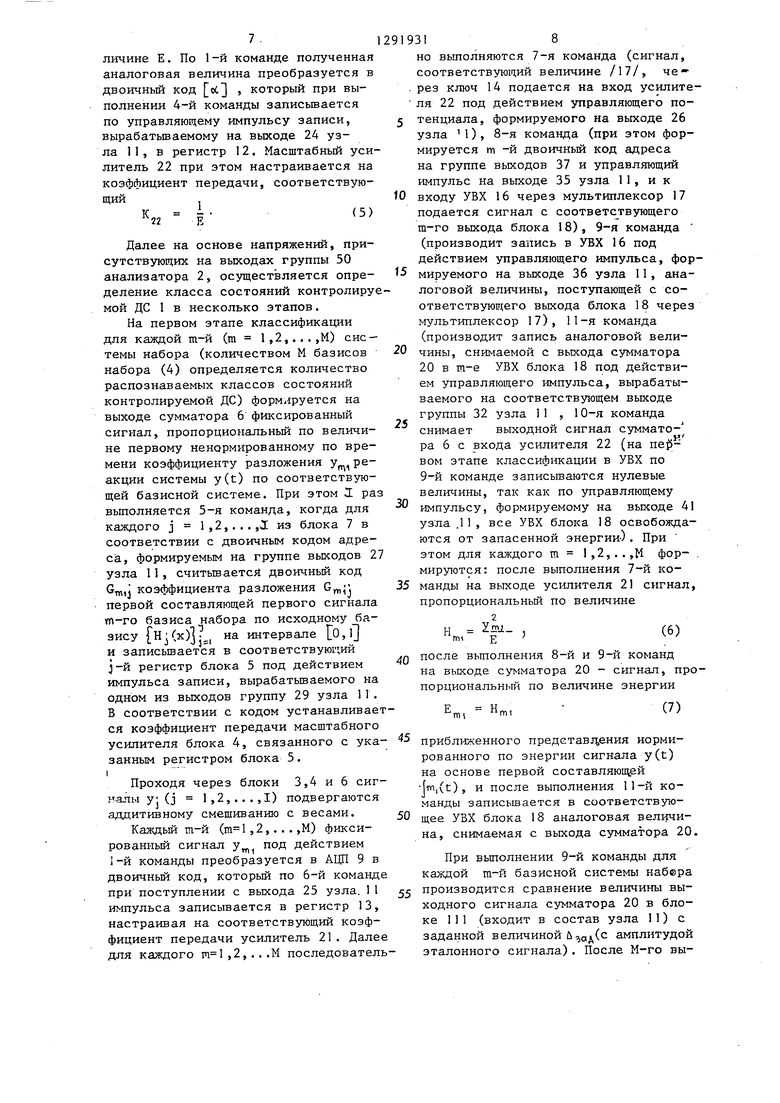

Каждый т-й (,2,...,М) фиксированный сигнал у под действием 1-й команды преобразуется в АЦП 9 в двоичньй код, который по 6-й команде при поступлении с выхода 25 узла. 11 импульса записывается в регистр 13, настраивая на соответствующий коэффициент передачи усилитель 21. Далее для каждого ,2, . . .М последователь1291

5 10

2035 0

9318

но выполняются 7-я команда (сигнал, соответствующий величине /17/, че , рез ключ 14 подается на вход усилите- ля 22 под действием управляющего потенциала, формируемого на выходе 26 узла О, 8-я команда (при этом формируется m -и двоичный код адреса на группе выходов 37 и управляющий импульс на выходе 35 узла 11, и к входу УВХ 16 через мультиплексор 17 подается сигнал с соответствующего т-го выхода блока 18), 9-я команда (производит запись в УВХ 16 под действием управляющего импульса, формируемого на выходе 36 узла 11, аналоговой величины, поступающей с соответствующего выхода блока 18 через мультиплексор 17), 11-я команда (производит запись аналоговой величины, снимаемой с выхода сумматора 20 в т-е УВХ блока 18 под действием управляющего импульса, вырабатываемого на соответствующем выходе группы 32 узла 11,10-я команда снимает выходной сигнал сумматоV

ра 6 с входа усилителя 22 (на nei5- вом этапе классификации в УВХ по 9-й команде записываются нулевые величины, так как по управляющему импульсу, формируемому на выходе 41 узла .11 , все УВХ блока 18 освобождаются от запасенной энергии-) . При этом для каждого m ,2,..,М фор- . мируются: после выполнения 7-й команды на выходе усилителя 21 сигнал, пропорциональный по величине

Ь1

2iru

)

(6)

после вьтолнения 8-й и 9-й команд

на выходе сумматора 20 - сигнал, пропорциональньй по величине энергии

Е

ГО1

Н,

(7)

приближенного представт ения нормированного по энергии сигнала y(t) на основе первой составляющей Jin,(t) , и после выполнения 11-й команды записьшается в соответствующее УБХ блока 18 аналоговая величина, снимаемая с выхода сумматора 20.

При вьшолнении 9-й команды для каждой т-й базисной системы набора производится сравнение величины выходного сигнала сумматора 20 в блоке 111 (входит в состав узла 11) с заданной величиной Ь,,з|д(с амплитудой эталонного сигнала). После М-го выw

20

полнения последовательности -I команд и 1-,6-9-, 11- 10-х команд .осуществляется вьтолне ние 12-й команды, по которой производится оценка результатов сравнения величин выходных сигналов сзпмматора 20 с заданной величиной u., При этом может оказаться (с большой вероятностью), что амплитуда эталонного сигнала превышает амплитуды сформированных для всех М базисов выходных сигналов сумматора 20. Тогда в блоке 113 управления вьшолняется второй этап классификации. При этом двоичный счетчик 160 блока (входит в состав узла 11) продолжает подсчитывать импульсы, а из блока 112 .(входит в состав узла 11) будут считьшаться двоичные коды очередных команд.

На втором этапе для каждой т-й (,2,...,М) базисной системы набора в блоке 113 управления формируется на выходе сумматора 6 фиксированный сигнал, пропорциональньй по величине второму ненормированному по времени коэффициенту разложения Уд, сигнала y(t) по состветствутощей базисной системе. При этом раз выполняется 5-я команда, когда для каждого ЗО j 1,2,..., из блока 7 в соответствии с двоичным кодом адреса, форни- руемьм на группе выходов 27 узла 11, считывается двоичньй код коэффициента разложения второй 35

составляющей (сигнала)№ -го базиса

-t ,- Т Л

набора по исходному базису Hj (x)j. на интервале fO,lj и записывается в соответствующий регистр блока 5 под действием импульса записи, вырабаты- 40 Баемого на одном из выходов группы 29 узла I1. В соответствии с кодом величины устанавливается коэффициент передачи масштабного усилителя блока 4, связанного с указанным регист- 45 ром блока 5. Проходя через блоки 3,4 и 6, сигналы у- (J 1,2,.,.,л;) подвергаются аддитивному смешиванию с чесами при i 2.

129193110 ,

последовательно выполняется 7-я команда (сигнал, соответствующий величине , через ключ 14 подается на вход усилителя 22 под действием управляющего потенциала, формируемого на выходе 26 узла П), 8-я команда (при этом формируется т-й двоичный код адреса на группе выходов 37 и управляющий импульс на выходе 35 узла 11 и к входу УВХ 16 через мультиплексор I7 подается сигнал с соответствующего m-го выхода блока 18), 9-я команда (производит запись в УВХ 16 под действием управляющего 5 импульса, формируемого на выходе 36 узла 11 аналоговой величины, поступающей с соответствующего выхода блока 18 через мультиплексор 17), П-я команда (производит запись аналоговой величины, снимаемой с выхода сумматора 20, в ni-е УВХ блока 18 под действием -управляющего импульса, вырабатьшаемого на соответствующем выходе группы 32 узла 1l) и 10-я команда (снимает выходной сигнал сумматора 6 с входа усилителя 22), на втором этапе классификации в УВХ 16 по 9-й команде записываются соответствующие величины. При этом для каждого m l52,...,M формирзтотся после выполнения 7-й команды на выходе усилителя 21 сигнал, пропорциональньй величине

Ы

112

-±1

(8)

и после вьшолнения 8-й и 9-й команд на выходе сумматора 20 - сигнал, пропорциональный по величине энер- , гни

Еп,г г., - Н„,(9)

приближенного представления нормированного по энергии сигнала y(t) на основе двух первых составляющих f,(t) и jj,(t), и после выполнения

11-и команды записывается в соответствующее УВХ блока 18 аналоговая величина, снимаемая с выхода сумматора 20,

. Каждый ш-й (,2,...,М) фиксированный сигнал у под действием 1-и команды преобразуется в АЦП 9 в двоичный код, который по 6-й команде при поступлении с вых ода 25 узла 11 импульса записи записывается в регистр 13, настраивая на соответствующий коэффициент передачи усилитель 21 . Далее для каждого m ,1,2,.. . ,М ,

Ы

112

-±1

(8)

и после вьшолнения 8-й и 9-й команд на выходе сумматора 20 - сигнал, пропорциональный по величине энер- , гни

Еп,г г., - Н„,(9)

приближенного представления нормированного по энергии сигнала y(t) на основе двух первых составляющих f,(t) и jj,(t), и после выполнения

11-и команды записывается в соответствующее УВХ блока 18 аналоговая величина, снимаемая с выхода сумматора 20,

При выполнении 9-й команды для каждой т -и базисной системы набора производится сравнение величины выходного сигнала сумматора 20 в блоке 111 с зад,анной велшшной . После М-го выполнения последовательности 1, 5-х команд и 1-, 6-,7-,8-,9-, П- и 10-х команд осуществляется

11

вьшолнение 12-й команды, по которой производится оценка результатов сравнения величин выходных сигналов сум129

матора 20 с заданной величиной ь

JdA

20

Далее аналогично второму этапу выпол- няется следующий этап классификации (выполняется последовательность J ,5-е , команды и 1-,6-,7-,8-,9-,11- и 10-е команды)- и т.д. до тех пор, пока амплитуда эталонного сигнала превы- Ш шает амплитуды сформированньк сигналов для М базисов набора.

Если среди указанных сигналов на очередном этапе классификации обнаруживается хотя бы один сигнал, ампли- 5 туда которого не меньше амплитуды эталонного сигнала, то первьй из таких сигналов вызьшает образование на выходе формирователя 171 блока .111 импульса, которьш устанавливает триггер 172 блока 111 в единичное состояние. При этом после вьшолне- ния 12-й команды на выходе 180 блока 111 вырабатьшается импульс Класси- фикация, поступающий на вход 165 блока 113 и на выход 34 узла 11 (блоки 111 и 113 входят в состав узла 1 l), В блоке 113 по импульсу Классификация двоичньй счетчик устанавливается в нулевое состояние (при этом из блока 112 прекращается считьша- ние очередных команд).

С выхода 34 узла 11 импульс Классификация подается на вход 213 ка 19, запуская генератор 205, фор- -35 мирующий линейно убьшающее пилообразное напряжение. Последнее поступает на объединенные входы компараторов 204-208, на другие входы которых (соответственно через входы 210-212 блока 19) подаются сигналы с выходов блока 18. Суммарные сигналы с выходов сумматоров 217 через ключи 219 поступают на входы схем 220 сравнения (сумматор 217 ключ 219 и схема 220 сравнения входят в состав каждого из компараторов 204-208).

рез соответствующий вход из группы входов 229-232 индикатора 15 поступает на один из триггеров 225-227, устанавливая его в единичное состояние. Последнее отображается в состоянии соответствующего элемента инд кации схемы 228 индикации, указывая класс состояния ДС 1 (соответствует номеру выбранной для представления сигнала y(t) базисной системы набо- ра). На этом процесс классификации состояний контролируемого объекта . прекращается.

Формула изобретения

1. Устройство контроля, содержащее блок ключей, два блока масштабны усилителей, три блока регистров, сум матор, первый блок памяти, генератор стимулов, аналого-цифровой преобразователь, аналоговый мультиплексор, узел управления, второй блок памяти, блок нормализации, первый

25 сумматор и анализатор спектров, подключенный первым информационным входом к входу устройства, первым управляющим входом - к первому выходу узла управления, соединенного вторым

30 выходом с первым входом блока ключей третьими выходами - к первым информационным входам первого блока ре-- гистров, связанного вторыми информационными входами с вЬкодамй первого блока памяти, а выходами - с первыми информационньм и входами первого блока масштабных усилителей, четвертый и пятьй выходы узла управления подключены к управляющим входам соответственно второго блока регистров и третьего блока регистров, соединенного выходом с информационным входом второго блока масштабных усилителей, подключенного выходом к первому входу первого сумматора, соединенного с первым управляющим входом второго блока памяти, первый и второй входы генератора с 1 имулирую

40

45

щих сигналов подключены к шестому Как только хотя бы один из указан-50 седьмому выходам узла управления.

ных сигналов становится не меньшим эталонного сигнала, соответствующая схема сравнения переходит из одного состояния (например, единичного) в

другое (например, нулевое). При этом55 циональных возможностей устройства, на выходе 224 соответствуюп;его из введены второй сумматор, ключ, мас- компараторов 204-208 (на одном из штабный усилитель, два аналоговых выходов 214-216 блока 19) образуется мультиплексора, третий блок памяти,

импульс. Сформированный импульс че

20

, Ш 5,

-35

9193112

рез соответствующий вход из группы входов 229-232 индикатора 15 поступает на один из триггеров 225-227, устанавливая его в единичное состояние. Последнее отображается в состоянии соответствующего элемента индикации схемы 228 индикации, указывая класс состояния ДС 1 (соответствует номеру выбранной для представления сигнала y(t) базисной системы набо- ра). На этом процесс классификации состояний контролируемого объекта . прекращается.

Формула изобретения

1. Устройство контроля, содержащее блок ключей, два блока масштабных усилителей, три блока регистров, сумматор, первый блок памяти, генератор стимулов, аналого-цифровой преобразователь, аналоговый мультиплексор, узел управления, второй блок памяти, блок нормализации, первый

25 сумматор и анализатор спектров, подключенный первым информационным входом к входу устройства, первым управляющим входом - к первому выходу узла управления, соединенного вторым

30 выходом с первым входом блока ключей, третьими выходами - к первым информационным входам первого блока ре-- гистров, связанного вторыми информационными входами с вЬкодамй первого блока памяти, а выходами - с первыми информационньм и входами первого блока масштабных усилителей, четвертый и пятьй выходы узла управления подключены к управляющим входам соответственно второго блока регистров и третьего блока регистров, соединенного выходом с информационным входом второго блока масштабных усилителей, подключенного выходом к первому входу первого сумматора, соединенного с первым управляющим входом второго блока памяти, первый и второй входы генератора с 1 имулирую40

45

соединенного восьмыми выходами с адресными входами первого блока памяти, отличающееся тем, что, с. целью расширения функи индикатор, подключенный управляю

f5

20

25

щим входом к первому Bbixoflv узла управления, к первому управляющему входу третьего блока Пс:мяти, ко второму управляющему входу второго блока памяти, и информационными входа- 5 ми - к выходу блока нормализации, связанного информационными входами с выходами второго блока памяти и первыми информационными входами первого аналогового мультиплексора, а JO управляющим входом - с девятым выходом узла управления,, соединенного входом с выходом сумматора, а десятым выходом -- с управляющим входом ключа, подключенного сигнальным входом к выходу первого сумматора и к управляющему входу второго аналогового мультиплексора, а выходом - к сигнальному входу масштабного усилителя, связанного выходом с сигнальным входом второго блока мас- штабньк усилителей, а информационными входами - с выходами второго блока регистров, подключенного информационными входами к информационным входам третьего блока регистров, к выходам аналого-цифрового преобразователя и к третьему информационному входу первого блока регистров , подключенного четвертыми информационными входами к одиннадцатым выходам узла управления, соединенного двенадцатым выходом с управляющим входом аналого-цифрового преобразователя, тринадцатым выхо- 35 дом - с управляющим входом второго аналогового мультиплексора, четырнадцатыми выходами - со вторым информационным входом анализатора спектров , подсоединенного выходами ко вто- 40 рым входам блока ключей и к первым информационным входам второго аналогового мультиплексора, подключенного выходом к сигнальному входу аналого- цифрового преобразователя, а вторы- 45 ми информационными входами - к пятнадцатому выходу узла управления, связанного шестнадцатым выходом со вторым управляющим входом третьего блока памяти, подключенного выходом 50 ко второму входу сумматора, а информационным входом - к выходу первого аналогового мультиплексора, подключенного управляющим и вторыми информационными входами соответственно к 55 семнадцатому и восемнадцатому выходам узла управления, соединенного девятнадцатым выходом с информационными входами второго блока памяти.

129193114

причем выходы блока ключей соединены со вторыми информационными входами первого блока масштабных усилителей, подключенного выходам ко входам второго сумматора.

30

2. Устройство по П.1, о т л и - чающееся тем, что узел управления содержит генератор тактовых И1у пульсов, три блока управления, блок памяти, два регистра, дешифратор, блок коммутаторов и источник эталонных напряжений, подключенный первым выходом к седьмому выходу узла управления, вторым выходом - ко входу генератора тактовых импульсов, соединенного выходом со входом первого блока управления, подключенного первым и вторым выходами соответственно к шестому и четырнадцатому выходам узла управления, третьим выходом - к первому входу второго блока, управления, а четвертым выходом - ко второму входу второго блока управления, к первому выходу узла управления и к первому входу третьего блока управления, соединенного вторым входом со входом узла управления, третьим входом - с третьим выходом источника эталонных напряжений и с девятым выходом узла управления, с третьим входом второго блока управления , подключенного первьц 1 выходом к управляющим входам первого и второго регистров, а вторыми выходами - ко входам блока памяти, подключенного к информационным входам первого регистра и второго регистра, соединенного выходами со входом дешифратора, подключённого к первым управляющим входам блока коммутаторов , соединенного информационными входами с выходом первого регистра, вторым управляющим входом - с первым входом третьего блока управле - ния,. третьщ управляющим входом - с четвертым выходом первого блока управления , четвертым управляющим входом - с первьм выходом второго блока управления, первым выходом - с тринадцатым выходом узла управления, вторьм выходом - -с четвертым входом третьего блока управления и шестнадцатым вькодом узла управления., третьим выходом - с пятым входом третьего блока управления, а четвертый, пятьй, шестой, седьмой, восьмой,девятый,двсятьт,одиннадцатый, двенадцатый 5тринадцатый,четырнадца5

0

5

5 O 5 0 50 5

0

2. Устройство по П.1, о т л и - чающееся тем, что узел управления содержит генератор тактовых И1у пульсов, три блока управления, блок памяти, два регистра, дешифратор, блок коммутаторов и источник эталонных напряжений, подключенный первым выходом к седьмому выходу узла управления, вторым выходом - ко входу генератора тактовых импульсов, соединенного выходом со входом первого блока управления, подключенного первым и вторым выходами соответственно к шестому и четырнадцатому выходам узла управления, третьим выходом - к первому входу второго блока, управления, а четвертым выходом - ко второму входу второго блока управления, к первому выходу узла управления и к первому входу третьего блока управления, соединенного вторым входом со входом узла управления, третьим входом - с третьим выходом источника эталонных напряжений и с девятым выходом узла управления, с третьим входом второго блока управления , подключенного первьц 1 выходом к управляющим входам первого и второго регистров, а вторыми выходами - ко входам блока памяти, подключенного к информационным входам первого регистра и второго регистра, соединенного выходами со входом дешифратора, подключённого к первым управляющим входам блока коммутаторов , соединенного информационными входами с выходом первого регистра, вторым управляющим входом - с первым входом третьего блока управле - ния,. третьщ управляющим входом - с четвертым выходом первого блока управления , четвертым управляющим входом - с первьм выходом второго блока управления, первым выходом - с тринадцатым выходом узла управления, вторьм выходом - -с четвертым входом третьего блока управления и шестнадцатым вькодом узла управления., третьим выходом - с пятым входом третьего блока управления, а четвертый, пятьй, шестой, седьмой, восьмой,девятый,двсятьт,одиннадцатый, двенадцатый 5тринадцатый,четырнадцатый и пятнадцатый выходы блока коммтаторов являются соответственно вторым, третьим, четвертым, пятым, восмым, десятым, одиннадцатым, двенадцатым, семнадцатьм, восемнадцатым и девятнадцатым выходами узла управления,

3.Устройство по п.2, отличающееся тем, что первый

блок управления содержит формирова- тель импульсов, элементы И, элемент ИЛИ, триггер, элемент задержки, усилитель, двоичный счетчик, дешифратор и кнопку Пуск, подключенную выходом ко входу элемента задержки, к установочному входу двоичного счечика, к четвертому выходу первого блока управления и к первому входу элемента ИЛИ, соединенного вторым входом с третьим выходом блока упра ления и с выходом дешифратора, а выходом - с единичным входом триггера соединенного нулевым входом с выходом элемента задержки, а прямым выходом, через усилитель,- с первым выходом первого.блока управления,а также с первым входом первого элемента И, подключенного вторым входом со входом первого блока управления, а выходом со входом формирователя импульсов, подключенного к счетному входу двоичного счетчика, соединенного разрядными выходами со вторьп- и вькода- ми первого блока управления и со входами дешифратора,

4.Устройство по п.2, о т л и- чающееся тем, что второй блок управления содержит триггер, элемент И, генератор прямоугольньпс импульсов, двоичный счетчик, форми

j

0 0 5

5

0

рователь и.ульсов, элемент ИЛИ, подключенный первым и вторым входами соответственно ко второму и третьему входам второго блока управления, а выходом - к единичному входу триггера, соединенного нулевым входом с первым входом второго блока управления, а вькодом - с первым входом элемента И, подключенного вторым входом к генератору прямоугольных импульсов, а выходом - ко входу формирователя, соединенного выходом с первым выходом второго блока управления и установочным входом двоичного счетчика, подключенного счетным входом ко второму входу второго блока управления , а выходом - к второму выходу второго блока управления.

5. Устройство по п. 2, отличающееся тем, что третий блок управления содержит два форми- рователя импульсов, компаратор, триггер, элемент И и ключ., подключенный управляющим и сигнальным входами соответственно к пятому и второму входам третьего блока управления, а выходом - к первому входу компара - тора, подсоединенного вторым входом к третьему входу третьего блока управления, а выходом - к входу первого формирователя импульсов, соединенного выходом к нулевому входу триггера, подключенного единичным входом к первому входу третьего блока управления, а прямым выходом - к первому входу элемента И, соединенного вторым входом с четвертым входом третьего блока управления, а выходом - со входом формирователя импульсов, соединенного выходом с выходом третьего блока управления.

Фмг.2

Ж

S

2 и §

m

Фмг.З

ФигЛ

Фи&,7

Фиг. 6

Ю7

Фиг,. 8

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения коэффициентов разложения корреляционной функции по системе ортонормированных базисных функций | 1985 |

|

SU1287196A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Устройство для контроля динамической системы управления | 1979 |

|

SU875345A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство для вычисления алгебраических выражений | 1979 |

|

SU864298A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

Изобретение относится к технике контроля динамических систем и может быть использовано при контроле систем автоматизированного и автоматического управления. Цель изобретения состоит в расширении функциональных возможностей устройства. Поставленная цель достигается путем организации возможности различать классов состояний объектов контроля за время классификации состояний объектов контроля, соизмеримое с временем наблюдения реакции контролируемого объекта, в течение которого один раз производится определение коэффициентов разложения выходного сигнала объекта контроля по исходному базису; затем на основе коэффициентов определяются коэффициенты разложения указанного сигнала по базисам набора. 4 з.п.ф-лы,20 ил. g

.12

. JL.

Фиг. 7

- I 227,

- ИЗг/

т

/85

ш

200 201

hht

-. п lUsh

i 7 TlbDd .

I:

Фмг. 20

203

tr

Шме. 77

Составитель О.ГрабОйский Редактор В.Дйнко Техред И.Попович Корректор 0.Луговая

Заказ 261/45 Тираж 864Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная,4

| Устройство для контроля динамических систем | 1973 |

|

SU489086A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для контроля динамической системы управления | 1979 |

|

SU875345A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-02-23—Публикация

1985-07-25—Подача