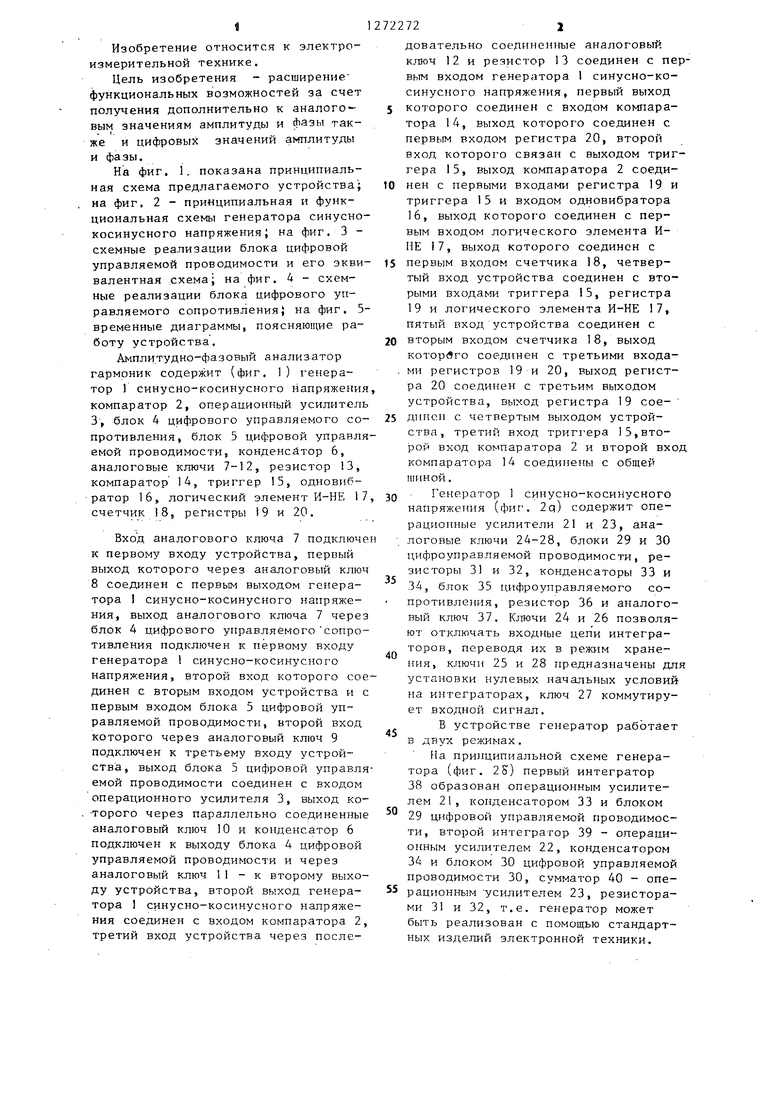

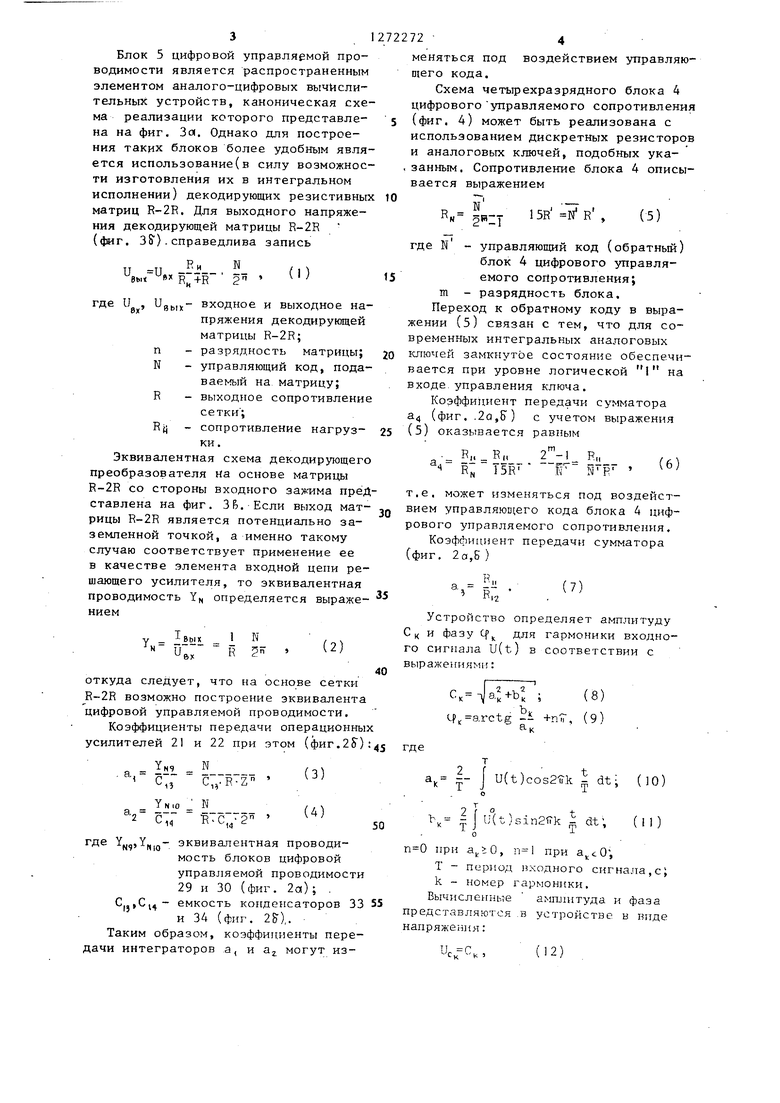

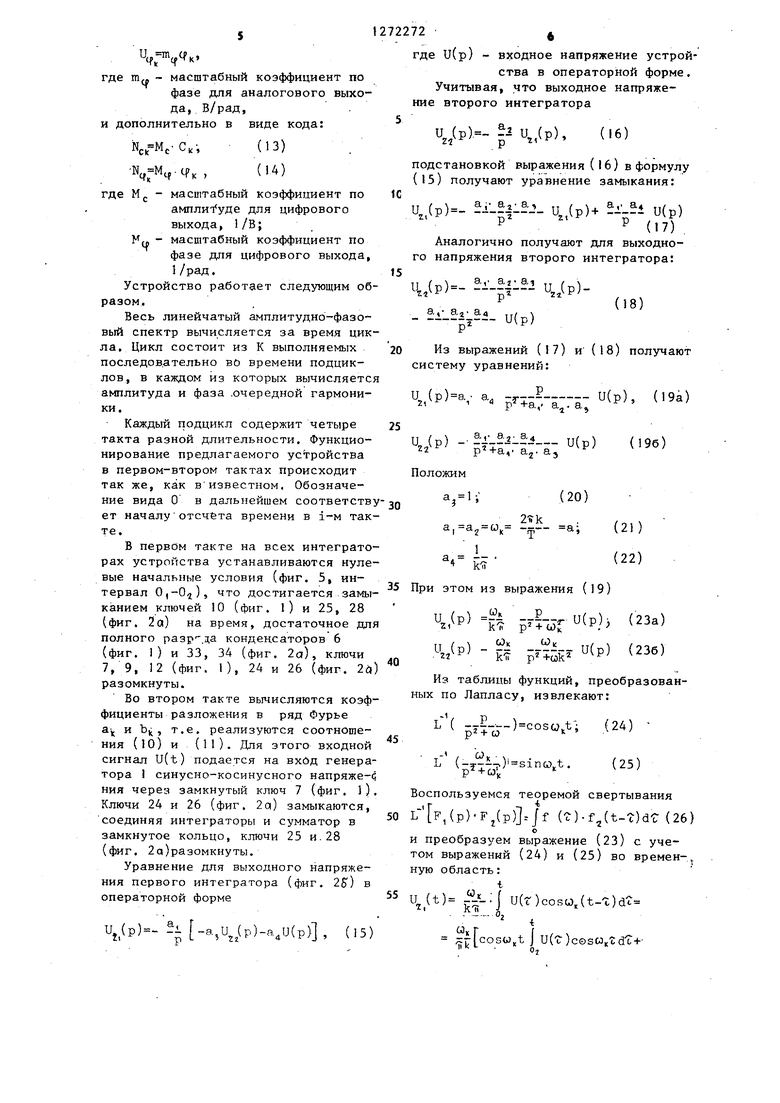

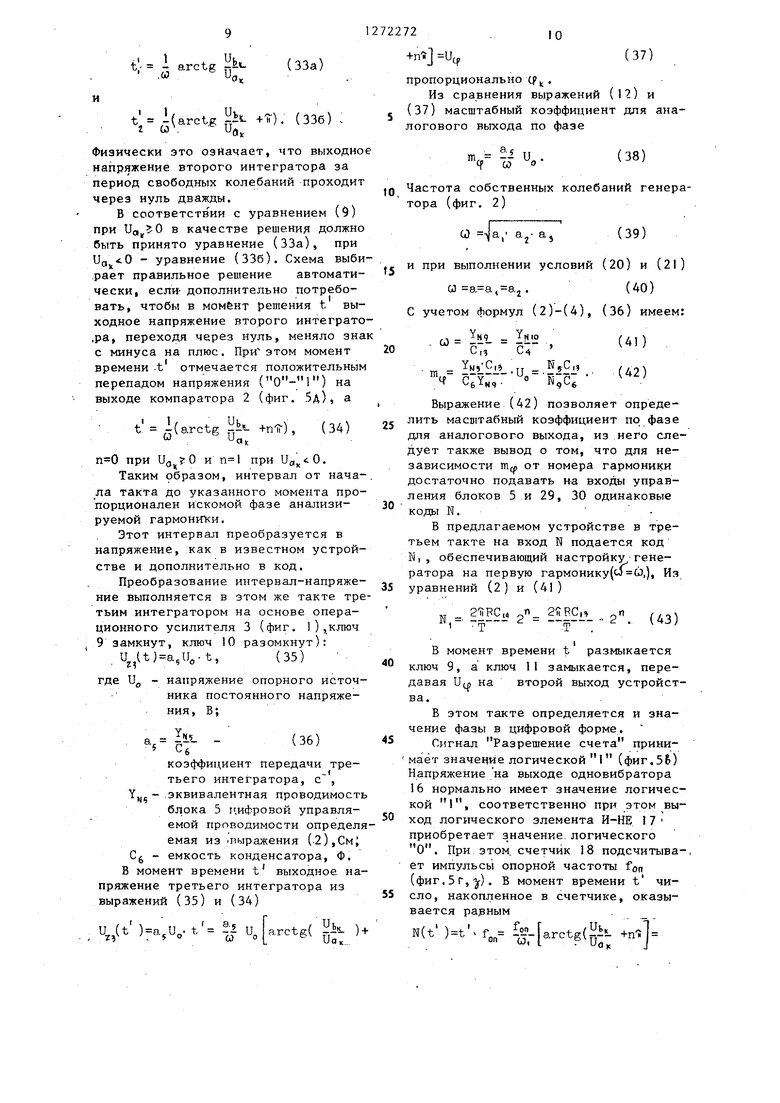

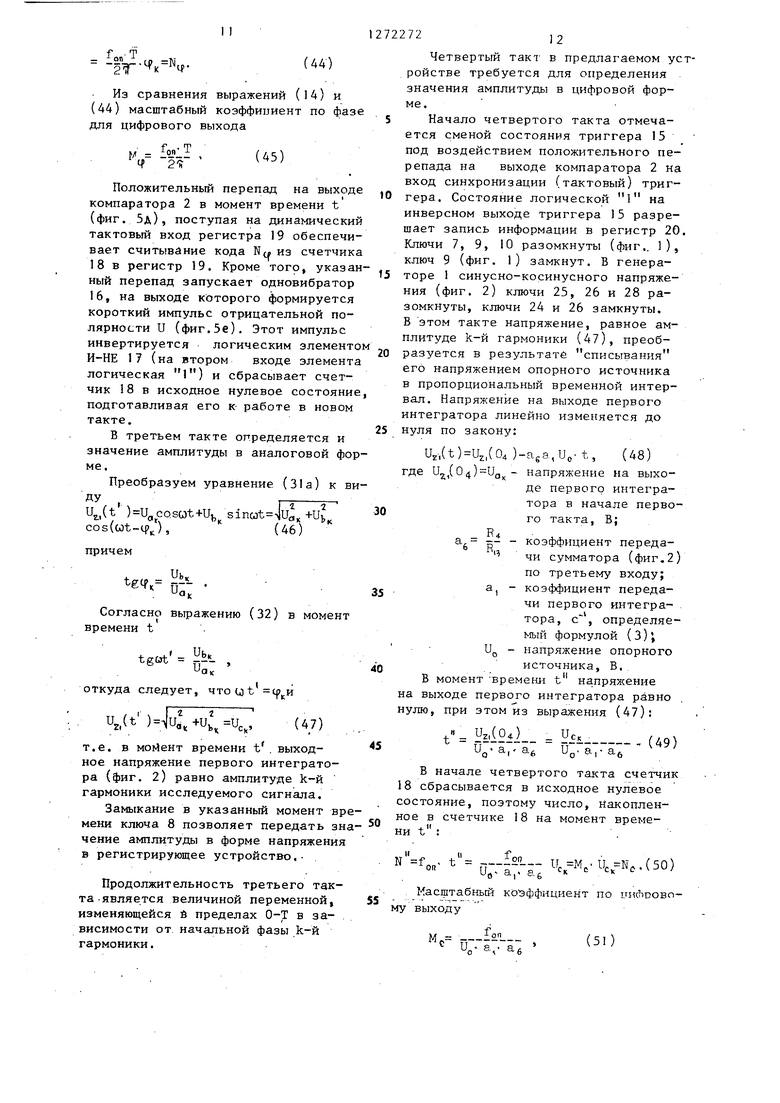

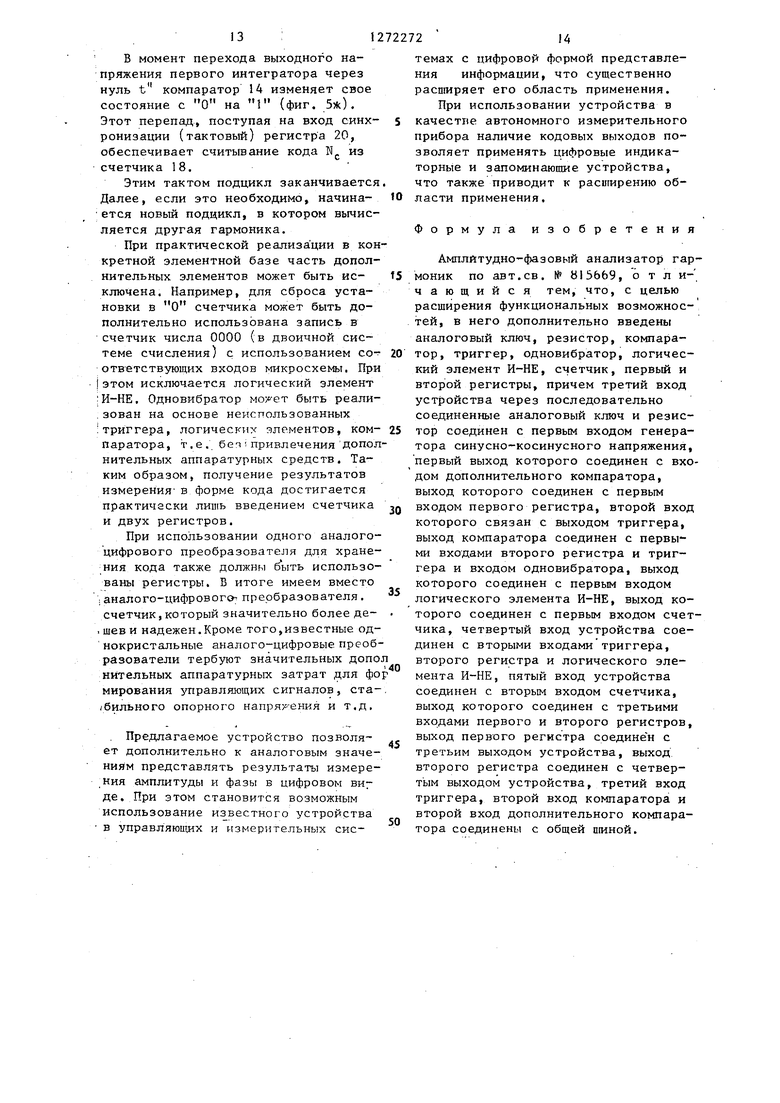

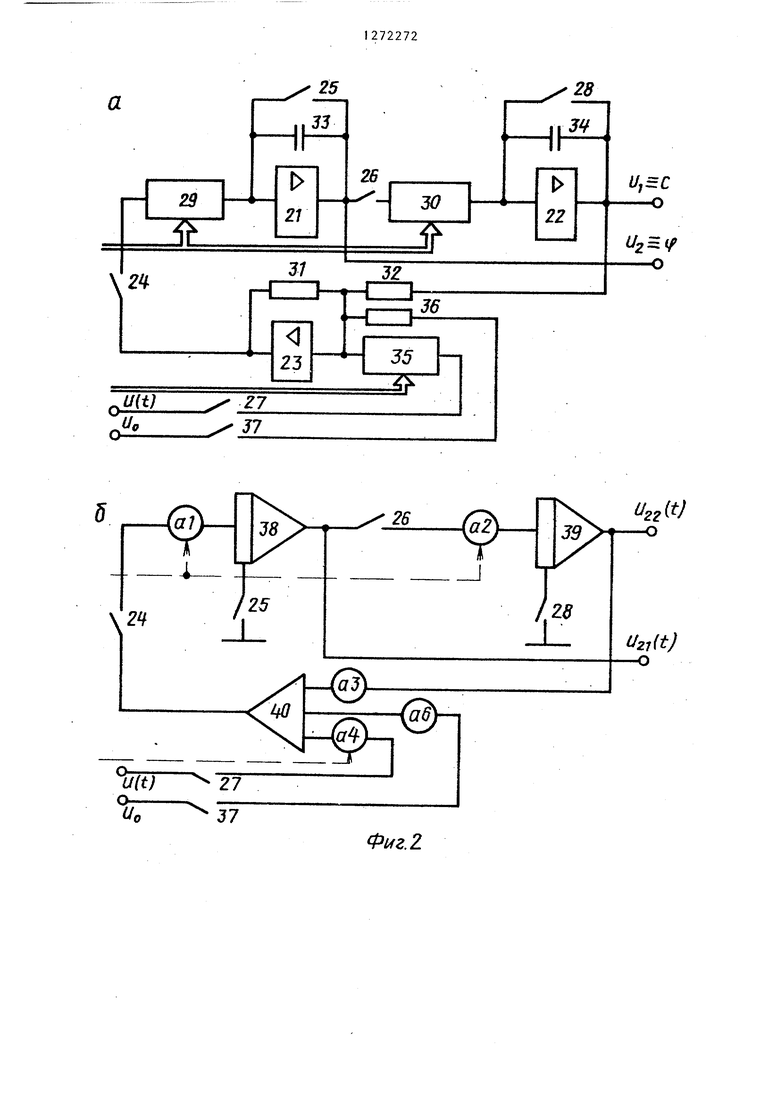

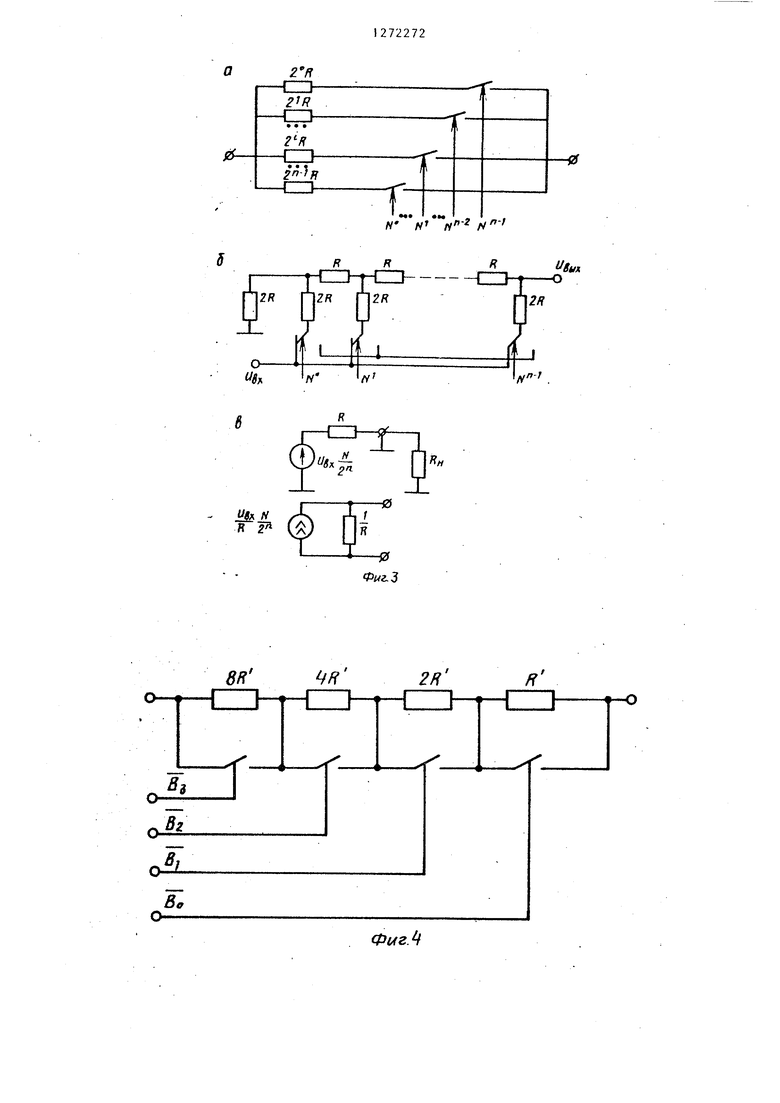

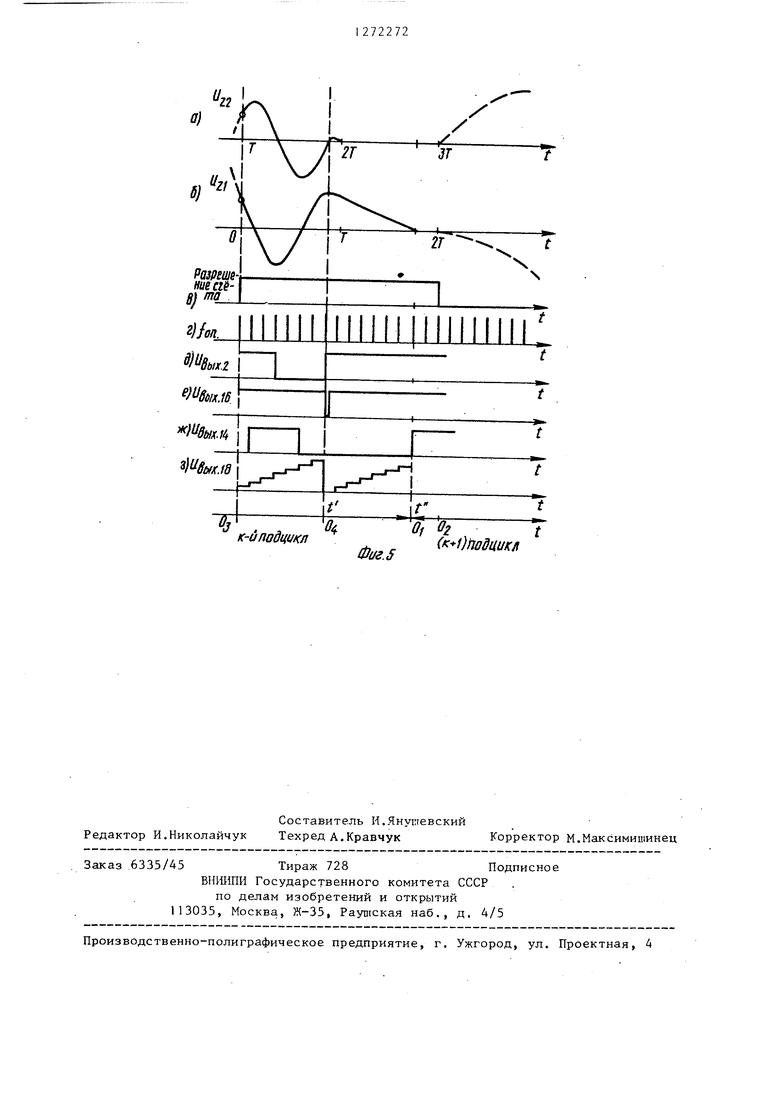

Уо/i Фиг. Изобретение относится к электроизмерительной технике. Цель изобретения - расширениефункциональных возможностей за счет получения дополнительно к аналоговым значениям амплитуды и фазы также и цифровых значений амплитуды и фазы. На фиг. 1, показана принципиальная схема предлагаемого устройства; на фиг, 2 - принципиальная и функциональная схемы генератора синусно косинусного напряжения; на фиг. 3 схемные реализации блока цифровой управляемой проводимости и его экви валентная схема; на фиг. 4 - схемные реализации блока цифрового управляемого сопротивления; на фиг. 5 временные диаграммы, поясняющие работу устройства. Амплитудно-фазовый анализатор гармоник содержит (фиг. 1) генератор 1 синусно-косинусного напряжения компаратор 2, операционный усилитель 3, блок 4 цифрового управляемого сопротивления, блок 5 цифровой управля емой проводимости, конденсйтор 6, аналоговые ключи 7-12, резистор 13, компаратор 14, триггер 15, одновибратор 16, логический элемент И-НЕ 17 счетчик iSj регистры 19 и 20. Вход аналогового ключа 7 подключ к первому входу устройства, первый выход которого через аналоговый ключ 8 соединен с первым выходом генератора I синусно-косинусного напряжения, выход аналогового ключа 7 чере блок 4 цифрового управляемого сопро тивления подключен к первому входу генератора 1 синусно-косинусного напряжения, второй вход которого со динен с вторым входом устройства и первым входом блока 5 цифровой управляемой проводимости, второй вход которого через аналоговый ключ 9 подключен к третьему входу устройства, выход блока 5 цифровой управля емой проводимости соединен с входом операционного усилителя 3, выход которого через параллельно соединенны аналоговый ключ 10 и конденсатор 6 подключен к выходу блока 4 цифровой управляемой проводимости и через аналоговый ключ I1 - к второму выходу устройства, второй выход генератора 1 синусно-косинусного напряжения соединен с входом компаратора 2 третий вход устройства через последовательно соединенные аналоговый к.пюч 12 и резистор 13 соединен с первым входом генератора 1 синусно-косинусного напряжения, первый выход которого соединен с входом компаратора 14, выход которого соединен с первым входом регистра 20, второй вход которого связан с выходом триггера 15, выход компаратора 2 соединен с первыми входами регистра 19 и триггера 15 и входом одновибратора 16, выход которого соединен с первым входом логического элемента ИНЕ 17, выход которого соединен с первым входом счетчика 18, четвертый вход устройства соединен с вторыми входами триггера 15, регистра 19 и логического элемента И-НЕ 17, пятый вход устройства соединен с вторым входом счетчика 18, выход которого соединен с третьими входами регистров 19 и 20, выход регистра 20 соединен с третьим выходом устройства, выход регистра 19 соединсн с четвертым выходом устройства, третий вход трипера 15, второй вход компаратора 2 и второй вход компаратора 14 соединены с общей шиной. Генератор 1 синусно-косинусного напряжения (фиг. 2q) содержит операционные усилители 21 и 23, аналоговые ключи 24-28, блоки 29 и 30 цифроуправляемой проводимости, резисторы 31 и 32, конденсаторы 33 и 34, блок 35 |ифроуправляемого сопротивления, резистор 36 и аналоговый ключ 37. Ключи 24 и 26 позволяют отключать входные цепи интеграторов, переводя их в режим хранения, ключи 25 и 28 предназначены для установки нулевых начальных условий на интеграторах, ключ 27 коммутирует входной сигнал. В устройстве генератор работает в двух режимах. Fla принципиальной схеме генератора (фиг. 2S) первый интегратор 38 образован операционнь М усилителем 21, конденсатором 33 и блоком 29 цифровой управляемой проводимости, второй интегратор 39 - операционным усилителем 22, конденсатором 34 и блоком 30 цифровой управляемой проводимости 30, сумматор 40 - операционным усилителем 23, резисторами 3 и 32, т.е. генератор может быть реализован с помощью стандартных изделий электронной техники. 3 Блок 5 цифровой упрарляемой проводимости является распространенным элементом аналого-цифровых вычислительных устройств, каноническая схема реализации которого представлена на фиг. За. Однако для построения таких блоков более удобным является использование(в силу возможности изготовления их в интегральном исполнении) декодирующих резистивных матриц R-2R. Для выходного напряжения декодирующей матрицы R-2R (фиг. З).справедлива запись еь, s R +R где и „, и входное и выходное напряжения декодирующей матрицы R-2R; п - разрядность матрицы; N - управляющий код, подаваемый на матрицу; R - выходное сопротивление сетки; R{j - сопротивление нагрузки. Эквивалентная схема декодирующего преобразователя на основе матрицы R-2R со стороны входного зажима пред ставлена на фиг. 3 Б. Если выход матрицы R-2R является потенциально заземпенной точкой, а именно такому случаю соответствует применение ее в качестве элемента входной цепи решающего усилителя, то эквивалентная YN определяется выражепроводимостьнием Y --BblK 1 и;г R откуда следует, что на основе сетки R-2R возможно построение эквивалента цифровой управляемой проводимости. Коэффициенты передачи операционных усилителей 21 и 22 при этом (фиг. YH, N , . С,, C,,.R-Z

У Y эквивалентная проводидемость блоков цифровой управляемой проводимости 29 и 30 (фиг. 2о(); . емкость конденсаторов 33 55

Г Г - и 34 (фиг. 28),. Таким образом, коэффициенты передачи интеграторов а, и а могут при , при

Т - период нходного сигнала,с; k - номер гармоники. Вычисленные амшштуда и фаза представляются .в устройстве в влде напряжения:

(12;

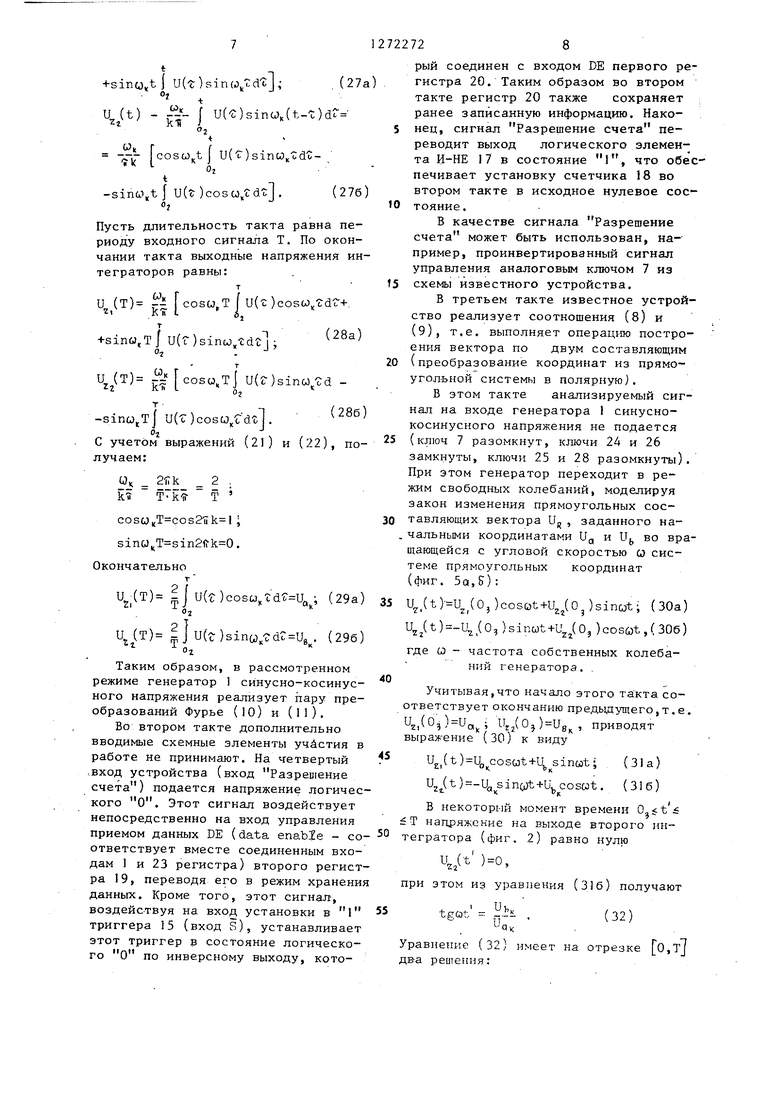

IL С, с« 72 меняться под воздействием управляющего кода. Схема четьфехразрядного блока 4 цифровогоуправляемого сопротивления (фиг. 4) может быть реализована с использованием дискретных резисторов и аналоговых ключей, подобных указанным. Сопротивление блока 4 описывается выражением , (5) R где N - управляющий код (обратный) блок 4 цифрового управляемого сойротивления; m - разрядность блока. Переход к обратному коду в выражении (З) связан с тем, что для современных интегральных аналоговых ключей замкнутое состояние обеспечивается при уровне логической I на входе.управления ключа. Коэффициент передачи сумматора а (фиг. .2а,Б) с учетом выражения (5) оказьшается равным т.е. может изменяться под воздействием управляющего кода блока 4 цифрового управляемого сопротивления. Коэффициент передачи сумматора (фиг. 2а,5) i: Устройство определяет амплитуду CK и фазу Cfi для гармоники входного сигнала U(t) в соответствии с выражениями: C, -Ja cp arctg -- +n I U(t) I dt; (10) ||,Kt)si sin2ffk , (K. где масштабный коэффициент по фазе для аналогового выхода, В/рад, и дополнительно в виде кода: NcrMeC,-, где Mj, - масштабный коэффициент по ампли уде для цифрового выхода, 1/В; М( - масштабный коэффициент по фазе для цифрового выхода. 1/рад. Устройство работает следующим об разом. Весь линейчатый амплитудно-фазовый спектр вычисляется за время цик ла. Цикл состоит из К выполняемых последовательно во времени подциклов, в каждом из которых вычисляетс амплитуда и фаза .очередной гармоники. Каждый подцикл содержит четыре такта разной длительности. Функционирование предлагаемого устройства в первом-втором тактах происходит так же, как визвестном. Обозначение вида О в дальнейшем соответств ет началуотсчёта времени в i-м так те. В первом такте на всех интеграто рах устройства устанавливаются нуле вые начальные условия (фиг. 5, интервал 0,-Oj, что достигается замы канием ключей 10 (фиг. l) и 25, 28 (фиг. 2а) на время, достаточное дл полного разрда конденсаторов 6 (фиг. 1) и 33, 34 (фиг. 2а), ключи 7, 9, 12 (фиг. 1), 24 и 26 (фиг. 2о разомкнуты. Во втором такте вычисляются коэф фициенты разложения в ряд Фурье aj, и Ъ, т.е. реализуются соотношения (10) и (П). Для этого входной сигнал U(t) подается на вхйд генера тора 1 синусно-косинусного напряжения через замкнутый ключ 7 (фиг. 1) Ключи 24 и 26 (фиг. 2а) замыкаются, соединяя интеграторы и сумматор в замкнутое кольцо, ключи 25 и.28 (фиг. 2а)разомкнуты. Уравнение для выходного напряжения первого интегратора (фиг. 26) в операторной форме -Ъ -«.Ujp)-a,U(p), (15) 1 72ф где и(р) - входное напряжение устройства в операторной форме, Учитывая, что выходное напряжение второго интегратора и (р).- tiu (р). подстановкой выражения ( 16) в формулу (15) получают уравнение замыкания: ) и, (р)4 и(р) (17) Аналогично получают для выходного напряжения второго интегратора: ..(Р)- ---р- и,.(р)9. 9.2 9-4 --pz - Из выражений (17) и (18) получают систему уравнений: и(р), (19а) и„(р)- а. г (196) Положим Р выражения (19) WIK Р и„(р) k7 р + Jf СОкfJic .VP) - R (р) Из таблицы функций, преобразованных по Лапласу, извлекают: ( )coscj,tВоспользуемся теоремой свертывания ,(p)-F(p)./f ()-f,(t-t)d: (26) и преобразуем выражение (23) с учетом выражений (24) и (25) во времен-, ную область: и, (t) if---f U(r)cosO,(t-l)dt . о. к Г I U(7r)ce ;ci;- cosu t c©sco tdc+t1+sino,t I U(t)sinw,;:dt;J; u(t) - I u(e)sinwK(t-t)d -X-,- cosw,t U(i:)sinw odt L0, -sina t 1 U(o )cosu,i:dtj,(27б Пусть длительность такта равна периоду входного сигнала Т. По окончании такта выходные напряжения ин теграторов равны: и (Т) - fcoscj.T f U(C)coscJ,rdC-+. 2iKIT Iej +sincj,T/ U(r)sinco, и (T) f U(e)sinu d I0 -sinOjTJ U(t)cosu rdtj. С учетом выражений (21) и (22), по лучаем: WK 2hk 2 . k f cosoKT cos2lIk l ; sinO T sin2fi-k 0. Окончательно U2,(T) | U()cosu,Td7..U,; (29а U(T) j U(t) . (296 oi Таким образом, в рассмотренном режиме генератор 1 синусно-косинус ного напряжения реализует пару пре образований Фурье (Ю) и (П). Во втором такте дополнительно вводимые схемные элементы участия работе не принимают. На четвертый вход устройства (вход Разрешение счета) подается напряжение логиче кого О. Этот сигнал воздействует непосредственно на вход управления приемом данных DE (data enable - с ответствует вместе соединенным вхо дам 1 и 23 регистра) второго регис ра 19, переводя его в режим хранени данных. Кроме того, этот сигнал, воздействуя на вход установки в 1 триггера 15 (вход S), устанавливае этот триггер в состояние логического О по инверсному выходу, кото728рый соединен с входом DE первого регистра 20. Таким образом во втором такте регистр 20 также сохраняет : ранее записанную информацию. Наконец, сигнал Разрешение счета переводит выход логического элемента И-НЕ 17 в состояние 1, что обеспечивает установку счетчика 18 во втором такте в исходное нулевое состояние. В качестве сигнала Разрешение счета может быть использован, на- пример, проинвертированный сигнал управления аналоговым ключом 7 из схемы известного устройства. В третьем такте известное устройство реализует соотношения (8) и (9), т.е. выполняет операцию построения вектора по двум составляющим (преобразование координат из прямоугольной системы в полярнуюJ. В этом такте анализируемый сигнал на входе генератора 1 синуснокосинусного напряжения не подается (ключ 7 разомкнут, ключи 24 и 26 замкнуты, ключи 25 и 28 разомкнуты). При этом генератор переходит в режим свободных колебаний, моделируя закон изменения прямоугольных составляющих вектора U, заданного начальными координатами Ug и U во вращающейся с угловой скоростью о системе прямоугольных координат (фиг. 5а,&): U.(t )-U(0, )cosot+U,(0, )sinot (ЗОа) U(t)-U,(03)sinut+U(0, )costot,(306) где со - частота собственных колебаний генератора. Учитывая,что начало этого такта сответствует окончанию предыдуп(его,т. е. Uz,(03)Ua, ; r/0})U8, приводят выражение (ЗО) к виду Uj.,(t)(ot+U sinut- (31 а) U.,(t): -Ug sincjt+U,coswt. (316) В некотормй момент времени 0.t Т напряжские на выходе второго инегратора (фиг. 2) равно нулю Ujt), ри этом из уравнения (31 б) получают tg.t ;jb.. t,;;.tot : .(32) равнение (32) имеет на отрезке 0,Tj ва решения:

t;. 1 arctg be (33a)

.WUg

t l(arct.g Hi -Hir). (336) Физически это означает, что выходно напряжение второго интегратора за период свободных колебаний проходит через нуль дважды. В ссответствии с уравнением (9) при Ua в качестве решения должно быть принято уравнение (ЗЗа), при - уравнение (ЗЗб). Схема выби .рает правильное решение автоматически, если- дополнительно потребовать, чтобы в MOMfeHT решения t выходное напряжение второго интеграто ,ра, переходя через нуль, меняло зна с минуса на плюс. При этом момент времени -t отмечается положительным перепадом напряжения () на (фиг. 5д), а выходе компаратора 2 t i(arctg -Ь- +nf), (34) , -ак при U(j О и при . Таким образом, интервал от начала такта до указанного момента пропорционален искомой фазе анализируемой гармоники. Этот интервал преобразуется в напряжение, как в известном устройстве и дополнительно в код. Преобразование интервал-напряжение выполняется в этом же такте тре тьим интегратором на основе операционного усилителя 3 (фиг. 1) ,ключ 9 замкнут, ключ 10 разомкнут): Uj,U)a,U.t, напряжение опорного источника постоянного напряжения, В; .Чг коэффициент Передачи третьего интегратора, с, :Эквивалентная Проводимость блока 5 и.ифровой управляемой проводимости определя емая из Пыражения (-2),См; емкость конденсатора, Ф. В момент времени t выходное напряжение третьего интегратора из выражений (35) и (34) arctg( ) + t 2-2 Uz,( ) Uo.

1272272

10

-Uc

(37)

пропорционально Cfij, .

Из сравнения выражений (12) и (37) масштабный коэффициент для аналогового выхода по фазе 1 0 Частота собственных колебаний генератора (фиг, 2) Q л|а, а. а, (20) и (21) и при выполнении условий (АО) Q ,aj,. С учетом формул (2)-(4), (Зб) имеем: ,, N9 YNIO UJ - ... Ь| Ьц .тт cf г Y о k--fttВыражение (42) позволяет определить масштабный коэффициент по фазе для аналогового выхода, из него следует также вывод о том, что для независимости m.(f от номера гармоники достаточно подавать на входы управления блоков 5 и 29, 30 одинаковые коды N. В предлагаемом устройстве в третьем такте на вход N подается код N,, обеспечивающий настройку генератора на первую гармонику(,), Из уравнений (2) и (41) ,. 21|РС„ „ 2ЯВС, п И. -. d --- .. .. В момент времени t размыкается ключ 9, а ключ 11 замыкается, передавая Uy, на второй выход устройстВ этом такте определяется и значение фазы в цифровой форме. Сигнал Разрешение счета принимает значение логической I (фиг,56) Напряжение на выходе одновибратора 16 нормально имеет значение логической 1, соответственно при этом выход логического элемента И-НЕ 17 приобретает значение, логического О. При этом, счетчик 18 подсчитыва-, ет импульсы опорной частоты fon (фиг.5 г, ). В момент времени t число, накопленное в счетчике, оказывается рарным ( fon f N(t )t. arctg(r. +П or. аГГ f Т Из сравнения выражений (14) и (44) масштабный коэффиииент по фаз для цифрового выхода f . Ф м о f 21Г Положительный перепад на выход компаратора 2 в момент времени t (фиг. 5д), поступая на динамически тактовый вход регистра 19 обеспечи вает считывание кода N(. из счетчик 18 в регистр 19. Кроме того, указа ный перепад запускает одновибратор 16, на выходе которого формируется короткий импульс отрицательной полярности и (фиг.5е). Этот импульс инвертируется логическим элемент И-НЕ 17 (на втором входе элемент логическая 1) и сбрасывает счетчик 18 в исходное нулевое состояни подготавливая его к- работе в новом такте. В третьем такте определяется и значение амплитуды в аналоговой фо ме. Преобразуем уравнение (31а) к в ду., )U cosot+U sinat |Ua, +и cos(cot-q)), причем , й-- г. о--Согласно выражению (32) в момент времени t . Ubk tgcrt- , откуда следует, 4Totot и Uj,/t );iu,. г 2 -г, Ck т.е. в моМент времени t . выходное напряжение первого интегратора (фиг. 2) равно амплитуде k-й гармоники исследуемого сигнала. Замыкание в указанный момент вр мени ключа 8 позволяет передать зн чение амплитуды в форме напряжения в регистрирующее устройство. Продолжительность третьего такта -является величиной переменной, изменяющейся и пределах 0-Т в зависимости от начальной фазы k-й гармоники. Четвертый такт в предлагаемом устройстве требуется для определения значения амплитуды в цифровой форме. Начало четвертого такта отмечается сменой состояния триггера 15 под воздействием положительного перепада на выходе компаратора 2 на вход синхронизации (тактовый) триггера. Состояние логической 1 на инверсном выходе триггера 15 разрешает запись информации в регистр 20. Ключи 7, 9, 10 разомкнуты (фиг.. 1), ключ 9 (фиг. 1) замкнут. В генераторе 1 синусно-косинусного напряжения (фиг. 2) ключи 25, 26 и 28 разомкнуты, ключи 24 и 26 замкнуты. В этом такте напряжение, равное амплитуде k-й гармоники (47), преобразуется в результате списывания его напряжением опорного источника в пропорциональный временной интервал. Напряжение на выходе первого интегратора линейно изменяется до нуля по закону: U.(t)Uj,,(04 )-aga,,Ue. t, (48) где Uj/O) напряжение на выходе первого интегратора в начале первого такта. В; R4 д,д, а. rg- - коэффициент переда чи сумматора (фиг,2) по третьему входу; 1 коэффициент передачи первого интегратора, с, определяеъът формулой (3); Up - напряжение опорного источника, В. . В момент -времени t напряжение на выходе первого интегратора равно нулю, при этом из выражения (47); « y,,(oj Uc. , . и;га7Га; u;, В начале четвертого такта счетчик 18 сбрасывается в исходное нулевое состояние, поэтому число, Накопленное в счетчике 18 на момент времеj к ни t :. ,M,.U,N,.(50) Масштабный коэффициент по пиетровоу выходу и. а:- Ё; 13 : в момент перехода выходного напряжения первого интегратора через нуль t компаратор 14 изменяет свое состояние с О на 1 {фиг. 5ж). Этот перепад, поступая на вход синхронизации (тактовый) регистра 20, обеспечивает считывание кода W. из счетчика 18. Этим тактом подцикл заканчивается Далее, если это необходимо, начинается новый подцикл, в котором вычисляется другая гармоника. При практической реализации в кон кретной элементной базе часть дополнительных элементов может быть исключена. Например, для сброса установки в О счетчика может быть дополнительно использована запись в счетчик числа 0000 (в двоичной системе счисления) с использованием соответствующих входов микросхемы. При I этом исключается логический элемент ;И-НЕ. Одновибратор мо)ет быть реали.зован на основе неиспользованных триггера, логических элементов, компаратора, т.е. бепiпривлечениядопол нительных аппаратурных средств. Таким образом, получение результатов измерения- в форме кода достигается практически лишь введением счетчика и двух регистров. При использовании одного аналогоцифрового преобразователя для хранеНия кода также должнг использованы регистры. Б итоге имеем вместо ;аналого-цифрового; преобразователя, счетчик, который значительно более де, шев и надежен.Кроме того,известные однокристальные аналого-цифровые преоб разователи тербуют значительных допо нйтельных аппаратурных затрат для фо мирования управляющих сигналов, ста обильного опорного напря ения и т.д. . Предлагаемое устройство позволяет дополнительно к аналоговым значениям представлять результаты измере,ния амплитуды и фазы в цифровом ви де. При этом становится возможным использование известного устройства в управляющих и измерительных сис122 темах с цифровой формой представления информации, что существенно распшряет его область применения. При использовании устройства в качестве автономного измерительного прибора наличие кодовых выходов позволяет применять цифровые индикаторные и запоминающие устройства, что также приводит к расширению области применения. Формула изобретения Амплитудно-фазовый анализатор гармоник по авт.св. № 815669, о т л ичающийся тем, что, с целью расширения функциональных возможностей, в него дополнительно введены аналоговый ключ, резистор, компаратор, триггер, Одновибратор, логический элемент И-НЕ, счетчик, первый и второй регистры, причем третий вход устройства через последовательно соединенные аналоговый ключ и резистор соединен с первым входом генератора синусно-косинусного напряжения, первый выход которого соединен с входом дополнительного компаратора, выход которого соединен с первым входом первого регистра, второй вход которого связан с выходом триггера, выход компаратора соединен с первыми входами второго регистра и триггера и входом одновибратора, выход которого соединен с первым входом логического элемента И-НЕ, выход которого соединен с первым входом счетчика, четвертый вход устройства соединен с вторыми входами триггера, второго регистра и логического элемента И-НЕ, пятый вход устройства соединен с вторым входом счетчика, выход которого соединен с третьими входами первого и второго регистров, выход первого регистра соединен с третьим выходом устройства, выход второго регистра соединен с четвертым выходом устройства, третий вход триггера, второй вход компаратора и второй вход дополнительного компаратора соединены с общей тиной.

il29(t}

.Z

2fJ HZ 2f

Я

cp

| название | год | авторы | номер документа |

|---|---|---|---|

| Амплитудно-фазовый анализатор гар-МОНиК | 1979 |

|

SU815669A1 |

| Амплитудно-фазовый анализатор гармоник | 1984 |

|

SU1307371A1 |

| Анализатор гармоник | 1985 |

|

SU1364996A2 |

| Анализатор гармоник | 1985 |

|

SU1347033A2 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Устройство для измерения рассогласования между углом и кодом | 1987 |

|

SU1411973A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГОЛ - КОД | 1991 |

|

SU1826836A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1293842A1 |

| Устройство для измерения рассогласования между углом и кодом | 1985 |

|

SU1277397A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 1980 |

|

SU1840148A1 |

Изобретение относится к электроизмерительной технике. Является iдополнительным к авт.св. СССР № 815669. Цель изобретения - расширение функциональных возможностей. В устройство, содержащее генератор 1 синусно-косинусного напряжения, операционный усилитель 3, блок 4 цифрового управляемого сопротивле ния, блок 5 цифровой управляемой проводимости, аналоговые ключи 7-11, для достижения цели введены аналоговый ключ 12, резистор 13, компаратор 14, триггер 15, одновибратор 16, логический элемент И-НЕ 17, счетчик 18, регистры 19, 20. Устройство позволяет дополнительно к ан алоговым значениям представлять результаты измерения амплитуды и фазы в цифровом виде. При использовании устройства в качестве автономного измериСО тельного прибора наличие кодовых выходов позволяет применять цифровые с индикаторные и запоминающие устройства, что приводит к расширению области применения. 5 ил. 1уаД Ю го ю IsP

л-г А/Л-/

W /V /V

, R FI ГЛ

dJ

CZD1

-cmi JФиг.

а)

6)

О, QZ t

(K- llJWSUUKK

Фиг.5

| Аналоговые и цифровые интегральные схемы./Справочное пособие под ред | |||

| Якубовского С.В | |||

| - М.: Радио и связь, 1984 | |||

| Авторское свидетельство СССР р | |||

| Амплитудно-фазовый анализатор гар-МОНиК | 1979 |

|

SU815669A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1986-11-23—Публикация

1985-03-26—Подача