Изобретение относится к электротехнике, а именно к релейной защите, может быть использовано длязащиты сборных шин электростанций и подстанций, ошнновок силовых трансформаторов и автотрансформаторов, высоковольтных электродвигателей и синхронных компенсаторов.

Цель изобретения - повышение селективности в режимах перехода внешнего короткого замыкания во внутреннее короткое замыкание, а также при внутренних коротких замыканиях, сопровождающихся наличием вытекающих токов.

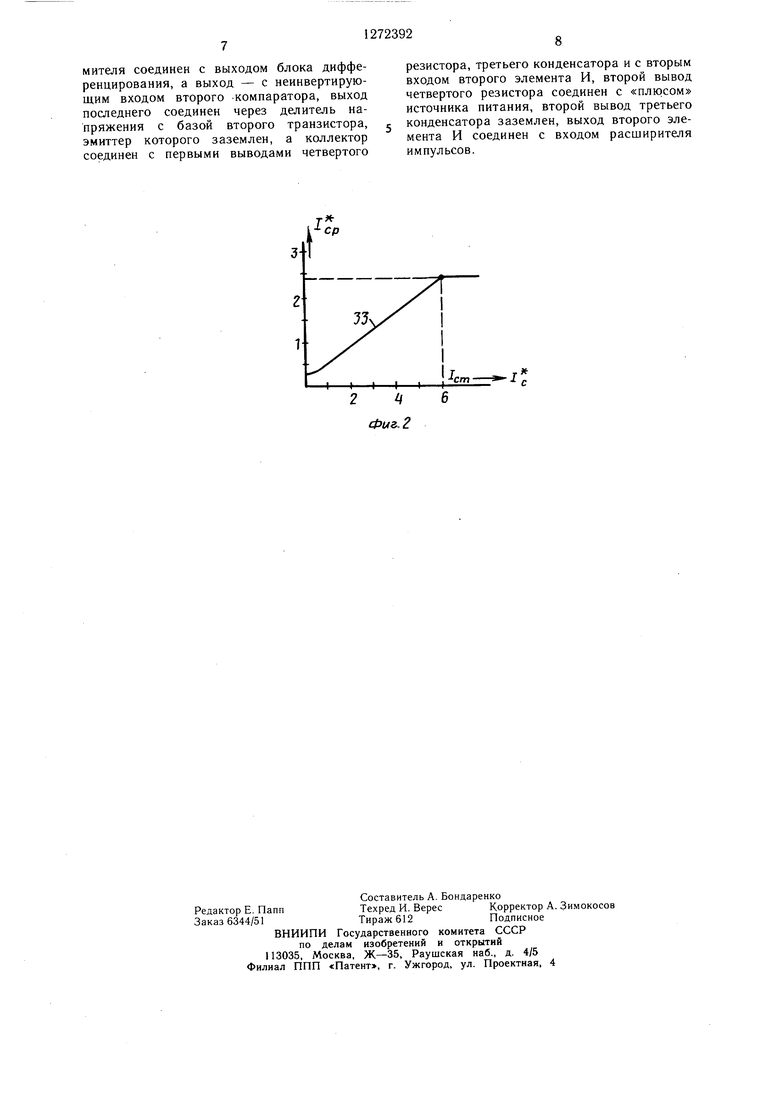

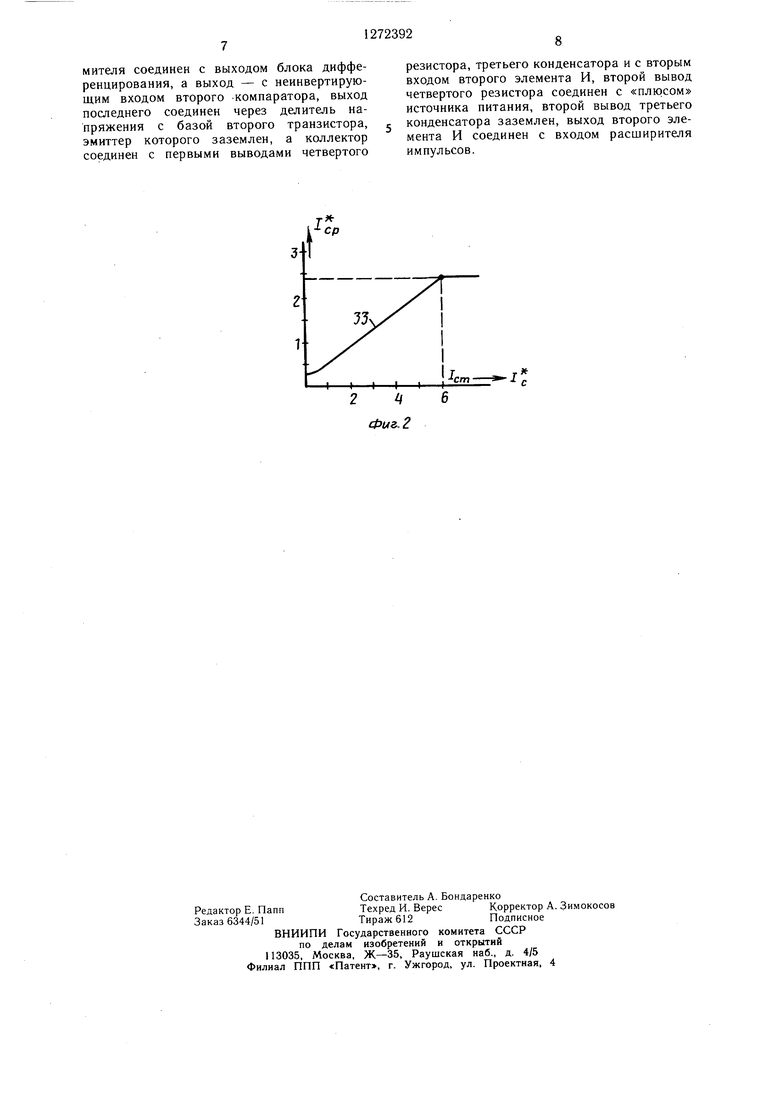

На фиг. 1 показана структурная схема предлагаемого устройства защиты; на фиг. 2 - характеристика срабатывания компаратора, формующего логические сигналы.

Устройство дифференциальной защиты устанавливается для защиты сборных шин 1 (фиг. 1) и содержит блок 2 датчиков тока, одни концы вторичных обмоток которых объединены, а другие присоединены к многоплечевому диодному полумосту 3, катоды и аноды диодов которого объединены и подключены к двуплечевой схеме 4 сравнения со средней точкой.

Через выпрямительный имост 5 реагирующий орган 6 соединен с выходом схемы 4 сравнения. Пусковой орган 7 включен между общей точкой вторичных обмоток датчиков тока и средней точкой схемы 4 сравнения. Первый логический элемент И 8 соединен своими первым и вторым входами с выходами реагирующего 6 и пускового 7 органов соответственно и подключен выходом к входу выходного органа 9. Дифференциальное сопротивление нагрузки 10 включено последовательно с пусковым органом 7 между общей точкой вторичных обмоток датчиков 2 тока и средней точкой схемы 4 сравнения, причем средняя точка схемы 4 сравнения соединена с одним концом дифференциального сопротивления 10 нагрузки и заземлена. Инверсирующий вход сумматора 11 соединен с анодами, а неинвертирующий - с катодами многоплечевого диодного полумоста 3. Выход сумматора 11 соединен с неинвертирующим входом первого компаратора 12, с первым входом формирователя 13 опорного напряжения и входом блока 14 задания уставки. Выход формирователя 13 опорного напряжения соединен с инвертирующим входом первого компаратора 12, а выход последнего - с первым входом второго элемента И 15.

Выходы ждущего мультивибратора 16 и расширителя 17 импульсов подключены к выходу второго элемента И 15.

Выход расширителя 17 импульсов соединен с входом элемента НЕ 18, выход которого подключен к третьему входу первого элемента и 8. Вход второго выпрямительного моста 19 соединен с выходом дифференциатора 20, вхол которого соединен с

незаземленным концом дифференциального сопротивления 10, а выход выпрямителя 19- с неинвертирующим входом второго компаратора 21, инвертирующий вход которого подключен к выходу блока 14. Первый выход ждущего мультивибратора 16 соединен с вторым входом формирователя 13 опорного напряжения, а второй выход ждущего мультивибратора 16 - с третьим входом формиррователя 13 опорного напряжения. Первым

входом формирователя 13 является анод диода 22, катод которого соединен с одним концом первого резистора 23, другой вывод которого связан с вторым резистором 24, коллектором первого транзистора 25, первым конденсатором 26, одним концом второго конденсатора 27, другой же вывод второго резистора 24 соединен с одним выводом третьего резистора 28 и является выходом формирователя 13 опорного напряжения. Второй вывод третьего резистора 28 соеди0 нен с вторым выводом второго конденсатора 27 и является вторым входом формирователя 13 опорного напряжения. Эмиттер первого транзистора 25 заземлен, а база является третьим входом формирователя 13. Выход второго компаратора 21 через де5 литель 29 соединен с базой второго транзистора 30, эмиттер которого заземлен, а коллектор связан с одним выводом третьего конденсатора 31, другой вь1вод которого заземлен, с одним выводом четвертого резистора 32 и с вторым входом второго элемента И 15. При этом второй вывод резистора 32 подключен к «плюсу источника напряжения.

Блок 14 может быть выполнен, например, по схеме (не показана), содержащей резисг торные делители напряжения, конденсатор, транзистор и разделительные диоды.

При этом анод одного из разделительных диодов является входом блока 14, а катод соединен с базой транзистора, включенного по схеме эмиттерного повторителя,

0 и с одним концом конденсатора, второй конец которого заземлен. К эмиттеру транзистора подключены первый резисторный делитель напряжения, который является выходом блока 14, и через второй разделительный диод - второй резисторный делитель

5 напряжения, подключенный к источнику питания.

Блоком 2 датчиков тока вторичные токи трансформаторов тока уменьшаются до удобной для дальнейших преобразований величины, разделяются по знаку полупериода

многоплечевым диодным полумостом 3 и поступают на схему 4 сравнения, выполненную на резисторах и стабилитронах.

Напряжение на выходе схемы 4 сравнения пропорционально длительности несовпас дения ограниченных по амплитуде сигналов с ее плеч при токах более тока стабилизации, при токах менее тока стабилизации - пропорционально дифференциальному току.

Это напряжение выпрямляется выпрямительным мостом 5 и подается на реагируюющий орган 6, представляющий электронное реле времени. Пусковой орган 7 и резистор 10 включены в дифференциальную цепь. Защита срабатывает, если срабатывает реагирующий орган 6 и пусковой орган 7 и на третьем входе элементе И 8 имеется при этом сигнал логической 1. Время срабатывания защиты составляет 3-4 мс и определяется соответствующим временем блокировки реагирующего органа 6.

Для обеспечения селективности при переходных процессах во входных цепях защита при определенном уровне напряжений на плечах схемы сравнений формирует импульсы запуска, которые сравниваются во времени с паузами в производной дифференциального тока. При этом уровень запуска не является постоянным и плавно изменяется в зависимости от величины напряжения на плечах схемы 4 сравнения.

Для этого предусмотрен формирователь 13 опорного напряжения, задающий на инвертирующем входе компаратора 12 исходный уровень запуска, превыщающий в нормальном установивщемся режиме напряжение на неинвертирующем входе того же компаратора. При внезапном КЗ напряжение на схеме 4 сравнения изменяется скачок (в течение одной полуволны тока КЗ) как минимум в 1,5-2 раза. При этом уровень запуска за это время существенно не возрастает, и напряжение на неинвертирующем входе компаратора 12 становится больще опорного на инвертирующем входе.

В случае внещнего КЗ дифференциальный ток до насыщения трансформаторов тока равен нулю, следовательно и его производная на выходе дифференциатора 20 равна нулю, и состояние второго компаратора 21 остается неизменным. При этом транзистор 30 закрыт и на обоих входах второго логического элемента И 15 имеются логические «1. Сигналом с выхода элемента И 15 запускается ждущий мультивибратор 16, который предназначен для снижения уровня запуска при внещних КЗ на время затухания переходного процесса в цепях защиты, кроме того, этот же сигнал удлиняется расширителем 17 импульсов до 25 мс и в качестве логического нуля с выхода элемента НЕ 18 поступает на третий вход первого элемента И 8, блокируя защиту.

Уровень замера пауз в производной дифференциального тока принят изменяемым в зависимости от сквозного тока. Это позволяет при Бнещних КЗ с током более тока стабилизации повысить уровень замера пауз по сравнению с известным устройством более, чем в 2 раза. Одновременно устраняется ВОЗМОЖНОСТЬ блокирования защиты при переходе внешнего КЗ во внутреннее с малым током КЗ.

Устройство работает следующим образом. В исходном режиме работы напряжение на инвертирующем входе первого компаратора 12 определяется делителем от источника питания, напряжением логической единицы на первом выходе ждущего мультивибратора 16 и установивщимся значением напряжения на первом конденсаторе 26 и превыщает напряжение на неинвертирующем входе.

0 При этом напряжение на втором выходе ждущего мультивибратора 16 соответствует логическому нулю и первый транзистор 25 закрыт.

При внешнем КЗ напряжение на неинвертирующем входе компаратора 12 соответствует возросщему напряжению на выходе сумматора 11, тогда как напряжение на инвертирующем входе возрастает плавно, что определяется постоянной Н2зС2б- Поэтому компаратор 12 срабатывает и, поскольку в

0 начале переходного процесса ток в дифференциальной цепи отсутствует, на обоих входах второго элемента И 15 имеются логические «1, что и является признаком внещнего КЗ.

После запуска ждущего мультивибратора

5 16 напряжение на его первом выходе становится равным напряжению логического нуля, а на втором - логической единицы. При этом открывается первый транзистор 25 и шунтирует конденсатор 26, что приводит к снижению порога запуска до минимально го.

Появившийся вследствие насыщения трансформаторов тока дифференциальный ток дифференцируется блоком 20, знакопеременный сигнал с выхода дифференциатора выпрямляется выпрямителем 19 и поступает на неинвертирующий вход второго компаратора 21, порог срабатывания которого задается блоком 14.

Характеристика 33 срабатывания компаратора 21 для синусоидального тока часто0 той 50 Гц в значениях относительно номинального тока трансформатора тока наиболее мощного присоединения приведена на фиг. 2.

Выделяемые таким образом признаки внешнего КЗ проявляются в каждом периоде

переходного процесса, поэтому вполне достаточно расширение импульса с выхода элемента И 15 до 25 мс. По истечении времени, достаточного для затухания переходных токов небаланса, ждущий мультивибратор 16 возвращается в исходное положение, пер0вый транзистор 25 закрывается, подготавливая схему к исходному режиму.

Однако после отключения внешнего КЗ под воздействием сквозных токов нагрузки вновь сработал бы компаратор 12 и запустил

2 бы ждущий мультивибратор 16 и i. д., поскольку первый конденсатор 26 за одну полуволну не успевает зарядиться до напряжения, достаточного для запирания компаратора 12. Чтобы этого не происходило, предусмотрен второй конденсатор 27, через который получает дополнительный заряд первый конденсатор 26 после возврата ждущего мультивибратора 16.

В любом режиме внутреннего КЗ, как и при внешнем КЗ, запускается компаратор 12, однако одновременно с этим (и даже несколько раньше, так как чувствительность второго компаратора 21 выше, чем первого 12) срабатывает второй компаратор, транзистор 30 открывается, и на втором входе логического элемента И 15 появляется логический

Последний не выдает импульс запуска на расширитель 17 импульсов и ждущий мультивибратор 16. Напряжение на первом конденсаторе 26 во втором периоде уже возрастает настолько, что первый компаратор в дальнейшем не запускается. Однако при переходе дифференциального тока через максимум его производная проходит через ноль и, следовательно, компаратор 21 на некоторое время возвращается в исходное состояние, причем в это время первый компаратор 12 выдает на вход элемента И 15 потенциал высокого уровня, что соответствует признакам внешнего КЗ. Для того, чтобы импульс запуска элементом И 15 в этом случае не формировался, предусматривается задержка на появление логической единицы на втором входе элемента И 15.

Реализуется такая задержка RC-цепью резистор 32 - конденсатор 31. Следует заметить, что длительность задержки и крутизна характеристики срабатывания второго компаратора 21 взаимосвязаны.

Так для заданной крутизны характеристики срабатывания (фиг. 2) длительность задержки выбирается таким образом, чтобы при внутреннегом КЗ и наличии примерно 20% вытекающего тока нагрузки с взаимным углом 180° зашиты не блокировалась в диапазоне токов от 1 т и более.

При внезапных внутренних КЗ с односторонним питанием, при наличии нескольких источников питания и сдвинутых по фазе тока, а также при наличии вытекающих токов нагрузки время срабатывания определяется временем блокировки реагирующего органа 6 и составляет примерно 4 мс. В более сложном случае - при переходе внешнего КЗ во внутреннее - задержка в срабатывании не превысит 14 мс.

Формула изобретения

Устройство дифференциальной защиты, содержащее блок датчиков тока, одни концы вторичных обмоток которых объединены, а другие присоединены к многоплечевому диодному полумосту, катоды и аноды диодов которого объединены и подключены к двуплечевой схеме сравнения со средней точкой, реагирующий орган, соединенный с выходом схемы сравнения через первый выпрямитель, пусковой орган, включенный последовательно с дифференциальным сопротивлением нагрузки между общей точкой вторичных обмоток датчиков тока и средней точкой схемы сравнения, которая при этом заземлена, первый логический элемент И, первый и второй входы которого соединены с выходом реагирующего и пускового органов, а выход - с входом выходного органа, два компаратора, второй элемент И, первый вход которого соединен с выходом первого компаратора, расширитель импульсов, выход которого соединен с входом инвертора, а выход последнего - с третьим входом первого элемента И, блок дифференцирования, выход которого соединен с незаземленным концом дифференциального сопротивления нагрузки, формирователь опорного напряжения, выход которого соединен с инвертирующим входом первого компаратора, причем формирователь опорного

0 напряжения содержит диод, первый, второй и третий резисторы, первый конденсатор, при этом анод диода является первым входом формирователя опорного напряжения, катод соединен с одним выводом

5 первого резистора, второй вывод которого соединен с первыми выводами второго резистора и первого конденсатора, второй вывод первого конденсагора заземлен, второй вывод второго резистора соединен с одним выводом третьего резистора и явля0ется выходом формирователя опорного напряжения, второй вывод третьего резистора является вторым входом формирователя опорного напряжения, ждущий мультивибратор, вход которого соединен с выходом второго элемента И, а первый выход - с вторым

5 входом формирователя опорного напряжения, отличающееся тем, что, с целью повыщения селективности, дополнительно введены сумматор, блок задания уставки, первый и второй транзисторы, второй и третий конденсаторы, четвертый резистор, второй выпря0митель и делитель напряжения, при этом инвертирующий вход сумматора соединен с анодами многоплечевого диодного полумоста, а неинвертирующий вход - с катодами, выход же сумматора соединен с не5инвертирующим входом первого компаратора, первым входом формирователя опорного напряжения и входом блока задания уставки, выход которого соединен с инвертирующим входом второго компаратора, второй выход ждущего мультивибратора сое0динен с базой первого транзистора, которая является третьим входом формирователя опорного напряжения, эмиттер первого транзистора заземлен, а коллектор соединен с первыми выводами первого и второго конденсаторов формирователя опорного напря5жения, второй .вывод второго конденсатора соединен с вторьш входом формирователя опорного напряжения, вход второго выпрямителя соединен с выходом блока дифференцирования, а выход - с неинвертирующим входом второго компаратора, выход последнего соединен через делитель напряжения с базой второго транзистора, эмиттер которого заземлен, а коллектор соединен с первыми выводами четвертого

резистора, третьего конденсатора и с вторым входом второго элемента И, второй вывод четвертого резистора соединен с «плюсом источника питания, второй вывод третьего конденсатора заземлен, выход второго элемента И соединен с входом расширителя импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дифференциальной защиты электроустановки | 1983 |

|

SU1141498A1 |

| Устройство для защиты сборных шин электрических станций и подстанций | 1982 |

|

SU1019539A1 |

| Устройство для дифференциальной защиты | 1987 |

|

SU1429212A2 |

| Устройство для дифференциальной защиты | 1988 |

|

SU1610533A2 |

| Устройство для защиты сборных шин электростанции и подстанции | 1981 |

|

SU945937A1 |

| Устройство для дифференциальной защиты | 1981 |

|

SU1019538A1 |

| Устройство для дифференциальной защиты двойной системы сборных шин электроустановки | 1987 |

|

SU1492411A1 |

| Устройство для дифференциальной защиты электроустановки | 1985 |

|

SU1259388A2 |

| Стабилизированный преобразователь постоянного напряжения с защитой | 1986 |

|

SU1317597A2 |

| Устройство для дифференциально-фазной защиты | 1982 |

|

SU1113866A1 |

Изобретение относится к области электротехники, а именно к релейной защите электроустановки, и может быть использовано для защиты сборных щин электростанций и подстанций, ошиновок силовых трансформаторов и автотрансформаторов, высоковольтных электродвигателей и синхронных компенсаторов. Цель изобретения - повыщение селективности в режимах перехода внешнего короткого замыкания во внутреннее короткое замыкание, а также при внутренних коротких замыканиях, сопровождающихся наличием вытекающих токов. Устройство содержит блок 2 датчиков тока, устанавливаемых по концам защищаемого объекта. К выходу блока 2 датчиков тока присоединены многоплечевой диодный полумост 3 и пусковой орган 7. К выходу выпрямительного полумоста 3 присоединены последовательно соединенные схема сравнения 4, выпрямитель 5, реагирующий орган 6, элемент И 8 и выходной орган 9. К входам элемента И 8 присоединены также выход пускового ю органа 7 и выход элемента НЕ 18. Повышение селективности достигается введением (Л сумматора 11, блока 14 задания уставки, транзисторов 25 и 30, конденсаторов 26 и 27, выпрямителя 19 и делителя 29. 2 ил. to to оо со ю

| 0 |

|

SU402414A1 | |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для дифференциально-фазной защиты сборных шин | 1977 |

|

SU729718A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для дифференциальной защиты электроустановки | 1983 |

|

SU1141498A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-11-23—Публикация

1985-02-05—Подача