короткого замыкания во внутреннее, введены два формирователя опорного напряжения, два элемента ИЛИ, третий элемент И и ждущий мультивибратор , при этом первый вход первого формирователя опорного напряжения соединен с катодами,а первый вход второго - с анодами многоплечевого диодного полумоста, их вторые входы соединены с первым и вторым выходами ждущего мультивибратора соответственно, выход первого формирователя опорного напряжения соединен с инвертирующим входом первого компаратора, а Еыход второго - с неинвертирующим входом второго Компаратора, выходы обоих компараторов соединены с входами первого элемента ИЛИ, выход которого является первым входом третье-, го элемента И, второй вход последнего соединен с третьим входом второго элемента И, выходом формирователя сигналов запрета и через резистор связан с плюсом источника питания, третий вход третьего элемента И сое.дииен с вторым выходом ждущего мультивибратора, а выход - с первым входом BTQporo элемента ИЛИ, второй вход которого соединен с выходом вто рого элемента И и входом ждущего мультивибратора, а выход- с входом расширителя импульсов.

2. Устройство по п. 1, о т л и чающееся тем, что первый фор1-шрователь опорного напряжения

98

содержит три диода, три резистора и конденсатор, причем анод первого диода является первым входом формирователя, катод соединен с одним концом первого резистора, другой конец которого связан с.вторым резистором и конденсатором с задемленным вторым концом, другой конецвторого резистора соединен с анодами второго и третьего диодов, катод второго диода сбёдинен с одним концом третьего резистора и является вторым входом формирователя, катод третьего диода соединен с другим концом третьего резистора и является выходом формирователя,

3. Устройство по пп, I и 2, отличающееся тем, что второй формирователь опорного напряжения , содержит два диода, стабилитрон, три резистора и крнденсатор, причем катод первого диода является первым входом формирователя, анод соединен с одним концом первого резистора, другой конец которого связаасо вторым резистором и конденсатором с заземленным вторым концом, другой конец второго резистора соединен с катодом второго диода и анодом стабилитрона, катод стабилитрона соединен с одним концом третьего резисто ра и является вторым входом формирователя, анод второго диода соединен с другим концом третьего резистор и является выходом формирователя .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты сборных шин электростанции и подстанции | 1981 |

|

SU945937A1 |

| Устройство для защиты сборных шин электрических станций и подстанций | 1982 |

|

SU1019539A1 |

| Устройство для защиты электроустановки | 1987 |

|

SU1406681A1 |

| Устройство для дифференциальной защиты двойной системы сборных шин электроустановки | 1987 |

|

SU1492411A1 |

| Устройство дифференциальной защиты | 1985 |

|

SU1272392A1 |

| Устройство для дифференциальной защиты | 1988 |

|

SU1610533A2 |

| Устройство для дифференциальной защиты | 1981 |

|

SU1019538A1 |

| Устройство для дифференциальной защиты | 1987 |

|

SU1429212A2 |

| Устройство для дифференциально-фазной защиты электроустановки | 1988 |

|

SU1601684A1 |

| Устройство для дифференциально-фазной защиты электроустановки | 1987 |

|

SU1677762A1 |

1. УСТРОЙСТВО ДЛЯ ДИФФЕРЕНЦИАЛЬНОЙ ЗАЩИТЫ ЭЛЕКТРОУСТАНОВКИ, содержащее блок датчиков тока, одии концы вторичных обмоток которых объединены а другие присоединены к многоплечевому диодному полумосту, катоды,и аноды диодов которого объединены и подключены к двухплечевой схеме сравнения со средней точкой, реагирующий орган, соединенный с выходом схемы сравнения через выпря- митель, пусковой орган, включенный последовательно с дифференциальным сопротивлением нагрузки между общей точкой вторичных обмоток датчиков тока и средней точкой схемы сравнения, которая при этом заземлена, логический элемент И, первый и второй входы которого соедине1ны с выгходом фазного и пускового органов, ; а вьIXo - с входом выходного органа,два компаратора, причем неинвертирующий вход первого компаратора соединен с катодами, инверти рующий вход второго - с анодами мкогоплечевого диодного полумоста, а их выходы являются,первым и вторым входами второго элемента И, расширитель импульсов, выход которого соединен с входом .инвертора, а выход последнего - с третьим входом первого элемента И, блок дифференцирования, вход которого соединен с незаземлешгьм концом дифференциального со.прот11вления, нагрузки, а выход является входом формирователя сигналов запрета, при этом формирователь сигналов запрета содер.г жит два компаратора, три диода, 5 .нагрузочный резистор, конденсатор (Л и инвертор, причем вход формирователя соединен с неинвертирующим с входом первого и инвертирующим вхо,; дом второго компаратора, инвертирующий вход первого компаратора соединен с плюсом источника питания, а неинвертирующий вход второго компаратора - с минусом, выходы Компараторов подключены к анодам двух диодов, катоды которых объединены в общ5по точку с входом инвертора, одним концом нагрузочного резисто4 СО ЭО ;ра и конденсатора, другие концы ко торых заземлены, выход инвертора соединен с катодом третьего диода, анод которого является выходом формирователя сигналов запрета, о тличающееся тем, что, с ,целью повышения надежности работы устройства путем обеспечения устойчивого формирования блокирующего сигнала при внешних коротких замыканиях и быстродействия переориентации защиты 1;ри переходе от внешнего

1

Изобретение относится к релейной защите и может быть использовано для защиты сборных шин электростанций и подстанций, ошиновок силовых трансф.орматоров и автотрансформаторов, высоковольтных электродвигателей и синхронный компенсаторов.

Известно устройство для дифференциапьно-фазной защиты электроустановки, содержащее блок сравнения, пусковой и фазный органы, пороговые органы, ограничитель напряжения, блок гальванического разделения цепей, обладающее высокой чувствительностью и быстродействием ij.

Однако для надежности отстроенности от виещних коротких замыканий (КЗ) необходимо значительное увеличение угла блокировки в этом режиме, для чего используется признак возрастания напряжения на блоке сравнения до удвоенного значения порога ограничения напряжения и запоминание этого признака на несколько периодов (на случай его исчезновения при глубоких насыщениях трансформаторов тока (ТТ). Такой принцип исполнения защиты может привести к за держке в срабатывании пртт переходе внешнего КЗ во внутренне, а также

3

к отказу защиты при определенных условиях внутренних КЗ со сдвинутыми по фазе токами.

Известно также устройство для дифференциально-фазной защиты сборных шин, содержащее датчики тока, включенные в каждое плечо защиты, многоплечевой диодный полумост, схему сравнения на резисторах .и стабилитронах, формирователи входных логических сигналов, блоки апрещёг ния и разрешения срабатывания. 0тстроенность этого устройства от ;внешних КЗ при глубоких насыщениях ТТ обеспечивается путем использования признака идеальной трансформации ТТ до момента насыщения сердечника С 2.

Однако этот признак в устройстве может быть верно использован в большинстве случаев лишь в первом периоде переходного процесса, если он является периодом первоначального насьШ1ения. Если ТТ работает в области средних индукций (в области характеристики намагничивания, расположенной непосредственно за ее перегибом ), возможна ложная выдача разрешающего на- срабатывание защиты сигнала при внешних КЗ. Кроме того, при глубоких насьщ1ениях ТТ напряжение на входе формирователя логического сигнала может оказаться недоста,точным для его запуска, и блокирующий сигнал не будет вырабатываться именно тогда, когда погрешность ТТ максимальна. Обеспечить гарантированную отстроенность защиты от .внешних КЗ в этом устройстве можно, заблоки;ровав логической частью защиту по информации от первого периода на такое время, когда разностная фазовая погрешность в самом неблагоприятном переходном процессе будет меньше угпа блокировки фазного органа. Однако lipH этом возможна задержка в срабатывании защиты при переходе внешнего КЗ во внутреннее или при внутреннем КЗ со сдвинутыми по фазе токами.

Известно также устройство защиты, содержащее датчик тока, включенные в каждое плечо защиты, многоплечевой диодный полумост, схему сравнения на резисторах и стабилитронах, фазный (реагирующий) и пусковой органы, два компаратора, блок дифференцирования, формирователь сигналов запрета, расширитель импульсов

414984

логические элементы, обладающие высоким уровнем отстроенности от внешних повреждений и высоким быстродействием - при внутренних. 5 Однако область использования известного устройства ограничена объектами, номинальный ток которых незначительно отличается от номинальных токов ТТ присоединений, поскольку уровень запуска логической части устройства,, определяющей отстроенность защиты от внешних КЗ, необходимо отстраивать от максимального сквозного тока в рабочем режиме. На

fS сборных шинах мощных ГЭС мощность подключенных генераторов может быть резк-о различной или в течение суток или в определенные времена года. При этом будет резко различным и уровень

20 токов внешних КЗ, который может в минимальном режиме работы станции оказаться менее максимального сквозного тока в рабочем режиме. Это относится и к сборным шинам мощных

25 узловых подстанций, максимальный сквозной ток которых значительно отличается от номинальных токов ТТ присоединений. Кроме того, ус.тойчивость идентификации внешних

30 КЗ этим устройством в периодах, следующих за периодом первоначального насьш ения одного из ТТ, невысока. Таким образом, известное устройство на наиболее ответственных объектах

, энергосистем имеет недостаточный уровень надежности и устойчивости идентификации режимов внешних и внутренних КЗ в течение переходного процесса.

Q , Цель изобретения - повышение надежности работы устройства путем обеспечения устойчивого формиро-. вания блокирующего сигнала при внешних коротких замыканиях /КЗ/ и строй переориентации защиты при

переходе от внешнего КЗ во внутреннее.

Поставленная цель достигается тем, что в устройство для дифференJQ циальной защиты электроустановки, содержащее блок датчиков ток-, одни концы вторичных обмоток которых объедине1ш, а другие присоединены к.многоплечевому диодному полумо-

JJ сту, катоды и аноды диодов которых объединены и подключены к дву: плечевой схеме сравнения со средней точкой, фазньш (реагирующий) орган.

соединенный с выходом схемы срав нения через выпрямитель, пусковой орган, включенный последовательно с диффвр1внциальным сопротивлением нагрузки между общей точкой вторичных обмоток датчиков тока и средней точкой схемы сравнения, которая при этом заземлена, логический элемент И, первый и второй входы которого со.единены с выходом фазного и пускового органов, а выход - с входом выходного органа, два компаратора, причем неинвертирующий вход первого компаратора соединен с катодами, инвертирующий вход второго с анодами многоплечевого диодного полумоста, а их выходы являются первым и вторым входами второго элемента И, расширитель импульсов, выход которого соединен с входом ннвертора.,, а выход последнего - с третьим входом первого элемента И, блок дифференцирования, вход которого соединен с незаземленным концом дифферен1,иального сопротивления нагруз- ки,а выход является входом формирователя сигналов запрета, при этом формирователь сигналов,запрета содержит два компаратора, три диода, нагрузочный резистор, конденсатор и инвертор, причем вход формирователя соединен с неинвертирующим входом первого и инвертирующим входом второго компаратора, инвертирующий вход первого компаратора соединен с плюсом источника питания, а неинвертирующий вход второго компаратора - с минусом, выходы компараторов подключены к анодам двух диодов, катоды которых объединены в общую точку с входом инвертора, одним концом нагрузочного резистора и конденсатора, другие концы которых заземлены, выход инвертора соединен с катодом третьего диода, анод которого является выходом формирователя сигналов запрета, -введены два формирователя опорного напряжения, два элемента ИЛ третий элемент И и ждущий мультивибратор, при этом первый вход первого формирователя опорного напряжения сдинен с катодами, а первый вход второго - с анодами многоплечевого диодного полумоста, их вторые входы соединены с первым и вторым выходами ждущего мультивибратора соответсвенно, выход первого формирователя опорного напряжения соединен -с инвертирующим входом первого компаратора, а выход второго - с неинвертирующим входом второго компаратора выходы обоих компараторов соединены с входами первого элемента ИЛИ, выход которого является первым входом третьего элемента И, второй вход последнего соединен с третьим входом второго элемента И, выходом формирователя сигнадов запрета и через резистор связан с плюсом источника питания, третий вход третьего элемента И соединен с вторым выходом ждущего мультивибратора, а выход с первым входом второго элемента ИЛИ, второй вход которого соединен с чыходом второго элемента И и входом ждущего мультивибратора, а выход - с входом расширителя импульсов.

Первый формирователь опорного напряжения содержит три диода, три резистора и конденсатор, причем ано первого диода является первым входом формирователя, катод соединен с одним концом первого резистору, другой конец которого связан с вт.орым резистором и конденсатором с заземленным вторым концом, другой конец второго резистора соединен с, анодами второго и третьего диодов, катод второго диода соединен с одним концом третьего резистора и является вторым входом формирователя, катод третьего диода соединен с другим концом третьего резистора и является выходом формирователя.

Второй формирователь опорного напряжения аналогичен первому за исключением того, что первьй и третий диоды имеют обратную полярность включения, а вместо второго диода используют стабилитрон.

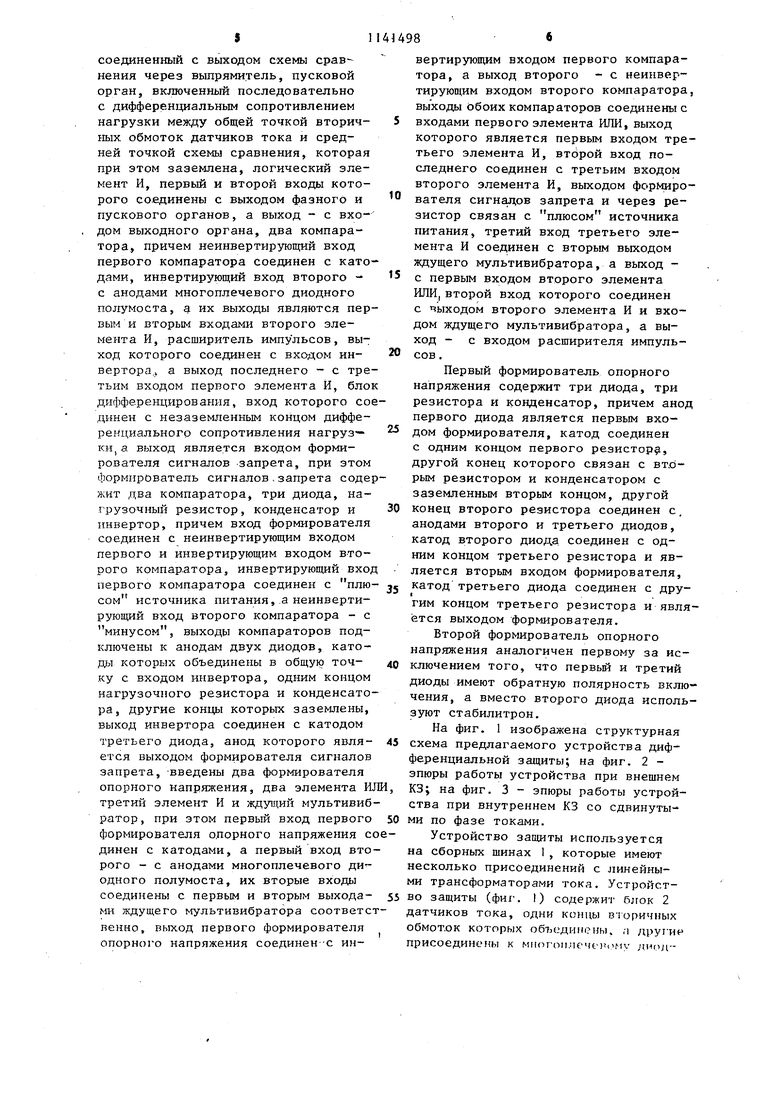

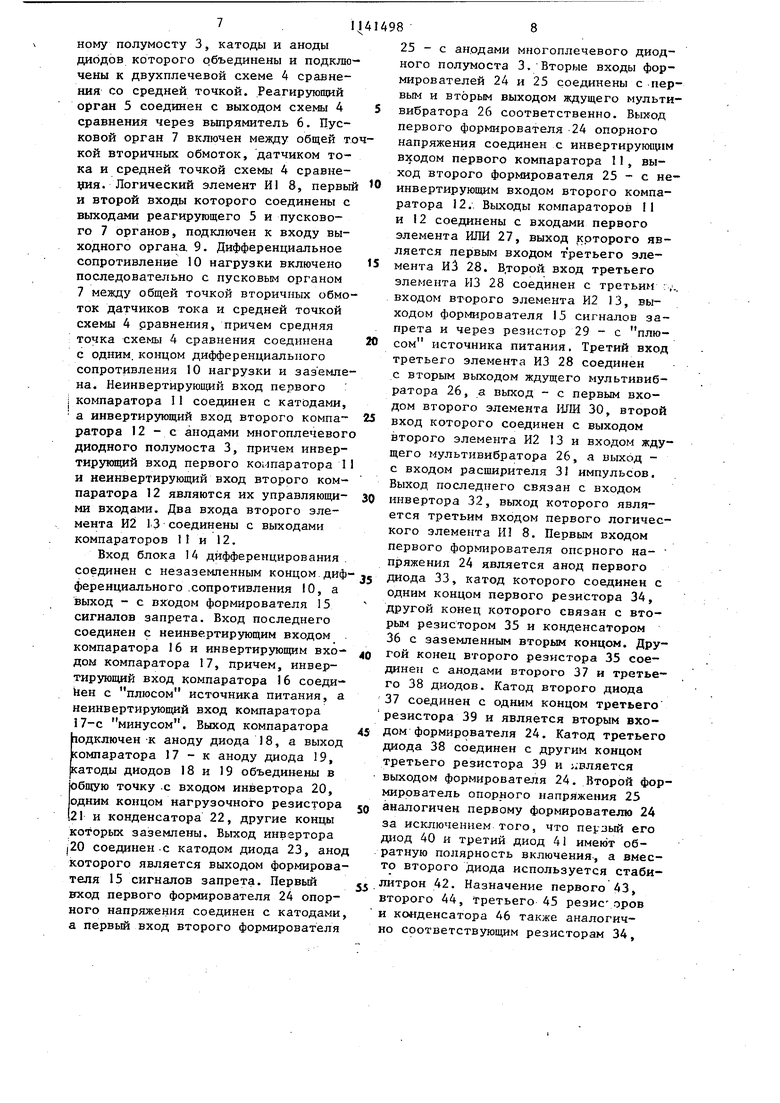

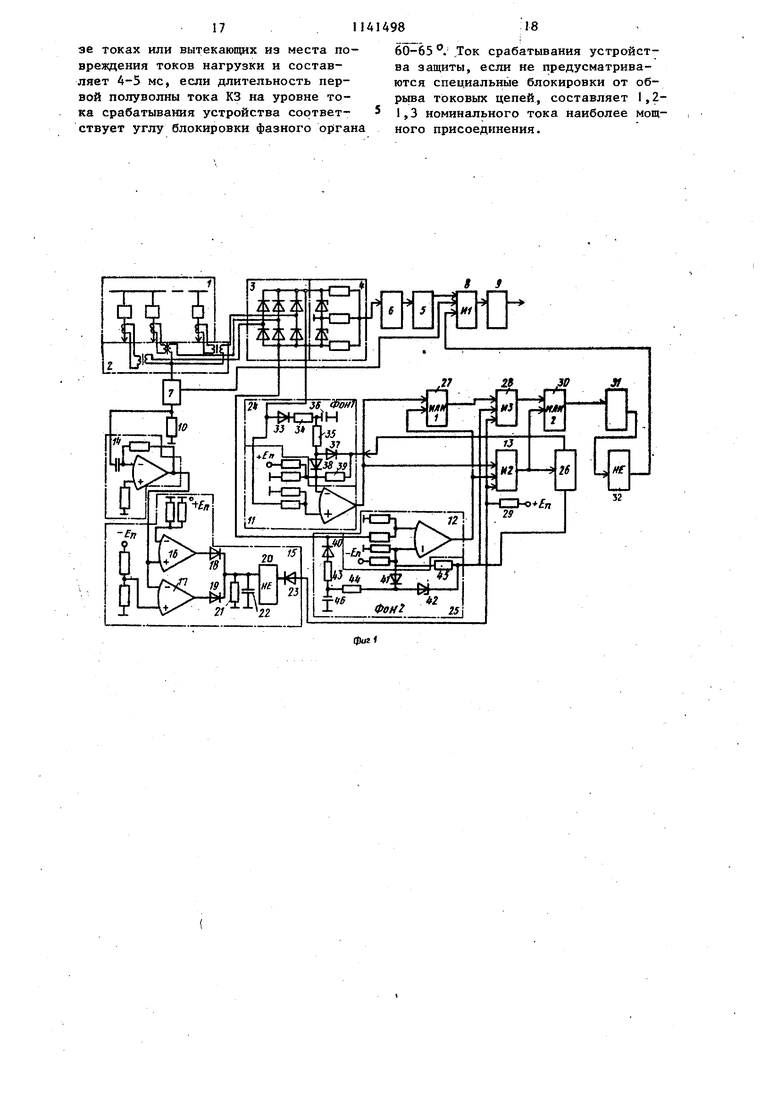

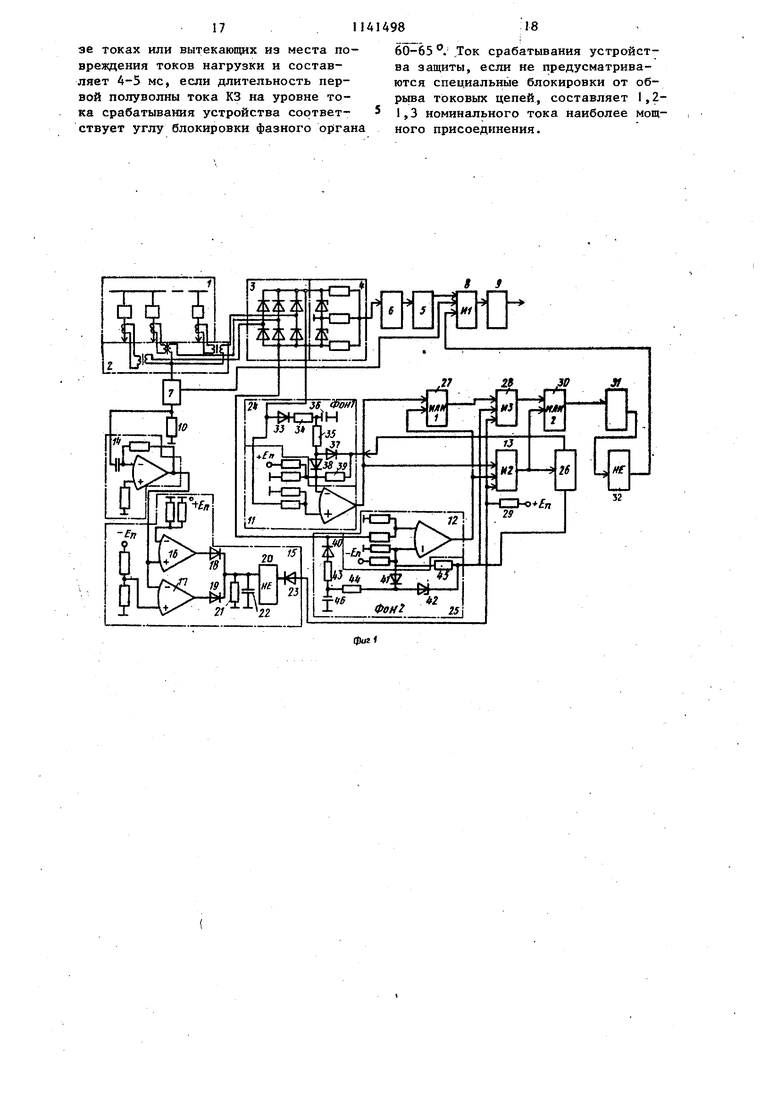

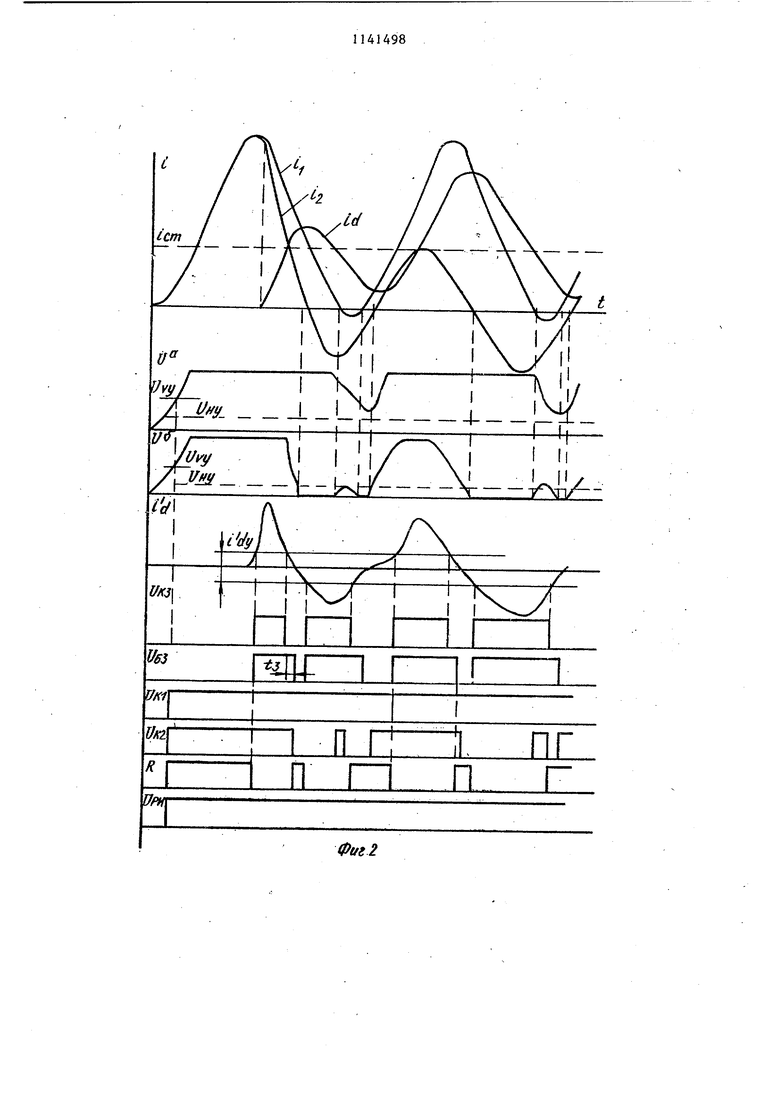

На фиг. 1 изображена структурная схема предлагаемого устройства дифференциальной защиты; на фиг. 2 эпюры работы устройства при внешнем КЗ; на фиг. 3 - эпюры работы устройства при внутреннем КЗ со сдвинутыми по фазе токами.

Устройство защиты используется на сборных шинах 1, которые имеют несколько присоединений с линейными трансформаторами тока. Устройство защиты (фиг. 1) содержит б;гок 2 датчиков тока, одни концы вторичных обмоток которых об7я ди11ены. а друт-ир присоединены к многоп.печеч.му дигдному полумосту 3, катоды и аноды диодов которого объединены и подклю чены к двухплечевой схеме 4 сравнения со средней точкой. Реагирующий орган 5 соединен с выходом схемы 4 сравнения через вьтрямитель 6. Пусковой орган 7 включен между общей т кой вторичных обмоток, датчиком тока и средней точкой схемы 4 сравнеция. Логический элемент И1 8, первы и второй входы которого соединены с выходами реагирующего 5 и пускового 7 органов, подключен к входу выходного органа 9. Дифференциальное сопротивление 10 нагрузки включено последовательно с пусковым органом 7 между общей точкой вторичных обмо ток датчиков тока и средней точкой схемы 4 сравнения, причем средняя : точка схемы 4 сравнения соединена с одним, концом дифференциального сопротивления 10 нагрузки и заземле на. Неинвертирующий вход первого i компаратора I1 соединен с катодами, а инвертирующий вход второго компаратора 12 - с анодами многоплечевог диодного полумоста 3, причем инвертирующий вход первого компаратора I и неинвертирующий вход второго компаратора 12 являются их управляющими входами. Два входа второго элемента И2 13 соединены с выходами компараторов 11 и 12. Вход блока 14 дифференцирования соединен с незаземпенным концом.диф ференциального .сопротивления 10, а выход - с входом формирователя 15 сигналов запрета. Вход последнего соединен с неинвертирующим входом компаратора 16 и инвертирующим входом компаратора 17, причем, инвертирующий вход компаратора 16 соединен с плюсом источника питания, а неинвертирующий вход компаратора 17-с минусом. Выход компаратора юдключен -к аноду диода 18, а выход компаратора 17 - к аноду диода 19, катоды диодов 18 и 19 объединены в общую точку с входом инвертора 20, одним концом нагрузочного резистора 21 и конденсатора 22, другие концы которых заземлены. Выход инвертора j20 соединен .с катодом диода 23, ано которого является выходом формирова теля 15 сигналов запрета. Первый вгход первого формирователя 24 опорного напряжения соединен с катодами а первый вход второго формирователя 25 - с анодами многоплечевого диодного полумоста 3. Вторые входы формирователей 24 и 25 соединены с первым и вторым выходом ждущего мультивибратора 26 соответственно. Выход первого формирователя 24 опорного напряжения соединен с инвартируюпщм входом первого компаратора 11, выход второго формирователя 25 - с неинвертирующим входом второго компаратора 12.. Выходы компараторов I 1 и 12 соединены с входами первого элемента ИЛИ 27, выход которого является первым входом третьего элемента ИЗ 28. В.торой вход третьего элемента ИЗ 28 соединен с третьин ;... входом второго элемента И2 13, выходом формирователя 15 сигналов запрета и через резистор 29 - с плюсом источника питания, Третий вход третьего элемента ИЗ 28 соединен с вторым выходом ждущего мультивибратора 26, а выход - с первым входом второго элемента ШШ 30, второй вход которого соединен с выходом второго элемента И2 13 и входом ждущего мультивибратора 26, а выход с входом расширителя 31 импульсов. Выход, последнего связан с входом инвертора 32, выход которого является третьим входом первого логического элемента И1 8. Первым входом первого фop rapoвaтeля оперного на- пряжения 24 является анод первого даода 33, катод которого соединен с одним концом первого резистора 34, другой конец которого связан с вторым резистором 35 и конденсатором 36с заземленным вторым концом. Другой конец второго резистора 35 соединен с анодами второго 37 и третьего 38 диодов. Катод второго диода 37соединен с одним концом третьего резистора 39 и является вторым входом формирователя 24. Катод третьего диода 38 соединен с другим концом третьего резистора 39 и i;вляeтcя выходом формирователя 24. Второй формирователь опорного напряжения 25 аналогичен первому формирователю 24 за исключением того, что пеузый его диод 40 и третий диод 41 имеют обратную полярность включения, а вместо второго диода используется стабиитрон 42. Назначение первого 43, второго 44, Третьего 45 резисоров конденсатора 46 также аналогичо соответствующим резисторам 34,

35, 39 и конденсатору 36 первого формирователя 24 опорного напряжения .

Устройство работает следующим оразом.

Сигналы от блока 2 датчиков тока разделяются по знаку полупериода с помощью многоплечевого диодного полумоста 3 и поступают на вход схемы 4 сравнения, где ограничиваются по амплитуде до величины напряжения стабилизации стабилитронов. При это по пусковому органу 7 и сопротивлению 10 протекает дифференциальный ток, а с выхода схемы 4 сравнения снимается напряжение, пропорциональное длительности несовпадения огра- HH4eHiftix по амплитуде сигналов с ее плеч токах, более тока стабилизации, при токах же менее стабилизации - пропорциональное дифференциальному току. Защита срабатывает, если срабатывает реагирующий 5. И пусковой 7 органы и на третьем входе логического элемента И1 8 будет при этом сигнал высокого уровня. Время срабатывания защиты состаляет 3-4 мс и определяется углом блокировки реагирующего органа 5.

I

Описанная часть схемы не может

обеспечить необходимый уровень отстроенности от внешних КЗ при указанном быстродействии, поскольку фазовые погрешности ТТ (или да тчика тока) в переходных режимах могут превышать 200, а угол блокировки из условия работоспособности при внутренних КЗ со сдвинутыми по фазе токами целесообразно иметь не более 60-70. Кроме того, уровень тока стабилизации (переход в фазный режим работы) в защите сборных шин, питающих мощную нагрузку с большой додей асинхронных двигателей, может оказаться достаточно высоким по условию отстройки от вытекающего тока нагрузки при внутреннем несимметричном КЗ на землю. Этот уровень може;т оказаться выше минимальных токов КЗ 5 способных вызвать достаточно тяжелый переходный процесс, когда защита работает как дифференциальная. Поэтому, как и в известном устройстве, в заиште предусматривается логическая часть, принцип действия которой основан на следующих свойствах переходного

процесса в ТТ при преимущественно активной нагрузке.

В переходном процессе даже при самых неблагоприятных условиях ТТ входит в насыщение не сразу, а спустя определенное время, в течение которого трансформация тока осуществляется практически без погрешносг ти. Таким образом, при внешнем КЗ .появление тока, небаланса, равного току намагничивания насытившегося ТТ, будет во времени отставать от момента появления напряжения на схеме 4 сравнения. Однако при последующих за первым периодах такой характер переходного процесса возможен лишь при глубоких. насьш ениях ТТ и активной нагрузке, близкой по величине предельной (переходной процесс первого рода). При ЭТОМ ТТ в каждо.й Положительной полуволне (совпадающей по знаку с апериодической слагающей) входит в насыщение, а в от-; рицательной - выходит, и трансформация вновь происходит без погрешности В большинстве случаев нагрузка ТТ и ток КЗ значительно меньше предельных, что при больших постоянных времени первичной сети может также обусловить насыщение ТТ, однако характе этого процесса (назовем его процессом второго рода) будет иным. При этом в периодах, следующих за периодом первоначального насьпцения, ТТ в течение нескольких периодов не выходит из насыщения, мгновенное значение тока намагничивания (ток небаланса) не равно нулю в начале положительных полуволн первичного тока, ток небаланса носит, как правило, однополярный характер. Однако при переходном процессе первого рода в одном плече защиты и переходном процессе второго рода в другом возможен и разнополярный ток небаланса.

Идентификация режима.в периодах, последующих за периодом первоначального насыщения, осложняется в перBjOM роде переходного процесса, вопервых, значительным умёньпгением времени идеальной трансформации вследствие быстрого насыщения ТТ одного плеча защиты и, во-вторых, снижением напряжения на схеме сравнения менее порога запуска логической части. При втором роде переходного процесса, кроме того, в начале полуволн дифференциальный ток не равен нулю. т.е. отсутствует идеальная трансформация даже на ограниченном интер вале времени. Воссталовление бестоковых пауз в устройстве достигается путем дифференцирования тока небаланса. Поставленная цель достигается путем повышения устойчивости идентификации режимов внешних и внутрен них КЗ в переходных процессах. Учитывая свойства переходного пр цесса в ТТ, в первом периоде при внешнем КЗ фиксируют несовпадение производной дифференциальной тока и напряжений на плечах схемы сравнения в интервале времени, когда последние совпадают между собой. Чтобы не было необходимости запоминать этот признак на весь переходный процесс, порог запуска логической части в последующих периодах при внешнем КЗ необходимо снизить. С целью повышения устойчивости идентификации режима внешнего КЗ в периодах, следующих после периода первоначального насьш1ения одного из ТТ, начиная со второго пе:риода и до конца переходного проi цесса фиксируется несовпадение про- :изводной дифференциального тока с первым появившимся из напряжений сх мы сравнения. Кроме того, для повышения устойчивости идентификации ре жимов внешних и внутренних КЗ в nep ходных процессах при защите шин узловых подстанций и ГЭС, порог ее за пуска зависит от амплитудного значения рабочего тока предаварийного режима, так как максимум мгновенного значения тока КЗ отличается от последнего как минимум в 1,5-2 раза и имеет место в первом периоде переходного процесса. Поскольку рабочий ток на шинах,мощных узловых под станций и ГЭС как правило не изменяется скачком в 1,5-2 раза за время одного периода (исключая пуски сверхмощных электродвигателей, при которых, однако, возникают переходные процессы, аналогичные КЗ), запуск логической части схемы в рабочих режимах производиться не будет, если плавно изменяющийся порог запуска по положительным полуволнам напряжения на плечах схемы 4 срав|Нения (и ) и отрицательным (U, ) будет превьшать максимум мгновенного значения предшествующего тока . нагрузки в Kfi l,5-2,0 раза. При внутренних КЗ напряжения на плечах схемы сравнения U и U либо не совпадают, либо производтпя от дифференциального тока i d . совпадает с напряжениями U и U на интервале совпадения последних. В предлагаемом устройстве, как и в известном, при внутреннем КЗ и наличии вытекающего тока нагрузки с взаимным углом, близким к 180 , на пряжения и° и и совпадают, при этом id принимает нулевые значения в интервале этого совпадения, что может быть воспринято устройством как признак внешнего КЗ, если величина вытекающего тока нагрузки превышает уровень запуска логической части. Для устранения возможных действий устройства в таких режимах вводится задержка на возврат измерительного органа, фиксирующего величину lidb Алгоритм работы логической части схемы можно описать следуюпщм образом. 1. По напряжениям плеч схемы сравнения U и U задается пеоеменный пороговый уровень Uyy , плавно отслеживающий амплитудные их значения и с запасом, превьш1ающим их. При быстром (в течение одного периода) возрастании напряжений U и U более, чем в Кр раз по этим напря- , жениям на переменном уровне Uyy и U формируются хотя бы один раз в течение периода логические сигналы и$(и). 2.Из выпрямленных сигналов производной от дифференциального тока на определенном уровне (idy) формируются логические сигналы (id), которые удлиняются на время t. 3.При совпадении логических сигналов и° и .и и отсутствии при этом логического сигнала lid|, удлиненного на t, формируется сигнал Запрет, при этом сигнал Запрет удлиняется примерно на 25 мс и блокирует защиту; запускается элемент памяти, который на время существования переходного процесса снижает уровень формирования логических сигналов до и и .Из входных си1иалов U и U в течение всего переходного процесса (после фиксации внешнего КЗ) форми;i3 . 1 руготся логические сигналы U° и U на более низком уровне, не зависящем от амплитуды входных сигналов. Сигна лы Запрет в последующих после первого периодах формируются при отсутствии логического сигнала lidf: в появления первого из сигналов момент И или Логическая функция Запрет R, соответствующая описанному алгоритму, может быть выражена следующим образом; R-CU AujAlidl D vjC(UvAUvAhdi-D)n A {UHVUH)A|7d|-D jJ, где D - оператор задержки логического сигнала на величину t ; П - оператор памяти. При этом формирователи 24 и 25 опорного напряясения (фиг. 1) реализуют следующие требования: при плавных и незначительных изменениях вход ного напряжения U и U (менее, чем в Кп ра;з) пороговое напряжение ,.., . Uyy(U ) должно с запасом превышать входное, а при быстром (в течение .од ного периода) увеличении входного сигнала в Кр раз к моменту поступле ния максимума при наиболее неблагоI приятных углах включения амплитуда входного сигнала должна достигать величины порогового напряжения (vy); после вьщачи сигнала прет пороговое напряжение должно снизиться до минимального уровня и ну и не зависеть от величины входного сигнала; закон изменения порогового напряжения должен восстанавливаться после истечения вьщержки бремени С,, задаваемой элементом памяти, с учетом возможного возрастания токов нагрузки в послеаварий ном режиме. Компараторы 11 и 12 (фиг. 1) пре назначены для формирования логичеси и и или к;их сигналов зависимости от уровня опорного напряжения. Формирователи опорных напряжений.ФОН 1-24 и ФОН2-25 изменяют уровень опорного Напряжения и.уу в зависимости от интенсивности входных сигналов u(U): если начал ное опорное напряжение } меньше и (и), то ФОН 1-24 и ФОН2-25 стре8мятся увеличить Ц,. до U(U ). Чтобы в рабочем режиме логическая часть не запускалась, на рабочий вход компараторов 11 и 12 подается только часть напряжения U° и U соответственно. При зтом изменение U,g во времени происходит таким образом, что при возрастании амплитуды последующей полуволны U°(U ) по сравнению7С предьщущей менев, чем в Kf, раз, величина превышает и° и uj и (1г) и логические сигналы не формируются. При внешнем КЗ (фиг. 2) компараторы 11 и 12 срабатывают одновременно, поскольку в первом периоде (или части периода) ТТ еще не насыщены и ток в дифференциальной цепи отсутствует. Логические сигналы lidl формируются при помощи дифференциатора- 14 и двух компараторов 16 и 17 на заданном уровне idy. Удлинение и инвертирова ше сигналов Ii d I производится при помощи конденсатора 22 и инвертора 20, На диодах 18 и. 19 собрана схема ИЛИ. Поскольку в начальной части переходного процесса сигналы (i d) отсут.,....,.. ствуют, на всех трех входах элемента И 13 будут потенциалы высокого уровня. с выхода элемента И 13 сигнал подается на вход ждущего мультивибратора 26у выполняющего функции элемента памяти, и через элемент ИЛИ2 30 - на вход расширителя 31 импульсов, где он удлиняется до 25мс, инвертируется (инвертор 33) и в виде непрерывного сигнала низкого уровня поступает на третий вход элемента И 8,блокируя срабатывание защиты. Ждущнй мультивибратор 26формирует импульсы длительностью tn, гарантирующей затухание переходных токов небаланса. При этом с его первого выхода на второй вход первого формирователя 24 опорного напряжения подается логический сигнал низкого уровня, а с второго выхода на второй вход второго формирователя 25 - сигнал высокого уровня, благодаря чему формирователи 24 и 25 снижают уровень опорного напряжения до минимально . необходимого () по условиям устойчивого запуска компараторов 11 и 12 при глубоких насыщениях ТТ. Таким образом., с момента появления первого логического импульса R на выходе элемента И2 13 в течение всего переходного процесса вызывающего насьщение ТТ, формирование логических импульсов по напряжению с плеч схемы 4 сравнения производится на сниженном уровне. Поскольку в конце отрицательной полуволны производная от тока небаланса невелика, логические сигналы 11d| к началу положительной полуволны вто рого и последующих периодов изчеза ют. При этом необходимо, чтобы задержка сигнала | i d| на время t. не приводила бы к осуществованию послед него в .начале следующей положительной полуволны. . При втором роде переходного процесса в ТТ передний фронт вторичного тока насыщенного ТТ отстает от перед него фронта ненасыщенного (до 2,5 мс поэтому момент совпадения напряжения на плечах схемы сравнения в нача ле положительных полуволн после насы щения одного из ТТ практически совпадает с появлением небаланса в дифф ренциальной цепи ((idl). Это привело бы к снятию блокирующих сигналов логической части. Поэтому в последующих полуволнах после определения факта внешнего КЗ в первой полуволне устройство меняет алгоритм работы для формирования импульсов R уже достаточно наличие логических сигналов и или и на выходах компараторов 11 и 12 и соответственно отсутствие (Id) .с выхода формирователя сигнапов запрета 15 (фиг. 2). Указанный алгоритм реализуется при помощи схе-г мы ИЛИ1 27, ИЗ 28 и .:вступает в действие лишь после срабатывания ждущего мультивибратора 26, т.е. после появления логической единицы на третьем входе элемента ИЗ 28. - В режиме внутреннего КЗ с односторонним питанием плечи схемы сравнения током обтекаются поочередно, поэтому совпадения сигналов U и Uy на входах элемента И2 I3 не будет, логическая функция R не сформируется В режиме внутреннего КЗ с двухсто ронним питанием о сдвинутыми по фазе токами (фиг. 3) в течение некоторого времени возможно совпадение сигналов и и и на входах элемента И2 13, однако при этом не равен нулю сигнал U d| и функция R попрежнему равна нулю. При внутреннем КЗ и наличии вытекающего тока нагрузки с взаимным уг118близким к 180°, превышающим уровень формирования сигналов U и будет совпадение сигналов на двух входах элемента И 13 при наличии сигнала |i dI. Однако если взаимный угол близок к 180°, то i3 момент совпадения сигналов U° и U сигнал I i d| может отсутствовать в течение некоторого времени. Для перекрытия последнего введена задержка на возврат lidf на время t, Длительность которой в расчетном случае должна быть достаточной, чтобы на выходе HHBepfopa 20 постоянно был логический нзшь. Таким образом, описанный алгоритм работы защиты обеспечивает высокую устойчивость идентификации внешних . и внутренних КЗ как в первом периоде переходного процесса, так и в каждом последующем, включая периоды максимального намагничивания одного из ТТ, что. обеспечивает высокую отстроенность защиты от внешних КЗ при сохранении высокого быстродействия - при внутренних, в том числе при переходе внешнего КЗ во внутреннее. Использование изменяемого порога запуска логической части устройства в зависимости от тока предшествующего режима, его резкое снижение в последующих после первого периодах переходного процесса при одновременном изменении алгоритма формирования сигналов Запрет обеспечивают достижение поставленной цели. По сравнению с базовым объектом, за который принята начавшая . выпускаться промышленностью дифференциальная зaщIiтa шин с торможением (ДЭШТ), предлагаемое устройство защиты обладает лучшей отстроенностью от внешних КЗ и быстродействием при внутренних КЗ. Устройство обладает высокой отстроенностью при внешних КЗ, сопровождающихся наиболее неблагоприятными переходными процессами в цепях защиты. При этом отстроенность устройства не снижается при использовании его для защиты двойНОИ системы сборных шин, а также сборных шип мощных узловых подстанций или ГЭС, к.-ксималькый сквозной ток которых значительно отличается от номинальных токов ТТ. Быстродействие же защиты не снижается как при наличии апериоднчоскоГ слагающей в токе КЗ, так и сдвинутых по фазе токах или вытекающих из места повреждения токов нагрузки и составляет 4-5 мс, если длительиость первой полуволны тока КЗ на уровне тока срабатывания устройства соответствует углу блокировки фазного органа

60-65 . ,Ток срабатывания устройства защиты, если не предусматриваются специальные блокировки от обрыва токовых цепей, составляет 1,21,3 номинального тока наиболее мощного присоединения.

icm

-- /id

UK3

V63

-ts

VKL

П П

ПГ

г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР | |||

| Устройство для дифференциально-фазной защиты сборных шин | 1977 |

|

SU729718A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1985-02-23—Публикация

1983-12-19—Подача