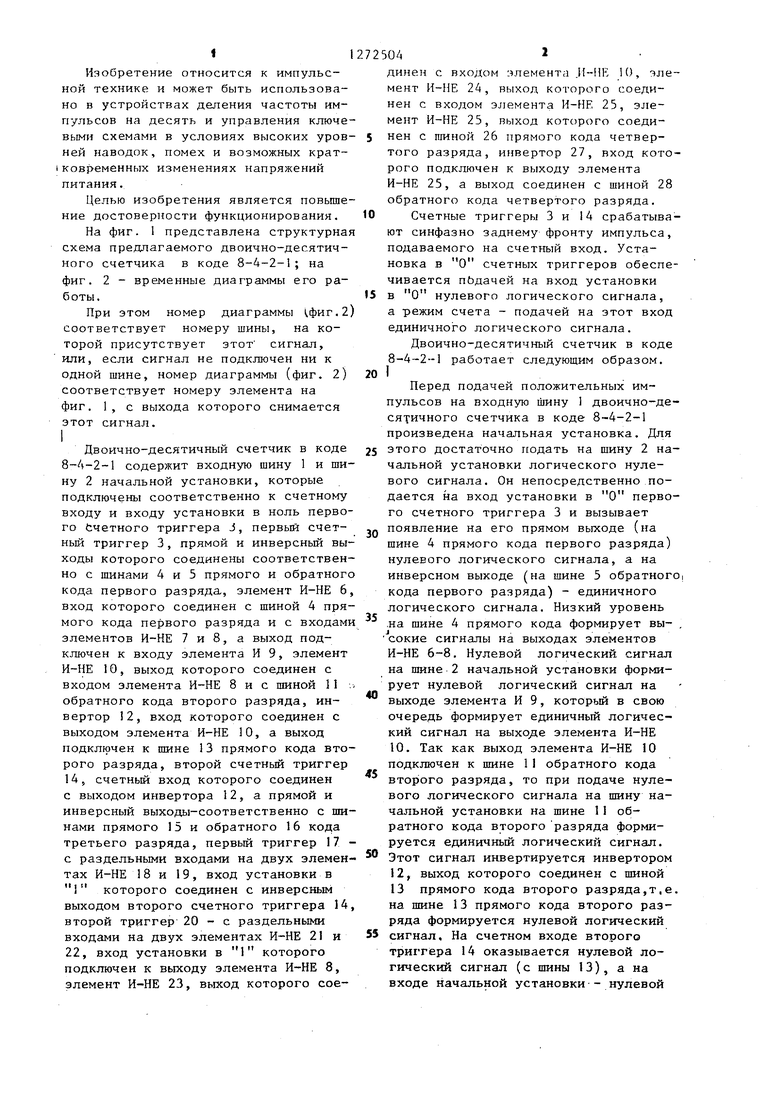

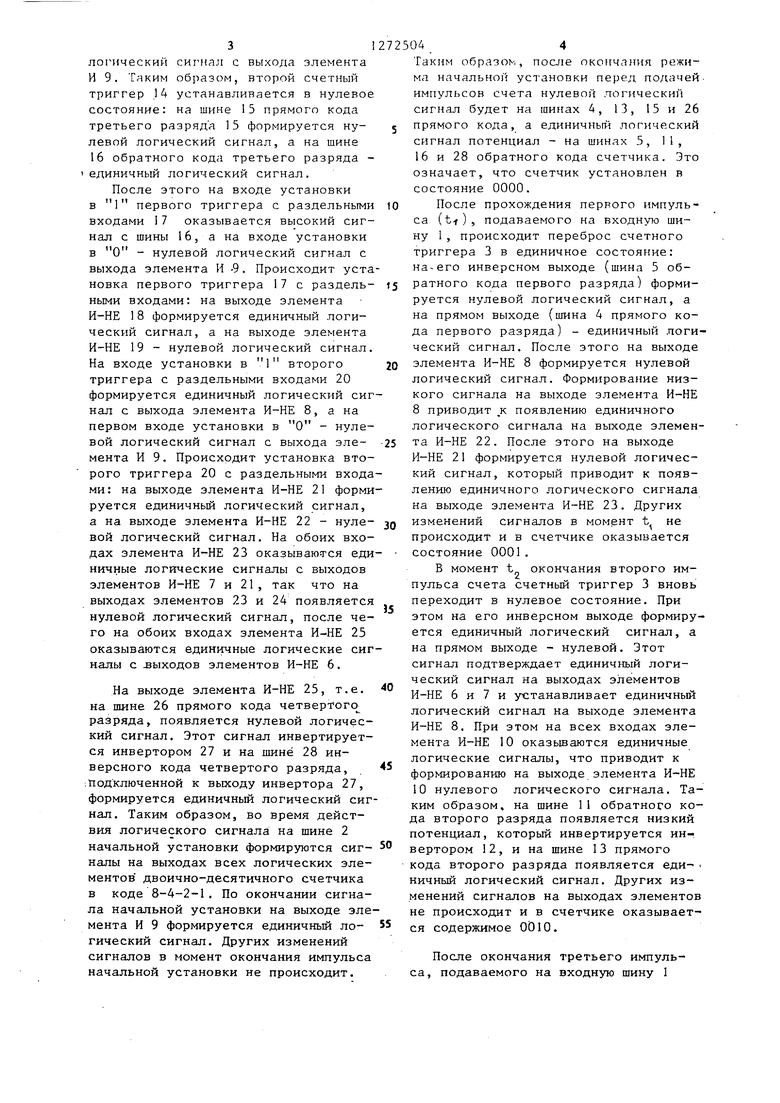

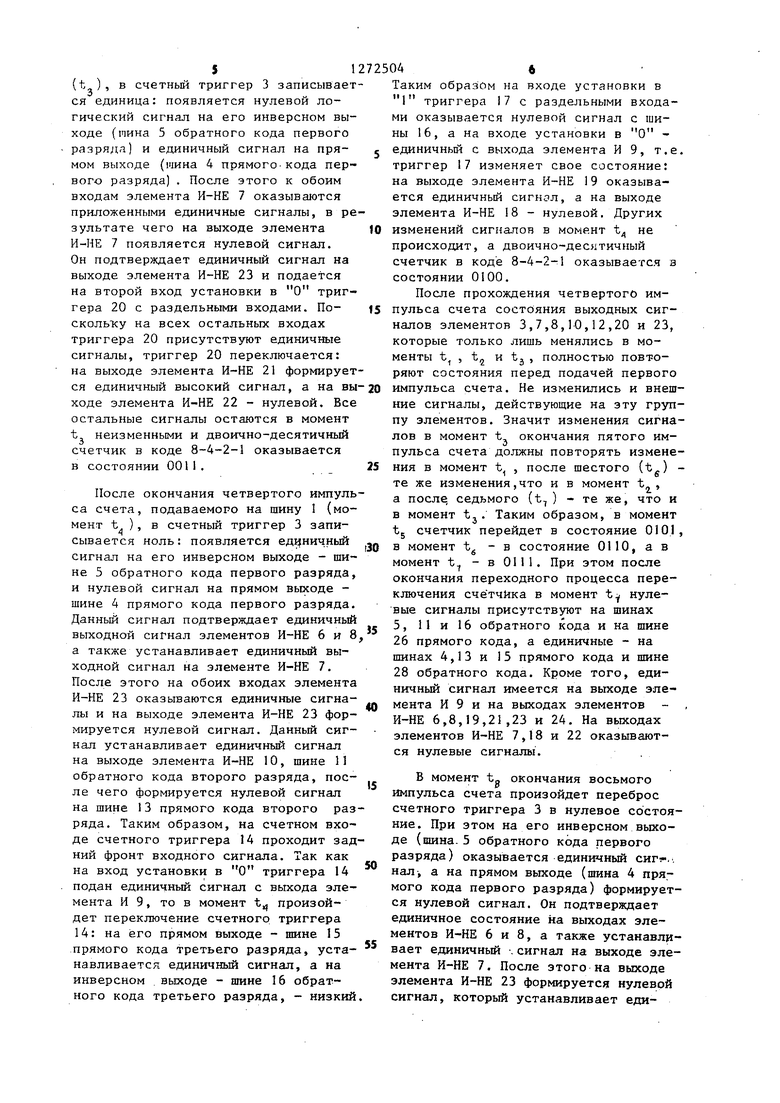

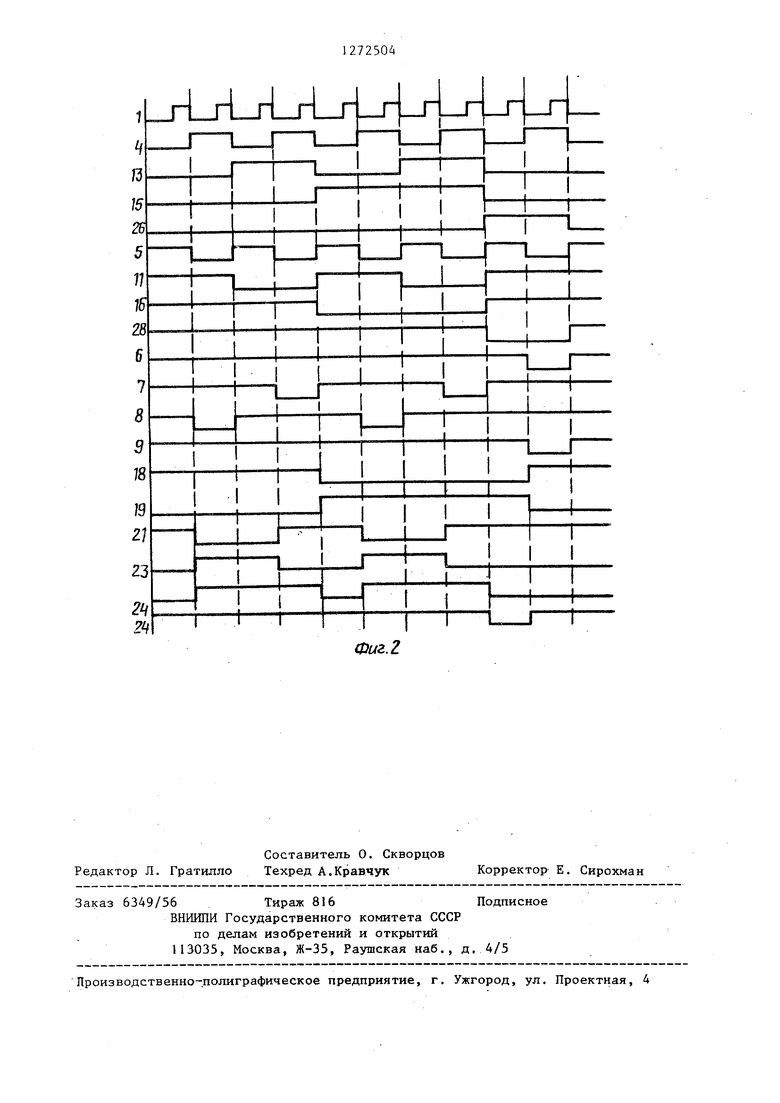

« Изобретение относится к импульсной технике и может быть использовано в устройствах деления частоты импульсов на десять и управления ключе выми схемами в условиях высоких уров ней наводок, помех и возможных крат1ковременных изменениях напряжений питания. Целью изобретения является повыше ние достоверности функционирования. На фиг. 1 представлена структурна схема предлагаемого двоично-десятичного счетчика в коде 8-4-2-1; на фиг. 2 - временные диаграммы его работы. При этом номер диаграммы фиг.2 соответствует номеру шины, на которой присутствует этот сигнал, или, если сигнал не подключен ни к одной шине, номер диаграммы (фиг. 2) соответствует номеру элемента на фиг. 1, с выхода которого снимается этот сигнал. Двоично-десятичный счетчик в коде 8-4-2-1 содержит входную шину 1 и ши ну 2 начальной установки, которые подключены соответственно к счетному входу и входу установки в ноль перво го Счетного триггера J, первый счетный триггер 3, прямой и инверсный вы ходы которого соединены соответствен но с шинами 4 и 5 прямого и обратног кода первого разряда, элемент И-НЕ 6 вход которого соединен с шиной 4 пря мого кода первого разряда и с входам элементов И-НЕ 7 и 8, а выход подключен к входу элемента И 9, элемент И-НЕ 10, выход которого соединен с входом элемента И-НЕ Вис шиной 11 обратного кода второго разряда, инвертор 12, вход которого соединен с выходом элемента И-НЕ 10, а выход подключен к шине 13 прямого кода вто рого разряда, второй счетньй триггер 14, счетный вход которого соединен с выходом инвертора 12, а прямой и инверсный выходы-соответственно с ши нами прямого 15 и обратного 16 кода третьего разряда, первый триггер 17 с раздельными входами на двух элемен тах И-НЕ 18 и 19, вход установки в 1 которого соединен с инверсным выходом второго счетного триггера 14 второй триггер 20 - с раздельными входами на двух элементах И-НЕ 21 и 22, вход установки в 1 которого подключен к выходу элемента И-НЕ 8, элемент И-НЕ 23, выход которого сое042динен с входом элемента .П-ПЕ И), элемент И-НЕ 24, выход которого соединен с входом элемента И-НЕ 25, элемент И-НЕ 25, выход которого соединен с птной 26 прямого кода четвертого разряда, инвертор 27, вход которого подключен к выходу элемента И-НЕ 25, а выход соединен с шиной 28 обратного кода четвертого разряда. Счетные триггеры 3 и 14 срабатывают синфазно заднему фронту импульса, подаваемого на счетный вход. Установка в О счетных триггеров обеспечивается пЬдачей на вход установки в О нулевого логического сигнала, а режим счета - подачей на этот вход единичного логического сигнала. Двоично-десятичный счетчик в коде 8-4-2--1 работает следующим образом. Перед подачей положительных импульсов на входную шину 1 двоично-десятичного счетчика в коде 8-4-2-1 произведена начальная установка. Для этого достаточно подать на шину 2 начальной установки логического нулевого сигнала. Он непосредственно подается на вход установки в О первого счетного триггера 3 и вызывает появление на его прямом выходе (на шине 4 прямого кода первого разряда) нулевого логического сигнала, а на инверсном выходе (на шине 5 обратного: кода первого разряда) - единичного логического сигнала. Низкий уровень .на шине 4 прямого кода формирует высокие сигналы на выходах элементов И-НЕ 6-8. Нулевой логический сигнал на шине 2 начальной установки формирует нулевой логический сигнал на выходе элемента И 9, которьм в свою очередь формирует единичный логический сигнал на выходе элемента И-НЕ 10. Так как выход элемента И-НЕ 10 подключен к шине 11 обратного кода второго разряда, то при подаче нулевого логического сигнала на шину начальной установки на шине 11 обратного кода второго разряда формируется единичный логический сигнал. Этот сигнал инвертируется инвертором 12, выход которого соединен с шиной 13 прямого кода второго разряда,т.е. на шине 13 прямого кода второго разряда формируется нулевой логический сигнал. На счетном входе второго триггера 14 оказывается нулевой логический сигнал (с шины 13), а на входе начальной установки - нулевой логический сиглал с выхода элемента И 9. Таким образом, второй счетный триггер .14 устанавливается в нулевое состояние: на шине 15 прямого кода третьего разряда 15 формируется нулевой логический сигнал, а на шине 16 обратного кода третьего разряда единичный логический сигнал. После этого на входе установки в 1 первого триггера с раздельными входами 17 оказывается высокий сигнал с шины 16, а на входе установки в О - нулевой логический сигнал с выхода элемента И -9. Происходит уста новка первого триггера 17 с раздельными входами: на выходе элемента И-НЕ 18 формируется единичный логический сигнал, а на выходе элемента И-НЕ 19 - нулевой логический сигнал На входе установки в 1 второго триггера с раздельными входами 20 формируется единичный логический сиг нал с выхода элемента И-НЕ 8, а на первом входе установки в О - нулевой логический сигнал с выхода элемента И 9. Происходит установка второго триггера 20 с раздельными входа ми: на выходе элемента И-НЕ 21 форми руется единичньш логический сигнал, а на выходе элемента И-НЕ 22 - нулевой логический сигнал. На обоих входах элемента И-НЕ 23 оказываются еди ничные логические сигналы с выходов элементов И-НЕ 7 и 21, так что на выходах элементов 23 и 24 появляется нулевой логический сигнал, после чего на обоих входах элемента И-НЕ 25 оказываются единичные логические сиг налы с -ВЫХОДОВ элементов И-НЕ 6. На выходе элемента И-НЕ 25, т.е. на шине 26 прямого кода четвертого разряда, появляется нулевой логический сигнал. Этот сигнал инвертируется инвертором 27 и на шине 28 инверсного кода четвертого разряда, ;1подключенной к выходу инвертора 27, формируется единичный логический сиг нал. Таким образом, во время действия логического сигнала на шине 2 начальной установки формируются сигналы на выходах всех логических элементов двоично-десятичного счетчика в коде 8-4-2-1. По окончании сигнала начальной установки на выходе эле мента И 9 формируется единичный логический сигнал. Других изменений сигналов в момент окончания импульса начальной установки не происходит. 044 Таким образоь, после окончания режима начальной установки перед подачейимпульсов счета нулевой логический сигнал будет на шинах 4, 13, 15 и 26 прямого кода, а единичньй логический сигнал потенциал - на шинах 5, 11, 16 и 28 обратного кода счетчика. Это означает, что счетчик установлен в состояние 0000. После прохождения первого импульса (t.f), подаваемого на входную шину 1, происходит переброс счетного триггера 3 в единичное состояние: на-его инверср ом выходе (шина 5 обратного кода первого разряда) формируется нулевой логический сигнал, а на прямом выходе (шина 4 прямого кода первого разряда) - единичный логический сигнал. После этого на выходе элемента И-НЕ 8 формируется нулевой логический сигнал. Формирование низкого сигнала на выходе элемента И-НЕ 8 приводит к появлению единичного логического сигнала на выходе элемента И-НЕ 22. После этого на выходе И-НЕ 21 формируется нулевой логический сигнал, который приводит к появлению единичного логического сигнала на выходе элемента И-НЕ 23. Других изменений сигналов в момент t не происходит и в счетчике оказывается состояние 0001. В момент t окончания второго импульса счета счетный триггер 3 вновь переходит в нулевое состояние. При этом на его инверсном выходе формируется единичный логический сигнал, а на прямом выходе - нулевой. Этот сигнал подтверждает единичный логический сигнал на выходах элементов И-НЕ 6 и 7 и устанавливает единичный логический сигнал на выходе элемента И-НЕ 8. При этом на всех входах элемента И-НЕ 10 оказьшаются единичные логические сигналы, что приводит к формированию на выходе элемента И-НЕ 10 нулевого логического сигнала. Таким образом, на шине 11 обратного кода второго разряда появляется низкий потенциал, который инвертируется инвертором 12, и на шине 13 прямого кода второго разряда появляется еди- ничный логический сигнал. Других изменений сигналов на выходах элементов не происходит и в счетчике оказывается содержимое ODlO. После окончания третьего импульса, подаваемого на входную шину 1 (t ), в счетный триггер 3 записывает ся единица: появляется нулевой логический сигнал на его инверсном выходе (шина 5 обратного кода первого разряда) и единичный сигнал на прямам выходе (шина 4 прямого-кода первого разряда). После этого к обоим входам элемента И-НЕ 7 оказываются приложенными единичные сигналы, в ре зультате чего на выходе элемента И-ИЕ 7 появляется нулевой сигнал. Он подтверждает единичный сигнал на выходе элемента И-НЕ 23 и подается на второй вход установки в О триггера 20 с раздельными входами. Поскольтсу на всех остальных входах триггера 20 присутствуют единичные сигналы, триггер 20 переключается: на выходе элемента И-НЕ 21 формирует ся единичный высокий сигнал, а на вы ходе элемента И-НЕ 22 - нулевой. Все остальные сигналы остаются в момент t неизменными и двоично-десятичный счетчик в коде 8-4-2-} оказывается в состоянии 0011. После окончания четвертого импуль са счета, подаваемого на шину 1 (момент t ), в счетный триггер 3 записывается ноль: появляется ед ничный сигнал на его инверсном выходе - шине 5 обратного кода первого разряда, и нулевой сигнал на прямом выходе шине 4 прямого кода первого разряда. Данный сигнал подтверждает единичный выходной сигнал элементов И-НЕ 6 и 8 а также устанавливает единичный выходной сигнал на элементе И-НЕ 7. После этого на обоих входах элемента И-НЕ 23 оказываются единичные сигналы и на выходе элемента И-НЕ 23 формируется нулевой сигнал. Данный сигнал устанавливает единичный сигнал на выходе элемента И-НЕ 10, шине 11 обратного кода второго разряда, после чего формируется нулевой сигнал на шине 13 прямого кода второго раз ряда. Таким образом, на счетном входе счетного триггера 14 проходит зад ний фронт входного сигнала. Так как на вход установки в О триггера 14 подан единичный сигнал с выхода элемента И 9, то в момент t, произойдет переключение счетного триггера 14: на его прямом выходе - пшне I5 прямого кода третьего разряда, устанавливается единичный сигнал, а на инверсном выходе - шине I6 обратного кода третьего разряда, - низкий Таким образом на входе установки в 1 триггера 17 с раздельными входами оказывается нулевой сигнал с шины 16, а на входе установки в О единичньш с выхода элемента И 9, т.е. триггер 17 изменяет свое состояние: на выходе элемента И-НЕ 19 оказывается единичный сигнал, а на выходе элемента И-НЕ 18 - нулевой. Других изменений сигналов в момент t, не происходит, а двоично-десятичный счетчик в коде 8-4-2-1 оказывается в состоянии 0100. После прохождения четвертого импульса счета состсряния выходных сигналов элементов 3 , 7,8,1-0,1 2 ,20 и 23, которые только лишь менялись в моменты t , t и tj , полностью повторяют состояния перед подачей первого импульса счета. Не изменились и внешние сигналы, действующие на эту группу элементов. Значит изменения сигналов в момент t окончания пятого импульса счета должны повторять изменения в момент t , после шестого (t,) те же изменения,что и в момент t-, а после, седьмого (t, ) - те же, что и в момент t,. Таким образом, в момент tg счетчик перейдет в состояние 0101, в момент tg - в состояние 0110, а в момент t - в 0111. При этом после окончания переходного процесса переключения счётчика в момент ty нулевые сигналы присутствуют на шинах 5, 11 и 16 обратного кода и на шине 26 прямого кода, а единичные - на шинах 4,13 и 15 прямого кода и шине 28 обратного кода. Кроме того, единичный сигнал имеется на выходе элемента И 9 и на выходах элементов И-НЕ 6,8,19,21,23 и 24. На выходах элементов И-НЕ 7,18 и 22 оказываются нулевые сигналы. В момент to окончания восьмого р импульса счета произойдет переброс счетного триггера 3 в нулевое состояние. При этом на его инверсном выходе (шина. 5 обратного кода первого разряда) оказывается единичный сигт-.. нал, а на прямом выходе (шина 4 прямого кода первого разряда) формируется нулевой сигнал. Он подтверждает единичное состояние на выходах элементов И-НЕ 6 и 8, а также устанавливает единичный .сигнал на выходе элемента И-НЕ 7. После этого на выходе элемента И-НЕ 23 формируется нулевой сигнал, который устанавливает единичныи сигиал на выходе элемента И-НЕ 10 (шина И обратного кода втоpoi o разряда). Этот сигнал инвертируется в инверторе 12. Таким образом на счетном входе триггера 14 проходит задний фронт сигнала счета, в то время как на входе начальной установки сохраняется неизменно единичный сигнал с выхода элемента И 9 что вызывает переброс триггера 14: на шине 15 прямого кода третьего раз ряда появляется нулевой сигнал, а на шине 16 обратного кода третьего разряда формируется единичный сигнал. После этого на обоих входах элемента И-НЕ 24 оказываются единичные сигналы, в результате чего на выходе элемента 24 формируется нулевой сигнал Последний устанавливает единичный сигнал на выходе элемента И-НЕ 25 и на шине 26 прямого кода четвертог разряда, после чего возникает нулев сигнал на выходе инвертора 27 и на шине 28 обратного кода четвертого разряда. Других изменений сигналов на выходах логических элементов в момент tg нет и в двоично-десятичном счетчике в коде 8-4-2-1 формиру ется код 1000. После окончания девятого импульса (момент tg) происходит срабатыва ние счетного триггера 3: на шине 5 обратного кода первого разряда появляется нулевой сигнал, а на шине 4 прямого кода первого разряда единичный. После этого на обоих вхо дах элемента И-НЕ 6 оказываются еди ничные сигналы. В результате на выходе элемента И-НЕ 6 формируется ну левой сигнал. Он подтверждает единичный сигнал на выходе элемента И-НЕ 2 и формирует нулевой сигнал н выходе элемента И 8, В свою очередь нулевой сигнал на выходе элемента И 9 подтверждает единичные сигналы навыходах элементов И-НЕ 21 и 10, а также, попадая на вход начальной установки счетного триггера 14, подтверждает его нулевое состояние. Таким образом, на входе установки в 1 триггера 17с раздельными входами оказывается единичный сигнал (с инверсного выхода триггера 14), а на выходе установки в О - нулевой сигнал (с выхода элемента И 9). Это приводит к перебросу триггера 17: на выходе элемента И-НЕ 18 оказывается единичный сигнал, а на выходе 048 элемента И-НЕ 19 - нулевой. Нулевой CHrHajT на выходе И-НЕ 19 формирует единичньм сигнал на выходе элемента И-НЕ 24. Других изменений сигналов на выходах логических элементов в момент tg не происходит и двоично-десятичный счетчик оказывается в состоянии 1 001 . По окончании десятого импульса счета (момент t ) происходит срабатывание счетного триггера 3. При этом на его инверсном выходе (шина 5 обратного кода первого разряда) оказывается единичный сигнал, а на прямом выходе (шина 4 прямого кода первого разряда) формируется нулевой сигнал. Он подтверждает единичный сигнал на выходах элементов И-НЕ 7 и 8, а также формирует единичный сигнал на выходе элемента И-НЕ 7. Поскольку на шине 2 начальной установки присутст- . вуют единичный сигнал, на выходе И 9 появляется .единичный сигнал. После формирования единичного сигнала на выходе элемента И-НЕ 6 на обоих входах элемента И-НЕ 26 оказываются единичные сигналы, что приводит к формированию на выходе этого элемента и . на шине 26 прямого кода четвертого разряда нулевого сигнала. Сигнал на шине 26 инвертируется инвертором 27 и на шине 28 обратного кода четвертого разряда появляется единичный сигнал. Других изменений сигналов в момент не происходит и двоично-десятичньй счетчик в коде 8-4-2-1 оказывается в состоянии 0000. При этом все выходные сигналы элементов двоично-десятичного счетчика повторяют соответствующие сигналы после окончания начальной установки перед подачей сигналов счета. Таким образом, далее работа двоично-десятичного счетчика в коде 8-4-2-1 повторяет рассмотренную. Двоично-десятичный счетчик в коде 8-4-2-1 последовательно переходит в состояния от 0000 до 1001 и далее опять в состояние 0000. Кроме этих десяти coctoяний схемная реализация счетчика не допускает никаких других состояний. Таких запрещенных состояний имеется шесть: 1010, 1011, 1100, 110, 1110 и 1111. Исключение запрещенных состояний 1100 и 1110 происходит следующим образом. Если в первом триггере 3 f yлeвoe состояние, то на выходе эле91мента И-НЕ 6 сф.)рм1 рован единичный сигнал. Если в триггере 14 - единичное содержимое, то нулевой сигнал на его инверсном выходе приводит к появлению единичного сигнала на выходе элемента И-НЕ 24. То есть, на обоих входах элемента И-НЕ 25 присутствуют единичные сигналы, что приводит к появлению на шине 26 прямого кода четвертого разряда нулевого сигнала, а на шине 28 обратного кода четвертого разряда - единичного сигнала. Таким образом, если в первом разряде счетчика присутствует нулевой сигнал, а в третьем - единичный, то в четвертом разряде может быть только нулевое состояние. Это исключает появление запрещенных состояний 1100 и . Исключение запрещенных состояний 1101, lOii и llil происходит следующим образом. Если в первом и четвертом разряда Счетчика единичное состояние - единичные сигналы на шинах 4 и 26 и нулевые на шинах 5 и 27, то на выходах элементов И-НЕ 8 и 21 - единичные сигналы. Таким образом, на обоих вхо дах элементов И-НЕ 6 и 22 присутствуют единичные сигналы. Нулевой сигнал на выходе элемента И-НЕ 6 подтверждает единичный сигнал на выходе элемента И-НЕ 25 и формирует ну левой сигнал на выходе элемента И 9. Этот сигнал приводит к формированию единичных сигналов на выходах элемен тов И-НЕ 19 и 10.Таким образом, на ши не 11 обратного кода второго разряда присутствует единичный сигнал, которьй, инвертируясь инвертором 12, при водит к появлению нулевого сигнала на шине 13 прямого кода второго разряда . Нулевой сигнал на шине 13 формирует единичньй сигнал на выходе элемента И-НЕ 7 и попадает на счетны вход .счетного триггера 14, на входе начальной установки которого присутствует нулевой сигнал с выхода элемента И 9. В счетном триггер 14 нуле вое содержимое: на шине 15 прямого кода третьего разряда присутствует . нулевой сигнал, а на шине 16 обратно го, кода третьего разряда - единичный сигнал. Таким образом, на обоих входах элемента И-НЕ 19 оказались единичные сигналы, что вызывает формиро вание на выходе элемента И-НЕ 19. нулевого сигнала, который формирует 04 единичньй сигнал на выходе элемента И-НЕ 24. Таким образом, предположение о том, что в первом и четвертом разрядах счетчика присутствует единичное состояние, однозначно определяет состояние всех логических элементов счетчика - состояние 1001, запрещенных состояний 1101, 1011 и 1111 возникнуть не может. Исключение запрещенного состояния 1010 происходит следующим образом. Пусть в первом разряде заменен нулевой сигнал информации, а в четвертом разряде - единичный. Это означает наличие высоких сигналов на шине 5 обратного кода первого разряда и шине 26 прямого кода четвертого разряда, в то время как на шине 4 прямого кода первого разряда и шине 28 обратного кода четвертого разряда присутствуют сигналы логического ну- . ля. Сигнал логического нуля с шины 4 устанавливает в единичное состояние сигнапы на выходах элементов И-НЕ 6-8. Поскольку на шине 2 начальной установки существует единичный сигнал, на обоих входах элемента И 9 оказываются единичные сигналы, что вызывает формирование на выходе элемента И 9 единичного сигнала. Нулевой сигнал на шине 28 попадает на вход установки в О триггера 20, на входе установки которого присутствует единичный сигнал с выхода элемента И-НЕ 8. Таким образом, на выходе элемента И-НЕ 21 присутствует единичный сигнал, а на выходе элемента И-НЕ 22 - нулевой. Единичные сигналы на.выходах элементов И-НЕ 21 и 7 формируют нулевой сигнал на выходе элемента И-НЕ 23. Нулевой сигнал на выходе элемента И-НЕ 23 устанавливает единичный сигнал rta выходе элемента И-НЕ 10 и на шине 11 обратного кода второго разряда, который после инвертирования в инверторе 12 вызывает появление нулевого сигнала на шина 13 прямого кода второго разряда. При нуле в первом разряде и единице в четвертом во втором разряде неизбежно оказывается логический ноль,, что исключает появление запрещенного состоянии счетчика 1 01 О и подтверждает исключение запрещенного состояния 1110. Таким образом, в двоично-десятичном счетчике в коде 8-4-2-1 исключается возможность появления любого запрещенного состояния.

Формула изобретения

Двоично-десятичный счетчик в коде 8-4-2-1, содержащий два счетных триггера, триггер с раздельными входами (на двух элемента И-НЕ), два инвертора, два элемента И-НЕ и элемент И, счетньш вход первого счетного триггера соединен с входной шиной, прямой и инверсный выходы - с шинами прямого и обратного кода первого разряда, а вход установки в О - с шиной начальной установки и с первым входом-элемента И, выход которого подключен к входам установки в О триггера с раздельными входами и второго счетного триггера, а второй вход - к первому входу первог элемента И-НЕ, выход которого непосредственно соединен с шиной прямого кода четвёртого разряда и через первый инвертор - с шиной обратного кода четвертого разряда, а второй вход - с выходом второго элемента И-НЕ, первыр вход которого подключен к единичному выходу триггера с раздельными входами, вход установки в 1 которого соединен с вторым входо второго элемента И-НЕ, с шиной обратного кода третьего разряда и с инверсным выходом второго счетного триггера, прямой выход которого подключен к mkHe прямого кода третьего .разряда, а счетный вход - к шине прямого кода второго разряда и к выходу второго инвертора, вход которого соединен с шиной обратного кода второго разряда, отличающийся

тем, что, с целью повьппения достоверности функционирования, в него введены второй триггер с раздельными входами (на двух элементах И-НЕ), а также третий, четвертьш, пятый, шестой и седьмой элементы И-НЕ, причем выход третьего элемента И-НЕ подключен к первому входу первого элемента И-НЕ, выход которого соединен с первым входом третьего элемента И-НЕ, второй вход которого подключен к шине прямого кода первого разряда, к первому входу четвертого элемента И-НЕ и к первому входу пятого элемента И-НЕ, выход которого соединен с входом установки в I второго триггера с раздельными входами и с первым входом шестого элемента И-НЕ, выход которого подключен к входу второго инвертора и к второму входу пятого элемента И-НЕ, а второй вход шестого элемента И-НЕ соединен с первым входом установки в О второго триггера с раздельными входами и к входу установки в О второго счетного триггера, счетньй вход которого соединен с вторым входом четвертого элемента И-НЕ, выход которого подключен к первому входу седьмого элемента И-НЕ и к второму входу установки в О второго триггера с раздельными входами, третий вход установки в О которого соединен с третьим входом пятого элемента И-НЕ и с выходом первого инвертора, а нулевой выход - с вторым входом седьмого элемента И-НЕ, выход которого подключен к третьему входу шестого элемента И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоично-десятичный счетчик в коде 8-4-2-1 | 1986 |

|

SU1415439A1 |

| Двоично-десятичный счетчик в коде 8-4-2-1 | 1987 |

|

SU1462474A1 |

| Двоично-десятичный счетчик вКОдЕ 8-4-2-1 | 1979 |

|

SU849498A1 |

| Двоично-десятичный счетчик | 1977 |

|

SU743206A1 |

| Устройство для кодирования | 1985 |

|

SU1287294A1 |

| ОХРАННОЕ КОДОВОЕ УСТРОЙСТВО | 1990 |

|

SU1834548A1 |

| СПОСОБ И УСТРОЙСТВО СЧЕТА ИМПУЛЬСОВ | 2015 |

|

RU2604334C2 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

| Преобразователь код-частота | 1980 |

|

SU869059A1 |

| Перестраиваемый делитель частоты следования импульсов | 1984 |

|

SU1213542A1 |

| Двоично-десятичный счетчик | 1973 |

|

SU477544A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Двоично-десятичный счетчик вКОдЕ 8-4-2-1 | 1979 |

|

SU849498A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-11-23—Публикация

1985-05-31—Подача