(k) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНОДЕСЯТИЧНЫЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1983 |

|

SU1149243A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| Преобразователь двоичных кодов в двоично-десятичные | 1984 |

|

SU1200428A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691843A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

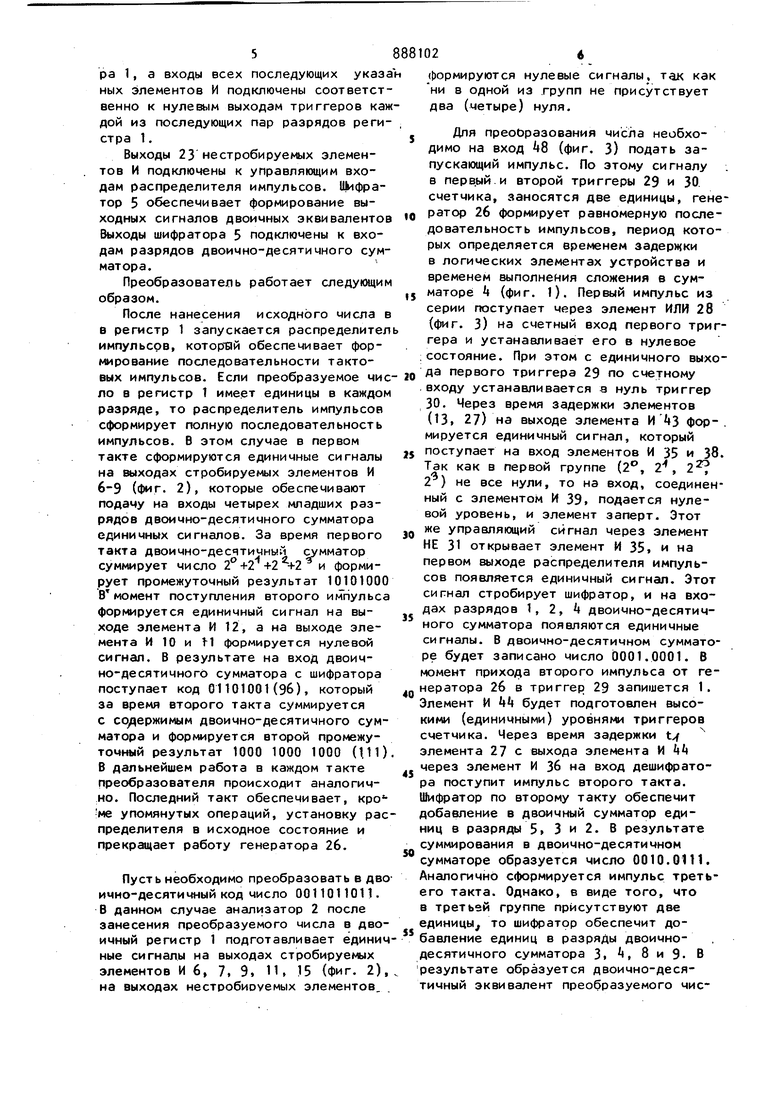

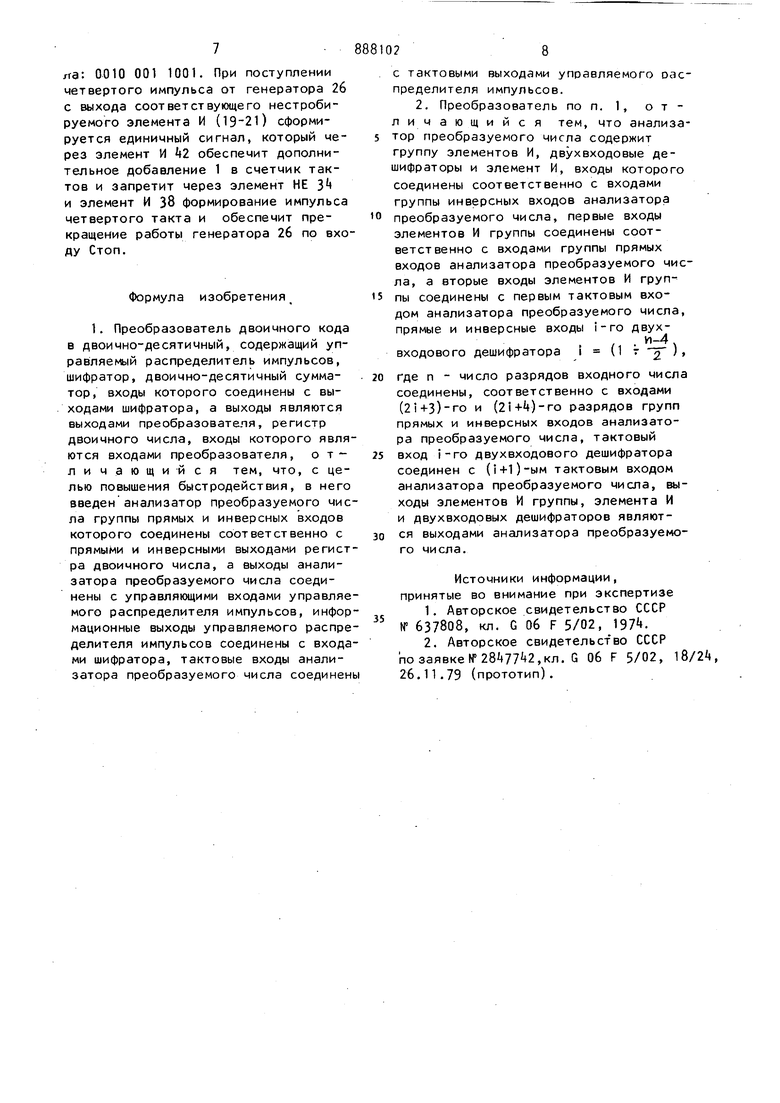

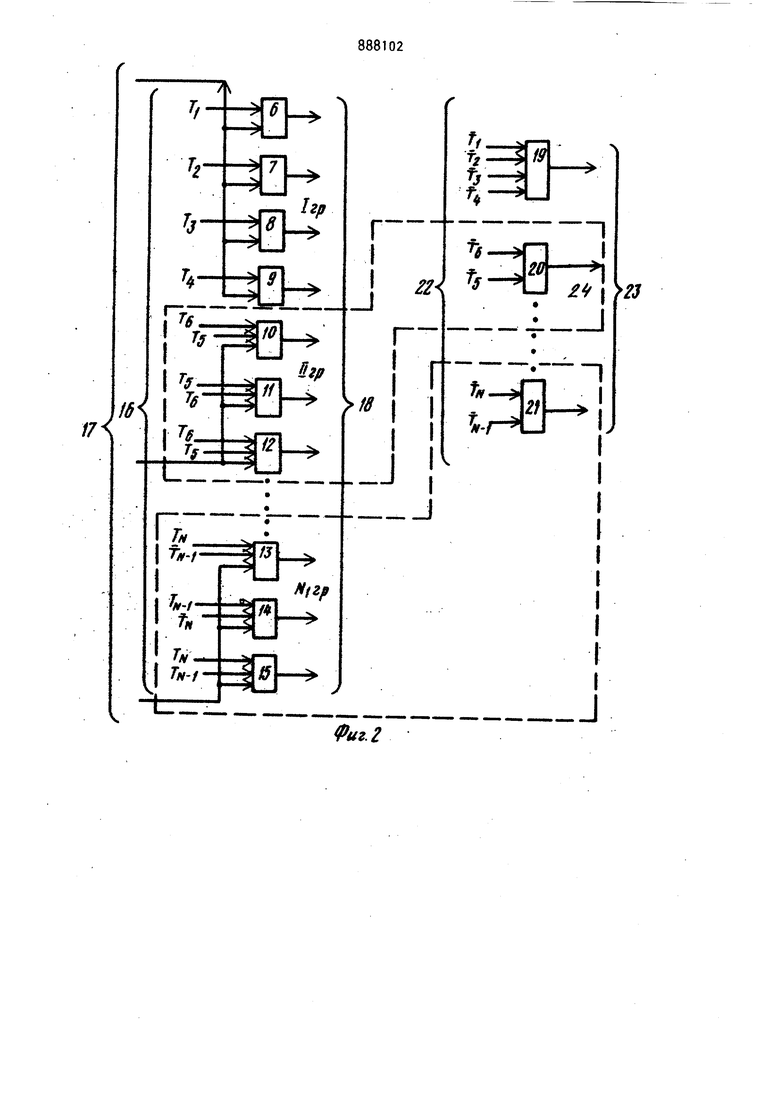

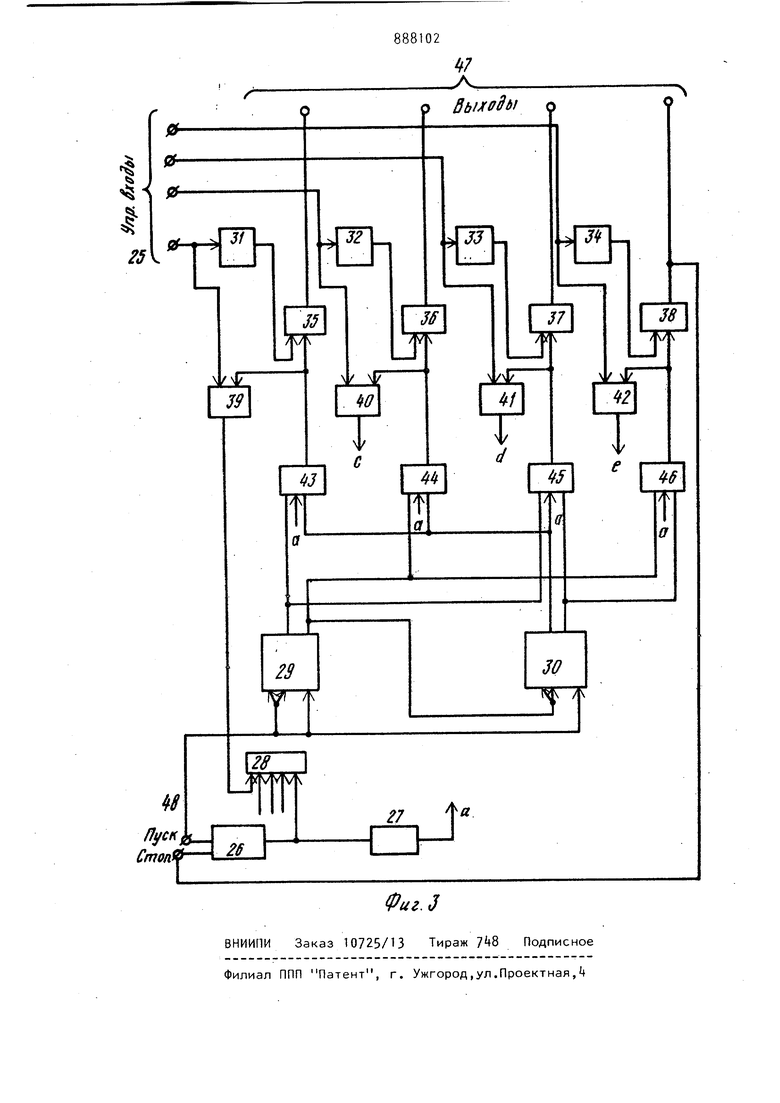

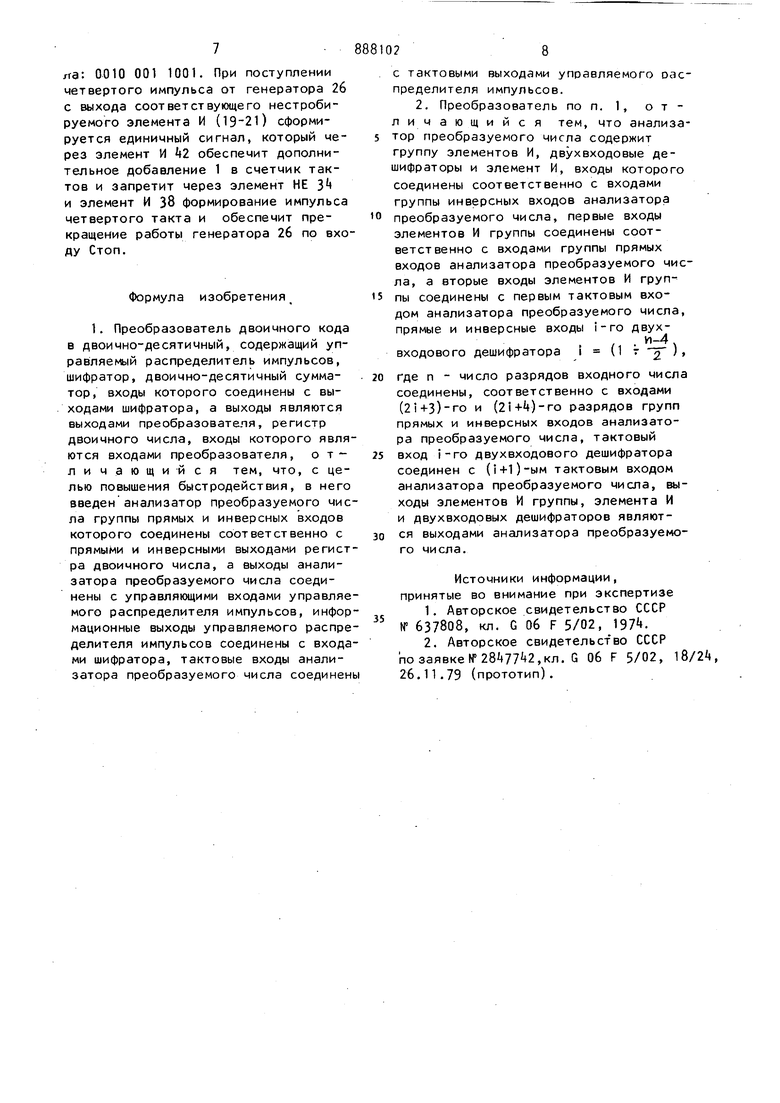

Изобретение относится к вычислительной технике и может быть использовано в устройствах вывода цифровых вычислительных машин, систем телекодовой связи, в цифровых измеритель ных устройствах, работающих в двоичной системе счисления. Известен преобразователь двоичного кода в двоично-десятичный рЗ содержащий регистр двоичного числа, распределитель импульсов, шифратор, группы элементов И. Недостаток известного преобразова теля состоит в низком быстродействии связанном с невозможностью учета реального двоичного кода. Наиболее близким решением по технической сущности и достигаемому результату к изобретению является прео разователь двоичного кода в двоичнодесятичный , содержащий управляемый распределитель импульсов, шифратор, двоично-десятичный сумматор и регистр двоичного числа. Недостаток данного преобразователя состоит в относительно низком быстродействии, связанном с трудностью объединения пар разрядом двоичного кода, эквиваленты которых не имеют единиц в одних и тех же разрядах. Недостаток преобразователя состоит еще и в сложности перестройки преобразователя при изменении его разрядности. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что в преобразователь двоичного кода в двоично-десятичный, содержащий управляемый распределитель импульсов, шифратор, двоично-десятичный сумматор, входы которого соединены с выходами шифратора, а выходы являются выходами преобразователя, регистр двоичного числа, входы которого являются входами преобразователя, введен анализатор преобразуемого числа, группы прямых и инверсных входов которого соединены соответственно с прямыми и инверсными выходами регистра двоичного числа, а выходы анализатора преобразуемого числа соединены с управляющими входами управляемого рас пределителя импульсов, информационные выходы управляемого распределителя им пульсов соединены с входами шифратора, тактовые входы анализатора преобразуемого числа соединены с тактовыми выходами управляемого распределителя импульсов. Анализатор преобразуемого числа содержит группу элементов И, двухвходовые дешифраторы и элемент И, входы которого соединены соответствен но с входами группы инверсных входов анализатора преобразуемого числа первые входы элементов И группы соединены соответственно с входами групп прямых входов анализатора преобразуе мого , а вторые входы элементов И группы соединены с первым тактовым входом анализатора преобразуемого числа, прямые и инверсные входы i-ro двухвходового дешифратора i (1), где п - число разрядов входного числа, соединены соответств но с входами (21+3)-го и ()-го разрядов групп прямых и инверсных входов анализатора преобразуемого чи ла, тактовый вход i-ro двухвходового дешифратора соединен с (1+1)-ым так товым входом анализатора преобразуем го числа, выходы элементов И группы, элемента И и двухвходовых дешифраторов являются выходами анализатора пр образуемого числа. На фиг.1 приведена блок-схема предлагаемого преобразователя; на фиг. 2 - блок-схема анализатора прео разуемого числа; на фиг. 3 - блок-сх ма одного из вариантов построения распределителя импульсов. Преобразователь двоичного кода в двоично-десятичный содержит (см. фиг. 1) регистр 1 двоичного числа, анализатор 2 преобразуемого числа, управляемый распределитель 3 импуль сов, двоично-десятичный сумматор k, шифратор SАнализатор 2 преобразуемого числа содержит (см. фиг. 2) элементы И 6тактовые входы 16, группу прямых вх дов 17i выходы 18 анализатора преоб-55 разуемого числа, элементы И 19-21, группу инверсных входов 22, выходы 23 нестробируемых элементов И. 4 Элементы И 10-12 совместно с элеентом И 20 образуют двухвходовый деифратор . Управляемый распределитель 3 имульсов содержит (см. фиг. 3) управяющие входы 25, генератор 2б серий мпульсов, элемент 27 задержки, элеент ИЛИ 28, триггеры 29-30 разрядов воичного счетчика, элементы НЕ 31 3 лементы И , выходы kj и вход уска 8. f.. . Двоичный регистр 1 представляет собой регистр параллельного действия. Он имеет входы для занесения О или 1 в триггеры соответствующих разрядов. Выходами регистра 1 являются нулевые и единичные выходы триггеров соответствующих разрядов (всего два выхода). Анализатор 2 преобразуемого числа представляет собой набор элементов И, подключенных входами к единичным и нулевым выходам регистра 1 (см. фиг. 2). При этом первые входы элементов И 6-9 соединены соответственно с единичными выходами триггеров первых четырех разрядов регистра 1, Вторые входы указанных элементов И соединены с первым выходом управляемого распределителя импульсов. Все последующие элементы И (10-15) объединены в группы по три элемента каждая. Каждый из элементов И каждой группы подключен к единичным и нулевым выходам соседней пары триггеров регистра 1. При этом первые входы первых двух элементов И каждой группы соединены соответственно с единичными выходами пары соседних разрядов (TJ и 1j ), а вторые входы соединены с нулевыми выходами указанных триггеров, но в обратной последовательности ( Т). Третий элемент И каждой группы своими первыми двумя входами подключены к единичному выходу триггеров соседней пары разрядов регистра 1 {Jf и Т,. Третьи входы элементов И каждой группы являются стробирующими и соединены с соответствующим номеру группы выходом распределителя импульсов. Выходы всех стробируемых элементов И подключены к входам шифратора 5- Кроме того, в анализаторе 2 имеются нестробируемые элементы И , входы 22 которых соединены с нулевыми выходами триггеров регистра 1. При этом входы первого из упомянутых элементов И 19 соединены с нулевыми выходами первых четырех триггеров регист5pa 1, a входы всех последующих указ ных элементов И подключены соответст венно к нулевым выходам триггеров каж дой из последующих пар разрядов реги стра 1, Выходы 23 нестробируемых элементов И подключены к управляющим входам распределителя импульсов. Шифратор 5 обеспечивает формирование выходных сигналов двоичных эквиваленто Выходы шифратора 5 подключены к входам разрядов двоично-десятичного сумматора. Преобразователь работает следующим образом. После нанесения исходного числа в а регистр 1 запускается распределител импульсов, которйй обеспечивает формирование последовательности тактовых импульсов. Если преобразуемое чис ло в регистр t имеет единицы в каждом разряде, то распределитель импульсов сформирует полную последовательность импульсов. В этом случае в первом такте сформируются единичные сигналы на выходах стробируемых элементов И 6-9 (фиг. 2), которые обеспечивают подачу на входы четырех младших разрядов двоично-десятичного сумматора единичных сигналов. За время первого такта двоично-десятичный сумматор суммирует число 2+2 +2 +2 и формирует промежуточный результат 10101000 Вмомент поступления второго импульса формируется единичный сигнал на выходе элемента И 12, а на выходе элемента И 10 и формируется нулевой сигнал. В результате на вход двоично-десятичного сумматора с шифратора поступает код 01101001(96), который за время второго такта суммируется с содержимым двоично-десятичного сумматора и формируется второй промежуточный результат 1000 1000 1000 () В дальнейшем работа в каждом такте преобразователя происходит аналогично. Последний такт обеспечивает, кро ме упомянутых операций, установку рас пределителя в исходное состояние и прекрацает работу генератора 26. Пусть необходимо преобразовать в дво ично-десятичный код число 0011011011. В данном случае анализатор 2 после занесения преобразуемого числа в двоичный регистр 1 подготавливает единич ные сигналы на выходах стробируемых элементов Иб, 7, 9. 11. 15 (фиг. 2) на выходах нестробиоуемых элементов. 02 (формируются нулевые сигналы, так как ни в одной из групп не присутствует два (четыре) нуля. Для преоЬразования числа необходимо на вход 48 (фиг. 3) подать запускающий импульс. По этому сигналу в первый.и второй триггеры 29 и 30. счетчика, заносятся две единицы, генератор 26 формирует равномерную последовательность импульсов, период которых определяется временем задержки в логических элементах устройства и временем выполнения сложения в сумматоре k (фиг. 1). Первый импульс из серии поступает через элемент ИЛИ 28 (фиг. 3) на счетный вход первого триггера и устанавливает его в нулевое состояние. При этом с единичного выхоД первого триггера 29 по счетному ВХОДУ устанавливается а нуль триггер 30. Через время задержки элементов (13, 27) на выходе элемента И фор-, мируется единичный сигнал, который поступает на вход элементов И 35 и 38. как в первой группе (2, 2, 2 не все нули, то на вход, соединенс элементом И 39, подается нулеВОЙ уровень, и элемент заперт. Этот же управляющий сигнал через элемент НЕ 31 открывает элемент И 35, и на первом выходе распределителя импульсов появляется единичный сигнал. Этот сигнал стробирует шифратор, и на входах разрядов 1, 2, 4 двоично-десятичного сумматора появляются единичные сигналы. В двоично-десятичном сумматоре будет записано число 0001.0001. В момент прихода второго импульса от генератора 26 в триггер 29 запишется 1. Элемент И 44 будет подготовлен высокими (единичными) уровнями триггеров счетчика. Через время задержки элемента 27 с выхода элемента И 44 через элемент И 36 на вход дешифратора поступит импульс второго такта. Шифратор по второму такту обеспечит добавление в двоичный сумматор единиц в разряды 5 3 и 2. В результате суммирования в двоично-десятичном сумматоре образуется число 0010.0111. Аналогично сформируется импульс третьего такта. Однако, в виде того, что в третьей группе присутствуют две единицы то шифратор обеспечит добавление единиц в разряды двоичнодесятичного сумматора 3, 4, 8 и 9. В результате образуется двоично-десятичный эквивалент преобразуемого чис/га: 0010 001 1001. При поступлении четвертого импульса от генератора 26 с выхода соответствующего нестробируемого элемента И () сформируется единичный сигнал, который через элемент И 2 обеспечит дополнительное добавление 1 в счетчик тактов и запретит через элемент НЕ З и элемент И 38 формирование импульса четвертого такта и обеспечит прекращение работы генератора 26 по вхо ду Стоп. Формула изобретения 1. Преобразователь двоичного кода в двоично-десятичный, содержащий управляемый распределитель импульсов, шифратор, двоично-десятичный сумматор, входы которого соединены с выходами шифратора, а выходы являются выходами преобразователя, регистр двоичного числа, входы которого явля ются входами преобразователя, отличающийся тем, что, с целью повышения быстродействия, в него введен анализатор преобразуемого чис ла группы прямых и инверсных входов которого соединены соответственно с прямыми и инверсными выходами регист ра двоичного числа, а выходы анализатора преобразуемого числа соединены с управляющими входами управляе мого распределителя импульсов, инфор мационные выходы управляемого распре делителя импульсов соединены с входа ми шифратора, тактовые входы анализатора преобразуемого числа соединен с тактовыми выходами управляемого распределителя импульсов. 2. Преобразователь по п. 1, отличающийся тем, что анализатор преобразуемого числа содержит группу элементов И, двухвходовые дешифраторы и элемент И, входы которого соединены соответственно с входами группы инверсных входов анализатора преобразуемого числа, первые входы элементов И группы соединены соответственно с входами группы прямых входов анализатора преобразуемого числа, а вторые входы элементов И группы соединены с первым тактовым входом анализатора преобразуемого числа, прямые и инверсные входы i-ro двухи-4входового дешифратора i (1 т - ) где п - число разрядов входного числа соединены, соответственно с входами ()-го и ()-го разрядов групп прямых и инверсных входов анализатора преобразуемого числа, тактовый вход i-ro двухвходового дешифратора соединен с (1+1)-ым тактовым входом анализатора преобразуемого числа, выходы элементов И группы, элемента И и двухвходовых дешифраторов являются выходами анализатора преобразуемого числа. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 637308, кл. G Об F 5/02, 197. 2.Авторское свидетельство СССР по заявке tf 28 77+2,кл. G Об F 5/02, 18/2, 26.11.79 (прототип).

/л /л /л /л

иг.г

1 «

I

25

7 V

Авторы

Даты

1981-12-07—Публикация

1980-01-10—Подача