1 12872822

Изобретение относится к импульснойустановки в единицу второго Д-триггетехнике и может быть использовано вра 19 и второму входу четве:ртого лоустройствах измерения и регистрациигического элемента 9, трет1 ;й вход копотоков импульсов.торого соединен с выходом третьего лоЦелью изобретения является расши-j гического элемента, третий вход котор ние функциональных возможностей пу-рого подключен к выходу элемента ИЛИ,

тем устранения ограничений по перио-первый, второй и третий входы котороду следования входных импульсов.го соединены соответственно с первьгм.

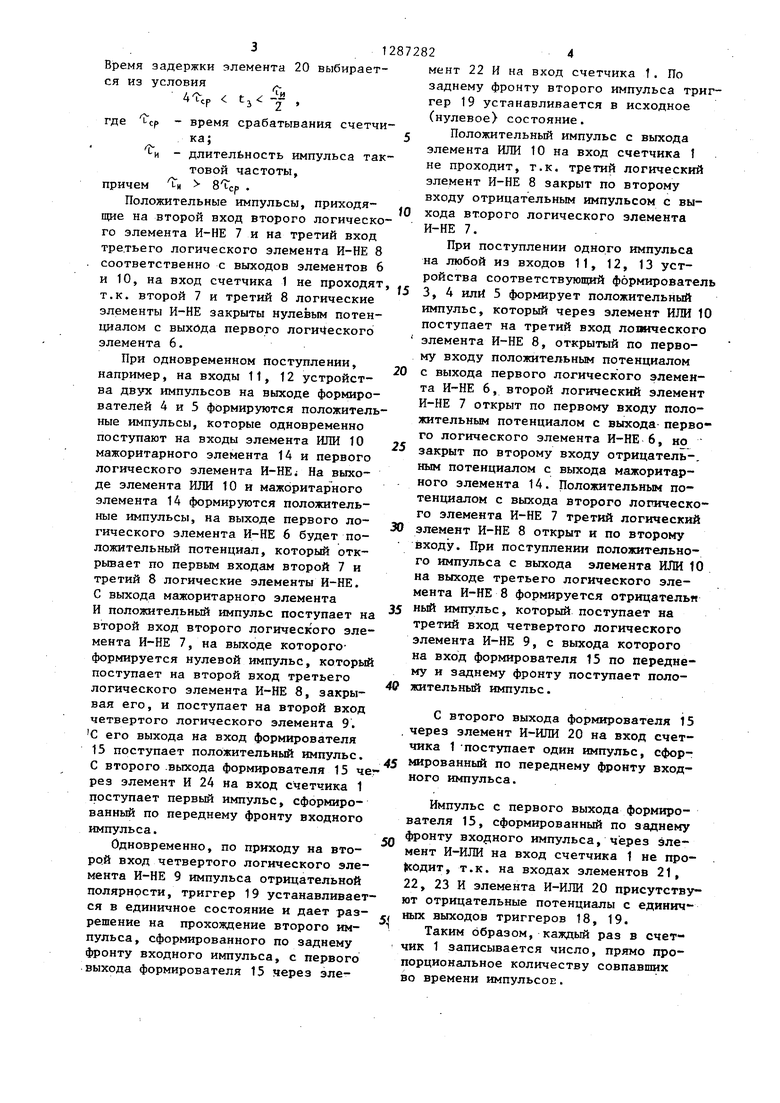

На чертеже представлена функцио-вторым и третьим входами мажоритарнональная схема устройства. О го элемента. Первый и второй входы

Устройство для разделения входныхчетвертого элемента И 24 элемента Иимпульсов содержит счетчик 1, элементИЛИ соединены с вторьш выходом фор2 задержки, первый 3, второй 4 и тре-мирователя 15.

тий 5 формирователи, первый 6, второйУстройство работает следующим об7, третий 8 и четвертый 9 логические 5 разом.

элементы И-НЕ, элемент ИЛИ 10, йер-При одновременном поступлении на

вьп1, второй и третий входы котороговхода 11-13 устройства трех импульсоединены соответственно с первым,сов на выходе трех формирователей

вторым и третьим входами первого ло-3-5 формируются положительные импульгического элемента и через соответст- О сы, которые одновременно поступают

вующие формирователи соединены соот-на входы элемента ИЛИ 10, мажоритарноветственно с первым 11, вторым 12 иго элемента 14 и первого логического

третьим 13 входами устройства. Уст-элемента И-НЕ 6. На выходе первого

ройство также содержит мажоритарныйлогического элемента И-НЕ 6 формируетэлемент 14, формирователь 15 импуль-ся отрицательный импульс, который эаксов по заднему и переднему фронту нарывает по первому входу второй 7 и

первом и втором выходах соответствен-третий 8 логические элементы И-НЕ и

но, пятый 16 и шестой 17 логическиепоступает на первый вход четвертого

элементы И-НЕ, первый 18 и второй 19логического элемента И-НЕ 9. С его

Д-триггеры и элемент И-ШШ 20, выход выхода на вход четвертого, формировакоторого соединен с входом счетчика 1теля 15 по переднему и заднему фрони первыми входами пятого 16 и шестоготу поступает положительный импульс.

17 логических элементов, выходы ко-С второго выхода формирователя 15 четорых соединены с тактовыми входамирез элемент 24 на вход счетчика 1

соответственно первого и второго35 поступает первый импульс, сформированД-триггеров, Д-входы которых соедине-ный по переднему фронту входного имны с общей шиной. Выходы первого 18пульса.

и второго 19.Д-триггеров соединены сОдновременно по приходу на перпервыми входами соответственно пер-вый вход четвертого логического эле- вого 21 и второго 22 элементов И эле- 0 мента И-НЕ 9 нулевого импульса, пер- мента И-ИЛИ, вторые входы которых под- вый Д-триггер 18 устанавливается в

ключены к первому выходу формировате-единичное состояние и дает разрешеля 15, второму входу шестого логичес-ние на прохождение второго импульса,

кого элемента 2 задержки, выход кото-сформированного по заднему фронту

рого соединен с вторым входом пятого45 входного импульса, с первого выхода

логического элемента 16 и первым вхо-формирователя 15 через элемент И 21

дом третьего элемента И 23 элементана вход счетчика 1. И-ИЛИ, второй вход которого соединен

с выходом первого Д-триггера, входПоложительный потенциал прямого

установки в единицу которого подклю-50 выхода Д-триггера 18 дает разрешение

чен к первому входу четвертого логи-на прохождение третьего импульса,

ческого элемента 9, выходу первогосформированного по заднему фронту логического элемента 6, первому входу входного импульса с первого выхода третьего логического элемента 8 и пер- формирователя 15 через элемент 2 за- вому входу второго логического элемен-55 держки и элемент И 23 на вход счетчи- та 7, второй вход которого соединен с ка 1.

выходом мажоритарного элемента 14, аПо заднему фронту третьего импульвыход подключен к второму входу тре-са первый Д-триггер 18 устанавливасттьего логического элемента, входуся в исходное (нулевое) состояние.

Время задержки элемента 20 выбирается из условия

где ь ср - время срабатывания счетчиЧ

1Ги

ка;

- длительность импульса так-- товой частоты.

и 8

ср

Положительные импульсы, приходящие на второй вход второго логического элемента И-НЕ 7 и на третий вход третьего логического элемента И-НЕ 8 соответственно с выходов элементов 6 и 10, на вход счетчика 1 не проходят т.к. второй 7 и третий 8 логические элементы И-НЕ закрыты нулевым потенциалом с выхода первого norHtiecKoro элемента 6.

При одновременном поступлении, например, на входы 11, 12 устройства двух импульсов на выходе формирователей 4 и 5 формируются положительные импульсы, которые одновременно поступают на входы элемента ИЖ 10 мажоритарного элемента 14 и первого логического элемента И-HEj На выходе элемента ИЛИ 10 и мажоритарного элемента 14 формируются положительные импульсы, на выходе первого логического элемента И-НЕ 6 будет положительный потенциал, который отк- рьшает по первым входам второй 7 и третий 8 логические элементы И-НЕ. С выхода мажоритарного элемента И положительный импульс поступает на второй вход второго логического элемента И-НЕ 7, на выходе которого- формируется нулевой импульс, который поступает на второй вход третьего логического элемента И-НЕ 8, закрывая его, и поступает на второй вход четвертого логического элемента 9. С его выхода на вход формирователя 15 поступает положительный импульс. С второго .выхода форм1фователя 15 че рез элемент И 24 на вход счетчика 1 поступает первый импульс, сформированный по переднему фронту входного импульса.

Одновременно, по приходу на второй вход четвертого логического элемента И-НЕ 9 импульса отрицательной полярности, триггер 19 устанавливается в единичное состояние и дает разрешение на прохождение второго импульса, сформированного по заднему фронту входного импульса, с первого выхода формирователя 15 через эле0

5

мент 22 И на вход счетчика t. По заднему фронту второго импульса триггер 19 устанавливается в исходное (нулевое) состояние.

2 Положительный импульс с выхода элемента ШШ 10 на вход счетчика 1 не проходит, т,к, третий логический элемент И-НЕ 8 закрыт по второму входу отрицательным импульсом с выO хода второго логического элемента И-НЕ 7.

При поступлении одного импульса на любой из входов 11, 12, 13 устройства соответствующий формирователь

5 3, 4 или 5 формирует положительный импульс, который через элемент ИЛИ 10 поступает на третий вход лопического элемента И-НЕ 8, открытый по первому входу положительным потенциалом с выхода первого логического элемента И-НЕ 6, второй логический элемент И-НЕ 7 открыт по первому входу положительным потенциалом с выхода первого логического элемента И-НЕ 6, но закрыт по второму входу отрицатель-, ным потенциалом с выхода мажоритарного элемента 14. Положительным потенциалом с выхода второго логического элемента И-НЕ 7 третий логический

0 элемент И-НЕ 8 открыт и по второму входу. При поступлении положительного импульса с выхода элемента ИЛИ 10 на выходе третьего логического элемента И-НЕ 8 формируется отрицательп

5 ный импульс, который поступает на третий вход четвертого логического элемента И-НЕ 9, с выхода которого на вход формирователя 15 по переднему и заднему фронту поступает поло- 0 жительный импульс.

С второго выхода формирователя 15 , через элемент И-ШШ 20 на вход счетчика 1 поступает один импульс, сфор- 5 мированный по переднему фронту входного импульса.

Импульс с первого выхода формирователя 15, сформированный по заднему - фронту входного импульса, через элемент И-ИЛИ на вход счетчика 1 не про- |кодит, т.к. на входах элементов 21, 22, 23 И элемента И-ИЛИ 20 присутствуют отрицательные потенциалы с единичных выходов триггеров 18, 19.

Таким образом, каждый раз в счетчик 1 записывается число, прямо пропорциональное количеству совпавших во времени импульсоЕ.

ормула и

5

зоб

1287282

р е т е н и я

м ве му та ко то вх Иневх по го во вх и эл не а тр ду ге ги ро ги то ИЛ ко Пе жо к И вы за ве

Устройство для разделения входных импульсов, содержащее счетчик, элемент задержки, первый, второй и тре- тий формирователи, первый, второй, третий и четвертъш логические элементы, элемент ИЛИ, первый, второй и третий входы которого соединены соответственно с nepBbiM, вторым и тре- тьим входами первого логического элемента и через соответствующие формирователи соединены соответственно с первым, вторым и третьим входами устройства, отлича-ющееся тем что, с целью расщирения функциональных возможностей путем устранения ограничений по периоду следования входных импульсов, в него введены мажоритарный элемент, формирователь импульсов по заднему и переднему фронту на соответственно первом и втором выходах, пятый и шестой логические элементы, первый и второй Д-триггеры и элемент И-ИЛИ, выход которого соединен с входом счетчика и первыми входами пятого и шестого логических элементов, выходы которых соединены с тактовыми входами соответственно первого я второго Д-триггеров, Д-вхо- дь1 которых соединены с общей шиной, а выходы соединены с первыми входами соответственно первого и второго эле

и переднему фронту на соответственно первом и втором выходах, втор му входу шестого логического- элемен та и входу элемента задержки, выход которого соединен с вторым входом п того логического элемента и первым- входом третьего элемента И элемента ИИЛИ, второй вход которого соединен с выходом первого Д-триггера, вход установки в единицу которого подключен к первому входу четвертого логического элемента, выходу пер вого логического элемента, пефвому входу третьего логичесокго элемента и первому входу второго логического элемента, второй вход которого соед нен с выходом мажоритарного ;1лемент а выход подключен к второму входу третьего логического элемента, входу установки в единицу второго Д-тр гера и второму входу четвертого логического элемента, тетий вход которого соединен с выходом третьего ло гического элемента, третий вход которого подключен к выходу элемента ИЛИ, первый, второй и третий входы которого соединены соответственно с Первым, вторым и третьим входами мажоритарного элемента, причем первый к второй входы четвертого элемента И элемента И-ИЛИ соединены с вторым выходом формирователя импульсов по заднему и переднему фронту На соответственно первом и втором выходах.

ментов И элемента И-ИЛИ, вторые входы которых подключены к первому выхо- 35 а все логические элементы вьшолнены ду формирователя импульсов по задне- в виде элементов И-НЕ.

Составитель А.Смирнов Редактор М.Циткина Техред И.Попович Корректор

Заказ 7728/58 Тираж 899Подписное

БНИИПИ Государственного комитета СССР

по делам изобретений к открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

и переднему фронту на соответственно первом и втором выходах, второму входу шестого логического- элемента и входу элемента задержки, выход которого соединен с вторым входом пятого логического элемента и первым- входом третьего элемента И элемента ИИЛИ, второй вход которого соединен с выходом первого Д-триггера, вход установки в единицу которого подключен к первому входу четвертого логического элемента, выходу первого логического элемента, пефвому входу третьего логичесокго элемента - и первому входу второго логического элемента, второй вход которого соединен с выходом мажоритарного ;1лемента, а выход подключен к второму входу третьего логического элемента, входу установки в единицу второго Д-триггера и второму входу четвертого логического элемента, тетий вход которого соединен с выходом третьего логического элемента, третий вход которого подключен к выходу элемента ИЛИ, первый, второй и третий входы которого соединены соответственно с Первым, вторым и третьим входами мажоритарного элемента, причем первый к второй входы четвертого элемента И элемента И-ИЛИ соединены с вторым выходом формирователя импульсов по заднему и переднему фронту На соответственно первом и втором выходах.

а все логические элементы вьшолнены в виде элементов И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный счетчик | 1982 |

|

SU1040603A1 |

| Устройство для разделения входных импульсов реверсивного счетчика | 1985 |

|

SU1256194A1 |

| @ -Разрядный счетчик с контролем | 1983 |

|

SU1138944A1 |

| Двоичный счетчик с обнаружением ошибок | 1984 |

|

SU1169163A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1984 |

|

SU1218503A1 |

| Удлинитель импульсов | 1978 |

|

SU744944A1 |

| Цифровая регулируемая линия задержки | 1983 |

|

SU1325663A1 |

| Формирователь длительности импульса | 1981 |

|

SU1001453A1 |

| Формирователь импульсов по переднему и заднему фронтам входного импульса | 1978 |

|

SU785976A1 |

| Устройство для обнаружения потери импульса | 1989 |

|

SU1647870A1 |

Изобретение относится к импульсной технике. Может быть использовано J в устройствах измерения и регистрации потоков импульсов. Целью изобре- тения является расширение функциональ ных возможностей путем устранения ограничений по периоду следования входных импульсов. Для достижения поставленной цели в устройство введены мажоритарный элемент 14., формирователь 15 импульсов по заднему и переднему фронту на соответственно первом и втором выходах, пятый 16 и шестой 17 логические И-НЕ П-тригге- ры 18, 19, элемент И/ИЛИ 20; образованы новые функциональные связи,.а : все логические элементы выполнены в виде элементов И-НЕ. Кроме того, .устройство- содержит счетчик 1, элемент 2 задержки, формирователи 3-5, логические элементы 6-9, элемент 10 ИЛИ. На чертеже обозначены входы устройства 11-13. 1 ил. с S 11 12- If. 73(Л ю 00 | N5 00

Авторы

Даты

1987-01-30—Публикация

1984-12-17—Подача