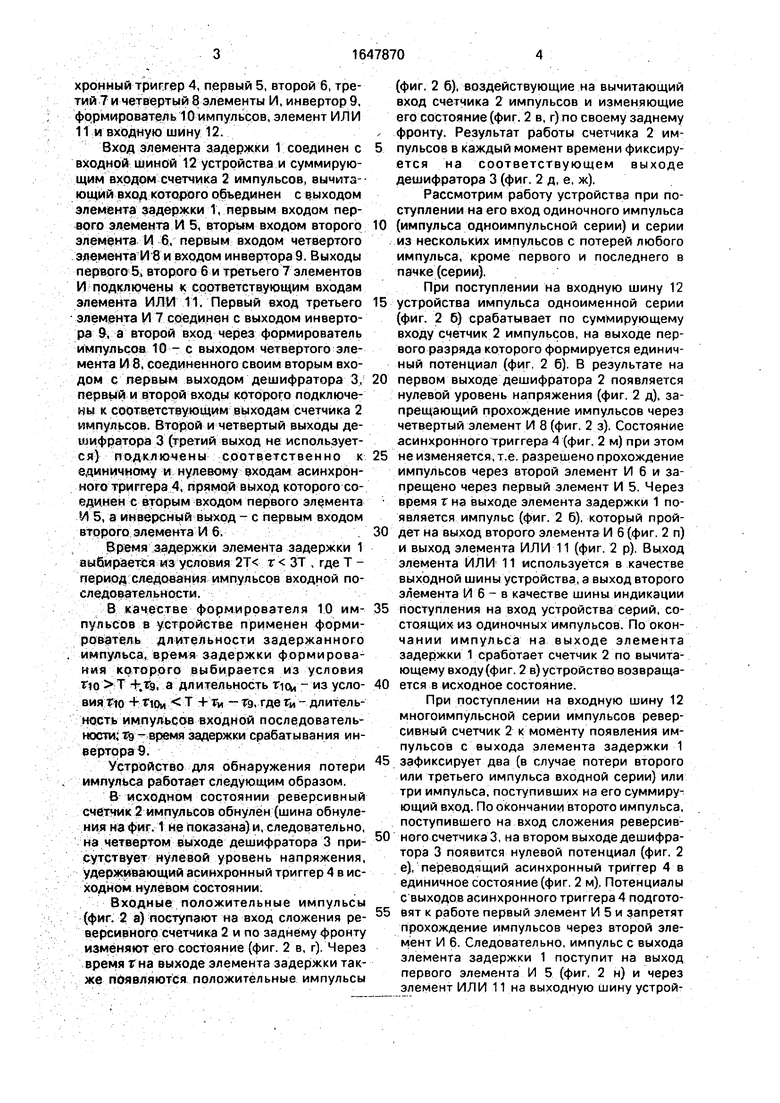

кронный триггер 4, первый 5, второй 6, третий 7 и четвертый 8 элементы И, инвертор 9, формирователь 10 импульсов, элемент ИЛИ 11 и входную шину 12.

Вход элемента задержки 1 соединен с входной шиной 12 устройства и суммирующим входом счетчика 2 импульсов, вычитающий вход которого объединен с выходом элемента задержки 1, первым входом первого элемента И 5, вторым входом второго элемента И 6, первым входом четвертого элемента И 8 и входом инвертора 9. Выходы первого 5, второго 6 и третьего 7 элементов И подключены к соответствующим входам элемента ИЛМ 11. Первый вход третьего элемента И 7 соединен с выходом инвертора 9, а второй вход через формирователь импульсов 10 - с выходом четвертого элемента И 8, соединенного своим вторым входом с первым выходом дешифратора 3, первый и второй входы которого подключены к соответствующим выходам счетчика 2 импульсов. Второй и четвертый выходы дешифратора 3 (третий выход не используется) подключены соответственно к единичному и нулевому входам асинхронного триггера 4, прямой выход которого соединен с вторым входом первого элемента Л 5, а инверсный выход - с первым входом второго элемента И б.

Время задержки элемента задержки 1 выбирается из условия 2Т г ЗТ , где Т - период следования импульсов входной последовательности.

В качестве формирователя 10 импульсов в устройстве применен формирователь длительности задержанного импульса, время задержки формирования которого выбирается из условия ю Т +.Тэ. а длительность тюн - из условия Тю + 10и Т + т - Тэ, где - длительность импульсов входной последовательности; Тд - время задержки срабатывания инвертора 9.

Устройство для обнаружения потери импульса работает следующим образом.

В исходном состоянии реверсивный счетчик 2 импульсов обнулен (шина обнуления на фиг. 1 не показана) и, следовательно, на четвертом выходе дешифратора 3 присутствует нулевой уровень напряжения, удерживающий асинхронный триггер 4 в исходном нулевом состоянии.

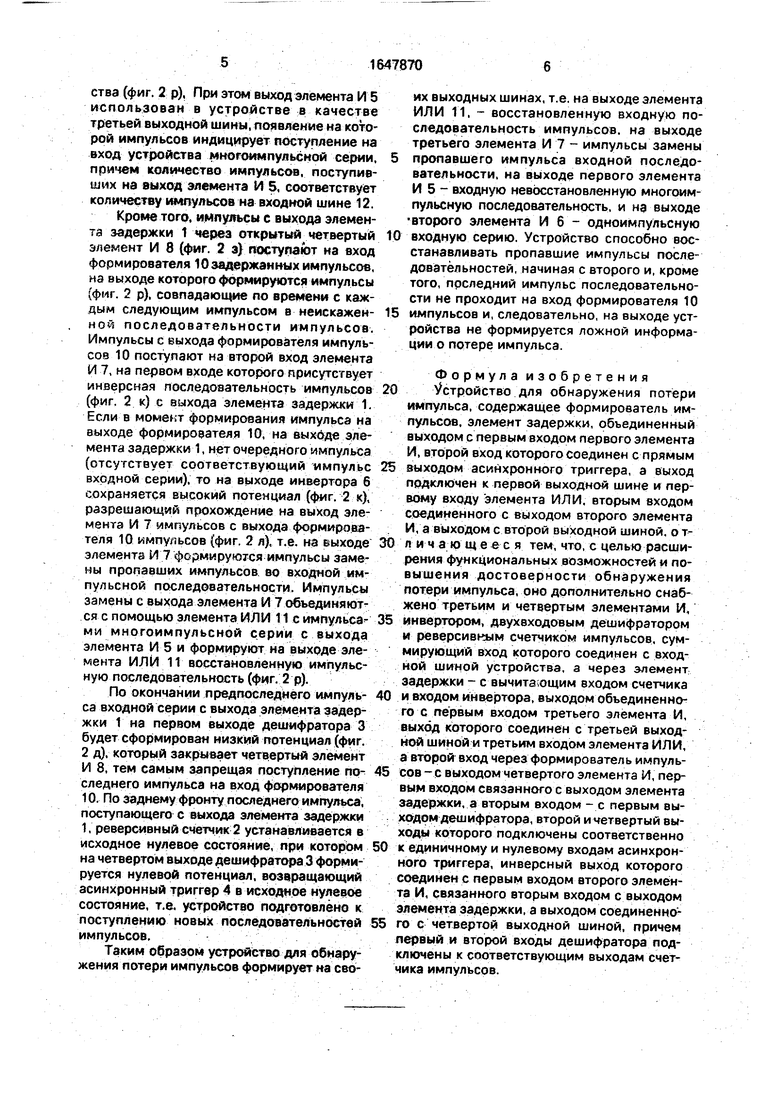

Входные положительные импульсы (фиг. 2 а) поступают на вход сложения реверсивного счетчика 2 и по заднему фронту изменяют его состояние (фиг. 2 в, г). Через время г на выходе элемента задержки также появляются положительные импульсы

(фиг, 2 б), воздействующие на вычитающий вход счетчика 2 импульсов и изменяющие его состояние (фиг. 2 в, г) по своему заднему

фронту. Результат работы счетчика 2 импульсов в каждый момент времени фиксируется на соответствующем выходе дешифратора 3 (фиг. 2 д, е, ж).

Рассмотрим работу устройства при поступлении на его вход одиночного импульса

0 (импульса одноимпульсной серии) и серии из нескольких импульсов с потерей любого импульса, кроме первого и последнего в пачке (серии).

При поступлении на входную шину 12

5 устройства импульса одноименной серии (фиг. 2 б) срабатывает по суммирующему входу счетчик 2 импульсов, на выходе первого разряда которого формируется единичный потенциал (фиг, 2 б). В результате на

0 первом выходе дешифратора 2 появляется нулевой уровень напряжения (фиг. 2 д), запрещающий прохождение импульсов через четвертый элемент И 8 (фиг. 2 з). Состояние асинхронного триггера 4 (фиг, 2 м) при этом

5 не изменяется, т.е. разрешено прохождение импульсов через второй элемент И 6 и запрещено через первый элемент И 5. Через время г на выходе элемента задержки 1 появляется импульс (фиг. 2 б), который прой0 дет на выход второго элемента И 6 (фиг. 2 п) и выход элемента ИЛИ 11 (фиг. 2 р). Выход элемента ИЛИ 11 используется в качестве выходной шины устройства, а выход второго элемента И 6 - в качестве шины индикации

5 поступления на вход устройства серий, состоящих- из одиночных импульсов. По окончании импульса на выходе элемента задержки 1 сработает счетчик 2 по вычитающему входу (фиг. 2 в) устройство возвраща0 ется в исходное состояние.

При поступлении на входную шину 12 многоимпульсной серии импульсов реверсивный счетчик 2 к моменту появления импульсов с выхода элемента задержки 1

5 зафиксирует два (в случае потери второго или третьего импульса входной серии) или три импульса, поступивших на его суммирующий вход. По окончании второто импульса, поступившего на вход сложения реверсив0 ного счетчика 3, на втором выходе дешифратора 3 появится нулевой потенциал (фиг. 2 е), переводящий асинхронный триггер 4 в единичное состояние (фиг. 2 м). Потенциалы С выходов асинхронного триггера 4 подгото5 вят к работе первый элемент И 5 и запретят прохождение импульсов через второй элемент И 6. Следовательно, импульс с выхода элемента задержки 1 поступит на выход первого элемента И 5 (фиг, 2 н) и через элемент ИЛИ 11 на выходную шину устройства (фиг. 2 р), При этом выход элемента И 5 использован в устройстве в качестве третьей выходной шины, появление на которой импульсов индицирует поступление на вход устройства многоимпульсной серии, причем количество импульсов, поступивших на выход элемента И 5, соответствует количеству импульсов на входной шине 12.

Кроме того, импульсы с выхода элемента задержки 1 через открытый четвертый элемент И 8 (фиг. 2 з) поступают на вход формирователя 10 задержанных импульсов, на выходе которого формируются импульсы (фиг. 2 р), совпадающие по времени с каждым следующим импульсом в неискаженной последовательности импульсов. Импульсы с выхода формирователя импульсов 10 поступают на второй вход элемента И 7, на первом входе которого присутствует инверсная последовательность импульсов (фиг. 2 к) с выхода элемента задержки 1. Если в момент формирования импульса на выходе формирователя 10, на выходе элемента задержки 1, нет очередного импульса (отсутствует соответствующий импульс входной серии), то на выходе инвертора б сохраняется высокий потенциал (фиг. 2 к), разрешающий прохождение на выход элемента И 7 импульсов с выхода формирователя 10 импульсов (фиг. 2 л), т.е. на выходе элемента И 7 формируются импульсы замены пропавших импульсов во входной импульсной последовательности. Импульсы замены с выхода элемента И 7 объединяются с помощью элемента ИЛИ 11с импульсами многоимпульсной серии с выхода элемента И 5 и формируют на выходе элемента ИЛИ 11 восстановленную импульсную последовательность (фиг. 2 р).

По окончании предпоследнего импульса входной серии с выхода элемента задержки 1 на первом выходе дешифратора 3 будет сформирован низкий потенциал (фиг. 2 д). который закрывает четвертый элемент И 8, тем самым запрещая поступление последнего импульса на вход формирователя 10. По заднему фронту последнего импульса, поступающего с выхода элемента задержки 1, реверсивный счетчик 2 устанавливается в исходное нулевое состояние, при котором на четвертом выходе дешифратора 3 формируется нулевой потенциал, возвращающий асинхронный триггер 4 в исходное нулевое состояние, т.е. устройство подготовлено к поступлению новых последовательностей импульсов.

Таким образом устройство для обнаружения потери импульсов формирует на своих выходных шинах, т.е. на выходе элемента ИЛИ 11. - восстановленную входную последовательность импульсов, на выходе третьего элемента И 7 - импульсы замены

5 пропавшего импульса входной последовательности, на выходе первого элемента И 5 - входную невосстановленную многоимпульсную последовательность, и на выходе второго элемента И 6 - одноимпульсную

0 входную серию. Устройство способно восстанавливать пропавшие импульсы последовательностей, начиная с второго и, кроме того, последний импульс последовательности не проходит на вход формирователя 10

5 импульсов и, следовательно, на выходе устройства не формируется ложной информации о потере импульса.

Формула изобретения

0 Устройство для обнаружения потери импульса, содержащее формирователь импульсов, элемент задержки, объединенный выходом с первым входом первого элемента И, второй вход которого соединен с прямым

5 выходом асинхронного триггера, а выход подключен к первой выходной шине и первому входу элемента ИЛИ, вторым входом соединенного с выходом второго элемента И, а выходом с второй выходной шиной, о т0 личающееся тем, что, с целью расширения функциональных возможностей и повышения достоверности обнаружения потери импульса, оно дополнительно снабжено третьим и четвертым элементами И,

5 инвертором, двухвходовым дешифратором и реверсивным счетчиком импульсов, суммирующий вход которого соединен с входной шиной устройства, а через элемент задержки - с вычитающим входом счетчика

0 и входом инвертора, выходом объединенного с первым входом третьего элемента И, выход которого соединен с третьей выходной шиной и третьим входом элемента ИЛИ, а второй вход через формирователь импуль5 сов - с выходом четвертого элемента И, первым входом связанного с выходом элемента задержки, а вторым входом - с первым выходом дешифратора, второй и четвертый выходы которого подключены соответственно

0 к единичному и нулевому входам асинхронного триггера, инверсный выход которого соединен с первым входом второго элемента И, связанного вторым входом с выходом элемента задержки, а выходом соединенно5 го с четвертой выходной шиной, причем первый и второй входы дешифратора подключены к соответствующим выходам счетчика импульсов.

.

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетный элемент с контролем | 1986 |

|

SU1370779A1 |

| Селектор серий импульсов по дли-ТЕльНОСТи | 1979 |

|

SU813768A1 |

| Селектор импульсов по длительности | 1981 |

|

SU1001458A2 |

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| Селектор импульсов по длительности | 1980 |

|

SU917331A2 |

| Формирователь длительности импульса | 1981 |

|

SU1001453A1 |

| Устройство для ввода информации | 1980 |

|

SU930311A1 |

| Устройство для обнаружения потери импульса | 1985 |

|

SU1267602A1 |

| Устройство для выделения и вычитания первого импульса из серии | 1990 |

|

SU1718372A2 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

Изобретение может быть использовано как в системах приема и обработки данных для обнаружения потери импульсов в последовательности, так и для восстановления импульса при пропадании его в контролируемой последовательности. Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности распознавания одно- и многоимпульсных входных серий, а также повышение достоверности обнаружения потери импульса путем обеспечения возможности об- наружения потери и восстановления Изобретение относится к импульсной технике и может быть использовано в системах приема и обработки данных для обнаружения потери импульсов в последовательности, а также для восстановления импульса при пропадании его в контролируемой последовательности. Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности распознавания одно- и многоимлульсных входных серий, а также импульса, начиная со второго импульса контролируемой последовательности. Поставленная цель достигается введением в состав устройства дополнительных реверсивного счетчика 2 импульсов, дешифратора 3, третьего 7 и четвертого 8 элементов И, а также инвертора 9. Кроме того устройство содержит элемент задержки 1, асинхронный триггер 4, первый 5 и второй 6 элементы И, формирователь 10 импульсов, элемент ИЛИ 11 и входную шину 12. В качестве формирователя 10 в устройстве применен формирователь длительности задержанного импульса. Устройство формирует на выходе элемента ИЛИ 11 восстановленную входную последовательность импульсов, на выходе элемента И 7 - импульсы замены пропавшего импульса входной последовательности, на выходе элемента И 5 - входную невосстановленную многоимпульсную последовательность, и на выходе элемента И 6 - одноимпульсную входную серию. Время задержки элемента задержки 1 и формирователя 10 (длительность задержанного импульса) выбирают иэ математических выражений, приводимых в описании изобретения. 2 ил. повышение достоверности обнаружения потери импульса путем обеспечения возможности обнаружения и восстановления импульса, начиная с второго импульса контролируемой последовательности. На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - временные диаграммы, поясняющие его работу. Устройство содержит элемент задержки 1, счетчик 2 импульсов, дешифратор 3, асинON J VI СО V О

| Устройство для формирования импульсов | 1982 |

|

SU1064447A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Солесос | 1922 |

|

SU29A1 |

| Устройство для обнаружения потери импульса | 1985 |

|

SU1267602A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

Авторы

Даты

1991-05-07—Публикация

1989-05-05—Подача