)0

11300607

Изобретение относится к нреобразо- вательной технике и может быть исполь зовано в различной радиоэлектронной аппаратуре и устройствах автоматики, в частности в системах электропитания ,

Цель изобретения - увеличение диапазона и линейности регулирования напряжения на выходе конвертора.,

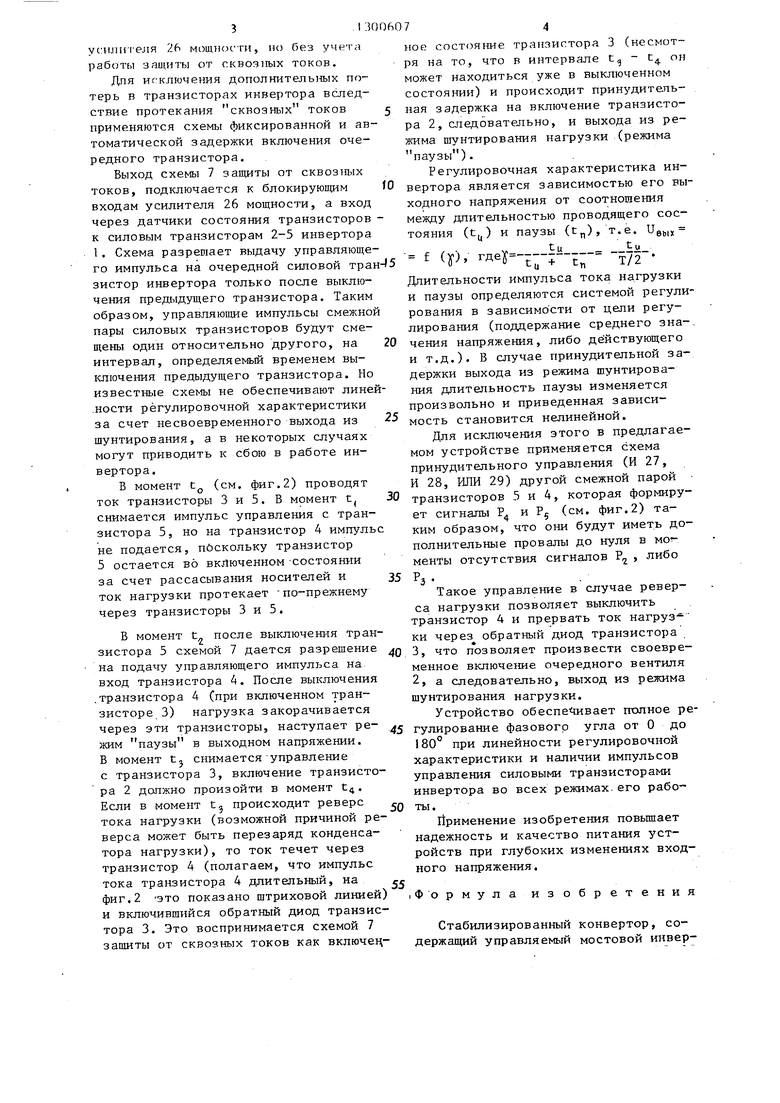

На фиг.1 представлена схема предлагаемого устройства; на фиг,2 - временные диаграммы.

Устройство содержит управляемый транзисторный инвертор i с силовыми транзисторами 2-5, выходной силовой трансформатор 6, схему 7 защиты от сквозных токов, нагрузку 8, выпрямитель 9 с фильтром и усилитель 0 обратной связи, подключенный к входу по постоянному току модулятора 11, к модулирующему входу которого подключен выход источника 12 треугольного напряжения, вход которого подключен к прямому выходу первой ступени делителя 13 частоты. Вход- дделителя 13 подключен к выходу за- дающего генератора 14, Прямой выход мрдулятора 11 подключен к первому схемы И 15 блока 16 логики, второй вход которой подключен к инверсному выходу триггера делителя 13, а инверсный выход модулятора 1 подключен к первому входу второй схемы И 17, второй вход которой подключен к прямому выходу триггера 13. Прямой и инверсный выходы делителя . 13 подключены к тактовым входам счетных триггеров 18 и 19 второй ступени делителя, причем прямой выход

венно к входам смежной пары транзисторов 2 и 3, а прямой и инверсный выходы триггера 25 - через усилитель 26 мощности и схемы И 27 и 28 к другой смежной паре транзисторов 5 и 4, первые входы схем И 27 и 28 подсоединены через схему ИПИ 29 к первым двум выходам усилителя мощности, дополнительный вход которого

подключен к схеме 7 запщты от сквозных токов, вход которой в свою очередь подключен через датчики напряжения к силовым транзисторам 2-5,

Устройство работает следующим 5 образом.

Задающий генератор 14 формирует последовательность импульсов, поступающих на вход делителя 13 частоты (например, счетного триггера). Сигнал с прямого выхода триггера 13 (сигнал а, фиг,2) поступает на вход источника треугольного напряжения.

Треугольное напряжение (си1 нап в, фиг.2) сравнивается с напряжением обратной связи (Ц) с помощью модулятора П, на выходе которого формируется последовательность импульсов (сигнгшы сие, фиг,2) длительность которых зависит от уровня напряжения обратной связи.

Прямой (сигнап а, фиг,2) и инверсный сигналы с выхода делителя 13 частоты поступают на счетные входы триггеров 18 и 19 делителя частоты втр- 35 рой ступени, причем прямой выходной сигнал триггера 18 (сигнал прямого выхода к, фиго2) поступает на D-вход (вход задержки триггера 9 (D - триггер) , что позволяет сформировать вы20

25

30

триггера 18 подкл1 чен к входу задерж- 40 ходной сигнал триггера 19 (сигнал пряки (D-вход) триггера 19,

Прямой и инверсный выходы триггера 19 подключены к вторым входам схем ИЛИ 20 и 21 блока логики, первые входы которых подключены к выходу схемы И 15, Прямой и инверсный выходы триггера 18 подключены к вто- рым входам схем ИЛИ 22 и 23, первые входы которых подключены к выходу схемы И 17, Выходы схем ИЛИ 20 и 22 подключены к S-входам R-S триггеров 24 и 25, выходы схем 21 и 23 подкпю- .чены к R-входам тех же триггеров.

Выходы триггеров 24 и 25 через усилитель 26 мощности подключаются к входам силовых транзисторов 2-5, причем прямой и инверсный выходы триггера 24 подключаются непосредст45

мого выхода т, фиг,2), сдвинутый на 90 относительно аналогичного сигнала триггера 18, Выходные сигналы модулятора 11 и триггеров 18 и 19 поступают на блок 16 логики, содержащий две схемы И (-15 и .17) и четыре схемы ИЛИ (20-23),

Выходные сигналы схемы И 15 (сиг- 50 нал е), .чсхемы И 17 (схемы f), схем ИЛИ 20-23 (сигналы U Uj.) приведены на фиг.2.

Выходные сигналы U - Ug блока 16 логики поступают на R- и S-входы триг- 55 геров 24 и 25, Выходные сигналы триггеров 24 и 25 (сигналы Q, Q4 с прямых выходов приведены сплощной линией на фиг,2, а Qj, Qs штриховой линией) соответствуют выходным сигналам

венно к входам смежной пары транзисторов 2 и 3, а прямой и инверсный выходы триггера 25 - через усилитель 26 мощности и схемы И 27 и 28 к другой смежной паре транзисторов 5 и 4, первые входы схем И 27 и 28 подсоединены через схему ИПИ 29 к первым двум выходам усилителя мощности, дополнительный вход которого

подключен к схеме 7 запщты от сквозных токов, вход которой в свою очередь подключен через датчики напряжения к силовым транзисторам 2-5,

Устройство работает следующим образом.

Задающий генератор 14 формирует последовательность импульсов, поступающих на вход делителя 13 частоты (например, счетного триггера). Сигнал с прямого выхода триггера 13 (сигнал а, фиг,2) поступает на вход источника треугольного напряжения.

Треугольное напряжение (си1 нап в, фиг.2) сравнивается с напряжением обратной связи (Ц) с помощью модулятора П, на выходе которого формируется последовательность импульсов (сигнгшы сие, фиг,2) длительность которых зависит от уровня напряжения обратной связи.

Прямой (сигнап а, фиг,2) и инверсный сигналы с выхода делителя 13 частоты поступают на счетные входы триггеров 18 и 19 делителя частоты втр- рой ступени, причем прямой выходной сигнал триггера 18 (сигнал прямого выхода к, фиго2) поступает на D-вход (вход задержки триггера 9 (D - триггер) , что позволяет сформировать вы

мого выхода т, фиг,2), сдвинутый на 90 относительно аналогичного сигнала триггера 18, Выходные сигналы модулятора 11 и триггеров 18 и 19 поступают на блок 16 логики, содержащий две схемы И (-15 и .17) и четыре схемы ИЛИ (20-23),

ус:или 1 еля 2Ь мощ1к.стн, но без учета работЕ 1 защиты от сквозных токов,

Дпя исключения дополнительных потерь в транзисторах инвертора вследствие протекания скнозных токов применяются схемы фиксированной и автоматической задержки включения очередного транзистора.

Выход схемы 7 защиты от сквозтшх токов, подключается к блокирующим входам усилителя 26 мощности, а вход через датчики состояния транзисторов к силовым транзисторам 2-5 инвертора 1, Схема разретает выдачу управляющего импульса на очередной силовой тран зистор инвертора только после выключения предыдущего транзистора. Таким образом, управляющие импульсы смежной пары силовых транзисторов будут смещены один относительно другого, на интервал, определяемьм временем выключения предыдущего транзистора. Но известные схемы не обеспечивают линей .ности регулировочной характеристики за счет несвоевременного выхода из шунтирования, а в некоторых случаях могут приводить к сбою в работе инвертора.

В момент t (см. фиг.2) проводят ток транзисторы 3 и 5. В момент t снимается импульс управления с транзистора 5, но на транзистор 4 импульс не подается, поскольку транзистор 5 остается во включенном -состоянии за счет рассасывания носителей и ток нагрузки протекает -по-прежнему через транзисторы 3 и 5.

В момент t после выключения транзистора 5 схемой 7 дается разрешение на подачу управляющего импульса на вход транзистора 4. После выключения .транзистора 4 (при включенном транзисторе 3) нагрузка закорачивается через эти транзисторы, наступает режим паузы в выходном напряжении. В момент tj снимается управление

Для исключения этого в предлагаемом устройстве применяется схема принудительного управления (И 27, И 28, ИЛИ 29) другой смежной парой

30 транзисторов 5 и 4, которая фop шpyет сигналы Р и

Pj (см. фиг.2) таким образом, что они будут иметь дополнительные провалы до нуля в менты отсутствия сигналов Р , либо

35 РЗ .

Такое управление в случае реверса нагрузки позволяет выключить транзистор 4 и прервать ток нагруз- ки через обратный диод транзистора

40 3, что позволяет произвести своевременное включение очередного вентиля 2, а следовательно, выход из режима шунтирования нагрузки.

Устройство обеспечивает полное ре45 гулирование фазового угла от О до 180° при линейности регулировочной характеристики и наличии импульсов управления силовыми транзисторами инвертора во всех режимах.его работы.

Йрименение изобретения повьшает надежность и качество питания устройств при глубоких изменениях входного напряжения.

с транзистора 3, включение транзистора 2 должно произойти в момент t. Если в момент t происходит реверс сп тока нагрузки (возможной причиной реверса может быть перезаряд конденсатора нагрузки), то ток течет через транзистор 4 (полагаем, что импульс тока транзистора 4 длительный, на „ фиг. 2 ЭТО показано штриховой линией) и включившийся обратный диод транзистора 3. Это воспринимается схемой 7 защиты от сквозных токов как включец- держащий управляемый мостовой инверФормула изобретения Стабилизированный конвертор, соное состояние транзистора 3 (несмотря на то, что в интервале t - с он может находиться уже в выключенном состоянии) и происходит принудитепь- ная задержка на включение транзистора 2, следовательно, и выхода из режима шvнтиpoвaния нагрузки (режима паузы).

Регулировочная характеристика инвертора является зависимостью его выходного напряжения от соотношения между длительностью проводящего сосO5 0

тояния f

(t(j) и паузы (t), т.е. U, (у),

ц/ г «itajf-iui /j 1.5;. - etJlX

tu tu.

ty + t; т72

Длительности импульса тока нагрузки и паузы определяются системой регулирования в зависимости от цели регулирования (поддержание среднего зна-. чения напряжения, либо действующего и т.д.). В случае принудительной задержки выхода из режима шунтирования длительность паузы изменяется произвольно и приведенная зависи мость становится нелинейной.

Для исключения этого в предлагаемом устройстве применяется схема принудительного управления (И 27, И 28, ИЛИ 29) другой смежной парой

0 транзисторов 5 и 4, которая фop шpyет сигналы Р и

Pj (см. фиг.2) таким образом, что они будут иметь дополнительные провалы до нуля в менты отсутствия сигналов Р , либо

РЗ .

Такое управление в случае реверса нагрузки позволяет выключить транзистор 4 и прервать ток нагруз- ки через обратный диод транзистора

3, что позволяет произвести своевременное включение очередного вентиля 2, а следовательно, выход из режима шунтирования нагрузки.

Устройство обеспечивает полное регулирование фазового угла от О до 180° при линейности регулировочной характеристики и наличии импульсов управления силовыми транзисторами инвертора во всех режимах.его работы.

Йрименение изобретения повьшает надежность и качество питания устройств при глубоких изменениях входного напряжения.

держащий управляемый мостовой инвердержащий управляемый мостовой инверФормула изобретения Стабилизированный конвертор, со5 13

тор с трансформатором на выходе н узел управления, включаюищй в себя соединенные последовательно задающий генератор, делитель частоты, генератор пилообразного напряжения, модуля- тор и усилитель мопщости, а также выпрямитель, фильтр и усилит(У1ь обратной связи, отличающийся тем, что, с цепью увеличения диапазона и линейности регулирования напряжения на выходе конвертора, генератор пилообразного напряжения выполнен в виде источника треугольного напряжения, введены блок логики на двух схемах И и четырех ИЛИ, RS-триггеры и схема принудительного управления одной из смежных пар силовых транзисторов, причем вход первой -ступени делителя частоты подключен к задающему

генератору, а выход - к входу источ- 20 ника треугольного напряжения, выход которого подключен к одному из входов модулятора, второй вход которого подключен к выходу усилитепя обратной

t5

теля частоты подключены к вторым вхо 0 дам первых схем ИЛИ блока логики, первые входы которых подключены к вы ходу второй схемы И , причем выходны сигналы второго триггера второй сту пени делителя частоты подключены к t5 вторым входам вторых схем ИЛИ блока логики, первые входы которых подключаются к выходу первой схемы И, а выходы схем ИЛИ через RS-триггеры подключены к входам усилителя мощнос ти, который своими двумя выходами подключен к входам одной пары смеж- ных транзисторов инвертора непосредственно, а двумя другими - к входам другой пары смежных транзисторов

связи, а прямой и инверсные выходы мо-25 через схемы И, вторые входы которых

дулятора подключены к первым входам схем И блока логики, вторые входы которых подключены к прямому и инверсному выходам первой ступени делителя частоты, которые в свою очередь подключены к тактовым входам двух триггеров второй ступени делителя, причем прямой выход первого триггера второй ступени делителя подкпючен к входу задерж{ и второго триггера, а выходы первого триггера второй CTynenvj дели

теля частоты подключены к вторым вхо- дам первых схем ИЛИ блока логики, первые входы которых подключены к выходу второй схемы И , причем выходные сигналы второго триггера второй ступени делителя частоты подключены к вторым входам вторых схем ИЛИ блока логики, первые входы которых подключаются к выходу первой схемы И, а выходы схем ИЛИ через RS-триггеры подключены к входам усилителя мощности, который своими двумя выходами подключен к входам одной пары смеж- ных транзисторов инвертора непосредственно, а двумя другими - к входам другой пары смежных транзисторов

через схемы И, вторые входы которых

подключены через схему ИЛИ к первым двум выходам усилителя мощности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизированный преобразователь постоянного напряжения в постоянное | 1985 |

|

SU1267560A1 |

| РЕЗЕРВИРОВАННЫЙ ИСТОЧНИК ТОКА | 2013 |

|

RU2512890C1 |

| Стабилизированный конвертор | 1979 |

|

SU892425A1 |

| Регулируемый конвертор | 1986 |

|

SU1365290A1 |

| Релейно-импульсный стабилизатор постоянного напряжения | 1990 |

|

SU1758640A1 |

| Программируемый преобразователь напряжения произвольной формы в напряжение требуемой формы | 1990 |

|

SU1711303A1 |

| Регулируемый преобразователь постоянного напряжения | 1986 |

|

SU1336175A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ИНТЕРВАЛОВ | 2011 |

|

RU2470458C1 |

| Стабилизированный преобразователь напряжения | 1988 |

|

SU1614007A1 |

| Преобразователь постоянного напряжения в трехфазное квазисинусоидальное | 1986 |

|

SU1361691A1 |

Изобретение относится к преобразовательной технике и может быть использовано во вторичных источниках электропитания. Цель изобретения - увеличение диапазона и линейности регулирования напряжения на выходе. Конвертор содержит инвертор 1 с тран зисторами 2-5, силовой трансформатор 6, схему защиты 7 от сквозных токов, нагрузку 8, выпрямитель с фильтром 9, усилитель обратной связи 10, модулятор 11, генератор пилообразного напряжения 12, задающий генератор 14, дeлитeл)-частоты 13, усилитель мощности 26. Генератор пилообразного напряжения 12 выполнен в виде источника треугольного напряжения и введен блок логики 16, выполненный на схемах И 15, 17, триггерах.18, 19 схемах ИЛИ 20-23, а также введены RS-триггеры 24 и 25 и схема принудительного управления на элементах И 27, 28 и элементе ИЛИ 29. Управление обеспечивает полное регулирование; фазового угла от О до 180° при линейности регулировочной характеристики и наличии импульсов управления транзисторами 2-5 во всех режимах работы. Изобретение повышает надежность и качество питания при изменениях входно- го напряжения. 2 ил. Г о

| Запор для дверей крытых товарных вагонов | 1923 |

|

SU479A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Стабилизированный конвертор | 1978 |

|

SU888295A2 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-03-30—Публикация

1985-06-24—Подача