11301326

Изобретение относится к автоматике и вычислительной технике и может быть использовано для ввода инфор- MamiH с магнитной ленты в ЭВМ.

5 с

Цель изобретения - повышение помехозащищенности устройства за счет коррекции фазы частоты синхронизации

На фи1 .1-9 приведены схемы устройства (варианты) и временные диаграммы.

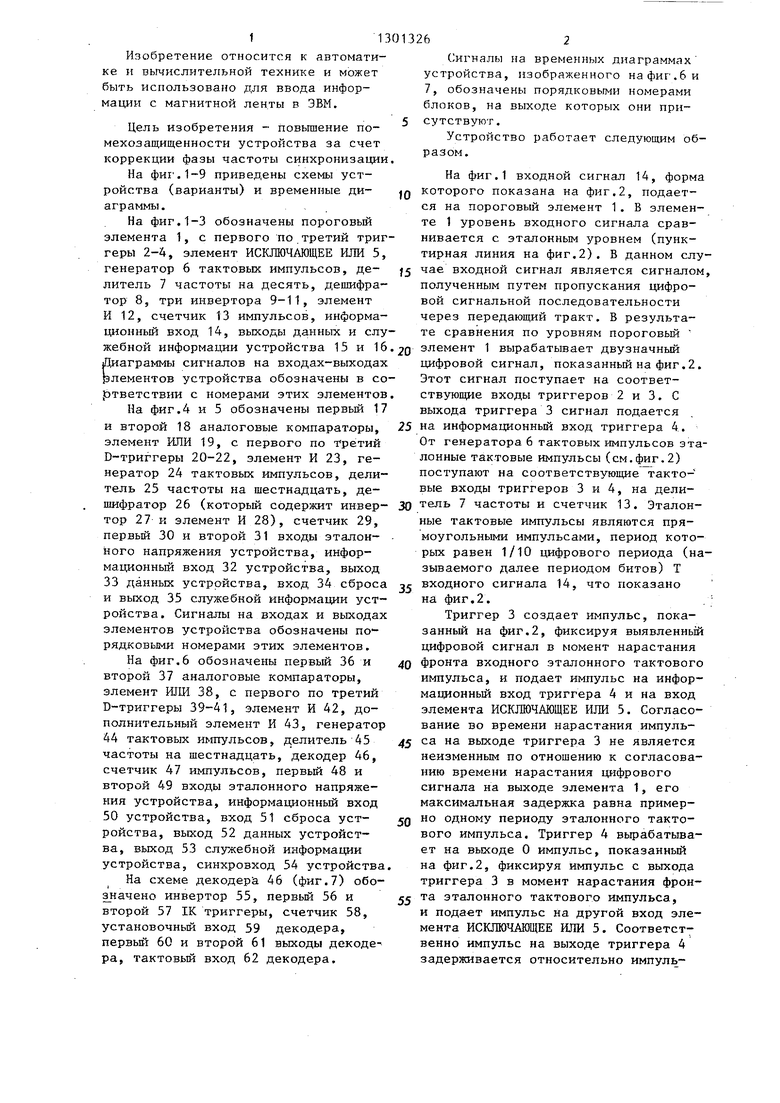

На фиг,1-3 обозначены пороговый элемента 1, с первого по третий триггеры 2-4, элемент ИСКЛЮЧАЮЩЕЕ ИЖ 5, генератор 6 тактовых импульсов, делитель 7 частоты на десять, дешифратор 8, три инвертора 9-11, элемент И 12, счетчик 13 импульсов, информаНа фиг.1 входной сигнал 14, форм IQ которого показана на фиг.2, подается на пороговый элемент 1. В элемен те 1 уровень входного сигнала сравнивается с эталонным уровнем (пунктирная линия на фиг.2). В данном сл },5 чае входной сигнал является сигнало полученным путем пропускания цифровой сигнальной последовательности через передающий тракт. В результате сравнения по уровням пороговый

ционный вход 14, выходы данных и служебной информации устройства 15 и 16.20 элемент 1 вырабатывает двузначный Диаграммы сигналов на входах-выходах цифровой сигнал, показанный на фиг.2 {элементов устройства обозначены в со- )этветствии с номерами этих элементов.

Этот сигнал поступает на соответствующие входы триггеров 2 и 3. С выхода триггера 3 сигнал подается 25 на информационный вход триггера 4. От генератора 6 тактовых импульсов эт лонные тактовые импульсы (см. фиг. 2) поступают на соответствующие такто- вые входы триггеров 3 и 4, на делиНа фиг.4 и 5 обозначены первый 17 и второй 18 аналоговые компараторы, элемент ИЛИ 19, с первого по третий D-триггеры 20-22, элемент И 23, генератор 24 тактовых импульсов, делитель 25 частоты на шестнадцать, деЭтот сигнал поступает на соответствующие входы триггеров 2 и 3. С выхода триггера 3 сигнал подается 25 на информационный вход триггера 4. От генератора 6 тактовых импульсов эталонные тактовые импульсы (см. фиг. 2) поступают на соответствующие такто- вые входы триггеров 3 и 4, на делишифратор 26 (который содержит инвер- 30 .ь 7 частоты и счетчик 13. Эталон- тор 27 и элемент И 28), счетчик 29, ные тактовые импульсы являются пря- первый 30 и второй 31 входы эталон- . моугольными импульсами, период кото- ного напряжения устройства, инфор- рых равен 1/10 цифрового периода (на- мационньш вход 32 устройства, выход зываемого далее периодом битов) Т 33 данных устройства, вход 34 сброса з и выход 35 служебной информации устройства. Сигналы на входах и выходах элементов устройства обозначены порядковыми номерами этих элементов.

40

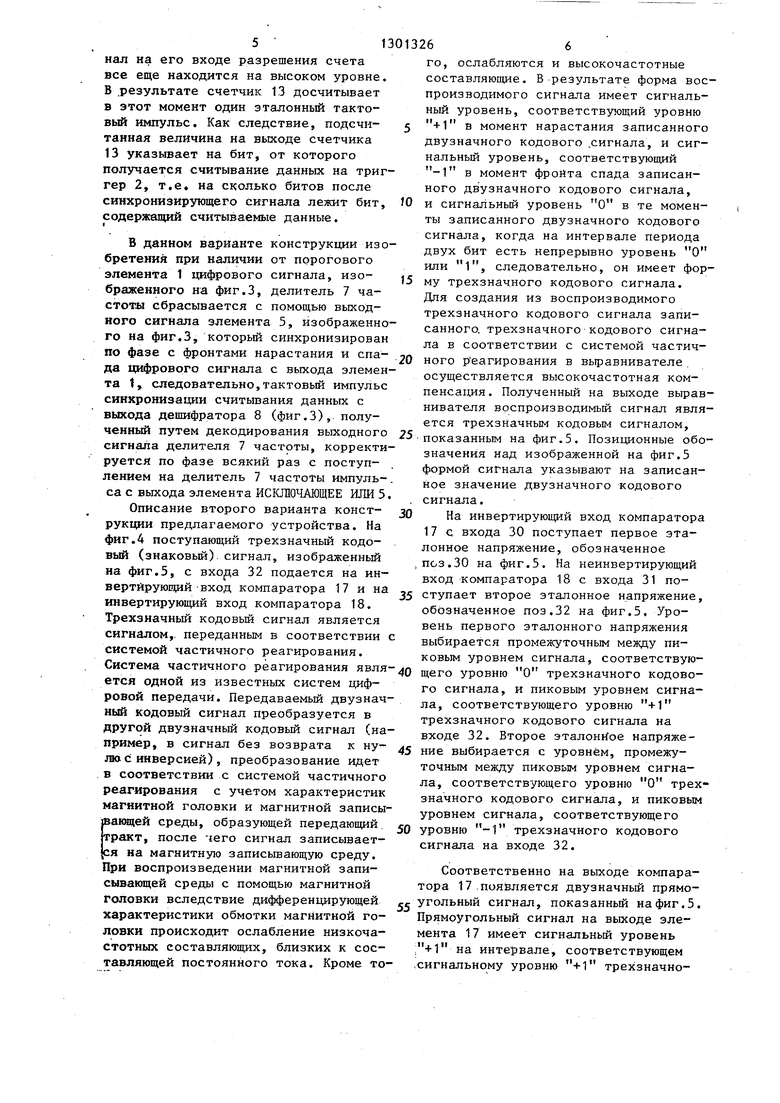

На фиг.6 обозначены первый 36 и второй 37 аналоговые компараторы, элемент ШШ 38, с первого по третий D-триггеры 39-41, элемент И 42, дополнительный элемент И 43, генератор 44 тактовых импульсов, делитель 45 частоты на шестнадцать, декодер 46, счетчик 47 импульсов, первый 48 и второй 49 входы эталонного напряжения устройства, информационный вход 50 устройства, вход 51 сброса устройства, выход 52 данных устройства, выход 53 служебной информации устройства, синхровход 54 устройства.

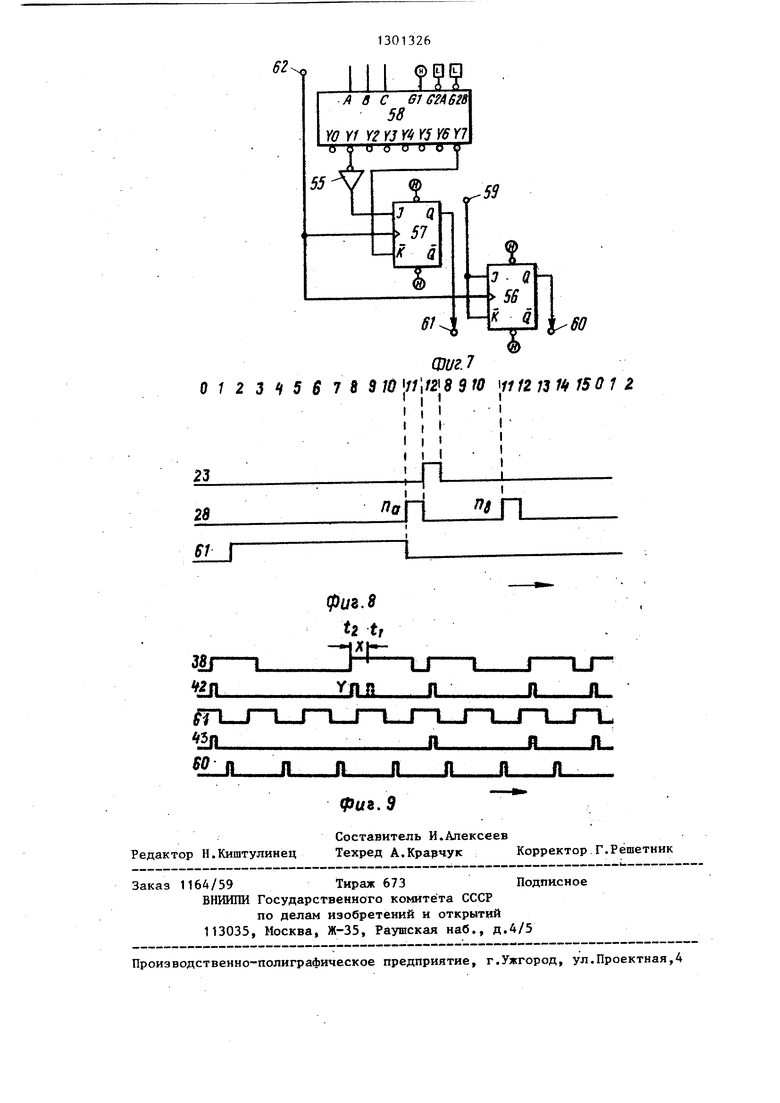

На схеме декодера 46 (фиг.7) обозначено инвертор 55, первьм 56 и второй 57 IK триггеры, счетчик 58, установочный вход 59 декодера, первый 60 и второй 61 выходы декоде ра, тактовьш вход 62 декодера.

входного сигнала 14, что показано на фиг.2.

Триггер 3 создает импульс, показанный на фиг.2, фиксируя выявленньй цифровой сигнал в момент нарастания фронта входного эталонного тактового импульса, и подает импульс на инфор- мационньй вход триггера 4 и на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5. Согласование во времени нарастания импуль J5 са на выходе триггера 3 не является неизменным по отношению к согласованию времени нарастания цифрового сигнала на выходе элемента 1, его максимальная задержка равна примерtfQ НО одному периоду эталонного тактового импульса. Триггер 4 вырабатывает на выходе О импульс, показанный на фиг.2, фиксируя импульс с выхода триггера 3 в момент нарастания фрон-

та эталонного тактового импульса, и подает импульс на другой вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5. Соответственно импульс на выходе триггера 4 задерживается относительно импульСигналы на временных диаграммах устройства, изображенного на фиг.6 и 7, обозначены порядковыми номерами блоков, на выходе которых они при- сутствугот.

Устройство работает следующим образом.

На фиг.1 входной сигнал 14, форма которого показана на фиг.2, подается на пороговый элемент 1. В элементе 1 уровень входного сигнала сравнивается с эталонным уровнем (пунктирная линия на фиг.2). В данном слу- чае входной сигнал является сигналом, полученным путем пропускания цифровой сигнальной последовательности через передающий тракт. В результате сравнения по уровням пороговый

элемент 1 вырабатывает двузначный цифровой сигнал, показанный на фиг.2

элемент 1 вырабатывает двузначный цифровой сигнал, показанный на фиг.2

Этот сигнал поступает на соответствующие входы триггеров 2 и 3. С выхода триггера 3 сигнал подается на информационный вход триггера 4. От генератора 6 тактовых импульсов эталонные тактовые импульсы (см. фиг. 2) поступают на соответствующие такто- вые входы триггеров 3 и 4, на дели ь 7 частоты и счетчик 13. Эталон- ые тактовые импульсы являются пря- моугольными импульсами, период кото- рых равен 1/10 цифрового периода (на- зываемого далее периодом битов) Т

входного сигнала 14, что показано на фиг.2.

Триггер 3 создает импульс, показанный на фиг.2, фиксируя выявленньй цифровой сигнал в момент нарастания фронта входного эталонного тактового импульса, и подает импульс на инфор- мационньй вход триггера 4 и на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5. Согласование во времени нарастания импульса на выходе триггера 3 не является неизменным по отношению к согласованию времени нарастания цифрового сигнала на выходе элемента 1, его максимальная задержка равна примерНО одному периоду эталонного тактового импульса. Триггер 4 вырабатывает на выходе О импульс, показанный на фиг.2, фиксируя импульс с выхода триггера 3 в момент нарастания фрон-

та эталонного тактового импульса, и подает импульс на другой вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5. Соответственно импульс на выходе триггера 4 задерживается относительно импульса на выходе триггера 3 на время задержки, соответствующее одному периоду эталонных) тактовых импульсов. В результате элемент 5 ИСКЛЮЧАЮЩЕЕ ИЛИ вырабатывает импульс, показанный на фиг.2. Ширина этого импульса соответствует одному периоду эталонных тактовых импульсов, этот сигнал вырабатывается при фронте нарастания и при фронте спада цифрового сигнала на выходе элемента 1. Так как импульс с выхода элемента 5 вьфабатывается в окрестностях фронтов нарастания и спада цифрового сигнала с выхода элемента 1, то этот импульс является импульсом выявления отклонения по уровню (импульсом выявления фронта) цифрового сигнала с выхода элемента 1. Импульс выявления отклонения по уровню с выхода элемента 5 подается на вход сброса делителя 7 для его обнуления фронтом нарастания.

Делитель 7 частоты считает эталонные тактовые импульсы и подает ре- зультирующий выходной сигнал с выходов Q,-Q4 на декодер 8. На интервале между девятым и десятым эталонным тактовым импульсом после сброса делитель 7 частоты вырабатывает сигнал, пери- од повторения которого равен упомянутому выше периоду битов Т, и подает этот сигнал с выхода переноса на вход разрешения счетчика 13. В состав дешифратора 8 входят инверторы 9 - 11 и элемент И-12 на четыре входа. Когда а входах Q,, Qj, Q4 делителя часто- }гы 7 существуют низкие уровни и только на выходе Q создается сигнал с высоким уровнем, т.е. когда делитель 7 насчитал четыре эталонных тактовых импульса, на всех четырех входах элемента И 12 присутствует высокий уровень. Поэтому элемент И 12 вьфа- батывает сигнал высокого уровня, по- казанный на фиг.2, и подает этот сигнал на тактовьй вход схемы триггера 2 в качестве тактового импульса синхронизации считывания данных. Фаза полученного таким образом так- тового импульса синхронизации считывания данных соответствует центру периода битов сигнала на входе 14, показанного на фиг.2. С приходом фронта нарастания упомянутого такто- вого импульса синхронизации считывания данных на триггер 2 в нем фиксируется цифровой сигнал с выхода порогового элемента 1, поданный на информационный вход триггера 2, полученный в результате на его выходе импульс, изображенный на фиг.2, подается на выход 15 устройства. Из Сравнения сигналов 14 и 2 на фиг.2 ясно видно, что импульс на выходе триггера 2 является считьшаемой информацией входного сигнала с

Кроме того, входной сигнал получается следующим образом. Цифровые данные, полученные после цифровой импульсной модуляции аналогового информационного сигнала, разделяются н заранее определ;енные секции, и к сигналу каждой секции добавляется сигнал синхронизации с фиксированной структурой, а также часто добавляется сигнал выявления ошибки в коде и сигнал исправления кодовой ошибки. Сам сигнал на входе получается из передающего тракта с помощью последовательной во времени передачи цифрового сигнала. Поэтому фронты нарастания и спада входного сигнала не- являются настолько крутыми, как показано на фиг.2, из-за ослабления высоких частот в передающем тракте и из-за других причин. Входной сигнал передается непрерывно с синхронизирующим сигналом, и синхронизирующий сигнал выделяется схемой выявления синхронизирующего сигнала (не показана), используя фиксированную структурную характеристику синхронизирующего сигнала. Сигнал выявления синхронизирующего сигнала подается на вход сброса счетчика 13 че-. рез соответствуюш 1й вход устройства.

На отрезке времени, когда входной сигнал на входе разрешения счетчика (13 имеет высокий уровень, счетчик :ведет счет эталонных тактовых им- пульсов, поступающих на его тактовый ход. На выходе 16 получается результирующий выходной сигнал. Отрезок времени, на котором входной сигнал на входе разрешения счетчика 13 имеет высокий уровень, соответствует интервалу от девятого до десятого эталонного тактового импульса после обнуления делителя 7 частоты. Однако фаза эталонного тактового импульса чуть запаздывает из-за задержки, вводимой схемными элементами в делителе 7 частоты. Поэтому в момент,когда десятый тактовый эталонный импуль подается на счетчик 13, входной сигнал на его входе разрешения счета все еще находится на высоком уровне. В результате счетчик 13 досчитывает в этот момент один эталонный тактовый импульс. Как следствие, подсчитанная величина на выходе счетчика 13 указьшает на бит, от которого получается считывание данньк на триггер 2, т.е. на сколько битов после синхронизирующего сигнала лежит бит, содержащий считываемые данные.

В данном варианте конструкции изо бретения при наличии от ПОРОГОВОГО элемента 1 цифрового сигнала, изображенного на фиг.З, делитель 7 ча- стот-Ы сбрасывается с помощью выходного сигнала элемента 5, изображенного на фиг.З, который синхронизирован по фазе с фронтами нарастания и спа- да цифрового сигнала с выхода элемента 1, следовательно,тактовый импульс синхронизации считывания данных с выхода дешифратора 8 (фиг.З), полученный путем декодирования выходного сигнала делителя 7 частоты, корректируется по фазе всякий раз с поступлением на Делитель 7 частоты импульса с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5

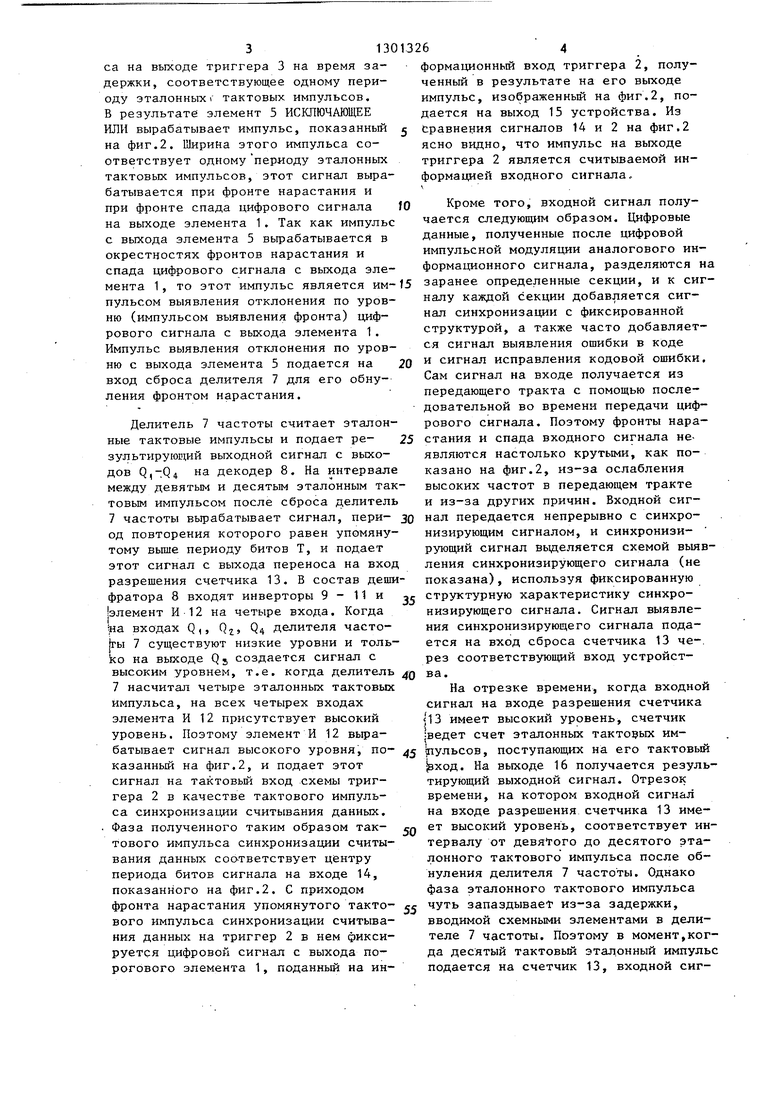

Описание второго варианта конструкции предлагаемого устройства. На фиг.4 поступающий трехзначный кодовый (знаковый) сигнал, изображенньй на фиг.З, с BXOjpa 32 подается на инвертирующий-вход компаратора 17 и на инвертирукмций вход компаратора 18. Трехзначный кодовый сигнал является сигналом,, переданным в соответствии системой частичного реагирования. Система частичного реагирования ЯВЛЯ ется одной из известных систем цифровой передачи. Передаваемьй двузначный кодовый сигнал преобразуется в другой двузначный кодовый сигнал (например, в сигнал без возврата к ну- люс инверсией), преобразование идет . в соответствии с системой частичного реагирования с учетом характеристик магнитной головки и магнитной записы шакнцей среды, образующей передающий. (тракт, после чего сигнал записывает- |ся на магнитную записывающую среду. При воспроизведении магнитной записывающей среды с помощью магнитной головки вследствие дифференцирующей характеристики обмотки магнитной головки происходит ослабление низкочастотных составляющих, близких к составляющей постоянного тока. Кроме то

0

5

5

Q

0

5

го, ослабляются и высокочастотные составляющие. В-результате форма воспроизводимого сигнала имеет сигнальный уровень, соответствующий уровню +1 в момент нарастания записанного двузначного кодового .сигнала, и сигнальный уровень, соответствующий -1 в момент фройта спада записанного двузначного кодового сигнала, и сигнальный уровень О в те моменты записанного двузначного кодового сигнала, когда на интервале периода двух бит есть непрерывно уровень О или 1, следовательно, он имеет форму трехзначного кодового сигнала. Для создания из воспроизводимого трехзначного кодового сигнала записанного, трехзначного кодового сигнала в соответствии с системой частичного р еагирования в выравнивателе осуществляется высокочастотная компенсация . Полученный на выходе выравнивателя воспроизводимый сигнал является трехзначным кодовым сигналом, показанным на фиг.З. Позиционные обозначения над изображенной на фиг.З формой сигнала указывают на записанное значение двузначного кодового сигнала.

На инвертирующий вход компаратора 17 с входа 30 поступает первое эталонное напряжение, обозначенное поз.30 на фиг.З. На неинвертирующий вход компаратора 18 с входа 31 поступает второе эталонное напряжение, обозначенное поз.32 на фиг.З. Уровень первого эталонного напряжения выбирается промежуточным между пиковым уровнем сигнала, соответствующего уровню О трехзначного кодового сигнала, и пиковым уровнем сигнала, соответствующего уровню +1 трехзначного кодового сигнала на входе 32. Второе эталонное напряжение выбирается с уровнем, промежуточным между пиковым уровнем сигнала, соответствующего уровню О трехзначного кодового сигнала, и пиковым уровнем сигнала, соответствующего уровню -1 трехзначного кодового сигнала на входе 32.

Соответственно на вьшоде компаратора 17 .появляется двузначный прямоугольный сигнал, показанный на фиг.З. Прямоугольный сигнал на выходе элемента 17 имеет сигнальный уровень на интервале, соответствующем .сигнальному уровню +1 трехзначно го кодового сигнала на входе 32, и имеет сигнальный уровень О на интервалах, соответствующих сигнальным уровням -1 и О входного трехзначного кодового сигнала/ На выходе компаратора 18 получается, двузначный прямоугольный сигнал, показанный на фиг.5. Этот сигнал имеет сигнальный уровень +1 на интервале, соответствующем сигнальному уровню -1 трехзначного кодового сигнала на входе 32, и имеет сигнальный уровень О на-интервалах, соответствующих сигнальным уровням +1 и О трехзначного кодового сигнала на входе 32. Элемент ИЛИ 19 вырабатывает прямоугольный сигнал, показанный на фит,5. Прямоугольный сигнал с выхода элемента ИЛИ 19 поступает на соответствующие информационные входы триггеров 20 и 21 в качестве сигналов выявления уровня.

Сигнал, полученный на выходе Q триггера 21, поступает на информационный вход триггера 22. От генератора. 24 тактовых импульсов на соответствующие тактовые входы триггеров 21 и 22 поступает эталонный тактовый сигнал, период которого равен 1/10 периода битов трехзначного кодового сигнала на входе 32. Сигнал с выхода Q триггера 21 и сигнал с выхода Q триггера 22 поступает соответственно на элемент И 23, который вырабатывает импульс, показанный на фиг.5. Этот импульс находится в синхронизме по фазе с фронтом нарастания сигнала выявления уровня на выходе элемента ИЛИ 19, что видно из фиг.5. Импульс поступает с выхода элемента И 23 на вход загрузки делителя 25 частоты в качестве импульса выявления отклонения по уровню. Фазовая ошибка между фронтом нарастания импульса с выхода элемента И 23 и сигналом с .выхода элемента ИЛИ 19 непостоянна, и фронт нарастания импульса отстает от фронта нарастания сигнала выявления уровня на величину задержки, примерно равную в максимальном случае одному периоду эталонных тактовых имПульсов.

На информационные входы предварительной установки D1-D4 делителя 25 частоты (где D1 является младшим, а D4 старшим разрядом) поступает соответствующий уровень, причем на входы D1 и D2 приложено низкоуровневое напряжение . Входы D3 и D4 делителя частоты 25 подключаются соответственно к выходам Q и Q триггера 20. Делитель 25 частоты подсчитывает этапонные тактовые импульсы, поступающие от генератора 24 тактовых импульсов, и вырабатывает на выходах Q1-Q4 подсчи- танный выходной сигнал. Кроме того, на выходе переноса делителя 25 частоты вырабатывается импульс с высоким уровнем, когда подсчитанное значение равняется 15, и с низким уровнем при поступлении шестнадцатого эталонного тактового импульса, т.е. это

импульс, полученный путем частотного деления частоты эталонного тактового импульса на 16 от исходной частоты. Импульс на выходе переноса делителя 25 частоты равен 1/16 от периода битов. )

Когда сигналы на выходах Q, Q

и Q делителя 25 частоты равным соответственно уровню логической 1,

а сигнал на выходе равен уровню логического О, т.е. когда подсчитанное значение равно 11, выходной сигнал с Qj подается элемент И 28 через инвертор 27, тогда как сигналы

Q1 Qi Q+ непосредственно поступают на элемент И 28. Элемент И 28 вырабатывает импульс, форма которого показана на фиг.5. Этот импульс подается на тактовый вход триггера 20 в качестве тактового импульса синхронизации считывания данных. Таким образом, триггер 20 фиксирует сигнал с выхода элемента ИЛИ 19 с помощью фронта нарастания импульса и вырабатывает на выходе Q прямой выходной сигнал, тогда как сигнал с инвертированной фазой вырабатьшается на выходе Q. Показанный на фиг.5 импульс подается с выхода Q триггера 20 на выход 33 устройства в качестве сигнала считывания информации. Сигнал считывания информации имеет сигнальный уровень +1 по отношению к уровням +1 и -1 трехзначного кодово

го сигнала на входе 32 и имеет уровень О по отношению к уровню О трехзначного кодового сигнала и соответственно представляет исходную инфор.мацию.

Счетчик 29 сбрасывается сигналом, полученным с входа 34, и считает эталонные тактовые импульсы на интервале существования сигнала с высоким уровнем на его входе разрешения.Так

как на вход разрешения счетчика 29 подается импульс с периодом, равным 1/16 периода битов, то на выходе 35 счетчик 29 вырабатывает подсчитанную величину. Как и.в случае описанного выше счетчика 13, выходная подсчитанная величина счетчика 29 указывает бит, от которого получается считывание информации на триггере 20, т.е. через сколько битов после синхронизирующего сигнала лежит бит |содержа ций считываемую информацию.

Из сравнения трехзначного кодового информационного сигнала на входе 32, показанного на фиг.5 поз.30.31, и сигнала на выходе элемента ИЛИ 19 показанного на фиг.5, видно, что фронт нарастания сигнала на выходе элемента MJIIi 19 приходится на моменты, когда сигнальньш уровень трехзначного кодового информационного сигнала становится равньм +1 или -1. Когда сигнальньй уровень трехзначного кодового информационного сигнала на битовом периоде, непосредственно предшествующем битовому периоду сигнала считывания информации, полученного с клеммы Q триггера 20, равен О, фронт нарастания сигнала на выходе элемента lilHi 19 выражается резче, чем в случае, когда сигнальный уровень трехзначного кодового сигнала информационного в посредственно предшествующем битовом периоде равен -1 или +1, Так как импульс на выходе элемента И 23 также создается в синхронизме с сигна- лом на выходе элемента 19, то импуль на выходе элемента И 23 создается с различным временным согласованием в зависимости от того, равен ли О или -1 (или +1) сигнальный уровень трехзначного кодового сигнала информационного на непосредственно предшествующем битовом периоде.

Если на делителе 25 частоты всегда предполагается одно и то же значение сброса (заранее установленная информационная величина) и тактовый импульс синхронизации считывания ин- формац1-ш вырабатывается подсчитанным выходным сигналом делителя 25 частоты, то считывание данных триггером 20 не вьтолняется точно по центру периода битов согласно величине бита непосредственно предшествующего данным.

5

Для предотвращения этого явления выходной сигнал с выхода Q триггера 20 подается на информационньш вход предварительной установки D4 делйтеля 25 частоты в предшествующем варианте конструкции. Вместе с тем выходной сигнал с клеммы Q триггера 20 подается на клемму информационного входа предварительной установки D3

О делителя частоты 25. Следовательно, когда уровень сигнала считьшания информации на выходе 33 является низким, входные Уровни на входах D1, D2 и D4 становятся соответственно низкими, тогда как уровень на входе D3 становится высоким. В этом случае в делителе 25 частоты запишется значение 4 при наличии импульса выявления отклонения по уровню на

0 делителе 25 частоты. Когда уровень , .сигнала считывания информации явля- |ется высоким, в делителе 25 частоты запишется величина 8 при условии существования импульса на выходе элемента И 23. Если уровень сигнала считывания информации на выходе 33 окажется низким в тот момент времени, когда генерируется сигнал на выходе элемента И 23, то информация в непосредственно предшествующем бите равна О, а если уровень сигнала считывания информации на выходе 33 является высоким, то информация в непосредственно предшествующем би5 те равна 1 , что видно из

фиг. 5.

I

5

0

Поэтому в данном варианте конструкции, если информация в непосредственно предществуюп ем бите равна С, при сбросе делителя 25 частоты в нем запишется значение 4. Теперь, когда подсчитанная величина достигнет значения 11, тактовый импульс

синхронизации считывания информации с выхода дешифратора 26 будет создан сравнительно задержанным образом, что показано с, помощью точек п1, п4 и п7 на фиг.5. Если информация в

непосредственно предшеству1ош;ем бите равна 1, то при сбросе делителя 25 частоты в нём запишется значение 8. В этом случае, когда подсчитанное значение достигнет величины 11,

тактовый импульс синхронизации считывания информации с выхода дешифратора 26 будет создан несколько опережающим о бразом, что показано на фиг.5 с помощью точки п5.

П

Изображенные на фиг.5 тактовые ипульсы синхронизации считывания информации, помеченные, точками п2, пЗ п6, создаются всякий раз, как делитель 25 частоты насчитывает шестнадцать эталонных тактовых импульсов. Следовательно, в соответствии с изобретением фаза тактового импульса синхронизации считывания информации с вьгхода дешифратора 26 корректируется для каждого фронта нарастания сигнала с выхода элемента ИЛИ 19, благодаря чему предупреждается О1иибочное считывание информации из-за дрожания. Кроме того, согласование во времени, для которого создается тактовый импульс синхронизации считывания информации с вы- хода дешифратора 26, меняется в соответствии с данным в непосредственно предшествующем бите сигнала с выхода элемента. ИЛИ 19. Поэтому данные могут быть считаны точно по центру периода битов этого сигнала. , Однако, во втором варианте кон- струкции по фиг.4, при условии соз- удания фронта нарастания сигнала с тзыкода элемента 19, показанного

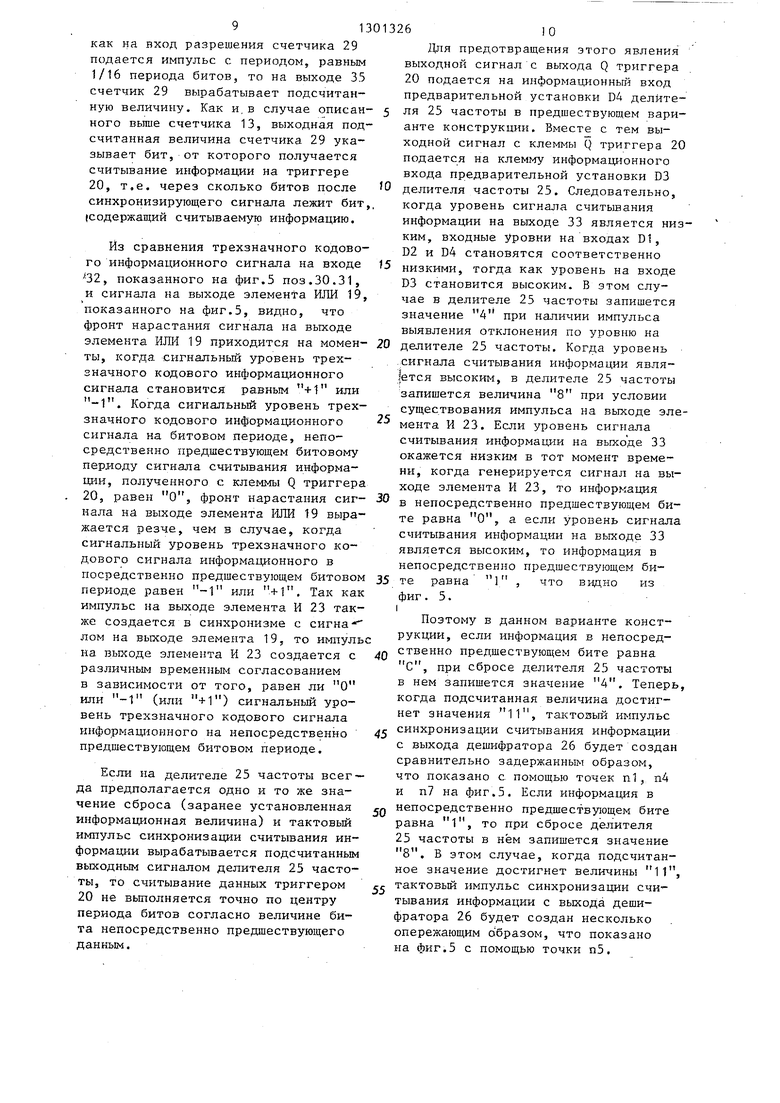

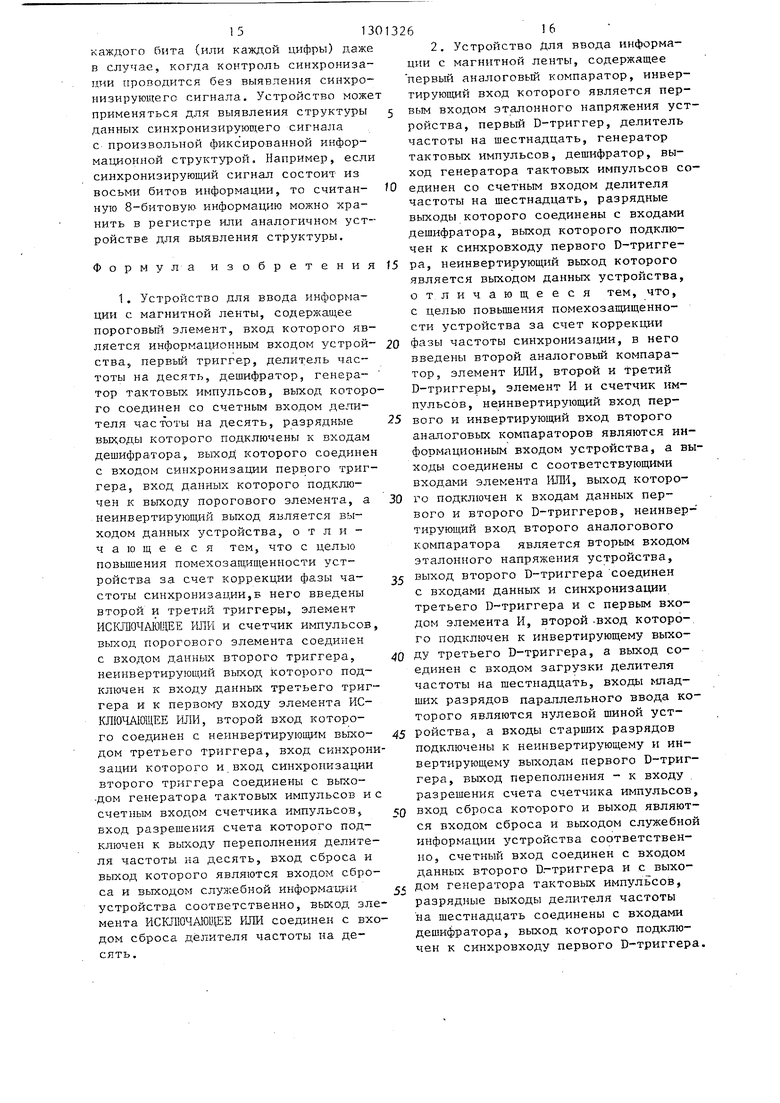

на фиг.55 в момент времени t, , показанный на фиг.9 поз.38 со сдвигом от исходного момента нарастания при синхронизации t на время х вследствие шума, колебаний уровня и других причин в передающем тракте, импульс выявления отклонения на выходе элемента И 23 также создается со сдвигом, что показано импульсом у на фиг.9. Если сброс делителя 2S частоты произойдет от сдвинутого по фазе импульса выявления отклонения по уровню у, то делитель 25 частоты сможет далее генерировать тактовые импульсы синхронизации считывания информации со сдвинутой фазой до тех пор, пока не произойдет правильный сброс делителя 25 частоты.

Кроме того, в втором варианте конструкции в делитель 25 частоты записывается заранее установленная информация с помощью импульса выявления отклонения по уровню с выхода элемента И 23 (т.е. начальная установка) . На интервале времени между двумя моментами начальной установки импульс синхронизации считывания информации с выхода дешифратора 26 может быть создан дважды, т.е. может случиться так, что при создании такO

1326

12

тового импульса синхронизации считывания информации при равенстве подсчитанного значения в делителе 25 частоты 11, что показано на фиг.8 поз.28 с помощью точки п, импульс выявления отклонения по уровню с выхода элемента И 23 будет создан, когда подсчитанное значение в делителе 25 частоты станет равным 12, что показано на фиг.8, и в делителе 25 частоты соответственно запишется значение 8. На фиг.В позиционные обозначения над сигналом указывают на подсчитанное -значение в делителе 25 частоты.

В этом случае делитель 25 частоты начинает считать со значения 8. Подсчитанное значение 11 получается в момент времени до создания последующего импульса выявления отклонения по уровню с вьгхода элемента И 23. Б результате вьфабатывается тактовый импульс синхронизации считывания информации, показанный на фиг.8 как Пц,. т.е. из-за равенства15

0

0

5

0

5

0

5

минимального импульсного интервала импульсов выявления отклонения по уровню одному периоду битов, требуемому для подсчета шестнадцати эталонных тактовых импульсов, в пределах этого импульсного интервала вы- .вабатьшаются два тактовых импульса {синхронизации считывания информации

п, показанные на фиг.8.

6

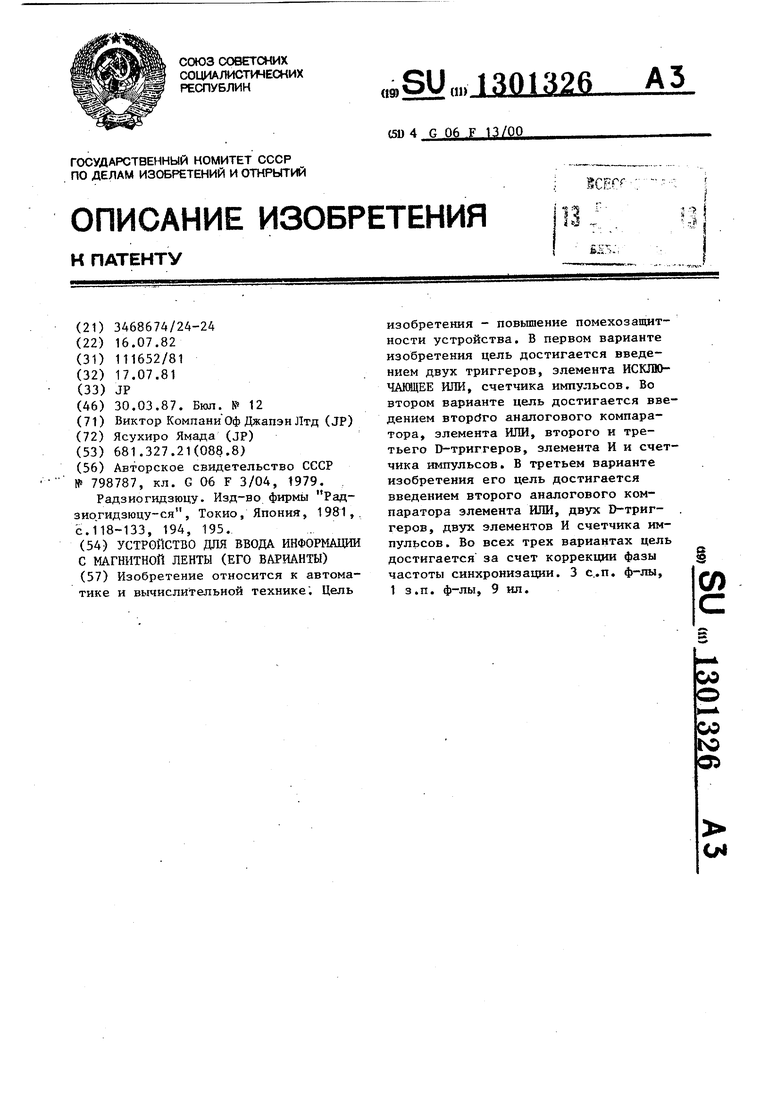

Предупредить возникновение этого явления можно с помощью третьего варианта конструкции устройства, показанного на фиг. 6. В схеме по фиг. 6 на декодер 46 подаются выходные сигналы с входов Q,Q4 делителя 45 частоты. Когда подсчитанное делителем 45 частоты значение равно 11, например, декодер 46 вырабатывает такто- вьй импульс синхронизации считывания информации на выводе Р1, 1тредставлен- ный на фиг.9, и на выходе 61 вьфаба- тывает импульс, показанный на фиг.9 и 8. Из фиг.8 видно, что уровень импульса на выходе 61 является высоким на интервале, в о время которого значение, подсчитанное делителем 25 частоты, может быть равным от 2 до 10. В пределах указанного интервала, когда подсчитанное делителем 25 частоты значение может быть от 2 дс вырабатывается нормальный импульсню.

выявления отклонения по урон-

Импульс с элемент И 43 вместе с

JO

15

20

25

13 1301326

выхода 61 подается на

импульсом выявления отклонения по уровню с выхода элемента И 42, Соответственно сигнал, поступающий на вход загрузки делителя 45 частоты от элемента И 43, изображен на фиг.9. Это означает устранение импульса выявления отклонения по уровню , изображенного на фиг.95 создавшегося с неверной фазой, и к входу загрузки делителя 45 частоты прилагается лишь импульс выявления отклонения по уровню, вы-к- работанный с нормальной фазой. Следовательно, предупреждается рассмотренная выше ошибка. I

Схемное построение декодера 46

изображено на фиг.7, От делителя частоты на 15 (не показан), соответствующего делителю 45 частоты на шестнадцать, подсчитанные выходные сигналы в трех разрядах за исключением младшего разряда соответственно по- даютсй на входы А, В, С счетчика 58. На фиг.7 обозначение н - высокий уровень, а обозначение , - низкий уровень. Когда к всем входам А,В,С счетчика 58 прикладывается напряжение .низкого уровня, то лишь на выходе УО будет напряжение низкого уровня. На других выходах У1-У7 будут напряжения высокого уровня. Если высокий уровень будет только на входе В, ТО низкий уровень напряжения будет получен лишь на выходе У1. В этом случае на других выходах УО и У2-У7 будут высокие уровни напря- i-жения. Аналогичным образом при по- ступлении высоких уровней на входы .А, В и С счетчика 58 низкий уровень напряжения будет получен лишь на выходе У7, на других выходах будет высокий уровень.

Полученный с выхода У1 сигнал поступает на вход 4 триггера 57 через инвертор 55. Кроме того, с выхода У7 выходной сигнал поступает на вход К триггера 57. Поступающий на вход 62

дывается к соответствующим тактовым входам триггеров 56 и 57. Соответственно на выходе Q триггера 57 вырабатывается импульс, показанный на фиг.9 и 8, и этот импульс подается на выход 61, Сигнал с выхода переноса делителя 45 частоты подается на входы I и К триггера 56. На выходе триггера 56 вьфабатывается тактовый

14

импульс синхронизации считывания информации, изображенньй на фиг.9, он подается на выход 60.

Все приведенное описание было выполнено при условии считывания информации в несамотактируемой цифровой сигнальной последовательности. Однако, предлагаемое устройство считывания информации может быть аналогичным образом применено и для само- тактируемых цифровых сигнальных последовательностей типа модифицированного частотно-модулированного сигнала (MFM) или фазокодированного сигнала, полученный путем выполнения модифицированной частотной модуляции или фазового кодирования с незначи- .модификацией. Так, например, при считьгоании информации в сигнале MFM период повторения эталонных тактовых импульсов выбирается равньм 1/20 периода битов сигнала MFM. Кроме того, к выходам 15 (фиг,1) или 52 (фиг.6) добавляется схема декодирования модифицированного частотно-модулированного сигнала.

30

35

40

Кроме того, между несамотактиру- емыми цифрами сигнальными последовательностями и между произвольной кодовой последовательностью типа отдельно вырабатываемого кода из М-по- следовательностей можно получить функцию ИСКЛЮЧАЮЩЕЕ МИ, В этом случае предлагаемое -устройство можно применить к неупорядоченной цифровой сигнальной последовательности, в которой несамотактируемая цифровая сигнальная последовательность разупоря- дочивается с тем, чтобы уменьшить темп поступления непрерывных логических О или 1.

Изобретение не ограничивается применением при передаче на вход уст- г ройства двузначного или трехзначного кода, как было описано в приведенных вариантах конструкции: оно может быть применено для четырехзначных и восьмизначных, кодовых передаэталонный тактовьй импульс прикла- ,гд ющих систем и т,д. Как правило, в

М-значных кодовых передающих системах (М является целым) существует (М-1) видов значений предварительной установки в Делителе частоты от им- гс пульса выявления отклонения по уровню.

Согласно предлагаемому устройству можно получить точный тактовьй импульс синхронизации считывания для

6

14

импульс синхронизации считывания информации, изображенньй на фиг.9, он подается на выход 60.

Все приведенное описание было выполнено при условии считывания информации в несамотактируемой цифровой сигнальной последовательности. Однако, предлагаемое устройство считывания информации может быть аналогичным образом применено и для само- тактируемых цифровых сигнальных последовательностей типа модифицированного частотно-модулированного сигнала (MFM) или фазокодированного сигнала, полученный путем выполнения модифицированной частотной модуляции или фазового кодирования с незначи- .модификацией. Так, например, при считьгоании информации в сигнале MFM период повторения эталонных тактовых импульсов выбирается равньм 1/20 периода битов сигнала MFM. Кроме того, к выходам 15 (фиг,1) или 52 (фиг.6) добавляется схема декодирования модифицированного частотно-модулированного сигнала.

каждого бита (или каждой цифры) даже в случае, когда контроль синхронизации проводится без выявления синхронизирующего сигнала. Устройство може применяться для выявления структуры данных синхронизируюп;его сигнала с произвольной фиксированной информационной структурой. Например, если синхронизирующий сигнал состоит из восьми битов информации, то считан- ную 8-битовую информацию можно хранить в регистре или аналогичном устройстве для выявления структуры.

Формула изобретения

1. Устройство для ввода информации с магнитной ленты, содержащее пороговьш элемент, вход которого является информационньм входом устрой- ства, первый триггер, делитель частоты на десять, дешифратор, генера- тор тактовых импульсов, выход которого соединен со счетным входом делителя частоты на десять, разрядные выходы которого подключены к входам дешифратора, выход которого соединен с входом синхронизации первого триггера, вход данных которого подключен к выходу порогового элемента, а неинвертирующий выход является выходом данных устройства, отличающееся тем, что с целью повышения помехозащищенности устройства за счет коррекции фазы ча- стоты синхронизации,в него введены второй и третий триггеры, элемент ИС1ШОЧА ЬЩЕЕ ИЛИ и счетчик импульсов, выход порогового элемента соединен с входом данных второго триггера, неинвертирующий выход которого подключен к входу данных третьего триггера и к пepвo fy входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с неинвертирующнм выхо- дом третьего триггера, вход синхронизации которого и вход синхронизации второго триггера соединены с выхо- -дом генератора тактовых импульсов и с счетным входом счетчика импульсов, вход разрешения счета которого подключен к выходу переполнения делителя частоты на десять, вход сброса и выход которого являются входом сброса и выходом служебной информации устройства соответственно, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом сброса делителя частоты на десять.

2. Устройство Для ввода информации с магнитной ленты, содержащее первый аналоговый компаратор, инвертирующий вход которого является первым входом эталонного напряжения устройства, первый D-триггер, делитель частоты на шестнадцать, генератор тактовых импульсов, дешифратор, выход генератора тактовых импульсов соединен со счетным входом делителя частоты на шестнадцать, разрядные выходы которого соединены с входами дешифратора, выход которого подключен к синхровходу первого D-тригге- ра, неинвертирующий выход которого является выходом данных устройства, о тличающе е ся тем, что, с целью повьш1ения помехозащищенности устройства за счет коррекции фазы частоты синхронизагщи, в него введены второй аналоговый компаратор, элемент ИЛИ, второй и третий D-триггеры, элемент И и счетчик импульсов, неинвертирующий вход первого и инвертирующий вход второго аналоговых компараторов являются информационным входом устройства, а выходы соединены с соответствующими входами элемента lillli, выход которого подклЕочен к входам данных первого и второго D-триггеров, неинвертирующий вход второго аналогового компаратора является вторым входом эталонного напряжения устройства, выход второго D-триггера соединен с входами данных и синхронизации третьего В триггера и с первым входом элемента И, второй -вход которого подключен к инвертирующему выходу третьего D-триггера, а выход соединен с входом загрузки делителя частоты на шестнадцать, входы maд- ших разрядов параллельного ввода которого являются нулевой шиной устройства, а входы старишх разрядов подключены к неинвертирующему и инвертирующему выходам первого D-триггера, выход переполнения - к входу разрешения счета счетчика импульсов, вход сброса которого и выход являются входом сброса и выходом служебной информации устройства соответственно, счетный вход соединен с входом данных второго D.-триггера и с выходом генератора тактовых импульсов, разрядные выходы делителя частоты на шестнадцать соединены с входами дешифратора, выход которого подключен к синхровходу первого D-триггера

17 1

3,.Устройство для ввода информации с магнитной ленты, содержащее первый аналоговый компаратор, инвертирующий вход которого является первым входом эталонного напряжения уст ройства, первый D-триггер, делитель частоты на шестнадцать, генератор тактовых импульсов, декодер, выход генератора тактовьпс импульсов соединен со счетным входом делителя часто ты на Шестнадцать, разрядные выходы которого соединены с входами декодера, первый выход которого подключен к синхровходу первого В триггера, неинвертирующий выход которого является выходом данных устройства, о т- ли чающееся тем, что, с целью повьпиения помехозащищенности устройства за счет коррекции фазы частоты синхронизации, в него введены второй аналоговый компаратор, элемент ИЛИ, второй и третий D-триггеры элемент И и дополнительный элемент И, счетчик импульсов, неинвертирующий вход первого и инвертирующий вход второго аналоговых компараторов являются информационньм входом устройства, а выходы соединены с соответствующими входами элемента ИЛИ, выход которого подключен к входам данных первого и второго D-триггеров, неинвертирующий вход второго аналогового компаратора является BTopbjM входом эталонного напряжения устройства, выход второго D-тригге- ра соединен с входом данных второго D-триггера и с первым входом элемента И, второй вход которого подклю

5 0 0

18

чей к инвертирующему выходу третьего Dтриггера, выход соединен с первым входом дополнительного элемента И, второй вход которого подключен к второму выходу декодера, а выход - к входу загрузки делителя частоты на шестнадцать, входы младших разрядов параллельного ввоДа которого являются нулевой шиной устройства, а входы старших разрядов подключены к неин- вертирующему и инвертирующему выходам первого D-триггера, выход переполнения - к входу разрешения счета счетчика импульсов и к установочно-

5 му входу декодера, вход сброса и выход счетчика импульсов являются входом -сброса и выходом служебной информации устройства соответственно, а .счетньй вход соединен с входами син- {Хронизации второго и третьего D-триг- еров и с выходом генератора тактовых импульсов, разрядные выходы де- лителя частоты на шестнадцать соединены с разрядными входами декодера, синхровход которого является синхро- входом устройства.

А. Устройство по п.З, отличающееся тем, что декодер содержит счетчик, инвертор и йервый

0 и второй 1К-триггеры, выходы которых являются первыми и вторыми выходами декодера соответственно, син- хровходы - синхровходом декодера, входы счетчика являются разрядными входами декодера, один выход счетчика соединен с 1-входом второго IK- триггера через инвертор, другой выход - с К входом второго 1К-триггера.

5

5

Фие.З

А в с 61G2A62B 58

yOYI У KJ К4 У5 Y6 Y7

60

Фиг. 7

0123156769 Ю 1//1/21в е W 1112 13 Iff 15 О 1 Z

23

2В

61 г

О

YJIR

П

JL.

в

lUL

Л

JL

Фиг.З

Редактор Н.Киштулинец

Составитель И.Алексеев

Техред А.Крарчук Корректор Г.Решетник

Заказ 1164/59Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

П

П

ft

л

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - повышение помехозащит- ности устройства. В первом варианте изобретения цель достигается введением двух триггеров, элемента ИСКПЮ- ЧАНЩЕЕ ИЛИ, счетчика импульсов. Во втором варианте цель достигается введением BTopdro аналогового компаратора, элемента ИЛИ, второго и третьего D-триггеров, элемента И и счетчика импульсов. В третьем варианте изобретения его цель достигается введением второго аналогового компаратора элемента ИЛИ, двух D-триггеров, двух элементов И счетчика импульсов . Во всех трех вариантах цель достигается за счет коррекции фазы частоты синхронизации. 3 с..п. ф-лы, 1 з.п. ф-лы, 9 ил. I О) ы

| Устройство для сопряжения цифровойВычиСлиТЕльНОй МАшиНы C КАССЕТНыММАгНиТОфОНОМ зВуКОзАпиСи | 1979 |

|

SU798787A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Радзиогидзюцу | |||

| Изд-во фирмы Рад- зио.гидзюцу-ся, Токио, Япония, 1981, | |||

| Прибор для массовой выработки лекал | 1921 |

|

SU118A1 |

Авторы

Даты

1987-03-30—Публикация

1982-07-16—Подача