1

Изобретение относится к электросвязи и может быть использовано в системах передачи дискретной информации с решающей обратной связью.

Целью изобретения является повышение достоверности приема дискретной информации и сокращение времени приема дискретной информации по каналам низкого качества.

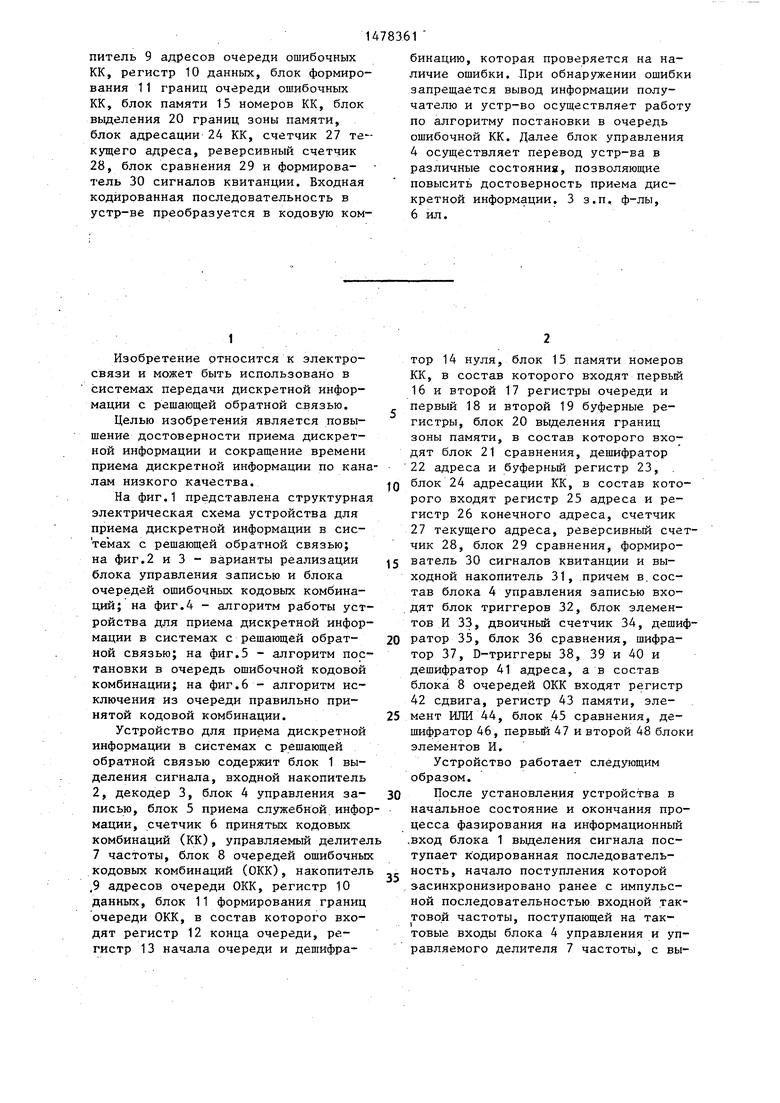

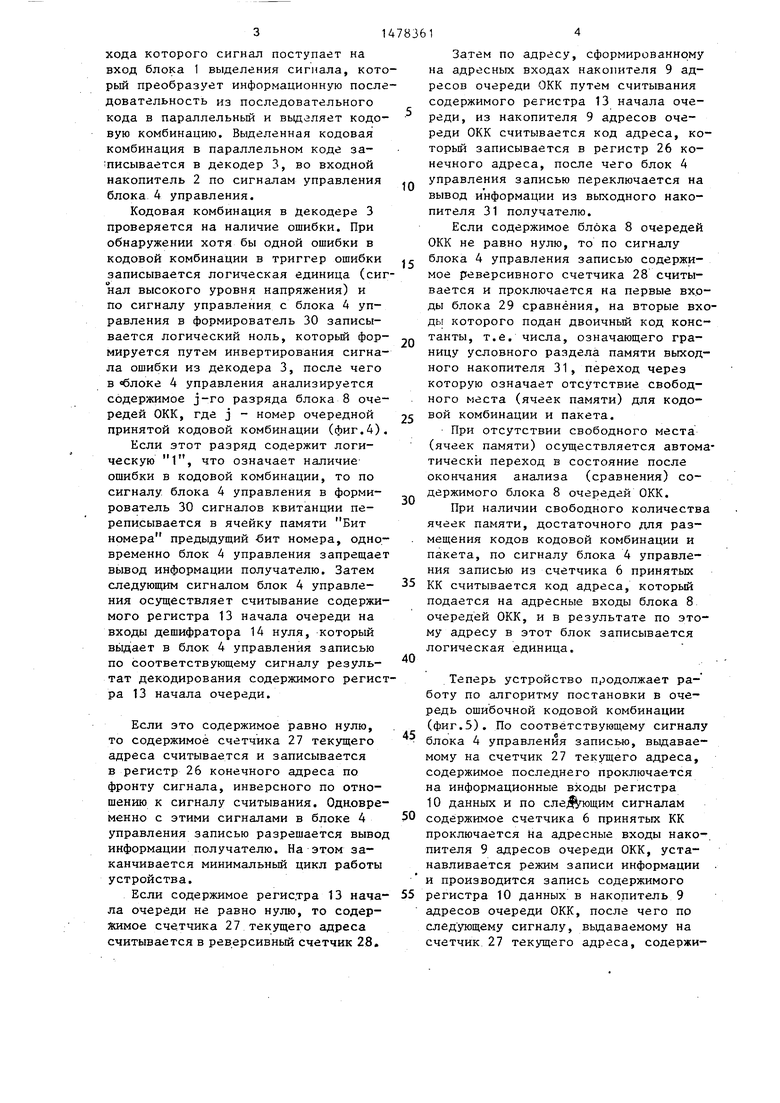

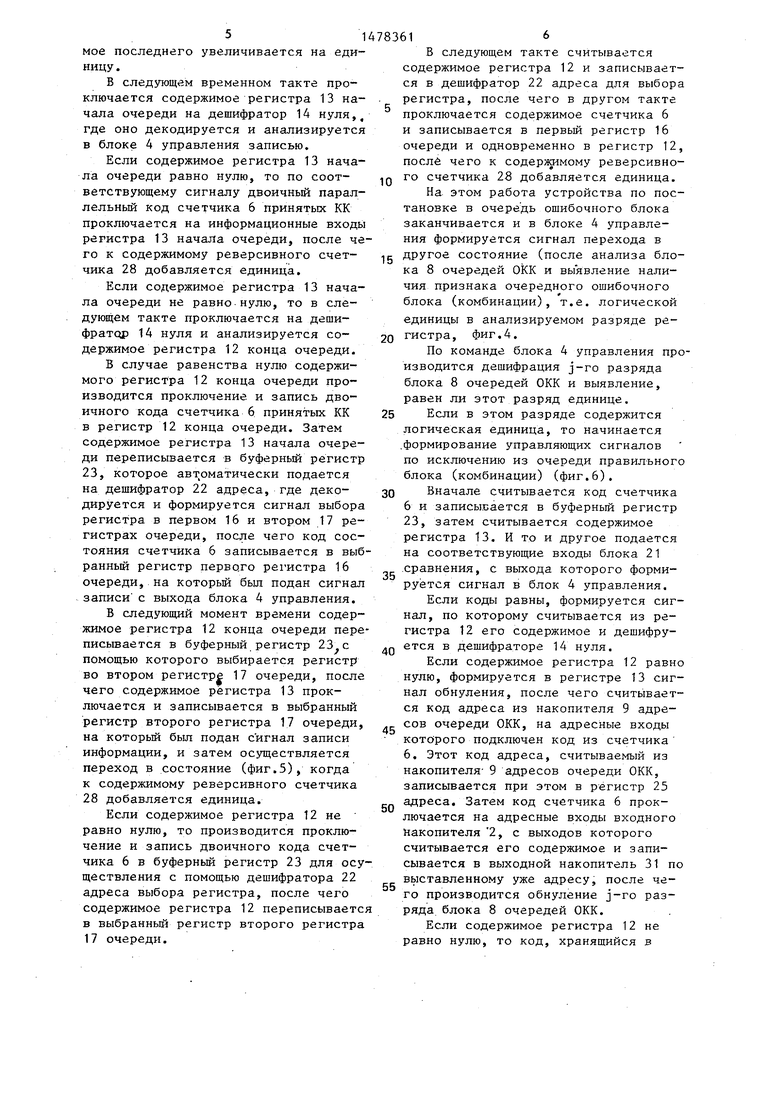

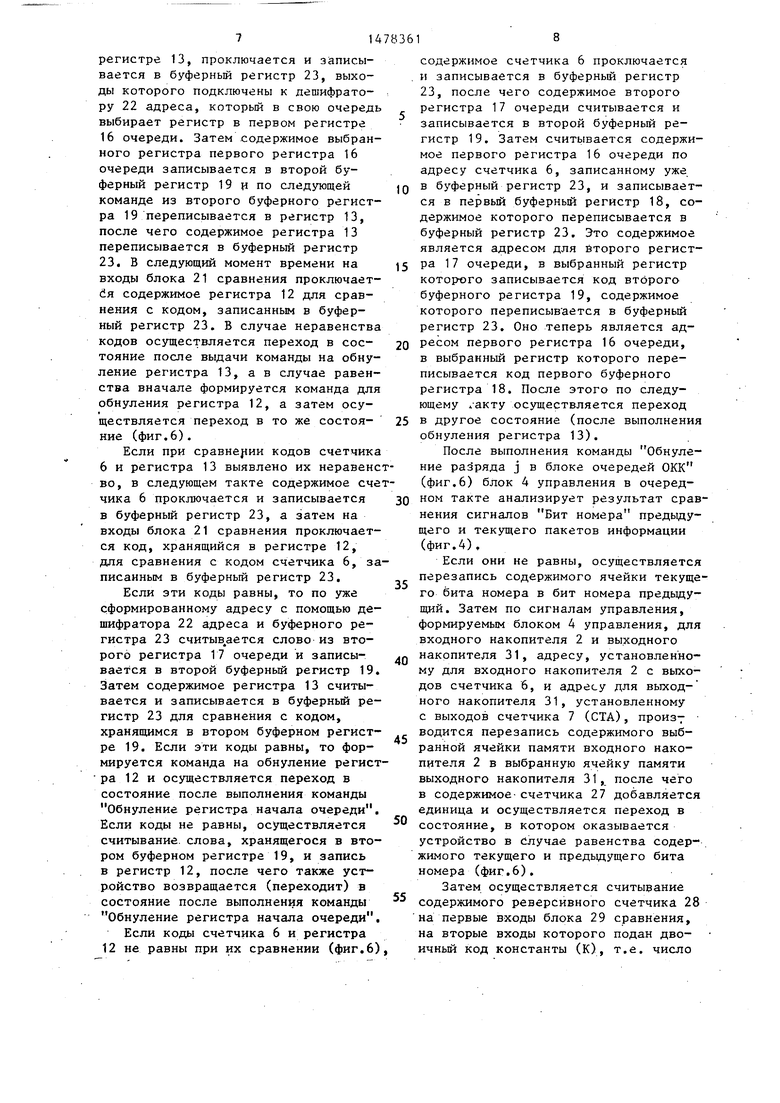

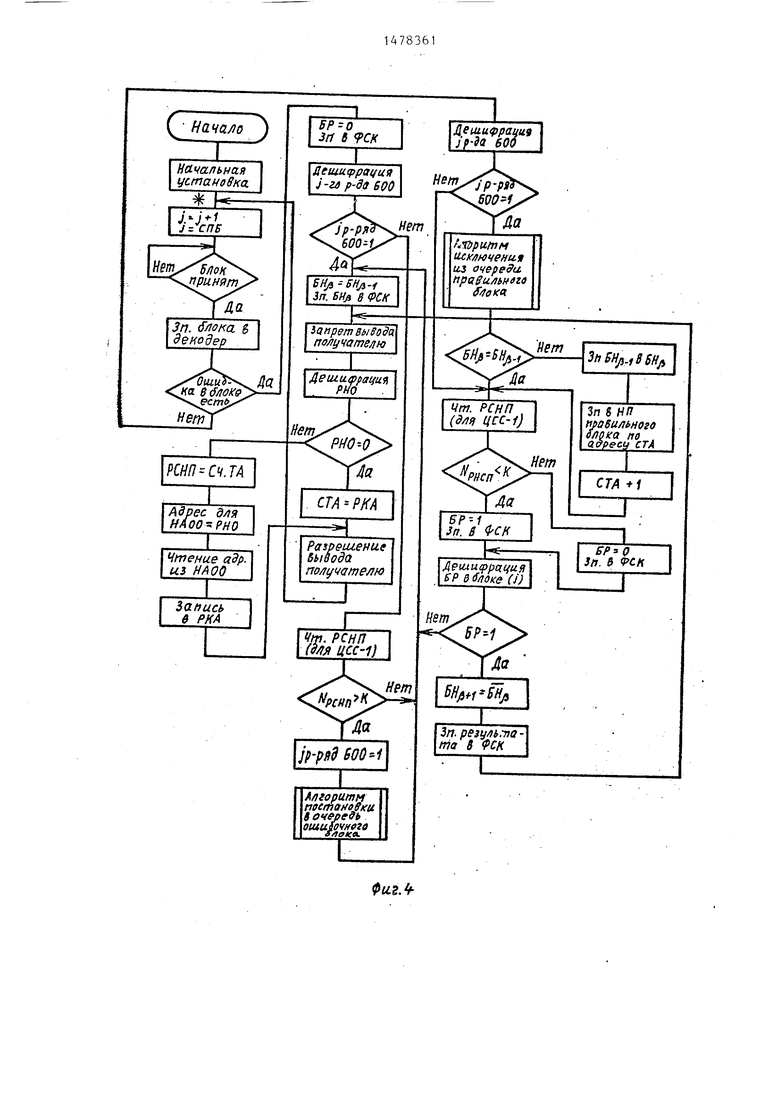

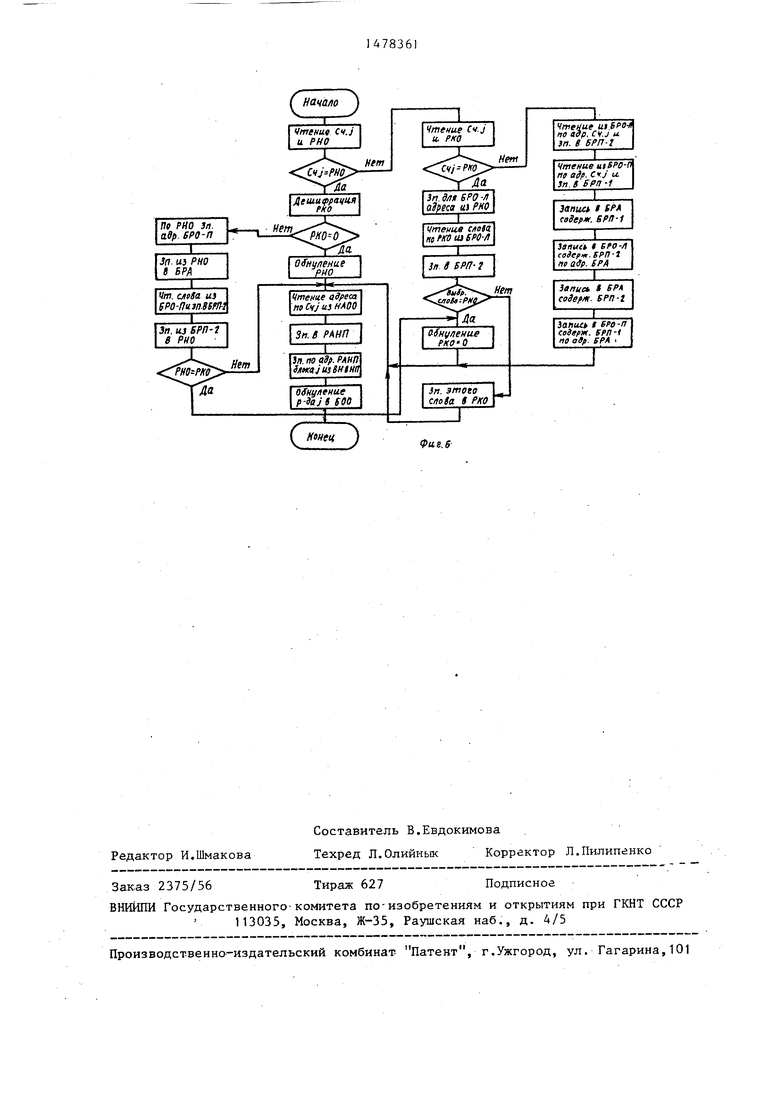

На фиг.1 представлена структурная электрическая схема устройства для приема дискретной информации в системах с решающей обратной связью; на фиг.2 и 3 - варианты реализации блока управления записью и блока очередей ошибочных кодовых комбинаций; на фиг.4 - алгоритм работы устройства для приема дискретной информации в системах с решающей обратной связью; на фиг.5 - алгоритм постановки в очередь ошибочной кодовой комбинации; на фиг.6 - алгоритм исключения из очереди правильно принятой кодовой комбинации.

Устройство для приема дискретной информации в системах с решающей обратной связью содержит блок 1 выделения сигнала, входной накопитель 2, декодер 3, блок 4 управления записью, блок 5 приема служебной информации, счетчик 6 принятых кодовых комбинаций (КК), управляемый делител 7 частоты, блок 8 очередей ошибочных кодовых комбинаций (ОКК), накопитель .9 адресов очереди ОКК, регистр Ю данных, блок 11 формирования границ очереди ОКК, в состав которого входят регистр 12 конца очереди, регистр 13 начала очереди и дешифра

0

5

0

5

0

тор 14 нуля, блок 15 памяти номеров КК, в состав которого входят первый 16 и второй 17 регистры очереди и первый 18 и второй 19 буферные регистры, блок 20 выделения границ зоны памяти, в состав которого входят блок 21 сравнения, дешифратор 22 адреса и буферный регистр 23, блок 24 адресации КК, в состав которого входят регистр 25 адреса и регистр 26 конечного адреса, счетчик 27 текущего адреса, реверсивный счетчик 28, блок 29 сравнения, формирователь 30 сигналов квитанции и выходной накопитель 31, причем в состав блока 4 управления записью входят блок триггеров 32, блок элементов И 33, двоичный счетчик 34, дешифратор 35, блок 36 сравнения, шифратор 37, D-триггеры 38, 39 и 40 и дешифратор 41 адреса, а в состав блока 8 очередей ОКК входят регистр 42 сдвига, регистр 43 памяти, элемент ИЛИ 44, блок 45 сравнения, дешифратор 46, первый 47 и второй 48 блоки элементов И.

Устройство работает следующим образом.

После установления устройства в начальное состояние и окончания процесса фазирования на информационный вход блока 1 выделения сигнала поступает кодированная последовательность, начало поступления которой засинхронизировано ранее с импульсной последовательностью входной тактовой частоты, поступающей на тактовые входы блока 4 управления и управляемого делителя 7 частоты, с выхода которого сигнал поступает на вход блока 1 выделения сигнала, который преобразует информационную последовательность из последовательного кода в параллельный и выделяет кодовую комбинацию. Выделенная кодовая комбинация в параллельном коде записывается в декодер 3, во входной накопитель 2 по сигналам управления блока 4 управления.

Кодовая комбинация в декодере 3 проверяется на наличие ошибки. При обнаружении хотя бы одной ошибки в кодовой комбинации в триггер ошибки записывается логическая единица (сигнал высокого уровня напряжения) и по сигналу управления с блока 4 управления в формирователь 30 записывается логический ноль, который формируется путем инвертирования сигнала ошибки из декодера 3, после чего в «блоке 4 управления анализируется содержимое j-го разряда блока 8 очередей ОКК, где j - номер очередной принятой кодовой комбинации (фиг.4).

Если этот разряд содержит логическую 1, что означает наличие ошибки в кодовой комбинации, то по сигналу блока 4 управления в формирователь 30 сигналов квитанции переписывается в ячейку памяти Бит номера предыдущий -бит номера, одновременно блок 4 управления запрещает вывод информации получателю. Затем следующим сигналом блок 4 управления осуществляет считывание содержимого регистра 13 начала очереди на входы дешифратора 14 нуля, который выдает в блок 4 управления записью по соответствующему сигналу результат декодирования содержимого регистра 13 начала очереди.

Если это содержимое равно нулю, то содержимое счетчика 27 текущего адреса считывается и записывается в регистр 26 конечного адреса по фронту сигнала, инверсного по отношению к сигналу считывания. Одновременно с этими сигналами в блоке 4 управления записью разрешается вывод информации получателю. На этом заканчивается минимальный цикл работы устройства.

Если содержимое регистра 13 начала очереди не равно нулю, то содержимое счетчика 27 текущего адреса считывается в реверсивный счетчик 28.

10

783614

Затем по адресу, сформированному на адресных входах накопителя 9 адресов очереди ОКК путем считывания содержимого регистра 13 начала очереди, из накопителя 9 адресов очереди ОКК считывается код адреса, который записывается в регистр 26 конечного адреса, после чего блок 4 управления записью переключается на вывод информации из выходного накопителя 31 получателю.

Если содержимое блока 8 очередей ОКК не равно нулю, то по сигналу блока 4 управления записью содержимое реверсивного счетчика 28 считывается и проключается на первые входы блока 29 сравнения, на вторые входы которого подан двоичный код константы, т.е. числа, означающего границу условного раздела памяти выходного накопителя 31, переход через которую означает отсутствие свободного места (ячеек памяти) для кодовой комбинации и пакета.

При отсутствии свободного места (ячеек памяти) осуществляется автома- тически переход в состояние после окончания анализа (сравнения) содержимого блока 8 очередей ОКК.

При наличии свободного количества

15

20

25

30

ячеек памяти, достаточного для размещения кодов кодовой комбинации и пакета, по сигналу блока 4 управления записью из счетчика 6 принятых 5 КК считывается код адреса, который подается на адресные входы блока 8 очередей ОКК, и в результате по этому адресу в этот блок записывается

логическая единица. 0

Теперь устройство продолжает ра- боту по алгоритму постановки в очередь ошибочной кодовой комбинации (фиг.5). По соответствующему сигналу блока 4 управления записью, выдаваемому на счетчик 27 текущего адреса, содержимое последнего проключается на информационные входы регистра 10 данных и по сле гющим сигналам содержимое счетчика 6 принятых КК проключается на адресные входы накопителя 9 адресов очереди ОКК, устанавливается режим записи информации и производится запись содержимого 5 регистра 10 данных в накопитель 9 адресов очереди ОКК, после чего по следующему сигналу, выдаваемому на счетчик 27 текущего адреса, содержи5

0

мое последнего увеличивается на единицу .

В следующем временном такте про- ключается содержимое регистра 13 начала очереди на дешифратор 14 нуля,, где оно декодируется и анализируется в блоке 4 управления записью.

Если содержимое регистра 13 начала очереди равно нулю, то по соответствующему сигналу двоичный параллельный код счетчика 6 принятых КК проключается на информационные входы регистра 13 начала очереди, после чего к содержимому реверсивного счетчика 28 добавляется единица.

Если содержимое регистра 13 начала очереди не равно нулю, то в следующем такте проключается на дешифратор 14 нуля и анализируется содержимое регистра 12 конца очереди.

В случае равенства нулю содержимого регистра 12 конца очереди производится проключение и запись двоичного кода счетчика 6 принятых КК в регистр 12 конца очереди. Затем содержимое регистра 13 начала очереди переписывается в буферный регистр 23, которое автоматически подается на дешифратор 22 адреса, где декодируется и формируется сигнал выбора регистра в первом 16 и втором 17 регистрах очереди, после чего код состояния счетчика 6 записывается в выбранный регистр первого регистра 16 очереди, на который был подан сигнал записи с выхода блока 4 управления.

В следующий момент времени содержимое регистра 12 конца очереди переписывается в буферный регистр 23 с помощью которого выбирается регистр во втором регистре 17 очереди, после чего содержимое регистра 13 проключается и записывается в выбранный регистр второго регистра 17 очереди, на который был подан сигнал записи информации, и затем осуществляется переход в состояние (фиг.5), когда к содержимому реверсивного счетчика 28 добавляется единица.

Если содержимое регистра 12 не равно нулю, то производится проключение и запись двоичного кода счетчика 6 в буферный регистр 23 для осуществления с помощью дешифратора 22 адреса выбора регистра, после чего содержимое регистра 12 переписываетс в выбранный регистр второго регистра 17 очереди.

5

0

5

0

5

0

5

0

5

В следующем такте считывается содержимое регистра 12 и записывается в дешифратор 22 адреса для выбора регистра, после чего в другом такте проключается содержимое счетчика 6 и записывается в первьй регистр 16 очереди и одновременно в регистр 12, после чего к содержимому реверсивного счетчика 28 добавляется единица.

На этом работа устройства по постановке в очередь ошибочного блока заканчивается и в блоке 4 управления формируется сигнал перехода в другое состояние (после анализа блока 8 очередей ОКК и выявление наличия признака очередного ошибочного блока (комбинации), т.е. логической единицы в анализируемом разряде регистра, фиг.4.

По команде блока 4 управления производится дешифрация j-ro разряда блока 8 очередей ОКК и выявление, равен ли этот разряд единице.

Если в этом разряде содержится логическая единица, то начинается формирование управляющих сигналов по исключению из очереди правильного блока (комбинации) (фиг.6).

Вначале считывается код счетчика 6 и записывается в буферный регистр 23, затем считывается содержимое регистра 13. И то и другое подается на соответствующие входы блока 21 сравнения, с выхода которого формируется сигнал в блок 4 управления.

Если коды равны, формируется сигнал, по которому считывается из регистра 12 его содержимое и дешифруется в дешифраторе 14 нуля.

Если содержимое регистра 12 равно нулю, формируется в регистре 13 сигнал обнуления, после чего считывается код адреса из накопителя 9 адресов очереди ОКК, на адресные входы которого подключен код из счетчика 6. Этот код адреса, считываемый из накопителя 9 адресов очереди ОКК, записывается при этом в регистр 25 адреса. Затем код счетчика 6 проключается на адресные входы входного накопителя 2, с выходов которого считывается его содержимое и записывается в выходной накопитель 31 по выставленному уже адресу, после чего производится обнуление j-ro разряда блока 8 очередей ОКК.

Если содержимое регистра 12 не равно нулю, то код, хранящийся в

714

регистре 13, проключается и записывается в буферный регистр 23, выходы которого подключены к дешифратору 22 адреса, который в свою очередь выбирает регистр в первом регистре 16 очереди. Затем содержимое выбранного регистра первого регистра 16 очереди записывается в второй буферный регистр 19 и по следующей команде из второго буферного регистра 19 переписывается в регистр 13, после чего содержимое регистра 13 переписывается в буферный регистр 23. В следующий момент времени на входы блока 21 сравнения проключает- 1я содержимое регистра 12 для сравнения с кодом, записанным в буферный регистр 23. В случае неравенства кодов осуществляется переход в состояние после выдачи команды на обнуление регистра 13, а в случае равенства вначале формируется команда для обнуления регистра 12, а затем осуществляется переход в то же состояние (фиг.6).

Если при сравнении кодов счетчика 6 и регистра 13 выявлено их неравенсво, в следующем такте содержимое счечика 6 проключается и записывается в буферный регистр 23, а затем на входы блока 21 сравнения проключается код, хранящийся в регистре 12, для сравнения с кодом счетчика 6, записанным в буферный регистр 23.

Если эти коды равны, то по уже сформированному адресу с помощью дешифратора 22 адреса и буферного регистра 23 считывается слово из второго регистра 17 очереди и записывается в второй буферный регистр 19. Затем содержимое регистра 13 считывается и записывается в буферный регистр 23 для сравнения с кодом, хранящимся в втором буферном регистре 19. Если эти коды равны, то формируется команда на обнуление регист ра 12 и осуществляется переход в состояние после выполнения команды Обнуление регистра начала очереди. Если коды не равны, осуществляется считывание слова, хранящегося в втором буферном регистре 19, и запись в регистр 12, после чего также устройство возвращается (переходит) в состояние после выполнения команды Обнуление регистра начала очереди.

Если коды счетчика 6 и регистра 12 не равны при их сравнении (фиг.6)

10

15

20

25

361

30

5

0

5

0

5

8

содержимое счетчика 6 проключается и записывается в буферный регистр 23, после чего содержимое второго регистра 17 очереди считывается и записывается в второй буферный регистр 19. Затем считывается содержимое первого регистра 16 очереди по адресу счетчика 6, записанному уже в буферный регистр 23, и записывается в первый буферный регистр 18, содержимое которого переписывается в буферный регистр 23. Это содержимое является адресом для второго регистра 17 очереди, в выбранный регистр которого записывается код второго буферного регистра 19, содержимое которого переписывается в буферный регистр 23. Оно теперь является адресом первого регистра 16 очереди, в выбранный регистр которого переписывается код первого буферного регистра 18. После этого по следующему акту осуществляется переход в другое состояние (после выполнения обнуления регистра 13).

После выполнения команды Обнуление разряда j в блоке очередей ОКК (фиг.6) блок 4 управления в очередном такте анализирует результат сравнения сигналов Бит номера предыдущего и текущего пакетов информации (фиг.4),

Если они не равны, осуществляется перезапись содержимого ячейки текущего бита номера в бит номера предыдущий. Затем по сигналам управления, формируемым блоком 4 управления, для входного накопителя 2 и выходного накопителя 31, адресу, установленному для входного накопителя 2 с выходов счетчика 6, и адресу для выход- ного накопителя 31, установленному с выходов счетчика 7 (СТА), произ7 водится перезапись содержимого выбранной ячейки памяти входного накопителя 2 в выбранную ячейку памяти выходного накопителя 31, после чего в содержимое счетчика 27 добавляется единица и осуществляется переход в состояние, в котором оказывается устройство в Случае равенства содержимого текущего и предыдущего бита номера (фиг.6).

Затем осуществляется считывание содержимого реверсивного счетчика 28 на первые входы блока 29 сравнения, на вторые входы которого подан двоичный код константы (К), т.е. число

9147

для выявления наличия свободного места (ячеек памяти) для размещения очередного пакета информации в входном накопителе 2. Если содержимое реверсивного счетчика 28 меньше коне танты, то в формирователь 30 записывается единица в ячейку Бит решения, а если больше, то записывается ноль. Затем анализируется содержимое ячейки Бит решения, хранящееся в блоке 5 приема.

Если бит решения не равен единице осуществляется переход (фиг.6) в состояние после выявления равенства единице j-ro разряда блока 8 очереди ОКК. Если бит решения равен единице, в формирователь 30 записывается инверсное значение содержимого ячейки памяти бита номера, храняще- гося в блоке 5 приема, после чего осуществляется переход в состояние после выполнения команды записи содержимого ячейки предыдущего бита номера в текущий бит номера.

Формула изобретения

1. Устройство для приема дискретной информации в системах с решаю- щей обратной связью, содержащее блок выделения сигнала, первый выход которого подключен к счетному входу счетчика принятых кодовых комбинаций (КК) , а другие выходы блока выделения сигнала подключены к соответс- твующим информационным входам входного накопителя и декодера, первый выход которого подключен к первому входу блока управления записью и к первому входу блока приема служебной информации, к второму и третьему входам которого подключены соответствующие выходы декодера, выходы сигнало управления блока управления записью подключены соответственно к первому и второму входам выходного накопителя, выходы которого и выходы формирователя сигналов квитанции являются соответственно выходами информационных и служебных сигналов устройства, входом которого является информационный вход блока выделения сигнала, отличающееся тем, что, с целью повышения достоверности приема дискретной информации и сокращения времени приема дискретной информации по каналам низкого качества, введены управляемый делитель частоты, блок

l

- Q 5

n 5 0 5

0

5

10

очередей ошибочных кодовых комбинаций (ОКК), накопитель адресов очереди ОКК, регистр данных, блок формирования границ очереди ОКК, блок памяти номеров КК, блок сравнения, блок выделения границ зоны памяти, реверсивный счетчик, блок адресации КК и счетчик текущего адреса, при этом к второму входу блока управления записью подключен первый выход блока приема служебной информации, второй выход которого соединен с первым входом блока очередей ОКК, третий вход блока управления записью объединен с первым входом управляемого делителя частоты и является тактовым входом устройства, управляющими входами которого являются другие входы управляемого делителя частоты, выход которого подключен к соответствующему входу блока выделения сигнала, к другим входам блока управления записью подключены соответственно выход блока очередей ОКК, выход блока формирования границ очереди ОКК, выход блока сравнения, выход блока выделения границ зоны памяти, первый вход реверсивного счетчика, объединенный с третьим входом выходного накопителя, который является входом сигнала считывания устройства, и третий выход блока приема служебной информации, выходы сигналов управления блока управления записью подключены соответственно к второму входу счетчика принятых КК, к первому и второму входам входного накопителя, к второму входу декодера, к дополнительному входу блока приема служебной информации, к соответствующим входам блока очередей ОКК, к соответствующим входам блока формирования границ очереди ОКК, к соответствующим входам накопителя адресов очереди ОКК, к первому входу регистра данных, к соответствующим входам блока памяти номеров КК, к первому входу блока выделения границ зоны памяти, к соответствующим входам блока адресации КК, к соответствующим входам реверсивного счетчика, к соответствующим входам счетчика текущего адреса и к соответствующим входам формирователя сигналов квитанции, выходы счетчика принятых КК подключены к соответствующим входам блока-очередей ОКК, входного накопителя, блока управления записью, блока выделения границ зоны памяти, на- .копителя адресов очереди ОКК, блока памяти номеров КК, к соответствующим входам и выходам блока формирования границ очереди ОКК и к соответствующим входам и выходам блока памяти номеров КК, четвертый выход блока приема служебной информации соединен с соответствующим входом формирова- теля сигналов квитанции, выходы входного накопителя подключены соответственно к первым выходам счетчика текущего адреса, к четвертым входам выходного накопителя и к вторым вхо- дам регистра данных, выходы которого подключены к соответствующим входам накопителя адресов очереди ОКК, выходы которого подключены к соответс твующим входам и выходам блока адре- сации КК, к соответствующим входам и выходам реверсивного счетчика, к вторым выходам счетчика текущего адреса, к соответствующим входам выходного накопителя и к первым вхо- дам блока сравнения, вторые входы которого являются входами констант устройства, выходы блока выделения границ зоны памяти подключены к соответствующим входам блока памяти номеров КК, причем выходы блока управления записью являются выходами сигналов разрешения.

2. Устройство по п.отличающееся тем, что блок очередей ОКК содержит последовательно соединенные регистр сдвига, регистр памяти, первый блок элементов И, элемент ИЛИ и блок сравнения, а также последовательно соединенные дешифратор и второй блок элементов И, выходы которого подключены к соответствующим входам регистра памяти,

$ 0 5 0

5

0

причем выходы дешифратора подключены к другим входам первого блока элементов И, другой вход блока сравнения объединен с информационным входом регистра сдвига и является первым входом блока очередей ОКК, а выход блока сравнения является выходом блока очередей ОКК, вход синхронизации регистра сдвига является вторым входом блока очередей ОКК, а вход синхронизации регистра памяти - третьим входом блока очередей ОКК, четвертым входом которого являются вторые объединенные входы второго блока элементов И, а входы дешифратора являются пятыми входами блока очередей ОКК.

3.Устройство по п.1, отличающее ся тем, что блок формирования границ очереди ОКК содержит регистр начала очереди и регистр конца очереди, выходы которых подключены к соответствующим входам дешифратора нуля, причем входы и выходы регистров начала и конца очереди и . выход дешифратора нуля являются соответственно входами и выходами блока формирования границ очереди ОКК.

4.Устройство по п.1, отличающее ся тем, что блок выделения границ зоны памяти содержит объединенные по входу блок сравнения и буферный регистр, выход которого подключен к объединенным входам дешифратора адреса и блока сравнения, причем первые входы блока сравнения и буферного регистра и выходы дешифратора адреса и блока сравнения являются соответствующими входами

и выходами блока выделения границ зоны памяти.

Шиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания тестовых воздействий | 1988 |

|

SU1541614A1 |

| Устройство для коррекции ошибок внешней памяти | 1989 |

|

SU1662011A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Устройство для исправления искажений в системах передачи дискретной информации | 1987 |

|

SU1603532A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1991 |

|

SU1807516A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для имитации информационных каналов | 1986 |

|

SU1386996A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU883976A2 |

Изобретение относится к электросвязи. Цель изобретения - повышение достоверности приема дискретной информации и сокращение времени приема дискретной информации по каналам низкого качества. Устройство содержит блок выделения 1 сигнала, входной и выходной накопители 2 и 31, декодер 3, блок управления 4 записью, блок приема 5 служебной информации, счетчик 6 принятых кодовых комбинаций (КК), управляемый делитель 7 частоты, блок очередей 8 ошибочных КК, накопитель 9 адресов очереди ошибочных КК, регистр 10 данных, блок формирования 11 границ очереди ошибочных КК, блок памяти 15 номеров КК, блок выделения 20 границ зоны памяти, блок адресации 24 КК, счетчик 27 текущего адреса, реверсивный счетчик 28, блок сравнения 29 и формирователь 30 сигналов квитанции. Входная кодированная последовательность в устройстве преобразуется в кодовую комбинацию, которая проверяется на наличие ошибки. При обнаружении ошибки запрещается вывод информации получателю и устройство осуществляет работу по алгоритму постановки в очередь ошибочной КК. Далее блок управления 4 осуществляет перевод устройства в различные состояния, позволяющие повысить достоверность приема дискретной информации. 3 з.п. ф-лы, 6 ил.

Фиг.з

Фиг.4

«e

a Is

Ч

I

«

| Устройство для передачи и приемадиСКРЕТНОй иНфОРМАции C КОРРЕКциЕйОшибОК | 1979 |

|

SU809615A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-05-07—Публикация

1986-02-06—Подача