Изобретение относится к электротехнике, а именно к устройствам автоматического управления статическим тиристорным компенсатором.

Цель изобретения - повышение качества компенсации колебаний напряжения сети от изменения тока нагрузки.

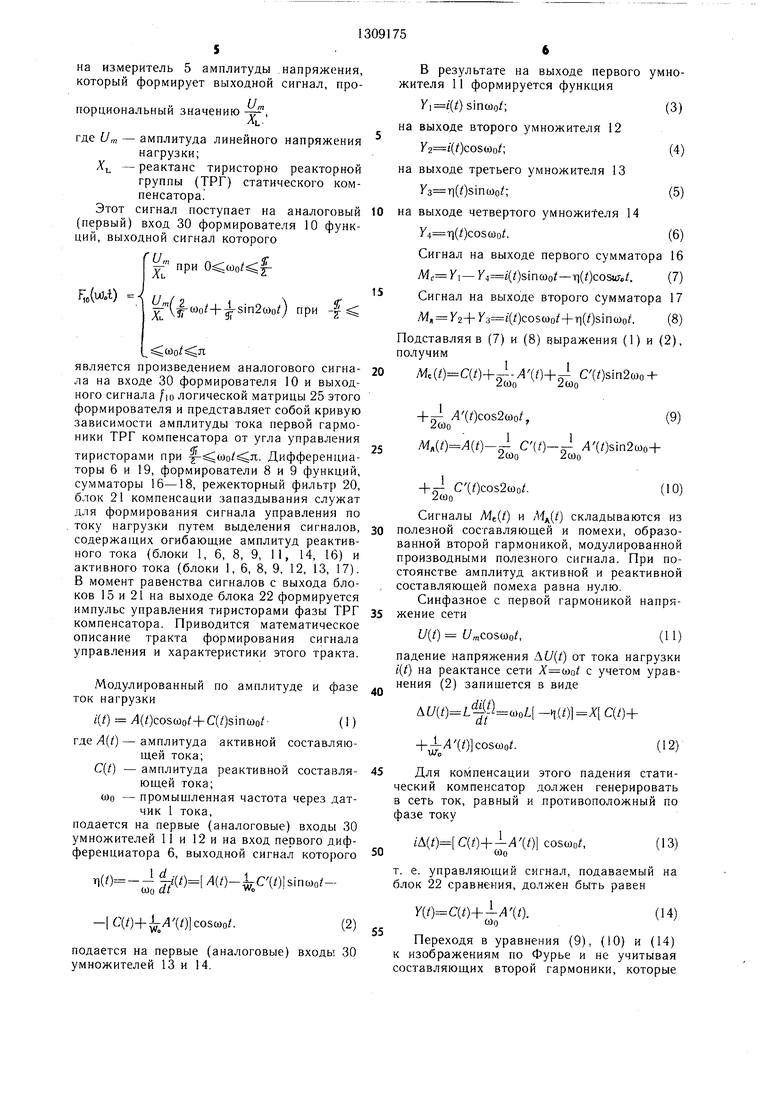

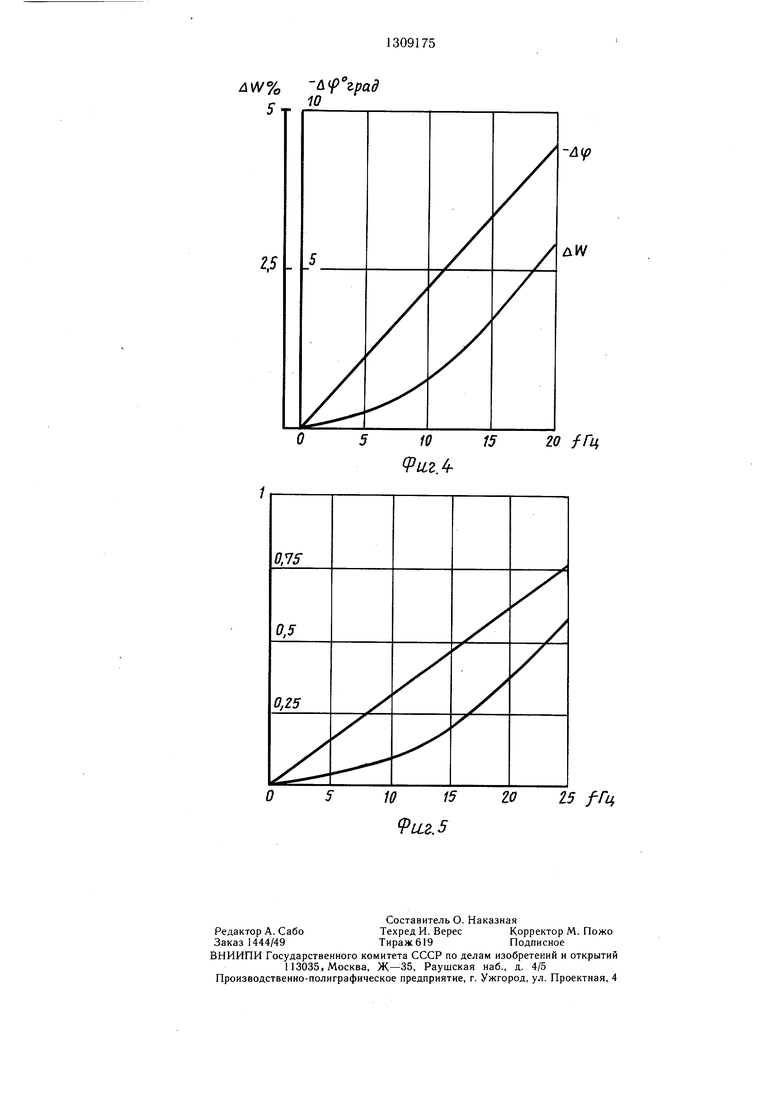

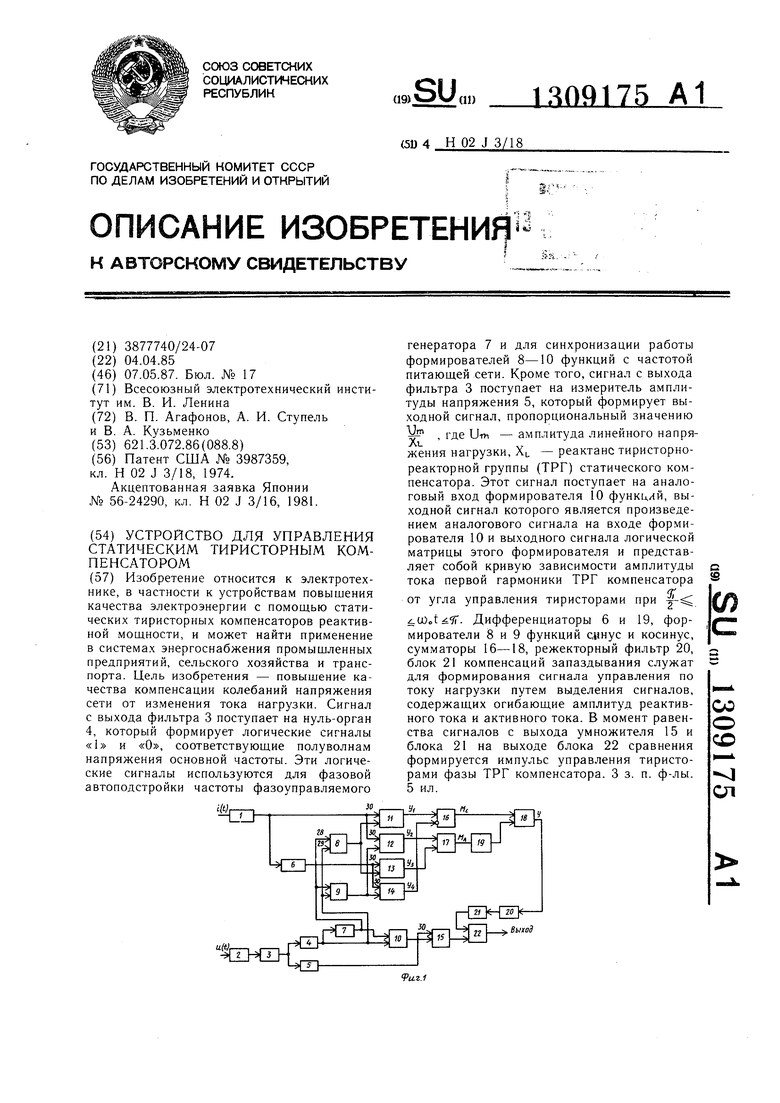

На фиг. 1 приведена блок-схема одной фазы устройства; на фиг. 2 - функциональная схема узла устройства, содержащая один из формирователей функций и умно- житель; на фиг. 3 - значение модуля частотной характеристики канала измерения управляющего сигнала в облас т и частоты 100 Гц; на фиг. 4 - амплитудная и фазовая погрешности канала измерения управляю- щего сигнала в области рабочих частот; на. фиг. 5 - кривые погрешности компенсации колебаний мощности нагрузки в двух случаях: со звеном компенсации запаздывания (блк) и без этого звена (бл).

Устройство (фиг. 1) содержит датчик 1 тока, датчик 2 напряжения, подключенный к его выходу полосовой фильтр 3, подключенные к выходу фильтра 3 нуль-орган 4 и измеритель 5 амплитуды напряжения, блок 6 сдвига фазы, причем вход блока 6 подключен к выходу датчика 1 тока, фазе- управляемый генератор 7, подключенный входом к выходу нуль-органа 4, формирователи 8-10 функций, счетные входы которых подключены к выходу фазоуправляемо- го генератора 7, а их входы установки под- ключены к выходу нуль-органа 4, умножители 11 -15, причем первые входы умножителей 11 и 12 подключены к выходу датчика 1 тока, первые входы умножителей 13 и 14 подключены к выходу блока 6 сдвига фазы, первый вход умножителя 10 подклю- чен к выходу измерителя 5 амплитуды напряжения, вторые входы умножителей 11 и 13 подключены к выходу формирователя 8 функции синус, вторые входы умножителей 12 и 14 подключены к выходу формирователя 9 функций косинус, второй вход умно- жителя 15 подключен к выходу формирователя 10 опорной функции /(а), сумматоры 16-18, причем первый вход сумматора 16 подключен к выходу умножителя 11, а его второй вход подключен к выходу умножителя 14, первый вход сумматора 17 подклю- чены к выходу умножителя 12, а второй его вход подключен к выходу умножителя 13, выход сумматора 16 соединен с первым входом сумматора 18, выход сумматора 17 соединен через последовательно включенный блок 19 сдвига фазы с вторым входом сум- матора 18, выход которого соединен через последовательно включенные режекторный фильтр 20 и блок 21 компенсации запаздывания с первым входом блока 22 сравнения, второй вход которого соединен с выходом умножителя 15.

Датчик 1 тока, датчик 2 напряжения, полосовой фильтр 3, нуль-орган 4, блок 6

сдвига фазы (дифференциатор), сумматоры 16-18 и блок 22 сравнения (компаратор) представляют собой известные устройства на операционных усилителях: датчик 1 тока преобразует ток трансформатора фидера нагрузки в напряжение 5-10 В, датчик 2 напряжения преобразовывает напряжение трансформатора напряжения в уровень 5- 10 В, полосовой фильтр 3 выделяет из входного сигнала напряжения составляющую основной частоты 50 Гц, нуль-орган 4 и компаратор 22 сравнивают величину входного аналогового сигнала с нулем или заданным значением, дифференциатор 6 и сумматоры 16-18 осуществляют математические операции дифференцирования и суммирования соответственно.

В качестве измерителя 5 амплитуды напряжения может быть использовано любое устройство для измерения амплитуды аналогового сигнала.

Режекторный фильтр 20 служит для подавления составляющих основного сигнала в области частот 100±20 Гц. Фильтр 20 имеет передаточную характеристику вида

ff,-(

LTz- j.2

r+ 2lrTw - WT:l

где:со - текущая частота; 0,2,

т| 0,00163 с;

Т2 0,00151 с;

TI - соответствует нулю числителя при 95 Гц;

Т2 - соответствует нулю числителя при 105 Гц.

Амплитудно-частотная характеристика канала измерения с режекторньш фильтром в области частоты 100 Гц приведена на фиг. 3.

Блок 21 компенсации запаздывания является форсирующим звеном, предсказывающим в момент / значение сигнала, соответствующее моменту (/-j-Tj), где т - суммарное запаздывание тракта измерения плюс и собственное запаздывание тиристор- но-реакторной группы (ТРГ) компенсатора. Передаточная характеристика блока 16 имеет вид

IV/ / 11/Ш-Ti

(.-}(

гдет,т,;т2..;т,Ь

Аппаратная реализация фильтров 3 и 21, дифференциатора 19, блока 21 компенсации запаздывания осуществляется по их передаточным характеристикам при помощи операционных усилителей с обратными связями.

На фиг. 2 приведен пример реализации цифроаналогового узла, выполняющего oneрацию формирования функции и умножения. По этой схеме могут быть выполнены пары блоков 8-11, 8-13, 9-12, 9-14, 9-15. Каждый узел состоит из схемы 23 выделения фронта, двоичного восьмиразрядного счетчика 24, программируемой логической матрицы 25 на 4096 бит, восьмиразрядного циф- роаналогового преобразователя 26, выходного операционного усилителя 27, соединенных следующим образом: вход 28 высокой частоты соединен со счетным входом С счетчика 24 и адресным входом АО логической матрицы 25, выходы Y, 2, ..., YS счетчика 24 соединены в соответствии с индексами с входами А, АЧ, ..., Ае, матрицы 25, выходы FO, Р, ..., f, которой соединены в соответствии с индексами с цифровыми входами Хо, Х, ..., Xi цифроаналогового преобразователя 26, выход /С которого соединен с выходом операционного усилителя 27, выход m - с инверсным входом, а выход п - с прямым входом этого усилителя, вход 29 основной частоты соединен с входом схемы 23 выделения фронта, выход которой соединен с / -входом установки счетчика 24, аналоговые входы б о(ЗО) цифроаналоговых преобразователей 26 соединены с выходами блоков 1, 5 и 6 соответственно.

Схема 23 выделения фронта, входящая в состав формирователей функций, состоит из резистора 31, конденсатора 32 и логической микросхемы НЕРАВНОЗНАЧНОСТЬ 33, соединенных следующим образом: вход 29 схемы соединен с первым входом резистора 31 и первым входом схемы НЕРАВНОЗНАЧНОСТЬ 33, второй вход которой соединен с вторым выводом резистора 31 и первым выводом конденсатора 32, второй вывод которого присоединен к нулю питания, выход схемы НЕРАВНОЗНАЧНОСТЬ 33 является выходо.м схемы 23 выделения фронта.

Цифроаналоговые узлы 8-11, 8-13, 9-12, 9-14, 10-15 работают следующим образом. Со счетного входа 28 высокая частота поступает на счетный вход с восьмиразрядного счетика 24 и на первый адресный разряд Ло логической матрицы 25, на отдельные адресные разряды которой с выходов счетчика 24 поступает пониженная в 2 раз частота в соответствии с номером п выхода счётчика.

Сигналами, поступающими с синхронизирующего входа 29 через схему выделения фронта 23 на / - вход установки счетчика 24, работа последнего синхронизируется с основной частотой /мн в моменты перехода напряжения основной частоты через ноль. Выделение фронтов логических сигналов происходит на интервале осуществления логических сигналов разного уровня на первом и втором входах микросхем НЕРАВНОЗНАЧНОСТЬ 33.

Разный логический уровень этих сигналов создается в момент изменения логического уровня сигнала на входе 29 за счет ; С-цепи 31-32.

Вид функции, формируемой формирователем, определяется типом аналогового сигнала, подаваемого на аналоговый вход 30 формирователя и типом программы, записываемой в логическую матрицу 25. Программа составляется из 29 двоичныл слов длиной 8 бит каждое, представляющих собой записи мгновенных значений выходного сиг нала формирователя в двоичной форме в моменты, определяемые адресом Ло, AI, ..., А на входе матрицы 25. Так как адрес линейно нарастает в течение полупериода основной частоты, то на выходах матрицы FQ, Fi, ...,

5 Fj происходит развертка во времени сигнала, записанного в память матрицы 25. Сигналы

в двоичной форме с выходов FO, Fj

матрицы 25 поступают на цифровые входы Хо, X, ..., Х7 цифроаналогового преобразователя 26 (ЦАП), на аналоговый вход UQ

0 которого с входа 30 формирователя подается опорный аналоговый сигнал. ЦАП совместно с подключенным к его выходам операционным усилителем 27 осуществляет преобразование цифрового двоичного кода в анало5 говую величину, пропорциональную опорному аналоговому сигналу, осуществляя тем самым операцию умножения цифрового и аналогового сигналов, подаваемых на ЦАП.

0 В логические матрицы 25 формирователей записываются следующие функции: для формирователя 8 fe sincooi ; для формирователя 9 fg costi)Qt-, для формирователя 10 /ю при

35

-s;. г

зг

fio при (

/10 -wot + 5rsin2u)o/ л

где Wot - текущий угол основной частоты входного Сигнала.

Устройство работает следующим образом. Напряжение системы шин питания U(t) через датчик 2 напряжения поступает на полосовой фильтр 3, который выделяет из него составляющую основной частоты 50 Гц и ее модуляционные составляющие-в области 50±15 Гц с искажением фазы сигнала 50 Гц

Q не более 0,5°. Сигнал с выхода фильтра 3 поступает на нуль-орган 4, который формирует логические сигналы «1 и «О, соответствующие полуволнам напряжения основной частоты. Эти логические сигналы используются для фазовой автоподстройки частоты

5 фазоуправляемого генератора 7 и для синхронизации работы формирователей 8-10 функций с частотой питающей сети. Кроме того, сигнал с выхода фильтра 3 поступает

на измеритель 5 амплитуды напряжения, который формирует выходной сигнал, пропорциональный значению -,

AL

где Urn - амплитуда линейного напряжения

нагрузки;

Х - реактанс тиристорно реакторной группы (ТРГ) статического компенсатора.

Этот сигнал поступает на аналоговый (первый) вход 30 формирователя 10 функций, выходной сигнал которого

при ли

tA,

XL

y- (|-a)(0o) при -f

ji -5-

а)

является произведением аналогового сигна- ла на входе 30 формирователя 10 и выходного сигнала /ю логической матрицы 25 этого формирователя и представляет собой кривую зависимости амплитуды тока первой гармоники ТРГ компенсатора от угла управления

тиристорами при . Дифференциаторы б и 19, формирователи 8 и 9 функций, сумматоры 16-18, режекторный фильтр 20, блок 21 компенсации запаздывания служат для формирования сигнала управления по току нагрузки путем выделения сигналов, содержащих огибающие амплитуд реактивного тока (блоки 1, 6, 8, 9, 11, 14, 16) и активного тока (блоки 1, 6, 8, 9, 12, 13, 17). В момент равенства сигналов с выхода блоков 15 и 21 на выходе блока 22 формируется импульс управления тиристорами фазы ТРГ компенсатора. Приводится математическое описание тракта формирования сигнала управления и характеристики этого тракта.

Модулированный по амплитуде и фазе ток нагрузки

((/) Л(ОС05СОО +С(031П(ЙО/ (1)

где A(i - амплитуда активной составляющей тока; С(/) - амплитуда реактивной составля-

ющей тока;

(йо - промыщленная частота через датчик 1 тока,

подается на первые (аналоговые) входы 30 умножителей 11 и 12 и на вход первого дифференциатора 6, выходной сигнал которого

ri( -(04 A((t sincoo/соо

(/)+l-/ (/)cosa)o/.

(2)

подается на первые (аналоговые) входы 30 умножителей 13 и 14.

В результате на выходе первого умножителя 11 формируется функция

y,/(0sincoo/;(3)

на выходе второго умножителя 12

(Ocosoo()/;(4)

на выходе третьего умножителя 13

(ф1па)(5)

на выходе четвертого умножителя 14

(/)СОЗО)0.(6)

Сигнал на выходе первого сумматора 16 (Osinu)o/-TI(OCOSWJ,/.(7)

Сигнал на выходе второго Сумматора 17 М, Y2+ (t)co54)ot+ ((f)smti)ot. (8)

Подставляя в (7) и (8) выражения (1) и (2), получим

Мс(0-С(/)(0+ C (0sin2ojo -t/0)02Шо

+ Л (0со82шо/,

/ООо

(9)

М,((0-9 C ( Л (0зт2шо+ zu)o.iWo

+ C (/)cos2coo/.(10)

(Оо

Сигналы (0 и () складываются из полезной составляющей и помехи, образованной второй гармоникой, модулированной производными полезного сигнала. При постоянстве амплитуд активной и реактивной составляющей помеха равна нулю.

Синфазное с первой гармоникой напряжение сети

U(t) Un coswot,(И)

падение напряжения At/(/) от тока нагрузки i(t) на реактансе сети X(Dot с учетом уравнения (2) запищется в виде

Ai/(,oL -n( C(i)+ (0 созсоо/.

(12)

Для компенсации этого падения статический компенсатор должен генерировать в сеть ток, равный и противоположный по фазе току

i&(t)C((t) coswo/, (Оо

(13)

т. е. управляющий сигнал, подаваемый на блок 22 сравнения, должен быть равен

Y(t)C(t)+l-A (t}.

СОо

(14)

Переходя в уравнения (9), (10) и (14) к изображениям по Фурье и не учитывая составляющих второй гармоники, которые

подавляются в сигнале управления фильтром 20, характеристики которого рассмотрены, получают

УИ(/о)-С(/ш)+24„ /« М,(/ш)Л(/со)-1-/ш-С(/со);

Y((v) А (/(о).

Решая совместно уравнения (.15), (16) и (17), получают

n/o.)|i3iU -(/«)(18)

.УИ,(/ш), где TQ, ,159 IQ- с.

Граничная частота спектра сигналов A(t) и С(/) не превышает 20 Гц. В этой области частот передаточная функция

( 1 1-а)7о

погрешность на границе не превышает 4%.

Передаточная функция эквива1-О) Го

лентируется инерционным дифференциатором 19 с передаточной функцией

гм(/со)/;.,.

На границе рабочей области частот фазовая погрешность при эквивалентировании не превышает 10°, амплитудная - 6%, при- чем эти цифры относятся лишь к той состав- ляюшей сигнала управления, которая компенсирует синфазное падение напряжения от изменения активного тока.

Таким образом, с указанными погреш- ностями уравнение (18) для сигнала управления может быть заменено следуюшим:

y(/co)M,(/(o).-M,(/co),

l-|-/(i)/o

которое реализуется дифференциатором 19 и сумматором 18.

Для устранения модуляционных составляющих второй гармоники, присутствующих в сигналах М,(/а)) и М/,(/со) (уравнения (9) и (10), выходной сигнал сумматора 18 подают на режекторный фильтр 20 с указан- ными характеристиками. Как видно из амплитудно-частотной характеристики фильтра, приведенной на фиг. 3, на границах диапазона 100±20 Гц результирующее подавление помехи не менее 26 дБ (в 20 раз), в диапазоне 100±10 Гц, где сосредоточена основная часть спектра помехи, подавление не менее 46 дБ (в 200 раз). Значения ампJ10

15

20

25

30

литудной и фазовой погрешности тракта, вызванные фильтрацией сигнала управления звеньями Wi5(/to) с указанными параметрами, приведены на фиг. 4. На границе рабочей области частот фазовая погрешность не превышает 10°, амплитудная - 3%. В диапазоне до 10 Гц, где сосредоточена основная часть спектра сигнала управления, фазовая погрешность не более 5°, амплитудная - не более 0,75%.

Сигнал (f) с выхода фильтра 20 подается на блок 21 компенсации запаздывания, выходной сигнал которого YfK(t) является предсказанным в момент / сигналом Y (+ТЕ ) где Tj. - время предсказания, равное времени суммарного запаздывания, рассмотренного при описании блока 21.

Относительная погрешность компенсации статическим компенсатором гармоники частоты (О, содержащейся в сигнале Y(t), при отсутствии блока 21 компенсации запаздывания, определяется выражением

б /I(L :L-zy M/(20)

/П/со)/

при наличии блока 21 компенсации

6. - ..(2п

-/П/о))

Зависимости (20) и (21) приведены на фиг. 5.

Блок 22 сравнения формирует фронт импульса а, управляющего вентилем ТРГ, в момент равенства сигналов с выхода блоков 15 и 21, т. е. при выполнении равенства

К|-«о + 5 2«оО к(0.(22)

1 IV

Формула изобретения

40

45

«1. Устройство для управления статическим тиристорным компенсатором, содержащее датчики тока и напряжения, умножитель, формирователь опорной функции и блок сравнения, отличающееся тем, что, с целью повышения качества компенсации колебаний напряжения сети от изменения тока нагрузки, оно снабжено полосовым фильтром, нуль-органом, измерителем амплитуды напряжения, фазоуправляемым генератором, двумя блоками сдвига фазы, формирователем функции синус, формирователем функции косинус, четырьмя умножителями, тремя сумматорами, режекторным фильтром, причем выход датчика тока соединен с первыми входами первого и второго умножителей и входом первого блока сдвига фазы, выход которого соединен с первыми входами третьего и четвертого умножителей, выход датчика напряжения соединен с входом полосового фильтра, выход которого соединен с входами нуль-органа и измерителя амплитуды напряжения, а выход последнего соединен с первым входом пятого

умножителя, выход нуль-органа соединен с входом фазоуправляемого генератора и синхронизирующими входами формирователей функций синус, косинус и опорной, а выход фазоуправляемого генератора соединен с входами частоты указанных формирователей функций, при этом выход формирователя функции синус соединен с вторыми входами первого и третьего умножителей, выход формирователя функции косинус соединен с вторыми входами второго и четвертого умножителей, а выход опорной функции соединен с вторым входом пятого умножителя, выход первого умножителя соединен с прямым входом первого сумматора, инверсный вход которого соединен с выходом четвертого умножителя, а выход соединен с первым входом третьего сумматора, второй вход которого соединен с выходом второго блока сдвига фазы, вход которого соединен с выхо

5

дом второго сумматора, первый вход которого соединен с выходом второго умножителя, а второй вход соединен с выходом третьего умножителя, выход третьего сумматора через последовательно включенный режектор- ный фильтр соединен с первым входом блока сравнения, второй вход которого соединен с выходом пятого умножителя.

2.Устройство по п. 1, отличающееся тем, что в него введен блок компенсации запаздывания, включенный между выходом ре- жекторного фильтра и первым входом блока сравнения.

3.Устройство по п. 2, отличающееся тем, что блок компенсации запаздывания выполнен в виде форсирующего звена.

4.Устройство по п. 2, отличающееся тем, что блок компенсации запаздывания выполнен в виде оптимального предсказывающего фильтра.

Фиг. 2

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство компенсации реактивного тока | 1988 |

|

SU1617528A1 |

| Устройство электропитания с компенсацией искажений токов и напряжений системы электропитания | 1987 |

|

SU1576979A1 |

| ДАТЧИК РЕАКТИВНОЙ МОЩНОСТИ РЕЗКОПЕРЕМЕННОЙ НАГРУЗКИ ДЛЯ УПРАВЛЕНИЯ СТАТИЧЕСКИМ КОМПЕНСАТОРОМ РЕАКТИВНОЙ МОЩНОСТИ | 2012 |

|

RU2488204C1 |

| Способ компенсации обменной мощности в электрической системе | 1987 |

|

SU1607044A1 |

| Способ компенсации обменной мощности в электрической системе | 1987 |

|

SU1525771A1 |

| ПРОЦЕССОР СПЕКТРОМЕТРИЧЕСКИХ ИМПУЛЬСОВ | 1995 |

|

RU2092872C1 |

| Устройство компенсации мощности в цепях с синусоидальными токами и переменной нагрузкой | 1988 |

|

SU1615836A1 |

| Следящий фазометр (его варианты) | 1981 |

|

SU1029095A1 |

| МИНИМИЗАТОР МОЩНОСТИ ИСПОЛНИТЕЛЬНОГО ОРГАНА ТИРИСТОРНОГО КОМПЕНСАТОРА РЕАКТИВНОЙ МОЩНОСТИ | 1995 |

|

RU2084066C1 |

| Устройство для двухчастотного вихретокового контроля | 1987 |

|

SU1446551A1 |

Изобретение относится к электротехнике, в частности к устройствам повышения качества электроэнергии с помощью статических тиристорных компенсаторов реактивной мощности, и может найти применение в системах энергоснабжения промышленных предприятий, сельского хозяйства и транспорта. Цель изобретения - повышение качества компенсации колебаний напряжения сети от из.менения тока нагрузки. Сигнал с выхода фильтра 3 поступает на нуль-орган 4, который формирует логические сигналы «1 и «О, соответствующие полуволнам напряжения основной частоты. Эти логические сигналы используются для фазовой автоподстройки частоты фазоуправляемого генератора 7 и для синхронизации работы формирователей 8-10 функций с частотой питающей сети. Кроме того, сигнал с выхода фильтра 3 поступает на измеритель амплитуды напряжения 5, который формирует выходной сигнал, пропорциональный значению , где Um - амплитуда линейного напряжения нагрузки, XL - реактанстиристорно- реакторной группы (ТРГ) статического компенсатора. Этот сигнал поступает на аналоговый вход формирователя 10 функций, выходной сигнал которого является произведением аналогового сигнала на входе формирователя 10 и выходного сигнала логической матрицы этого формирователя и представляет собой кривую зависимости амплитуды тока первой гармоники ТРГ компенсатора от угла управления тиристорами при 4z-U)ot:6. Дифференциаторы 6 и 19, формирователи 8 и 9 функций синус и косинус, сумматоры 16-18, режекторный фильтр 20, блок 21 компенсаций запаздывания служат для формирования сигнала управления по току нагрузки путем выделения сигналов, содержащих огибающие амплитуд реактивного тока и активного тока. В момент равенства сигналов с выхода умножителя 15 и блока 21 на выходе блока 22 сравнения формируется импульс управления тиристорами фазы ТРГ компенсатора. 3 з. п. ф-лы. 5 ил. с S СО о со О

80 85 90 95 100 105

9иг.з

110

113 120 /Л;

А(р

| Патент США № 3987359, кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-05-07—Публикация

1985-04-04—Подача