130

источника с напряжением эл. сети, а также обеспечение возможности управления включением регулируемого источника электроэнергии на параллельную работу с другими источниками. Введение логических элементов И 20 и И-НЕ 28, элемента 21 временной зал,ержки, параллельного регистра 22, формирователя 23 прямоугольных импульсов, синхронизированного с сетью, логической

Изобретение относится к электротехнике, в частности к автоматизированному регулированию частоты генерируемого электроагрегатом переменного напряжения, может быть использовано для автоматического регулирования частоты автономных источников электропитания и является усовершенствованием устройства по авт.св. № 1078571.

Целью изобретения является расширение функциональных возможностей автоматизированного регулятора частоты путем обеспечения возможности синхронизации папряж ения регулируемого источника электроэнергии с напряжением электрической сети, а также обеспечение возможности управления включением регулируемого источника электроэнергии на параллельную работу с другими источниками электроэнергии.

На фиг, 1 и 2 приведены структур- схемы автоматизированного регулятора частоты; на фиг, 3 и 4 - временные диаграммы, поясняющие принцип работы устройства.

Автоматизированный регулятор частоты содержит входной формирователь 1 прямоугольных импульсов, генератор 2 импульсов эталонной частоты, первый одновибратор 3, первый счетчик 4 им- пульсов, вход начальной установки которого подключен к выходу входного формирователя 1 прямоугольных импульсов через первьй одновибратор 3, а счетпът вход - к выходу первого логического элемента И 5, делитель 6 частоты, первый логический элемент И-НЕ 7. который подключен своими входами к выходам первого счетчика 4 импульсов, а выходом связан с одним вхо

схемы 24 сравнения на равно, счетчика 25 импульсов, одновибратора 26 и инвертора 27 позволяет осуществлять подгонку частоты к эталонному значению или к частоте постороннего источника. Кроме этого регулятор имеет дополнительный канал выявления вхождения разности частот в допустимую область значений. I з.п., 4 ил.

дом первого логического элемента И, 5, другой вход которого подключен к выходу генератора 2.импульсов эталонной частоты через делитесь 6 частоты, два

инвертора В и 9, первый из которых подключен к выходу входного формирователя 1 прямоугольных импульсов, а второй связан с выходом первого логического элемента И-НЕ 7, реверсивный

счетчик 10 1Ф1пульсов, второй логический элемент И-НЕ 11, логический элемент ИЛИ 12, входы которых попарно объединены и подключены к выходам реверсивного счетчика 10 импульсов, логическую 13 схему сравнения на равно, одни входы которой подключены к выходам реверсивного счетчика 10 импульсов, а другие к выходам второго счетчика 14 импульса, третий логический элемент .И 15, выход которого подключен к входу - Т-обратного счета реверсивного счетчика 10 импульёов, вход Т прямого счета,которого подключен к выходу второго логического эле

мента И 16., второй одновибратор 17

30

и выходной RS-триггер 18, R-вход которого подклочен к выходу логической схемы 13 сравнения на равно, а S-вход- к выходу последнего разряда второго счетчика 14 импульсов через второй одновибратор 17, Первый вход второго логического элемента И 16 подключен к выходу второго логического элемента PI-HE 11,, второй вход - к выходу пер- 35 вого инвертора 8, третий - к выходу второго инвертора 9, а четвертый соединен с четвертым входом третьего логического элемента И 15, третий вход Которого соединен с выходом второго инвертора 9., второй вход - с входом

40

313092524

первого инвертора 8, а первый вход - через дополнительный элемент 33 вре- с выходом логического элемента ИЖ 12. менной задержки - к входу D В-:ТриггеАвтоматизированный регулятор час- Р 9, первый и второй входы - соот- тоты также содержит входной вывод 19 . ветственно к выходам пятого 30 и шес- управления, четвертый логический эле- 5 того 31 логических элементов И, пер- мент И 20, элемент 21 временной за- ь « входы пятого логического держки, параллельный регистр 22, фор- элемента И 30 подсоединены соответ- мирователь 23 прямоугольных импульсов, .ственно к второ.у и третьему входам „„ третьего логического элемента И 15,

синхронизированный с электрической „ „, fO первый и второй входы шестого логи- сетью, вторую логическую схему 24т, -,,

„ „г ческого элемента И 3 соединены со- сравнения на равно, третий счетчик 25

„ ответственно с выходами первого и

импульсов, одновибратор 26, инвер-г

„-.„ TJ UI7 OQ второго инверторов, выход D-триггетор 27, логический элемент И-НЕ 28, j « t- on - тп 01 pa У предназначен для связи с уп- D-триггер 29, пятый 30 и шестой 31. -,

„15 равляющим входом устройства включе- логические элементы И, дополнительный

riTtii ттНИН на парагшельную работу регулируелогическии элемент ИЛИ 32 и дополни„ то „мого источника электропитания,

тельный элемент J3 временной задерж- ,. „

„ г-5 строиство работает следуюпшм обки. Причем объединенные четвертые вхо- MJ -H

разом,

ды первого и второго логических эле,,20 В режиме автономной работы на Вх,1

ментов И подключены или к выходу ге- „

„„ устройства от источника сигнала разнератора 2 импульсов эталонной часто„ о/ решения регулирования частоты при ты через дополнительньш делитель 34г fк

синхронизации приходит уровень логи- частоты, или к одному из выходов раз-,,.,„

.,ческого О . В результате на выходе

рядов второго счетчика 14 импульсов. ,-г „ „„

„-,00 третьего ло/ ического элемента И-НЕ 28

Выходы первого 7 и третьего /о

., ..„постоянно находится -ровень логичеслогических элементов И-НЕ через чет- - и, к

„ „, кои 1 и на дополнительный вход пер- вертыи логический элемент И 20 соеди-,. ,

вого логического элемента h-HE 7 и на иены с одним из входов первого логи-., .„ .

„ .. „ „ .„ вход элемента я 20 поступают сигналы ческого элемента И 5 Входной вывод 1У ,.-

JO разрешающих уровней., благодаря чеьгу

управления автоматизированным регу-

с.игна.а на входе второго инвертора 9 лятором частоты подсоединен к перво-;

и первого логического элемента И 5 му входу третьего логического элемен„ „„ т- определяется только KOAOBfc Mii комбината.И-НЕ 28, через третий инвертор 2/ ..г циями на входах первого логического

к дополнительному входу первого логи- ,.-эпемента И-НЕ 7 ческого элемента И-НЕ 7 и предназна- J5 |- чен для связи с источником сигнала Электроагрегат вьфабатывает напря- разрешения регулирования в режиме жение U с частотой f (период Т 1/f), синхронизации. Выход второй логичес- которое преобразуется входным форми- кой схемы 24 сравнения на равно под- . рователем по переходу синусоиды ключен к второму входу третьего ло- через нулевое значение в прямоуголь- гического элемента И-НЕ 28, первые ные импульсы длительностью Т/2, а при входы - к выходам первого счетчика 4 выполнении формирователя в виде триг- импульсов, вторые входы - к выходам гера-формирователя - импульсы дли- параллельного регистра 22, входы раз- тельностью 1/Т и периодом 2Т, рядов которого соединены с соответст- По заднему фронту импульсов с вход- вующими выходами третьего счетчика 25 ного формирователя 1 первый одновиб- импульсов, а вход синхронизации через ратор 3 формирует короткий импульс, третий одновибратор 26 - с выходом устанавливающий первый счетчик 4 им- формнрователя 23 прямоугольных им- пульсов в нулевое состояние. Первый пульсов, синхронизированного с элект- счетчик импульсов 4 отсчитывает за- рической сетью, счетньй вход Т треть- данное количество импульсов t, соот- его счетчика 25 импульсов подключен ветствующее интервалу времени Т , по к выходу делителя частоты, а вход ну- окончании которого запрещается полевой установки через элемент 21 вре- ступление на первый счетчик 4 импуль- менной задержки - к входу третьего сов счетньпх: импульсов первым логичес- одновибратора 26. Выход дополнитель- ким элементом И 5 до новой начальной ного логического элемента ИЛИ 32 под- установки счетчика 4. Логические эле- ключен непосредственно к входу С, а менты И 15 и 16 выделяют с помощью

инверторов 8 и 9 интервалы отклонения Т от Tj с учетом знака отклонения (элемент И 16 выделяет интервал

t т - т 1

И 15 - интервал С, Т, - Т

при Т

Т,

эг эт

а элемент при

Тэт Т).

В течение интервалов t на вход +Т реверсивного счетчика 10 импульсов поступают счетные импульсы t, полученные делением импульсов t, , а в течение интервала T.j эти импульсБ поступают на вход -Т реверсивного счетчика 10. В результате при одном знаке отклонения состояния счетчиВ режиме синхронизации на Вх. 1 устройства подается уровень логической 1, который, инвертируясь третьим инвертором 27, запирает первый логический элемент И-НЕ 7, формируя на его выходе сигнал уровня логичес- .кой 1 вне зависимости от состояния остальных его входов. Выходное состояние третьего логического элемента И-НЕ 28 в этом случае полностью определяется сигналом на его вхо ка 10 увеличиваются со скоростью, про-15 д подключенном к выходу второй лопорциональнои величине отклонения, а при противоположном знаке отклонения аналогичным образом уменьшаются. Увеличение или уменьшение состояния счетчика 10 происходит до тех пор, пока оно не станет равно нулю, либо пока счетчик 5 не достигнет одн ого из своих предельных состояний (максимального или минимального),

При достижении максимального и минимального состояний на выходе второго логического элемента И-НЕ 11 или логического элемента ИЛИ 12 появляется сигнал уровня логического О, :5апрещая таким образом прохождение счетных импульсов на соответствующий вход счетчика 10.

Импульсы с генератора 2 импульсов эталонной частоты делятся до получения заданной частоты следования, например 300-500 Гц. По переднему фронту полученных импульсов второй одно- вибратор 17 формирует короткие импульсы, устанавливающие RS-триггер 1 в единичное состояние. Второй счетчик 14 отсчитывает счетные импульсы и в момент, когда состояния его выходов полностью совпадут с состоянием выходов реверсивного счетчика 10, логическая схема 13 сравнения на равно формирует импульс, устанавливающий RS-триггер 18 в нулевое состояние. Таким образом, на прямом выходе RS- триггера 18 формируется импульс, длительность которого пропорциональна состоянию счетчика 10, При максимальном состоянии.счетчика 10 этот импульс превращается в постоянный сигнал уровня логической 1, а при минимальном - в постоянньй сигнал уровня логического О. Сигнал с выхода RS-триггера 18 поступает через усилитель на исполнительный электромаг

нит, изменяя тем самым усилие электро магнита до тех пор, пока отклонение не будет устранено.

В режиме синхронизации на Вх. 1 устройства подается уровень логической 1, который, инвертируясь третьим инвертором 27, запирает первый логический элемент И-НЕ 7, формируя на его выходе сигнал уровня логичес- кой 1 вне зависимости от состояния остальных его входов. Выходное состояние третьего логического элемента И-НЕ 28 в этом случае полностью определяется сигналом на его вход подключенном к выходу второй ло20

гической схемы 24 сравнения на равно. Соответственно на вход второго инвертора 9 и первого логш.1еского элемента И 5 проходит сигнал с элемента И-НЕ 28.

В режиме синхронизации формируется внешний этгшонный импульс Т, длительность которого совпадает с периодом напряжения внешнего источника Uj, , с которым происходит синхронизация и относительно которого осуществляется стабилизация частоты.

Достигается это следующим. Формирователь 23 преобразует напряжение

0

5

0

5

0

.5

внешнего источника U. в прямоут ольные импульсы длительностью Т. аналогично формирователю 1. На каждом полупери- оде (фиг, 3) третий счетчик 25 отсчитывает счетные импульсы t общей длительностью Tj.; . В конце полупериода по окончании отсчета третий одновибра- тор 26 формирует короткий импульс, осуществляющий перезапись информации из счетчика 25 в параллельный регистр 22,

Через короткое время, необходимое для надежной записи информации в параллельном регистре 22, третий счетчик 25 импульсов устанавливается в нулевое состояние сигналом нулевого логического уровня, подан.ным на его вход нулевой установки от формирователя 23 прямоугольных и myльcoв через элемент 21 временной задержки. В результате в параллельном регистре 22 постоянно хранится текущий код длительности Т, Счетчик 4 при зт.омг начиная отсчет импульсов с нулевого состояния, при подаче импульса с одно- вибратора 3 по соотвс:тствующег-1у фронту импульса с формирователя 1 считает до-тех пор, пока кодовая комбинация на его выходах не совпадает с комбинацией на соответствующих выходах параллельного регистра 22. Сравнение кодовых комбинаций осуществляется логической схемой 24 сравнения на равно, на выходе которой формируется уровень логической 1 цри равенстве кодов на

его входах АО...А,

и ..,В„.

В этот

момент сигнал с выхода элемента 24 инвертируется и поступает на первый логический элемент И 5, запрещая поступление счетных импульсов на вход счетчика 4. В результате формируется эталонный импульс Т 1(, но сдвинутый так, что его один фронт всегда совпадает с соответствующим фронтом импульса Т с формирователя (фиг.З). Логическими элементами И 15 и 16 в этом случае выделяется уже сигнал разности Т-Т , и регулирование частоты осуществляется так, что разность периодов T-Tjj, стремится к нулю.

При этом скорость отработки рассогласования пропорциональна величине отклонения Т-Т, что позволяет осуществлять подгонку частоты при синхронизации без перерегулирования- и возникновения неустойчивых режимов.

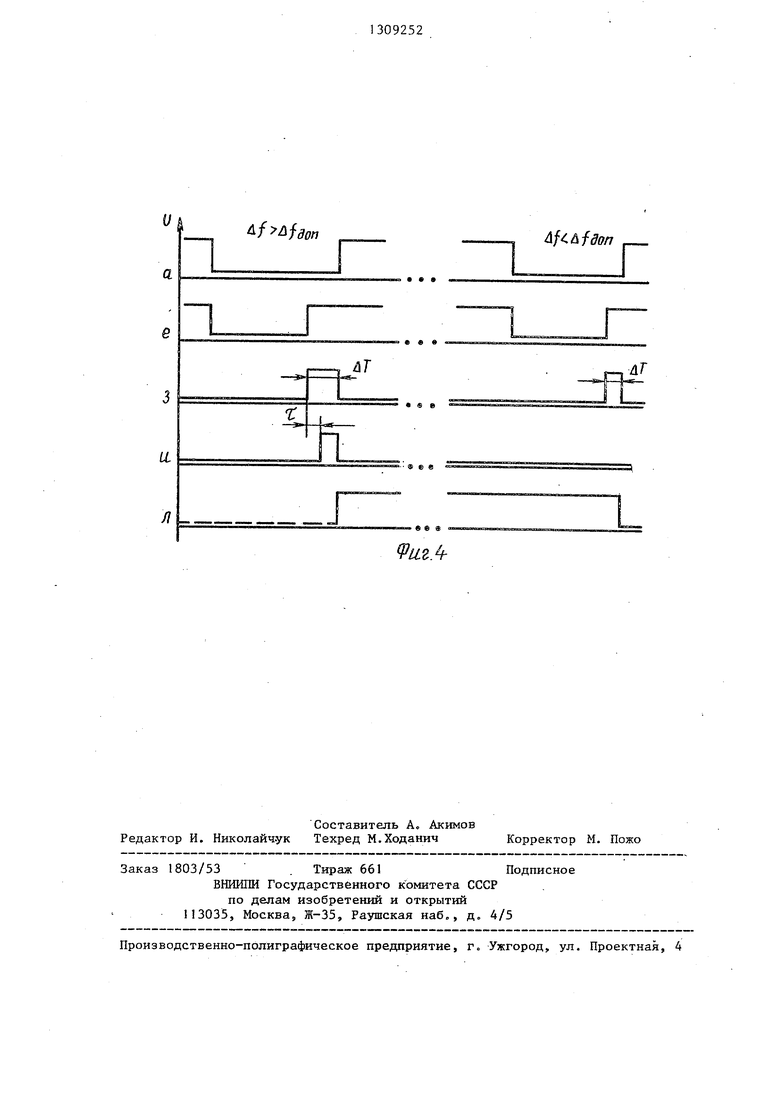

Для выявления вхождения разности частот синхронизируемых источников электропитания в допустимую для включения на параллельную работу зону устройство содержит канал выявления зоны разности частот. Действительная зона разности частот выявляется по текущему интервалу дТ Т -Т (фиг.4),

Выделение дТ осуществляется логическими элементами И 30 или 31 (при Т ТЗР импульс лТ формируется на

Формула изобретения

fO

15

20

1. Автоматизнрованньй регулятор частоты по авт.сз. № 1078з71, отличающийся тем, что, с целью расширения функциональных возможностей, он снабжен входньпу выводом управления, в него введены четвертьй логический элемент И, элемент временной задержки, параллельный регистр, формирователь прямоугольных импульсов вторая логическая схема сравнения на равно, третий счетчик импульсов, од- новнбратор, инвертор, логические элементы И-НЕ, первый логический элемент И-НЕ снабжен дополнительным входом, причем выходы первого и треть- jr его логических элементов И-НЕ соединены с одним из входов первого логического элемента И через четвертый логический элемент И, входной вывод управления автоматизированным регулятором частоты подсоединен к первому входу третьего логического элемента (И-КЕ через третий инвертор - к дoпoлf нительному входу первого логического элемента И-НЕ, выход второй логической схемы сравнения на равно подключен к второму/ входу третьего логического элемента И-НЕ, первые входы - к выходам первого- счетчика импульсов, вторые входы - к выходам параллель30

35

выходе логического элемента И 31, при

„, ,Ап кого регистра, входы разрядов котороТ Tj(; импульс лТ формируется на вы- 40 . ± м

ходе логического элемента И 30).

Сигналы с логических элементов И 30 и 31 объединяются логическим элементом ИЛИ 32, на выходе которого формируется импульс, соответствующий текущей абсолютной величине разности частот . Полученный импульс ЛТ сравнивается с заданным интервалом Т, определяющим величину допустимой зоны Сравнение осуществляется Б-тригге DOM 29.

го соединень с соответствующими выходами третьего счетчика импульсов, а вход синхронизации через третий од- новибратор - с выходом формирователя

прямоугольных импульсов, счетный вход третьего счетчика импульсов подключен к ьыходу делителя частоты, а вход нулевой установки через элемент временной задержки - к входу третьего одноCQ вибратора.

2. Регулятор но п. , о т л и ч а- ю щ и и с я темр что введень D-триг- гер, пятый и шестой логические эле- 55 менты И, дополнительный логический элемент 1-ШИ и дополнительный элемент временной задержки, причем выход дополнительного логического элемента ИЛИ подключен непосредственно к входу

В случае, если дТ Т , на Вых. 2 присутствует уровень логической 1, указывающий на то, что Af ДГддр.

Таким образом, предлагаемое устройство обладает расширенными функ- циoнaльны ш возможностями и позволяет осуществлять синхронизацию источ

2528

НИКОВ электропитания переменног о тока а также определить момент, когда разность частот источников электропитания имеет величину, позволяющую осуществить включение источников электропитания на параллельную работу.

Формула изобретения

O

5

0

1. Автоматизнрованньй регулятор частоты по авт.сз. № 1078з71, отличающийся тем, что, с целью расширения функциональных возможностей, он снабжен входньпу выводом управления, в него введены четвертьй логический элемент И, элемент временной задержки, параллельный регистр, формирователь прямоугольных импульсов, вторая логическая схема сравнения на равно, третий счетчик импульсов, од- новнбратор, инвертор, логические элементы И-НЕ, первый логический элемент И-НЕ снабжен дополнительным входом, причем выходы первого и треть- r его логических элементов И-НЕ соединены с одним из входов первого логического элемента И через четвертый логический элемент И, входной вывод управления автоматизированным регулятором частоты подсоединен к первому входу третьего логического элемента (И-КЕ через третий инвертор - к дoпoлf нительному входу первого логического элемента И-НЕ, выход второй логической схемы сравнения на равно подключен к второму/ входу третьего логического элемента И-НЕ, первые входы - к выходам первого- счетчика импульсов, вторые входы - к выходам параллель0

5

40 . ± м

го соединень с соответствующими выходами третьего счетчика импульсов, а вход синхронизации через третий од- новибратор - с выходом формирователя

прямоугольных импульсов, счетный вход третьего счетчика импульсов подключен к ьыходу делителя частоты, а вход нулевой установки через элемент временной задержки - к входу третьего одноCQ вибратора.

2. Регулятор но п. , о т л и ч а- ю щ и и с я темр что введень D-триг- гер, пятый и шестой логические эле- 55 менты И, дополнительный логический элемент 1-ШИ и дополнительный элемент временной задержки, причем выход дополнительного логического элемента ИЛИ подключен непосредственно к входу

С, а через дополнительный элемент времен1 ой задержки - к входу D D-триг- гера, первый и второй входы - соответственно к выходам пятого и шестого логических элементов И, первый и вто- рой входы пятого логического элемента И подсоединены соответственно к второму и третьему входам третьего

А В

30

логического элемента И, первый и второй входы шестого логического элемента И соединены соответственно с выходами первого и второго инверторов, выход В-триггед а предназначен для связи с управляющим входом устройства включения на параллельную работу регулируемого источника электропитания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Корректор частоты электроагрегата | 1985 |

|

SU1288890A1 |

| Автоматический регулятор частоты | 1982 |

|

SU1078571A1 |

| Устройство для подгонки частоты одного источника напряжения к частоте другого источника напряжения | 1981 |

|

SU991551A1 |

| Устройство для подгонки частоты одного источника напряжения к частоте другого источника напряжения | 1983 |

|

SU1141509A2 |

| Регулятор частоты | 1985 |

|

SU1290465A1 |

| Устройство для автоматической синхронизации генераторов переменного тока | 1984 |

|

SU1238189A1 |

| СИСТЕМА АВТОМАТИЗИРОВАННОГО КОНТРОЛЯ | 1991 |

|

RU2006896C1 |

| Регулятор частоты электроагрегата | 1985 |

|

SU1288891A1 |

| Одноканальное устройство для управления -фазным преобразователем | 1978 |

|

SU775855A1 |

| Вибрационный источник сейсмических сигналов | 1983 |

|

SU1138772A1 |

Изобретение относится к электротехнике, в частности к автоматизированному регулированию частоты генерируемого электроагрегатом перем. напряжения, м.б. использовано в автономных источниках питания. Целью изобретения является расширение функциональных возможностей регулятора частоты путем обеспечения возможности синхронизации напряжения регулируемого Crt Sat.l Риг.1

9iiz.5

и

а

6

п

LL

Составитель А. Акимов Редактор И. Николайчук Техред М.Ходанич

Заказ 1803/53 . Тираж 661Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Г

&J

f

яаЛ

Корректор М. Пожо

| Автоматический регулятор частоты | 1982 |

|

SU1078571A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-05-07—Публикация

1985-01-02—Подача