113

Изобретение относится к вычислительной технике и может быть использовано при построении систем обмена информацией межДу ЭВМ или функциональными модулями многопроцессорных вычислительных комплексов. Цель изобретения - уменьшение времени восстановления системы.

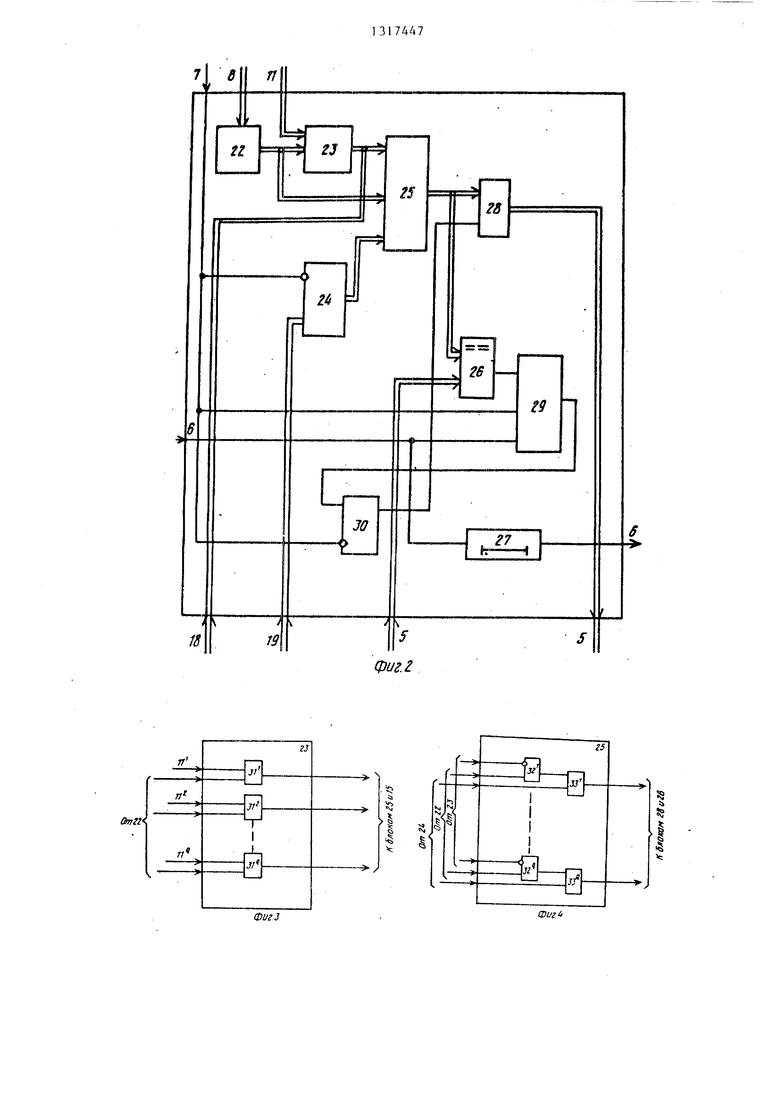

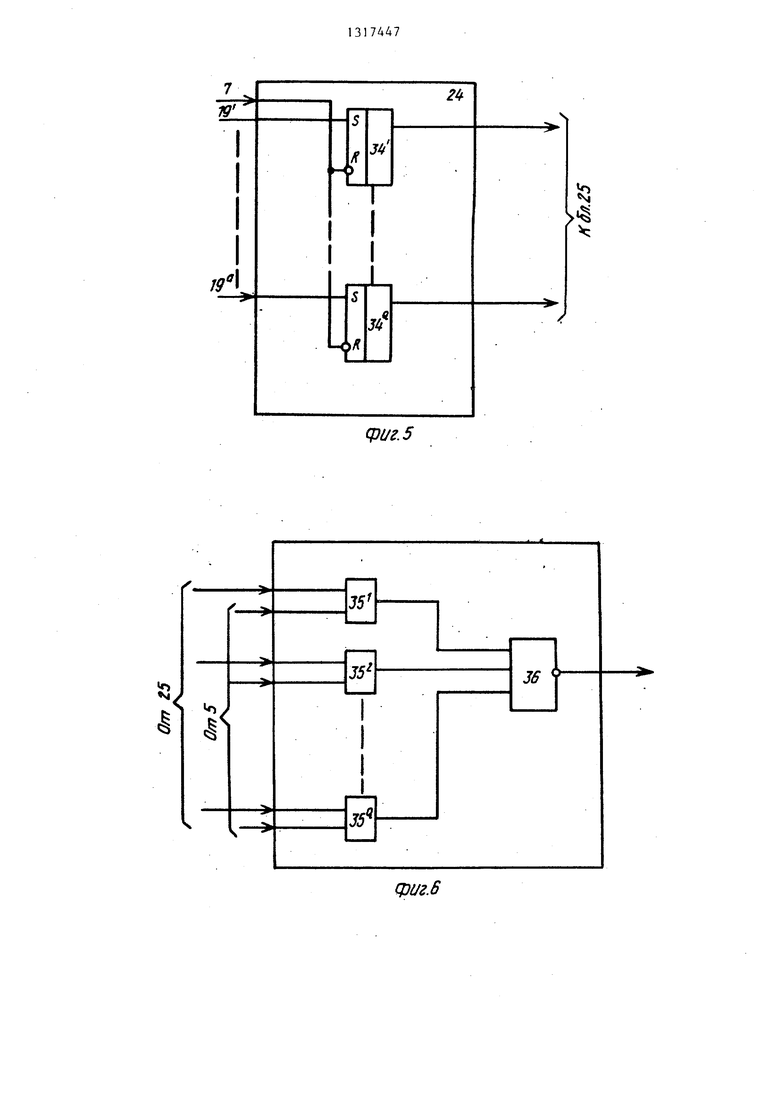

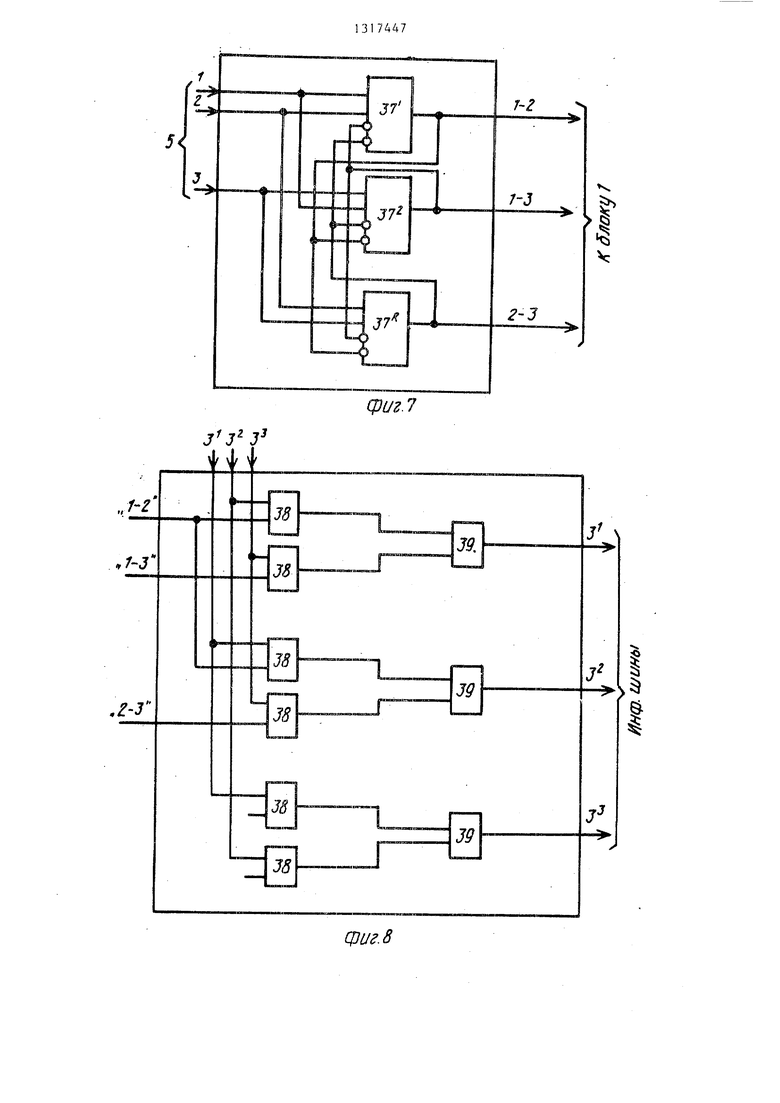

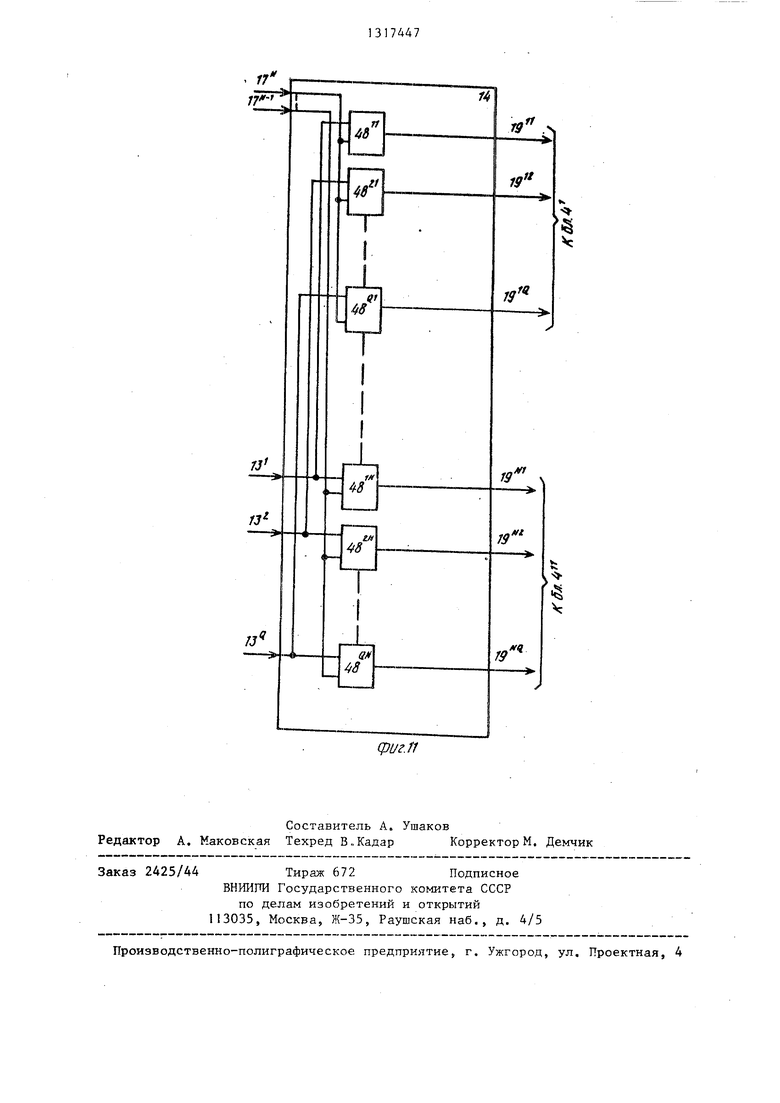

На фиг, 1 представлена структурная схема системы коммутации; на фиг. 2 - схема устройства управления обменом; на фиг, 3 - схема второй группы элементов Н; на фиг, 4 - схема блока модификации маршрута; на фиг,. 5 - схема регистра обхода; на фиг, 6 - схема сравнения; на фиг. 7 - схема блока управления коммутатором; на фиг. 8 - схема коммутатора; на фиг. 9 - схема блока контроля; на фиг. 10 - схема первого коммутатора; на фиг. 11 - схема второго коммутатора.

Система коммутации (фиг„ 1) содержит N коммутаторов 1, соединенных . между собой и с N абонентами 2 информационными шинами 3, N устройств 4 управления обменом, подключенных к линиям 5 управления и соединенных между собой линией 6 опроса. Каждый абонент 2 соединен с устройством 4 управления обменом линией 7 запроса

на обмен и адресйой пшной 8.

Линии 5 управления подключены к блокам 9 управления коммутаторами 1. Управляющие выходы блоков 9 связаны с коммутаторами 1. Блоки 10 контроля входами подключены к информационным шинам, а выходами - к линиям 11 индикации, отказа, которые подключешз ко всем устройствам 4 управления обменом.

Блок 12 постоянной памяти выходом 13 подключен к второму коммутатору 14, а линиями 16 выборки - к первому коммутатору 15.-

Первый коммутатор 15 соединен с вторым коммутатором 14 линиями 17. стробирования, а с устройствами управления обменом - линиями 18 адреса Второй коммутатор 14 кодов обхода подключен к выходу 13 блока 12 постоянной памяти и линиями 19 кода об обхода соединен с устройствами 4 управления обменом.

Блок 20 опроса включен в разрыв линии 6 опроса и выходом соединен с входом 21 синхронизации первого коммутатора 15.

72

Коммутаторы 1 предназначены для соединения информационных шин 3, которые последовательно входя в маршрут, позволяют абонентам 2 производить обмен данными. Устройства 4 управления обменом служат для возбуждения определенных линий 5, каждая из которых соответствует одной информационной шине 3. Число линий 5

равно Q - числу шин 3. Линия 6 опроса позволяет передавать импульс, во время которого может сработать устройство 4 и в соответствии с сигналом на линии 7 запроса, а также с

адресом запрашиваемого абонента на адресной шине 8 возбудить определенные линии 5. Блок 9 управления коммутатором при возбуждении линий 5 и 5 формирует управляющий сигнал на

соединение коммутатором информационных шин 3 и З .

Блоки 10 контроля служат для фиксации отказа информационных шин 3, а линии 11 индикации отказа - для передачи информации об отказе шин.З в устройство 4 управления обменом,

В блоке 12 постоянной памяти хранятся позиционные коды обходных маршрутов для каждой информационной шины 3 на случай ее отказа (табл. 1).

Например (фиг. 1), при отказе информационной шины 3 код из четвертой ячейки блока постоянной памяти определяет маршрут обхода с использованием информационных шин 3 . и 3. Код обхода с выхода 13 вьщается в коммутатор 14. Первый коммутатор15 предназначен ддя вьщачи по линиям 16 выборки номеров отказавших шин 3 в

блок 12 постоянной памяти и для синхронизации второго коммутатора 14 кодов обхода с помощью линий 17 стробирования. Номер отказавшей шины 3 поступает в первый коммутатор 15 по

линиям 18 адреса. Линии 19 служат для передачи кода обхода из второго коммутатора 14 в устройство 4 управления обменом.

Блок 20 опроса предназначен для

формирования импульса на линии 6 опроса при включении системы,

Т а б л и ц а 1

Номера информационных шин I I 2 з 4 5 б 7 s P

i.J1L111I

000000000 000000000

Продолжение табл.1

Номера информационных шин

0000 0001 0001

1 О

1

1000 1000 0000

Цепь, связьгеающая выход блока 20 с входом 21 синхронизации первого 20 коммутатора I5, служит для обеспечения синхронной работы устройств 4 управления обменом и второго коммутатора 14,

Устройство 4 управления обменом 25 (фиг. 2) содержит блок 22 памяти маршрутов, регистр 24 обхода, узел 25 модификации маршрута, схему 26 сравнения, элемент 27 задержки, первую

28 и вторую 23 группы элементов И, элемент И 29 и триггер 30.

Входы блока 22 памяти подключены к адресной шине 8, а выходы соединены с входами второй группы элементов И 23 и блока 25 модификации маршрута. Первые входы второй группы элементов И 23 подключены к линиям 11 индикации отказа, а выходы - к входам узла 25 и к линиям 18 адреса. Третьи входы узла 25 соединены с выходами регистра 24, а выходы - с входами группы элементов И 28 и схемы 26 сравнения.

Входь регистра 24 подключены к линиям.19 кода обхода, а инверсный вход установки в О соединен с инверсным входом установки в О триггера 30, с входом элемента 29 и с линией 7 запроса. Вторые входы схемы 26 сравнения подключены к линиям 5 управления, а выход -. к второму входу элемента И 29, третий вход которого свя;зан с входом линии 6 опроса и с входом элемента 27 задержки. Выход элемента И 29 соединен с установочны входом триггера 30, выход которого подключен к второму входу первой группы элементов И 28, выход которых

соединен по схеме ЮНТАЖНОЕ ИЛИ с линиями 5 управления. Выход элемента 28 задержки подключен к продолжению линии 6 опроса.

Блок 22 памяти имеет (N-1) ячейку и хранит коды маршрутов от данного абонента 2 ко всем остальным абонентам-адресатам 2 (табл. 2)..

Таблица 2

1 10010000...

101001000...

5 0

5

0

5

0

5

В табл. 2 представлено содержимое блока 22 в устройстве 4 управления обменом - коды маршрутов от абонента 2 ко всем остальным абонентам. Единица в J-й позиции k-й ячейки указывает, что информационная -шина З входит в маршрут от абонента 2 к абоненту 2 . Например, от абонента 2 к абоненту 2 маршрут включает информационные шины 3 , 3 и (фиг. 1).

Вторая группа элементов И 23 позволяет выявить, входит ли в маршрут, определенный в блоке 22, отказавшая информационная шина 3. Если такой факт имеет место, то вторая группа элементов И 23 выдает позиционный код ее номера с целью обращения к

первому коммутатору (по линиям 18 адреса) и с целью последующего исключения ее из маршрута. Регистр 24 служит для хранения кода обхода отказавшей шины 3 На время обмена данными между абонентами.

Узел 25 модификации маршрута предназначен для корректирования кода маршрута, считанного из блока 22. Корректирование производится с учетом кода маршрута обхода из регистра 24 и номера отказавшей шины 3 из .второй группы элементов И 23.

Схема 26 сравнения позволяет определить, свободны ли все шины 3, которые необходимо захватить в марш513

рут. Элемент 27 задерживает импульсГ опроса в линии 6 на время переходных процессов в устройствах при установлении соединения между абонентами. Первая группа элементов И 28 для синхронной выдачи кода маршрута rta линии 5 управления.

Синхронизацию захвата маршрута обеспечивает элемент И 29, который устанавливает в 1 триггер 30 При выполнении следующих условий: наличие разрешения от схемы 26 сравнения (все информационные шины маршрута свободны), наличие сигнала на линии 7 и появление сигнала на линии 6 опроса. Триггер 30 управляет первой группой элементов И 28.

Подключение линии 7 запроса к установочным в О входам регистра 24 и триггера 30 позволяет при снятии сигнала на линии 7 прекратить вьщачу кода маршрута на линии 5 управления и подготовить к последующей работе.

Вторая группа элементов И 23 (фиг. 3) содержит Q элементов И 31. Первые входы элементов И 31 образуют первые входы узла, подключенные к линиям 11 индикации отказов информационых шин 3. Вторые входы элементов И И 31 являются вторыми входами узла и подключены к выходам блока 22 маршрутов.. Сигнал 1 на выходе элемента И 31 появляется в случае отказа j-й информационной шины 3 и необходимости использования ее в маршруте. Выходы элементов И 31 являются выходами узла.

. Узел 25 модификации маршрута (фиг. 4) содержит О элементов И 32 и столько же элементов 33 сложения .по модулю два. Каждый j-й выход узла 23 служит для блокировки сигнала с j-ro выхода блока 22 памяти маршрутов поэтому указанные выходы объединяются соответствующим элементом И 32, причем выход уэла 23 подключается к нему через инвертор. Выход каждого зле- менТа И 32 вместе с соответствующим выходом регистра 24 подключается к сумматору 33 по модулю два, выход ко торого является выходом узла 25., Использование именно сумматора 33 по модулю два объясняется так. Если на некоторый элемент 33 поступает одновременно две единицы - с выхода элемента 32 и из регистра 24, то эт означает, что в маршруте, указанном в блоке 22, и в коде обходного мар

76

шрута из регистра 24 определена необходимость использовать одну и ту же информационную шину 3. Такой случай возможен, когда, например

(фиг. 1), в маршруту из блока 22 указаны информационные шины 3, 3, 3, 3, а для обхода шины 3 в случае ее отказа в блоке 12 постоянной памяти указаны шины 3 и 3. Скорректированный маршрут будет включать шины 3 3, 3(передача в одну сторону) 3 (передача в противоположную сторону), 3. Петлю по шине 3 целесообразно исключить, что и обеспечивает

элемент 33, формируя в рассматриваемом случае на своем выходе О.

Регистр 24 (фиг. 5) содержит Q триггеров 34. Информационные входы регистра являются входами установки

в 1 триггеров. Вход установки регистра 24 в О является установочным в нуль входом каждого триггера.

Схема 26 сравнения (фиг. 6) содержит Q элементов И 35 и элемент ИЛИНЕ 36. Первые и вторые входы элементов И 35 являются первыми и вторыми входами схемы 26 сравнения, а выходы соединены с входами элемента ИЛИ- НЕ 36, формирующего результат сравнения. Схема 26 сравнивает код маршрута, сформированньй в узле 25 модификации маршрута, с кодом состояния линий 5, отражаюш 1м занятость шин 3. 1 на выходе схемы появляется только

в том случае, если на выходе 5сех элементов И 35 - нуль. Такое состояние возможно, когда шина, входяш;ая в сформированный маршрут, свободна (О на соответствующей линии 5) или

ш:ина, пусть даже занятая, не входит в данный маршрут (на соответствующем выходе узла 25 .- О).

Блок 9 управления коммутатором (фиг. 7) содержит R элементов И 37 с

прямыми и инверсными входами. Максимальное значение R определяется числом всех возможных комбинаций по установлению соединений соответствую- шим коммутатором 1, к которо подключено f информационных шин 3, где Ср. Линии 5 управления, которые отображают занятость подключенных к коммутатору 1 шин 3, попарно (i, j) соединены с прямь ми входами элементов

и 37. Инверсные входы элементов И 37 подключены к выходам тех из оставшихся элементов И 37, к которым подключены i-я или j-я линии 5 управления.

71

Таким образом, появление единиц на паре линий 5 , 5 обеспечивает срабатывание только одного элемента И 37 и соединение шин 3 и 3J в коммутаторе 1. Поэтому в последующем разрешается соединение в коммутатор другой пары шин () и блокируется соединение между собой шин, принадлежащих разным маршрутам {З с 3 и с 3 3) с З и с ЗО.

Коммутатор 1, изображенный на фиг. 8 для случая трех (р) одноразрядных информационных шин 3, содержит шесть ( р(Р-1) - в общем случае элементов И 38 и три (р) элемента ШШ 39. Управляющие сигналы от блок 9 обеспечивают коммутацию соответствующих шин 3.

Блок 10 контроля (фиг. 9) содержит два идентичных узла (БК1 и БК2) каждый из которых фиксирует факт отказа линий информационной шины 3, предназначенных для передачи данных в одном из двух направлений.

Блок 10 контроля содержит сумматор 40 по модулю два, триггер 41, генератор 42 одиночных импульсов, элемент ИЛИ 43, элемент ИЛИ 44 и подключен к цепи 45 локализации отказа, введенной в состав линий шины 3. С целью контроля в состав информационной шины 3, кроме информационных линий, включена линия контрольнго по нечетности разряда, формируе

мого абонентом-инициатором. Сумматор 35 24 и временем модификации маршрута

40 по модулю два служит для обнаружения отказа. Если число единиц в коде передаваемом по информационным линиям и по линии контрольного разряда, окажется четным, то на инверсном выходе сумматора 40 появится 1. Указанный выход подключен к входу установки в 1 триггера .41, фикси- рующего факт отказа. Генератор 42 одиночных импульсов подключен к входу уЬтановки в О триггера 41 для перевода его в исходное состояние. Прямой выход триггера 41 подключен к элементу ИЛИ 43, включенному в разрьш цепи 45 локализации отказа. Цепь 45 введена в состав линий ин- формационных шин 3 с целью фиксации места возникновения отказа с точностью до одной информационной шины 3. В случае отсутствия цепи 45 отказ одной информационной шины 3 вызьгоа- ет срабатывание не только этого блока

10, но и других блоков 10, 10

10

и т. д., подключенных к информационным шинам 3 , 3f , входящих в проложенный маршрут. При этом последующие блоки контроля зафиксируют не отказ, а факт передачи искаженного в шине 3 кода. Цепь 45 подключена к входу установки в О триггера 41, Такое подключение позволяет сбросить в О триггеры 41 в блоках 10, и т.д. посредством распростране5

0

5

0

ния сигнала по. цепи 45 из блока 10 вдоль установленного маршрут.а через промежуточные коммутаторы 1. Таким образом, только в триггере 41 блока 10 сохранится 1 и будет локализован отказ единственной шины З .

Первый коммутатор 15 (фиг. 10) содержит N элементов 46 задержки и мультиплексор 47. Элементы 46 задержки включены последовательно. Каждый элемент 46 задержки имеет импульсный (подключенный к входу следующего элемента 46 задержки) и потенциальный выходы. Запуск первого коммутатора 15 осуществляется импульсом с входа 21 синхронизации. . Элемент 46 задержки обеспечивает задержку импульса на время, достаточное для формирования кода обходного маршрута. Оно определяется временем задержки сигнала во втором коммутаторе 14, временем считывания информации из блока 12 постоянной памяти, временем приема информации в регистр

5

О 0 5

в узле 15. При этом время задержки в элементе 46 должно быть не больше времени задержки импульса опроса в элементе 27 устройства 4 управления обменом. Мультиплексор 47 представляет собой (N Q)-разрядный по входу и Q-разрядный по выходу коммутатор. При этом управляющие входы V ,..,V мультиплексора 47 подключены к пот тенциальным выходам элементов 46 задержки, а информационные входы - к линиям 18 адреса. Подключение цепей 17 управления к элементам 46 и 47 осуществляется следуюшзим образом: цепь 17 подключена к потенциальному выходу элемента 46 и к входу

V,4. а цепь

элемента 4Ь и к входу V, мультиплексора 47. Этим достигается формирование обходного маршрута в устройстве 4 управления обменом до прихода импульса опроса по линии 6 в это

47 (i 1, N-1),

мультиплексора

17 - к потенциальному выходу 46 и к входу V,

913

устройство. Выходы мультиплексора. 47 подключены к линиям 16 выборки.

Второй коммутатор 14 (фиг. П) содержит N групп элементов И 48 по Q элементов в каждой. Первые входы элементов i-й группы подключены к линии а вторые входы из каждой группы - к выходу 13. Выходами второго коммутатора 14 являются выходы элементов И 48, соединенные с линиями 19 кода обхода.

Система коммутации функционирует следующим образом.

В исходном состоянии в блок 22 памяти маршрутов каждого устройства 4 управления обменом заносятся коды назначенных маршрутов от абонента 2 к остальным абонентам, а в блок 12 постоянной.памяти - коды маршрутов обхода для каждой из информационных шин 3. От блока 20 опроса производится запуск системы, и по линии 6 от устройства 4 к соседнему устройству 4 начинает передаваться сигнал, разрешающий устанавливать соединение по запросам абонентов 2.

Аналогичный сигнал начинает передаваться по цепочке элементов 46 задержки в первом коммутаторе 15. Сигнал в первом коммутаторе I5 опережает сигнал опроси в блоке 4. В случае отказа шины 3 этим обеспечивается подготовка обходного маршрута в блоке 4 до прихода импульса опроса по линии 6.

Для организации обмена абонент- инициатор 2 выдает в устройство 4 по адресной шине 8 адрес искомого абонента, а по линии 7 - запрос на обмен. По адресу из блока 22 памяти считывается код маршрута между абонентами. Во второй группе элементов И 23 осуществляется проверка, входят ли отказавшие шины 3 в этот маршрут. Если такой факт будет установлен, то от второй группы элементов И 23 позиционный код неисправньпс шин 3 по .линиям 18 адреса передается в первый коммутатор 15. Там мультиплексор 47 производит выдачу этого кода на лини 16 выборки. Из блока 12 постоянной памяти считывается код обхода отказавших щин 3, который через второй коммутатор 14 по сигналу на линии 17 стробирования выдается по линиям 19 кода обхода в запросившее устройство 4 управления обменом.

O

5

7447

0

5

0

10

В устройстве 4 управления обменом код обхода заносится в регистр 24 и с его выходов подается на узел 25 модификации маршрута. В узле 25 осуществляется блокировка сигналов из блока 22 памяти,-соответствующих отказавшим шинам 3, и наложение кода обхода из регистра 24 на код маршрута. Сформированный таким образом код нового маршрута подается на схему 26 сравнения, в которой определяется возможность его захвата, т. е. устанавливается факт незанятости всех входящих в новый маршрут шин 3. С приходом по линии 6 опроса разрешающего сигнала осуществляется захват маршрута - устанавливается в 1 триггер 30 и на линиях 5 управления, соответствуюпщх захватываемым шинам 3, появляются логические единицы. В результате срабатывают блоки 9 управления теми коммутаторами 1, кото- рые должны соединить захватываемые шины. Коммутаторы 1 производят требуемые соединения, I.

После обмена абонент-инициатор 2

снимает запрос на обмен на линии 7, что приводит к установке в О триггера 30 и сбросу регистра 24. Установка в О триггера 30 приводит к

появлению логических нулей на линиях 5 управления, поддерживающих соединение шин 3 маршрута. Как следствие, появляются нули на выходах блоков 9 управления коммутаторами, и соединение в коммутаторах 1 разрушается. Если с приходом по линии 6 опроса разрешающего сигнала занят хотя бы одна шина 3 сформированного маршрута, то триггер 30 в 1 не устанавливается и соединения абонентов не произойдет.

Формула изобретения

Система коммутации, содержащая л коммутаторов, м блоков управления коммутаторами, N устройств управле- ния обменом, Q блоков контроля информационных шин, блок опроса, причем m информационных входов-выходов всех коммутаторов (N m : Q) являются соответствующими информационными входами-выходами системы, подключаемыми к абонентам, остальные (Q-ш) информационных входов-выходов коммутаторов соединены между собой, вход адреса и вход запроса п-го устройст111

ва управления обменом (п l,.o,,N) являются п-ми входами адреса и запроса системы от п-го абонента соответственно, входы-выходы управления N блоков управления обменом поразрядно объединены и подключены через шину управления к входам А блоков управления коммутаторами, выходы которых соединены с управляющими входами М коммутаторов соответственно, информационные входы блоков контроля подключены к соответствующим информационным шинам системы, выход и вход блока опроса подключены к входу опроса первого и выходу опроса N-ro устройств .управления обменом соот- ветственно, выход опроса К-го (К 1, N-1) устройства управления обменом подключен к входу опроса К+1-го устройства зшравления обменом, причем устройство управления обменом содержит блок памяти маршрутов, первую группу элементов И, схему срав- нения, элемент И, триггер, элемент задержки, при этом вход адреса устройства управления обменом подключен к адресному входу блока памяти маршрута, а вход запроса подключен к первому входу элемента И и к инверсному входу сброса триггера, вход опроса устройства управления обменом соединен с вторым входом элемента И и через элемент задержки - с выходом опроса устройства управления обменом, выход элемента И подключен к входу установки триггера, выход триггера подключен к первым входам элементов И первой группы, вторые входы которых соединены с соответствующими разрядами первого информационного входа схемы сравнения, вьгход элементов И первой группы и второй информационный вход схемы сравнения соединены с входом-выходом управления устройства управления обменом, отличающаяся тем, что, с целью уменьшения времени восстановления системы, в нее введены блок постоянной памяти, первый и второй коммутаторы, причем вход синхронизации первого коммутатора подключен к выходу блока опроса, а информационный вход соединен с адресными выходами устройств управления обменом, первые выходы первого коммутатора подключе4712

ны к одноименным входам второго коммутатора, а вторые выходы - к входам адреса блока постоянной памяти, выход которого подключен к информаци- онному входу второго коммутатора, выходы которого соединены с входами кодов обхода соответствующих устройств управления обменом, входы контроля которых подключены к выходам

блоков контроля, причем первый коммутатор содержит N элементов задержки и мультиплексор, причем вход пер- , вого элемента задержки является входом синхронизации первого коммутатора, импульсный вьпсод К-го элемента задержки подключен к входу К+1-го элемента задержки, потенциальный выход К-го элемента задержки подключен к К+1-му управлянице входу мультиплексора и является К-м первым выходом первого коммутатора, потенциальный выход N-ro элемента задержки подключен к первому управляющему входу мультиплексора и

является N-M вторым вьпсодом первого коммутатора, Q. разрядных информационных входов мультиплексора являются информационным входом первого коммутатора, а Q-разрядный выход мульти- .

плексора является выходом адреса первого коммутатора, причем в каждое устройство управления обменом введены вторая группа элементов И, регистр обхода и блок модификации маршрута,

причем контрольньш вход устройства управления обменом соединен с первым входом элементов И второй группы, выход блока памяти маршрута подключен к входу маршрута блока модификации

маршрута и к второму входу второй группы элементов И, выход которой подсоединен к входу адреса отказавшей шины блока модификации маршрута и является одноименным выходом устройства управления обменом, вход ко- ; да обмена устройства управления обменом подсоединен к информационному входу регистра обходного маршрута, вход синхронизации которого подключен к входу запроса устройства управления обменом, выход регистра обходного маршрута подключен к входу кода обхода блока модификации маршрута, выход которого подключен к первому

информационному вход у схемысравнения.

18

| название | год | авторы | номер документа |

|---|---|---|---|

| Система коммутации | 1985 |

|

SU1317449A1 |

| Система коммутации | 1986 |

|

SU1359783A1 |

| Система коммутации | 1986 |

|

SU1403071A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Система коммутации | 1986 |

|

SU1410047A1 |

| Система коммутации | 1989 |

|

SU1702384A1 |

| Система коммутации | 1986 |

|

SU1354200A1 |

| Система коммутации | 1986 |

|

SU1411767A1 |

| Децентрализованная система коммутации | 1985 |

|

SU1272338A2 |

| Децентрализованная система коммутации | 1985 |

|

SU1282150A1 |

Изобретение относится к вычислительной технике. Цепь изобретения - уменьшение времени восстановления. Система коммутаций содержит коммутаторы 1, связанные информационными шинами между собой и с абонентами 2, устройства 4 управления обменом, соединенные с коммутаторами 1 линиями управления. Сущность изобретения состоит во введении первого и второго коммутаторов 15 и 14 и блока 12 постоянной памяти, в котором хранятся коды обходных маршрутов для каждой информационной шины на случай ее отказа. Связи второго коммутатора 14 с устройствами 4 управления обменом позволяют скорректировать код назначенного маршрута, если в нем предполагается использование отказавшей шины. 11 ил., 2 табл. а 9 (Л 00 4 4;:

Отгг.

фиг.з

1

Фиг.

§

q)UZ.5

фиг.В

37

7-J

к.

;

l

§

37

2-3

J JO

фиг.1

фиг. 8

фиг. ГО

Фиг. 9

Составитель А, Ушаков Редактор А. Маковская Техред В.Кадар Корректор М, Демчик

Заказ 2425/44 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

сригЛ

| Децентрализованная система коммутации | 1984 |

|

SU1228110A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Децентрализованная система коммутации | 1985 |

|

SU1272338A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-15—Публикация

1985-07-12—Подача