Изобретение относится к электросвязи и может быть иснользовано для контроля качества дискретного канала связи.

Цель изобретения - повышение достоверности нрогнозирования.

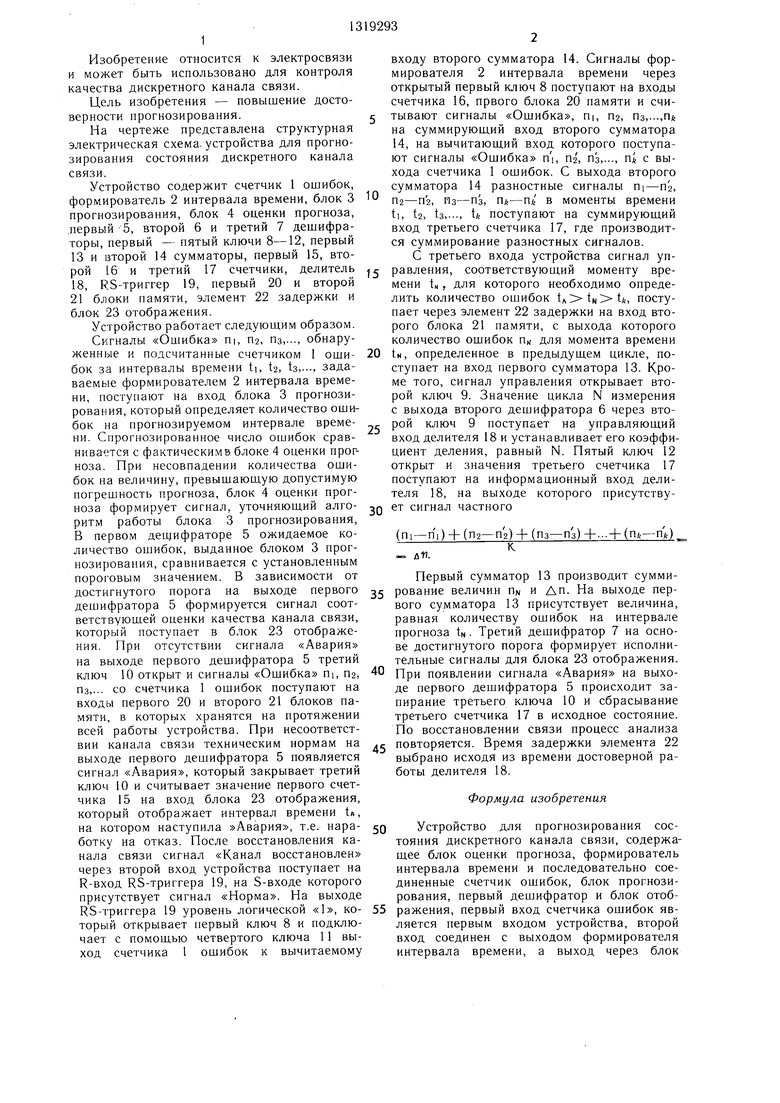

На чертеже представлена структурная электрическая схема.устройства для прогнозирования состояния дискретного канала связи.

Устройство содержит счетчик 1 ошибок,

входу второго сумматора 14. Сигналы формирователя 2 интервала времени через открытый первый ключ 8 поступают на входы счетчика 16, првого блока 20 иамяти и счи- 5 тывают сигналы «Ошибка, П|, П2, пз,...,Пй на суммируюший вход второго сумматора 14, на вычитаюш,ий вход которого поступают сигналы «Ошибка n l, nz, п з,..., n k с выхода счетчика 1 ошибок. С выхода второго сумматора 14 разностные сигналы ni-П2,

формирователь 2 интервала времени, блок 3Ю пз-п 2, пз-п з, в моменты времени

прогнозирования, блок 4 оценки прогноза,ti, t2, 1з,..., U поступают на суммируюший .первый-5, второй 6 и третий 7 дешифраторы, первый - пятый ключи 8-12, первый

13 и второй 14 сумматоры, первый 15, втовход третьего счетчика 17, где производится суммирование разностных сигналов.

С третьего входа устройства сигнал упрой 16 и третий 17 счетчики, делитель равления, соответствующий моменту вре- 18, RS-триггер 19, первый 20 и второймени IN, для которого необходимо опреде21 блоки памяти, элемент 22 задержки и блок 23 отображения.

Устройство работает следующим образом. Сигналы «Ошибка П|, П2, пз,..., обнаруженные и подсчитанные счетчиком 1 оши- 20 «, определенное в предыдущем цикле, по- бок за интервалы времени ti, iz, is,---, зада-ступает на вход первого сумматора 13. Кроваемые формирователем 2 интервала времени, поступают на вход блока 3 прогнозилить количество ошибок , поступает через элемент 22 задержки на вход второго блока 21 памяти, с выхода которого количество ошибок п для момента времени

ме того, сигнал управления открывает второй ключ 9. Значение цикла N измерения с выхода второго дешифратора 6 через вторования, который определяет количество ошиме того, сигнал управления открывает второй ключ 9. Значение цикла N измерения с выхода второго дешифратора 6 через втобок на прогнозируемом интервале време-рой ключ 9 поступает на управляющий

вход делителя 18 и устанавливает его коэффициент деления, равный N. Пятый ключ 12 открыт и значения третьего счетчика 17 поступают на информационный вход делителя 18, на выходе которого присутству(П1-rii) + (П2-П2) + (пз-Пз) + + () ли

Первый сумматор 13 производит суммини. Спрогнозированное число ошибок сравнивается с фактическим в, блоке 4 оценки прогноза. При несовпадении количества ошибок на величину, превышающую допустимую погрешность прогноза, блок 4 оценки прогноза формирует сигнал, уточняющий алго- ,Q ет сигнал частного ритм работы блока 3 прогнозирования, В первом дешифраторе 5 ожидаемое количество ошибок, выданное блоком 3 прогнозирования, сравнивается с установленным nopoi OBbiM значением. В зависимости от достигнутого порога на выходе первого 5 рование величин PN и Дп. На выходе пер- дешифратора 5 формируется сигнал соот-вого сумматора 13 присутствует величина,

ветствуюшей оценки качества канала связи,равная количеству ошибок на интервале

который поступает в блок 23 отображе-прогноза U. Третий дешифратор 7 на оснония. При отсутствии сигнала «Авария ве достигнутого порога формирует исполнина выходе первого дешифратора 5 третийтельные сигналы для блока 23 отображения,

ключ 10 открыт и сигналы «Ошибка ni, 02, 40 При появлении сигнала «Авария на выхо- пз,... со счетчика 1 ошибок поступают наде первого дешифратора 5 происходит запирание третьего ключа 10 и сбрасывание третьего счетчика 17 в исходное состояние. По восстановлении связи процесс анализа ВИИ канала связи техническим нормам на повторяется. Время задержки элемента 22 выходе первого дешифратора 5 появляетсявыбрано исходя из времени достоверной расигнал «Авария, который закрывает третий ключ 10 и считывает значение первого счетчика 15 на вход блока 23 отображения, который отображает интервал времени tn, на котором наступила Авария, т.е. нара- 50 ботку на отказ. После восстановления канала связи сигнал «Канал восстановлен через второй вход устройства поступает на R-вход RS-триггера 19, на S-входе которого присутствует сигнал «Норма. На выходе

RS-триггера 19 уровень логической «Ь, ко- 55 ражения, первый вход счетчика ошибок яв- торый открывает первый ключ 8 и подклю-ляется первым входом устройства, второй

чает с помощью четвертого ключа 11 вы-вход соединен с выходом формирователя

ход счетчика 1 ошибок к вычитаемому интервала времени, а выход через блок

входы первого 20 и второго 21 блоков памяти, в которых хранятся на протяжении всей работы устройства. При несоответстботы делителя 18.

Формула изобретения

Устройство для прогнозирования состояния дискретного канала связи, содержащее блок оценки прогноза, формирователь интервала времени и последовательно соединенные счетчик ошибок, блок прогнозирования, первый дешифратор и блок отобвходу второго сумматора 14. Сигналы формирователя 2 интервала времени через открытый первый ключ 8 поступают на входы счетчика 16, првого блока 20 иамяти и счи- тывают сигналы «Ошибка, П|, П2, пз,...,Пй на суммируюший вход второго сумматора 14, на вычитаюш,ий вход которого поступают сигналы «Ошибка n l, nz, п з,..., n k с выхода счетчика 1 ошибок. С выхода второго сумматора 14 разностные сигналы ni-П2,

пз-п 2, пз-п з, в моменты времени

равления, соответствующий моменту вре- мени IN, для которого необходимо опреде «, определенное в предыдущем цикле, по- ступает на вход первого сумматора 13. Кролить количество ошибок , поступает через элемент 22 задержки на вход второго блока 21 памяти, с выхода которого количество ошибок п для момента времени

ме того, сигнал управления открывает второй ключ 9. Значение цикла N измерения с выхода второго дешифратора 6 через второй ключ 9 поступает на управляющий

рой ключ 9 поступает на управляющий

вход делителя 18 и устанавливает его коэффициент деления, равный N. Пятый ключ 12 открыт и значения третьего счетчика 17 поступают на информационный вход делителя 18, на выходе которого присутствует сигнал частного рование величин PN и Дп. На выходе пер- вого сумматора 13 присутствует величина,

(П1-rii) + (П2-П2) + (пз-Пз) + + () ли

Первый сумматор 13 производит суммиет сигнал частного рование величин PN и Дп. На выходе пер- вого сумматора 13 присутствует величина,

пирание третьего ключа 10 и сбрасывание третьего счетчика 17 в исходное состояние. По восстановлении связи процесс анализа повторяется. Время задержки элемента 22 выбрано исходя из времени достоверной ра ражения, первый вход счетчика ошибок яв- ляется первым входом устройства, второй

боты делителя 18.

Формула изобретения

Устройство для прогнозирования состояния дискретного канала связи, содержащее блок оценки прогноза, формирователь интервала времени и последовательно соединенные счетчик ошибок, блок прогнозирования, первый дешифратор и блок отобоценки прогноза подю1ючен к другому входу блока прогнозирования, выход которого подключен к другому входу блока оценки прогноза, отличающееся тем, что, с целью повышения достоверности прогнозирования, в него введены первый счетчик, последовательно соединенные RS-триггер, первый ключ, второй счетчик, второй дешифратор, второй ключ, делитель, первый сумматор и третий дешифратор, последовательно соеди- ненные третий ключ, четвертый ключ, первый блок памяти, второй сумматор, третий счетчик и пятый ключ, последовательно соединенные элемент задержки и второй блок памяти, выход которого подключен к другому входу первого сумматора, а другой вход соединен с выходом третьего ключа, информационный вход которого соединен с выходом счетчика ошибок, а управляющий

вход соединен с выходом первого дешифратора, с другими входами второго и третьего счетчиков, с S-входом триггера и с управляющим входом первого счетчика, выход которого подключен к второму входу блока отображения, а информационный вход соединен с выходом формирователя интервала времени и с другим входом первого ключа, выход кот.орого подключен к другому входу первого блока памяти, / -вход триггера является вторым входом устройства, а выход подключен к другому входу четвертого ключа, другой выход которого подключен к другому входу второго сумматора, выход третьего дешифратора подключен к третьему входу блока отображения, вход элемента задержки соединен с управляющими входами второго и третьего ключей и является третьим входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для прогнозирования состояния дискретного канала связи | 1987 |

|

SU1501288A1 |

| Устройство для прогнозирования состояния дискретного канала связи | 1989 |

|

SU1658397A2 |

| Устройство для прогнозирования состояния дискретного канала связи | 1989 |

|

SU1688420A1 |

| Устройство для прогнозирования состояния дискретного канала связи | 1987 |

|

SU1497749A2 |

| УСТРОЙСТВО ДЛЯ ПРОГНОЗИРОВАНИЯ СОСТОЯНИЯ ДИСКРЕТНОГО КАНАЛА СВЯЗИ | 2014 |

|

RU2543957C1 |

| Устройство для прогнозирования состояния дискретного канала связи | 1986 |

|

SU1345360A2 |

| Устройство для оценки качества дискретного канала связи | 1987 |

|

SU1494238A2 |

| Устройство измерения качества каналов передачи дискретной информации | 1986 |

|

SU1358105A2 |

| Устройство измерения качества каналов передачи дискретной информации | 1989 |

|

SU1695522A2 |

| Устройство измерения качества каналов передачи дискретной информации | 1984 |

|

SU1197123A2 |

Изобретение относится к электросвязи и повышает достоверность прогнозирования. Устройство содержит счетчик 1 ошибок, формирователь 2 интервала времени, блок 5x2 3 прогнозирования, блок 4 оценки прогноза, дешифраторы 5-7, ключи 8-12, сумматоры 13 и 14, счетчики 15-17, делитель 18, RS- триггер 19, блоки 20 и 21 памяти, эл-т 22 задержки, блоки 23 отображения. Спрогнозированное число ошибок сравнивается с фактическим в блоке 4. При несовпадении кол- ва ошибок на величину, превышаюш,ую допустимую погрешность прогноза, блок 4 формирует сигнал, уточняющий алгоритм работы блока 3.. В дешифраторе 5 ожидаемое кол-во ошибок сравнивается с установленным пороговым значением, и на выходе формируется сигнал оценки качества канала связи, к-рый поступает в блок 23. 1 ил. со со К5 СО со

| Устройство для прогнозирования состояния дискретного канала связи | 1981 |

|

SU1003362A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-06-23—Публикация

1986-02-06—Подача