Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных ЭВМ с приоритетным обслуживанием потока заявок.

Цель изобретения - расширение области применения устройства за счет обеспечения независимой коммутации номера приоритетного канала и запроса.

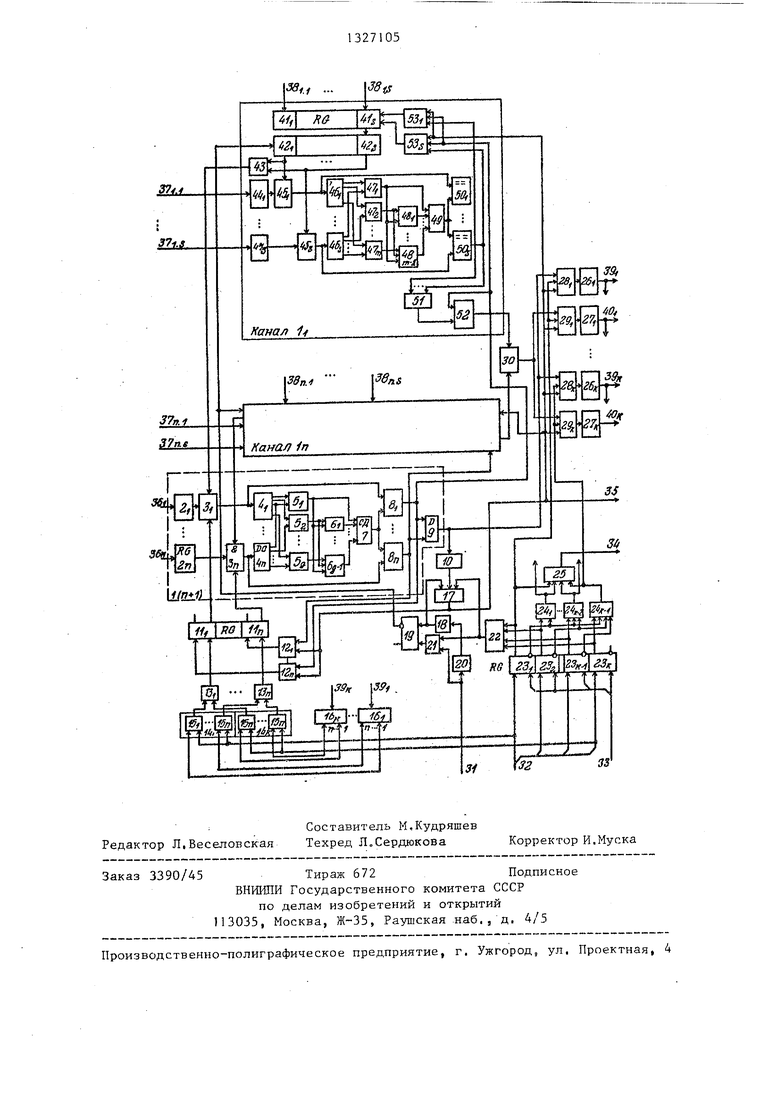

На чертеже представлена структурная схема;устройства.

Устройство содержит каналы 1,группу регистров 2 приоритета последнего канала 1, группу блоков элементов И 3 последнего канала 1, группу дешифраторов 4 последнего канала 1, группу элементов ИЛИ 5 последнего канала I , группу элементов 6 запрета последнего канала 1, шифратор 7 последнего канала 1, группу схем 8 сравнения последнего канала j шифратор 9 последнего канала 1, элемент ИЛИ 10, регистр 11 занятости каналов, группу элементов И 12, группу элементов ИЛИ 13, блок 14 групп элементов И 15, группу дешифраторов 16 номера каналов, элемент И 17, одновиб- ратор 18, триггер 19, элемент 20 за- держ1си, элемент И 21, элемент 1-ШИ 22, регистр 23 готовности процессоров, группу элементов И 24, шифратор 25, группу регистров 26 номера канала, группу регистров 27 номера абонентаj группу блоков элементов И 28,, группу блоков элементов И 29, блок элементов ИЛИ 30, вход 31 запуска устрой10

Устройство .работает следующим о разом.

Исходное состояние устройства х рактеризуется тем, что регистры 1 23, 26, 27 и триггер 19 установлен в состоянии О (не показано).

Б регистры 2 и регистры 44 кана лов 1 принимаются приоритетные код по входам 36 и 37 соответственно. Сигналы готовности процессоров по входам 32 поступают в соответствую щие разряды регистра 23, устанавли вая их в единичное состояние. При .g этом на выходе элемента РШИ 22 фор руется единичный сигнал, открывающ по второму входу элемент И 21.

Если в регистр 23 приняты сигна готовности от двух процессоров, то разряды 23 и 23 установлены в 1 Сигнал нулевого выхода разряда 23 закрывает элементы И 24, и на вход шифратора 25 формируется двоичный код 100, Единичным сигналом с выхо 25 да 23 открываются по вторым управ ляющим входам блоки элементов И 28 и 29 .

Так как триггер 19 находится в состоянии О, то высоким уровнем с Нулевого его входа входные цепи гистров 42 всех каналов открыты по информационным входам. При этом пр нятые запросы по входам 38 в регис ры 41 каналов передаются в соответ ствующие разряды буферных регистров- 42 каналов.

Так как регистр занятости каналов П находится в состоянии О, то единичными уровнями с нулевых е

20

30

ЗБ

ства, входы. 32 готовности процессоров, 40 выходов разрешается работа блоков

элементов И 3. При наличии запросо во всех каналах блоки- элементов И открываются и на информационных вх дах блоков элементов И 28 формируе

устройстваI входы 33 занятости процессоров устройства, выходы 34 номера процессора устройства,, сигнальньш выход 35 устройства, входы 36 кодов приоритета каналов устройства, вко™ ды 37 кодов приоритета запросов устройства, запросные входы 38 устройства, выходы 39 номера канал: а устройства, выходы 40 номера абонента устройства и в каждом канале 1, кроме последнего, регистр 41 запросов, буфер- ный регистр 42 запросов,элемент Mnii 43 группу регистров 44 приоритета запросов, группу блоков элементов И 45, группу дешифраторов, 463 группу элементов или 47, группу элементов 48 запрета, шифратор 49,-группу схем 50 сравнения, шифратор 51, блок элементов И 52 и группу элементов И 53,

0

Устройство .работает следующим образом.

Исходное состояние устройства характеризуется тем, что регистры 11, 23, 26, 27 и триггер 19 установлень в состоянии О (не показано).

Б регистры 2 и регистры 44 каналов 1 принимаются приоритетные коды по входам 36 и 37 соответственно. Сигналы готовности процессоров по входам 32 поступают в соответствующие разряды регистра 23, устанавливая их в единичное состояние. При g этом на выходе элемента РШИ 22 формируется единичный сигнал, открывающий по второму входу элемент И 21.

Если в регистр 23 приняты сигналы готовности от двух процессоров, то разряды 23 и 23 установлены в 1 Сигнал нулевого выхода разряда 23 закрывает элементы И 24, и на входе шифратора 25 формируется двоичный код 100, Единичным сигналом с выхо- 5 да 23 открываются по вторым управляющим входам блоки элементов И 28 и 29 .

Так как триггер 19 находится в состоянии О, то высоким уровнем с Нулевого его входа входные цепи регистров 42 всех каналов открыты по информационным входам. При этом принятые запросы по входам 38 в регистры 41 каналов передаются в соответствующие разряды буферных регистров- 42 каналов.

Так как регистр занятости каналов П находится в состоянии О, то единичными уровнями с нулевых его

0

Б

40 выходов разрешается работа блоков

элементов И 3. При наличии запросов во всех каналах блоки- элементов И 3 открываются и на информационных входах блоков элементов И 28 формирует g ся двоичный код приоритетного канала 1005 а на информационных входах блоков элементов И 29 - двоичный код приоритетного абонента приоритетного канала 010,

По сигналу, поступающему по входу 31, через открытьй элемент И 21 устанавливается триггер 19 в состояние 1. При этом единичный сигнал с синхронизирующих входов буферных

gg регистров 42 всех каналов снимается, фиксируя в них принятые запросы в цикле ра с пр еделе ния,

Через некоторое время, определяемое элементом 20 задержки, запускает50

ся одновибратор 18, устанавливающий триггер 19 в состояние О. Одновременно импульс одновибратора 18 через открытьш элемент Н 17 по второму и третьему входам поступает на вьп4од 35 (используется в ЭВМ в качестве сигнала прерывания и означает наличие информации в регистрах 26 и 27).

Одновременно через элемент И 12 устанавливается в состояние 1 разряд П регистра занятости каналов, закрепляя тем самым выбранный канал за первым процессором и исключая из анализа в очередном цикле приоритетный код четвертого канала. Кроме того, в состояние устанавливается через элемент И 53, в четвертом канале второй разряд регистра запросов 41, в регистр 26 через открытые блоки элементов И 28 принимается двоичньп код номера четвертого канала, а в регистр 27 - двоичный код номера второго абонента этого канала через открытые элементы 52 и элементы ИЛИ 30 .

По сигналу с выхода 35 ЭВМ организует передачу содержимого регистров 26 и 27 первому процессору: по входу 33., из ЭВМ выдается сигнал занятости первого процессора. При этом в устройстве первый разряд регистра 23 устанавливаемся в состояние О и на выходе шифратора 25 формируется двоичный код номера второго процессора 010, поступающий на выходы 34.

Так как на выходе элемента ИЛИ 22 поддерживается единичный уровень, то очередным импульсом опроса по входу 3 триггер 19 через элемент И 21 устанавливается в состояние 1 и аналогично рассмотренному в регистры 26 и 27 принимаются соответственно двоичные коды номера следующего по приоритету канала и приоритетного абонента в этом канале. Одновременно третий разряд, регистра 1 1 через элемент И 12 устанавливается в состояние 1, закрепляя за вторым процессором третий канал, чем исключается из анализа в очередном цикле приоритетный код третьего канала.

По сигналу на выходе 35 ЭВМ передает для обслуживания второму процессору номера канала и абонента из регистров 26;, и 27, , после чего сигналом занятости второй разряд регистра 23 устанавливается в состояние О

Пусть первый процессор закончил обслуживание абонента четвертого канала. При этом сигналом готовности, поступающим по входу 32 , первый разряд регистра 23 устанавливается в 1. Одновременно через элемент И 15 блока 14 и элемент ИЛИ 13 четвертый разряд регистра П устанавливается в

состояние О, чем разрешается анализ приоритетного кода четвертого канала при наличии в этом канале запросов. Так как элемент И 21 открьгоается единичным сигналом с выхода элемента ИЛИ 22, то импульсом опроса триггер 19 устанавливается в состояние 1. В дальнейшем устройство работает аналогично рассмотренному,

Вьщача сигналов опроса, занятости

и-готовности процессоров производится в строго определенные моменты времени. Так, очередной импульс опроса подается после передачи сигнала занятости процессора, а сигнал готовности процессора - перед очередным сигналом опроса. Последнее условие необходимо для того, чтобы после установки в О разряда регистра занятости каналов 11 на входах элемента ИЛИ 10 по завершении переходных процессов в . элементах И 3, дешифраторах 4, элементах ИЛИ 5, элементах группы запрета 6,шифраторе 7, схемах сравнения 8 и шифраторе У можно было

бы подавать импульс опроса..

При необходимости перераспределения приоритетов каналов либо запросов в кайалах производится приведение устройства в исходное состояние, занесение кодов приоритетов и запуск его сигналом опроса.

Формула изобретения

45

50

Многоканальное устройство приоритета для распределения заявок по процессорам, содержащее блок элементов ИЛИ, одновибратор, группу дешифраторов номера канала, первую группу блоков элементов И, группу регистров номера абонента, вторую группу блоков элементов И, группу регистров номера канала, первую группу элементов И, первый элемент ИЛИ и п+1 ка- 55 налов (п - число запросов), причем каждый канал, кроме последнего, содержит буферный регистр запросов, S регистров приоритета (S - число абонентов), группу из S блоков эле

51

ментов И, S дешифраторов, группу из m элементов ИЛИ (т 2 ), группу из т-1 элементов запрета, два шифратора, группу из S схем сравнения, элемент ИЛИ, блок элементов И, причем информационные входы регистров приоритета канала являются входами кодов приоритета устройства, выходы регистров приоритета канала соединены с информационными входами соответствующих блоков элементов И канала, выходы которых подключены к входам соот- ветствуюЕщх дешифраторов канала, j-й выход каждого i-ro депшфратора каналта (i 1,2,...,S; j ,2,.., m) соединен с i-м входом j-ro элемен та ИЛИ группы канала, выход первого элемента Ш1И группы канал.а подключен к первому входу первого шифратора и к первым инверсным входам элементов запрета группы канала, выход р-го элемента ИЛИ группы канала (р 2,3, .,,т) соединен с прямым входом (р-1 го и р-ми инверсными входами с первого по (га-)-и элементов запрета груп- пы канала, выход 1-го элемента запрета (1 ,2,.... ,т-1) канала соединен с (1+1)-м входом первого шифратора канала, выходы которого подключены к первым входам схем сравнения группы канала, вторые входы каждой из которых соединены с выходами соответствующих блоков элементов И группы канала, выходы схем сравнения группы канала подключены к входам второго шифратора канала, выходы которого под- ключеьы к информационным ззходам блока элементов И канала, выходы которого соединены с соответствующей группой входов блока элементов ИЛИ канала, выходы буферного регистра запросов канала соединены с управляющими Iвходами одноимен1й1х блоков элементов И группы и с входами элемента Ш1И канала, последний канал содерлшт группу из п регистров приоритета, группу из п блоков элементов И, п дешифраторов, группу из g элементов ИЛИ группу из g-1 элементов запрета (g 2), два шифратора и группу из п схем сравнения J при чем входы регистров приоритета группы являются входами приоритетов соответствующих каналов устройства 5 выходы регистров ; приоритета группы соединены с инфор- мационными входами соответствующих блоков элементов И группы, выходы которых подключены к входам соответст

ш

15

0

71

5

05 6

вующих дешифраторов и к первым входам соответствуюшдх схем .сравнения группы, уз-и выход каждого у-го дешифратора ( 1 ,2п, /3 1,2,.. .,g)

соединен с/}-м входом -го элемента ШП группы, выход первого элемента ИЛИ группы подключен к первому входу первого шифратора и к первым инверсным входам элементов запрета группы, выход z-ro элемента ИЛИ (z 253,...,g) группы соединен с прямым входом (z-l)-ro и z-ми инверсными входами с z-ro по (g-1)-и элементов запрета группы, выход t-ro элемента запрета группы (t 1,2,,.., g-1) соединен с (С+1)-м входом первого шифратора, выходы которого соединены с вторыми входами схем сравнения группы, выходы которых подключены к входам второго шифратора и к управляющим входам блока элементов И соответствующего канала, первый управляющий вход каждого блока элементов И группы соединен с выходом элемента ИЛИ одноименного канала, выходы второго шифратора подключены к информационным входам первого блока элементов И первой группы, выходы которых соединены с входами первого регистра номера канала группы, выходы которого являются первой группой выходов номера канала устройства, выходы блока элементов ИЛИ подключены к информационным входам первого блока элементов И второй группы, выходы которых подключены к входам первого регистра номера абонента группы, выходы которого являются первой группой выходов номера абонента устройства, отличающееся тем, что, с целью расширения области применения устройства за счет возможности независимой коммутации номера приоритетного канала и запроса, в него введены регистр занятости каналов, группа элементов ИЛИ, вторая группа из k-1 элементов И, блок из k групп элементов И (kчиcлo процессоров) 5 группа из k-2 дешифраторов номера кана0 )ла, два элемента И, триггер, второй элемент ИЛИ, регистр готовности процессоров, шифратор номера процессора, элемент задержки, а в канале, кроме последнего, регистр за5 просов и группа из S элементов И,

причем вход запуска устройства соединен с первым входом первого элемента И и Через элемент задержки - с

0

5

0

5

71

входом оДновибратора, выход которого подключен к первому входу второго элемента И и к нулевому входу триггера, нулевой выход которого подключен к синхронизирующим входам буферных регистров запросов всех каналов, единичные выходы регистра готовности процессоров подключены к входам первого элемента ИЛИ, выход которого соединен с вторым входом первого зле- мента И и с вторьм входом второго : элемента И, выход первого элемента И подключ ен к единичному входу триггера, первый вход g-ro элемента И второй группы .(g l,2,,.,,k-l) соединен с единичным выходом (g+l)-ro разряда регистра готовности процессоров, второй и последующие входы элементов И второй группы соединены с инверсными выходами разрядов регистра готовнос- ти процессоров, единичньй выход первого разряда регистра готовности процессоров подключен к первому входу шифратора номера процессора и к первым управляющим входам первых блоков элементов И первой и второй.групп, выход g-ro элемента И второй группы соединен с (g+l)-M входом шифратора номера процессора, выходы которого являются выходами номера процессора устройства, и с первым управляющим входом элементов И (g+l)-x блоков элементов И первой и второй групп, выходы второго шифратора (п+1)-го канала подключены к входам второго зле мента ИЛИ, выход которого соединен с третьим входом второго элемента И, выход которого является сигнальным выходом устройства и подключен к вторым управляющим входам всех блоков элементов И первой и второй групп, к первым входам элементов И первой группы и к первым входам элементов И групп всех п каналов, выход у-и схем сравнения группы (п+1)-го канала сое

058

динен с вторыми входами элементов И группы j--rQ канала и с вторым входом j-ro элемента И первой группы, выход которого подключен к прямому входу у-го разряда регистра занятости каналов. Нулевой выход которого соединен с вторым управляющим входом одноименного блока элементов И (h+1)-го канала, выходы -го регистра номера канала группы (Е 2,3,..,, 1с ) являются -й группой выходов номера канала устройства, выходы каждого регистра номера канала группы подключены к входам одноименного дешифратора номера канала группы,у-й выход f -го дешифратора номера канала группы соединен с первым входом -го элемента И группы блока групп элементов И, выход у-го элемента И Е-й группы блока групп элементов И соединен с -м входом -v-ro элемента ИЛИ группы, выхоД которого подключен к нулевому входу j-ro разряда регистра занятости каналов, выход i-й схемы сравнения каждого канала, кроме (п+1)-го, соединен с третьим входом i-ro элемента И группы своего канала, выход которого соединен с входом сброса i-ro разряда регистра запросов, входы кoтopo o являются соответствующей группой входов запросов устройства, выходы регистра запросов подключены к входам разрядов буферного регистра запросов своего канала, нулевые входы регистра готовности процессоров являются входами занятости процессоров устройства, вторые входы элементов И 6-й группы блока групп элементов И подключены к единичному входу -го разряда регистра готовности процессоров единичные входы разрядов которого являются входами готовности процессоро устройства, выходы регистров номера , абонента являются выходами номера абонента устройства.

39,

гг

3S

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

| Устройство приоритета для выбора групповых заявок | 1985 |

|

SU1319030A1 |

| Устройство приоритета с шифрацией номера канала и абонента | 1984 |

|

SU1247872A1 |

| Устройство для обслуживания групповых приоритетных запросов | 1990 |

|

SU1753473A1 |

| Устройство для обслуживания группы запросов | 1988 |

|

SU1562913A1 |

| Устройство переменного приоритета | 1986 |

|

SU1383353A1 |

| Устройство для организации доступа к ресурсам | 1988 |

|

SU1608663A1 |

| Многоканальное устройство для организации доступа к ресурсам | 1986 |

|

SU1322284A1 |

| Многоканальное устройство приоритета | 1985 |

|

SU1283765A1 |

| Устройство переменного приоритета | 1983 |

|

SU1151964A1 |

Изобретение относится к вычислительной технике и может найти применение в многопроцессорных ЭВМ с приоритетным обслуживанием потока заявок. Цель изобретения - расширение области применения устройства за счет обеспечения коммутации номера приоритетного канала и запроса. Устройство содержит два элемента ИЛИ, две группы элементов ИЛИ, одновибратор, два дешифратора номера канала, группу регистров номера абонента, группу регистров номера канала, блок групп элементов И,п+1 каналов (п - число запросов), каждый из которых, кроме последнего, содержит буферный регистр запросов, S регистров приори тета (S - число абонентов), S блоко в элементов И, S дешифраторов, группу из m элементов ИЛИ (т 2), группу из m-I элементов запрета, два шифра-v тора, группу из S схем сравнения, элемент ШИ, блок элементов И, последний канал содержит п регистров приоритета, п групп элементов И, h дешифраторов, группу из g элементов ИЛИ (g 2), группу из g-1 элементов запрета, два дешифратора и группу из п схем сравнения. В устройстве обеспечивается независимая выдача номера накала и номера абонента соответствующих процессоров. ил. i (Л со ГС

Составитель М.Кудряшев

Редактор Л.Веселовская Техред ЛоСердюкова Корректор И.Муска

Заказ 3390/45

Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Рауп1ская .н.аб. , д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Приоритетное устройство для обслуживания запросов в порядке поступления | 1984 |

|

SU1242949A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство приоритета с шифрацией номера канала и абонента | 1984 |

|

SU1247872A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-30—Публикация

1985-10-09—Подача