Изобретение относится к импульсной тех нике и может быть использовано при построении устройств анализа входных сигналов.

Целью изобретения является расширение функциональных возможностей за счет обеспечения однократности формирования выходного сигнала при пульсирующем входном напряжении.

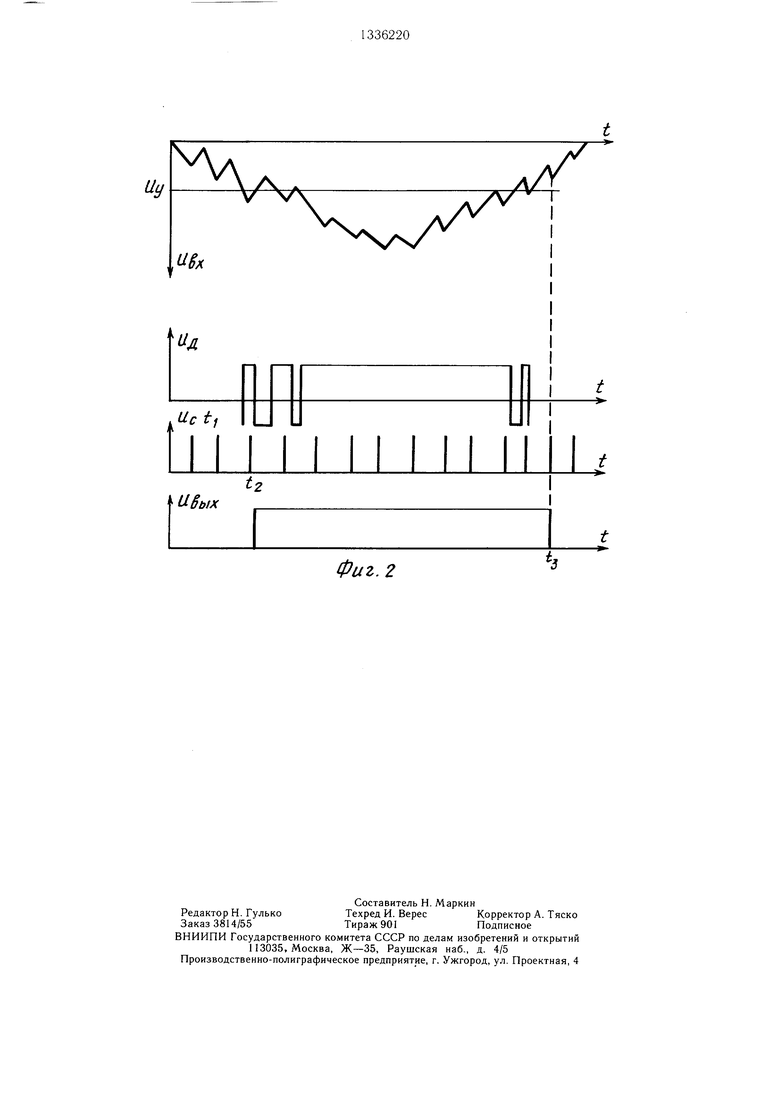

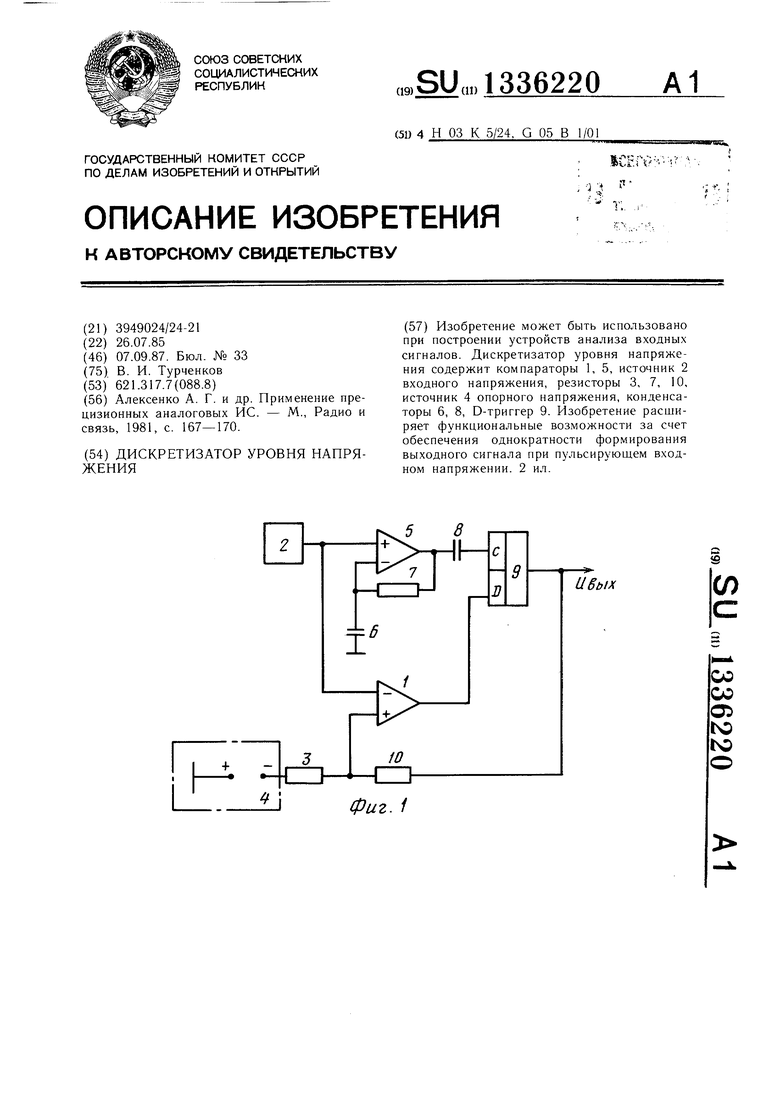

На фиг. 1 представлена структурная схема дискретизатора уровня напряжения; на фиг. 2 - временные диаграммы его работы.

Дискретизатор уровня напряжения содержит первый компаратор 1, первый вход которого подключен к источнику 2 входного напряжения, а второй вход через первый резистор 3 - к источнику 4 опорного напряжения, второй компаратор 5, неинвертирующий вход которого соединен с источником 2 входного напряжения, а неинвертирующий вход подключен через первый конденсатор 6 к щине нулевого потенциала, через второй резистор 7 к выходу второго компаратора 5, подсоединенного через второй конденсатор 8 к тактовому входу D-тригге- ра 9, информационный вход которого соединен с выходом первого компаратора 1, а выход подсоединен через третий резистор 10 к неинвертирующему входу первого компаратора 1.

Устройство работает следующим образом.

Если напряжение на инвертирующем входе первого компаратора 1 меньще напряжения на его неинвертирующем входе, то напряжение на выходе первого компаратора 1 равно логическому нулю и напряжение на выходе D-триггера 9 также равно нулю.

В момент времени t, (фиг. 2) напряжение на инвертирующем входе компаратора 1 превышает напряжение на его неинвертирующем входе и на D-входе D-триггера формируется напряжение, соответствующее логической единице.

Однако D-триггер не изменяет своего состояния, так как он установлен так, что его срабатывание происходит по положительному перепаду напряжения на тактовом С-входе.

Положительный перепад напряжения на тактовом С-входе формируется всякий раз, когда напряжение 0 источника 2 входного напряжения становится меньше напряжения на конденсаторе 6, т. е. в моменты умень- щения напряжения UBX, так как при этом на выходе формируется положительное на0

0

5

пряжение, от которого происходит разряд конденсатора 6 через резистор 7.

В момент ti (фиг. 2) совпадения положительного перепада напряжения на тактовом С-входе и логической единице на D-входе D-триггера 9, который срабатывает, и на его выходе напряжение станет равно логической единице, которая не изменяется при возврате компаратора 1 в исходное состояние на время, меньщее времени между максимальными пиками пульсирующего напряжения источника 2 входного напряжения.

D-триггер 9 возвращается в исходное

состояние в момент времени tj, (фиг. 2)

совпадения пика пульсирующего напряже5 ния с отсутствием напряжения на D-входе.

На выходе D-триггера 9 выходное напряжение с выхода делителя, например, установлено минус 0,5 В, которое после срабатывания D-триггера 9, с выхода которого формируется напряжение положительной полярности, становится, например, равно минус 0,4 В, что является дополнительным преимуществом предложенного дискретизатора уровня.

Выполняя напряжение уставки на делителе напряжения на резисторах, включенном между источником 4 напряжения и выходом триггера 9, можно устанавливать любой гистерезис на срабатывание дискретизатора уровня.

Формула изобретения

Дискретизатор уровня напряжения, содержащий компаратор, первый вход которого подсоединен к источнику входного напряжения, а второй вход - к источнику опорного напряжения, резистор, отличающийся тем, что, с целью расщирения функциональных возможностей за счет обеспечения однократности формирования выходного сигнала при пульсирующем входном напряжении, в него введен второй компаратор, D-триггер, первый и второй конденсаторы, при этом первый вывод резистора соединен с инверсным входом второго компаратора, подсоединенного через первый конденсатор к щине нулевого потенциала, а второй вывод соединен непосредственно с выходом второго компаратора и подключен через второй конденсатор к тактовому входу D-триггера, информационный вход которого соединен с выходом первого компаратора, причем неинвертирующий вход второго компаратора соединен с источником входного напряжения.

0

5

0

5

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки импульсов | 1991 |

|

SU1793536A1 |

| Широтно-импульсный модулятор | 1988 |

|

SU1619393A1 |

| Преобразователь напряжение - время | 1988 |

|

SU1654975A1 |

| Широтно-импульсный модулятор | 1985 |

|

SU1292173A1 |

| Устройство для форсированного управления электромагнитом постоянного тока | 1990 |

|

SU1714693A1 |

| Селектор импульсов по длительности | 1984 |

|

SU1226637A1 |

| Линейный преобразователь импульсных сигналов по длительности | 1984 |

|

SU1328930A1 |

| Устройство для контроля времени срабатывания электроклапана | 1990 |

|

SU1795421A1 |

| Преобразователь напряжение - интервал времени | 1986 |

|

SU1483638A1 |

| Дискретизатор уровней напряжения | 1986 |

|

SU1379938A1 |

Изобретение может быть использовано при построении устройств анализа входных сигналов. Дискретизатор уровня напряжения содержит компараторы 1, 5, источник 2 входного напряжения, резисторы 3, 7, 10, источник 4 опорного напряжения, конденсаторы 6, 8, D-триггер 9. Изобретение расширяет функциональные возможности за счет обеспечения однократности формирования выходного сигнала при пульсирующем входном напряжении. 2 ил. Ибых сл оо Сл 05 ГЧЭ N3 . 1

LJ L

1Л6ых

tz

Фиг. 2

| Алексенко А | |||

| Г | |||

| и др | |||

| Применение прецизионных аналоговых ИС | |||

| - М., Радио и связь, 1981, с | |||

| Прибор для запора стрелок | 1921 |

|

SU167A1 |

Авторы

Даты

1987-09-07—Публикация

1985-07-26—Подача