113

Изобретение относится к вычислительной технике и может быть использовано для построения управляющих автоматов и автоматов обработки дискретной информации.

Цель изобретения - экономия оборудования .

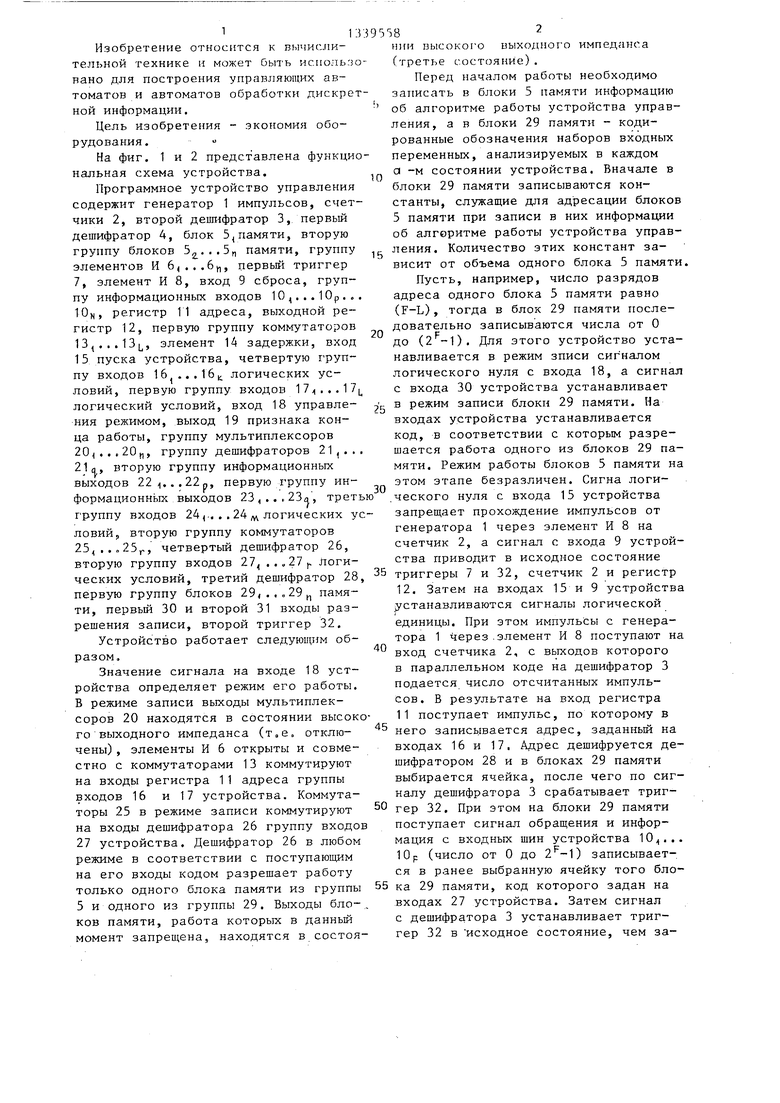

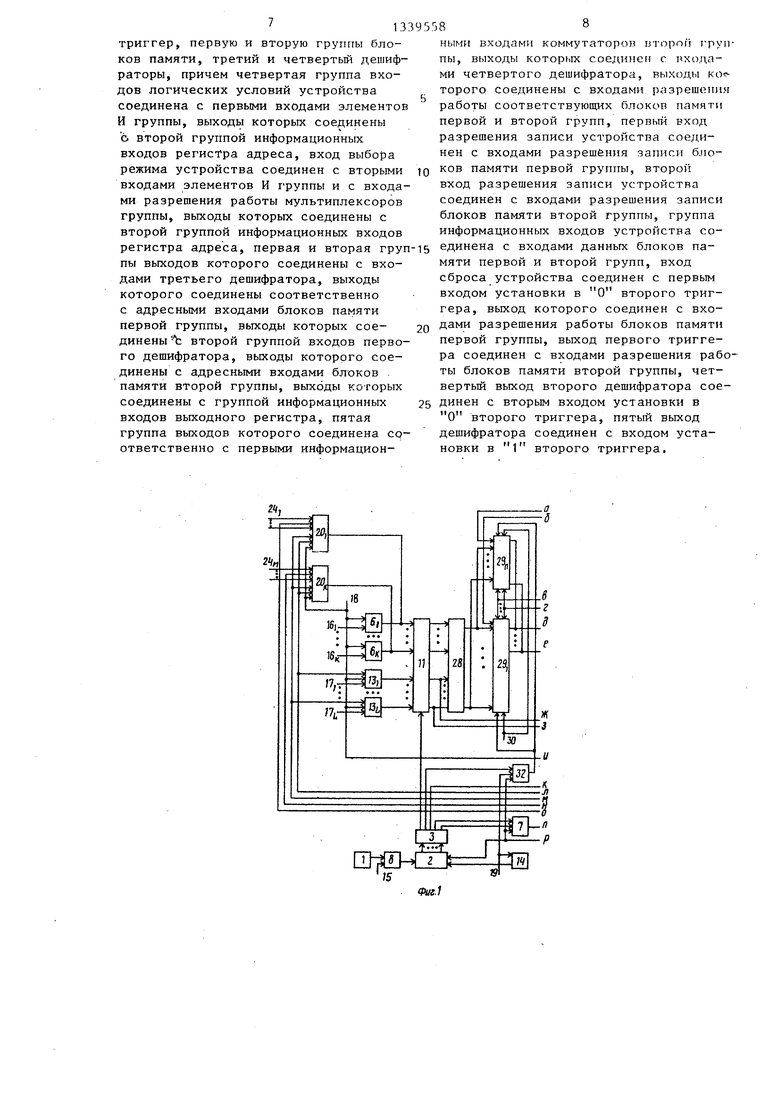

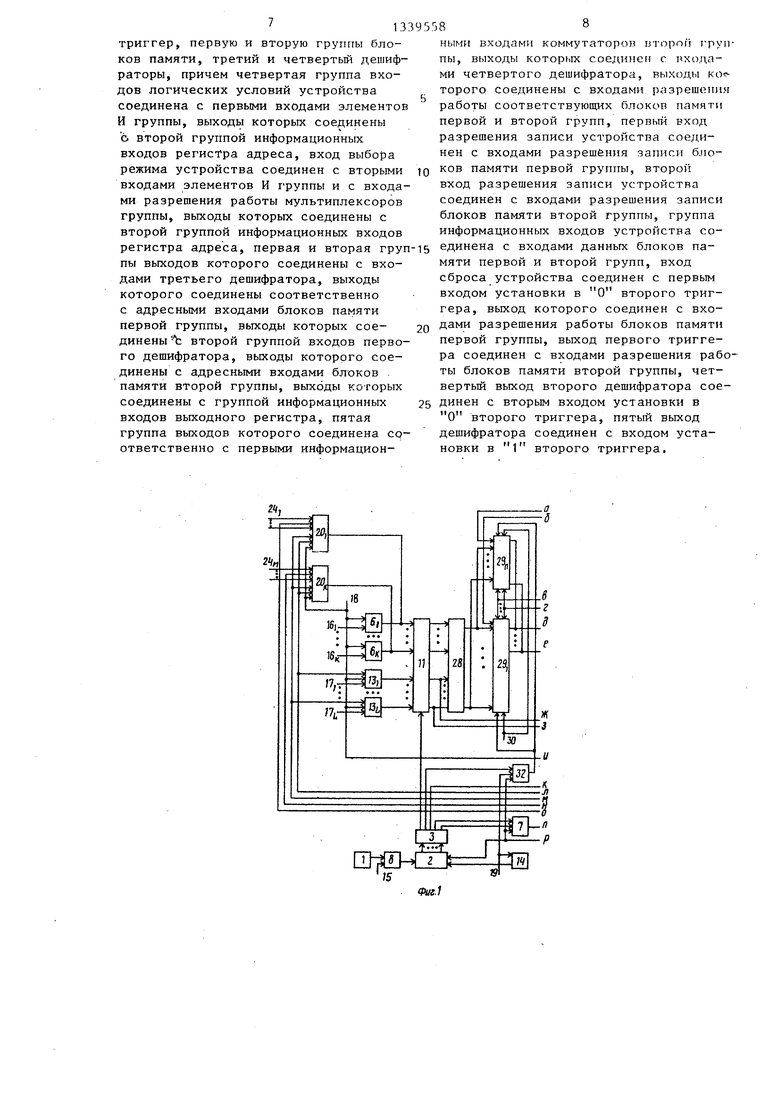

На фиг. 1 и 2 представлена функциональная схема устройства.

Программное устройство управления содержит генератор 1 импульсов, счетчики 2, второй деигифратор 3, первьй дешифратор 4, блок 5 памяти, вторую группу блоков ...5„ памяти, группу элементов И 6,,,6, первый триггер 7, элемент И 8, вход 9 сброса, группу информационных входов 10...10р.о. 10ц, регистр 11 адреса, выходной регистр 12, первую группу коммутаторов 13,...13ц, элемент 14 задержки, вход 15 пуска устройства, четвертую группу входов 16...16j логических условий, первую группу входов 17,..17 логический условий, вход 18 управле- ния режимом, выход 19 признака конца работы, группу мультиплексоров 20(...20f,, группу дешифраторов 21 . . , 21 а, вторую группу информационных выходов 22i...22p, первую группу информационных выходов 23,...23а, треть группу входов 24 (.... 24 ;у логических условий, вторую группу коммутаторов 25,..„25, четвертый дешифратор 26, вторую группу входов 27 ..„27 Логических условий, третий дешифратор 28, первую группу блоков 29«..о29 памяти, первый 30 и второй 31 входы разрешения записи, второй триггер 32.

Устройство работает следующим образом.

Значение сигнала на входе 18 устройства определяет режим его работы. В режиме записи выходы мультиплексоров 20 находятся в состоянии высокого выходного импеданса (т„е. отклю- чены), элементы И 6 открыты и совместно с коммутаторами 13 коммутируют на входы регистра 11 адреса группы входов 16 и 17 устройства. Коммутаторы 25 в режиме записи коммутируют на входы дешифратора 26 группу входов 27 устройства. Дешифратор 26 в любом режиме в соответствии с поступаюш 1м на его входы кодом разрешает работу только одного блока памяти из группы 5 и одного из группы 29. Выходы бло- , ков памяти, работа которых в данньм момент запрещена, находятся в состоя0

5

0

5

-SS2

НИИ высокого выходиог о импеданса (третье состояние).

Перед началом работы необходимо записать в бдоки 5 памяти информацию об алгоритме работы устройства управления, а в блоки 29 памяти - кодированные обозначения наборов входных переменных, анализируемых в каждом а -м состоянии устройства. Вначале в блоки 29 памяти записываются константы, служащие для адресации блоков

5памяти при записи в них информации

06алгоритме работы устройства управления. Количество этих констант зависит от объема одного блока 5 памяти.

Пусть, например, чнсло разрядов адреса одного блока 5 памяти равно (F-L), тогда в блок 29 памяти последовательно записываются числа от О до (2 1). Для этого устройство устанавливается в режим зписи сиг налом логического нуля с входа 18, а сигнал с входа 30 устройства устанавливает в режим записи блоки 29 памяти. На входах устройства устанавливается код, в соответствии с которым разрешается работа одного из блоков 29 памяти. Режим работы блоков 5 памяти на этом этапе безразличен. Сигна логи- .ческого нуля с входа 15 устройства запрещает прохождение импульсов от генератора 1 через элемент И 8 на счетчик 2, а сигнал с входа 9 устройства приводит в исходное состояние триггеры 7 и 32, счетчик 2 и регистр 12. Затем на входах 15 и 9 устройства устанавливаются сигналы логической единицы. При этом импульсы с генератора 1 через .элемент И 8 поступают на вход счетчика 2, с выходов которого в параллельном коде на дешифратор 3 подается число отсчитанных импульсов. В результате на вход регистра 11 поступает импульс, по которому в него записывается адрес, заданный на входах 16 и 17, Адрес дешифруется дешифратором 28 и в блоках 29 памяти выбирается ячейка, после чего по сигналу дешифратора 3 срабатывает триггер 32, При этом на блоки 29 памяти поступает сигнал обращения и информация с входных шин устройства 10,.. Юр (число от О до 2-1) записывается в ранее выбранную ячейку того блока 29 памяти, код которого задан на входах 27 устройства. Затем сигнал с дешифратора 3 устанавливает триггер 32 в исходное состояние, чем запрещает обращение к блокам 29 памяти, а также сигнализирует по выходу 19 о необходимости выставить новую информацию и новый адрес. При этом через элемент 14 задержки происходит сброс счетчика 2 в исходное состояни Процесс повторяется до тех пор, пока в блок памяти не будут записаны все числа от О до (2 -1).

Затем на входы 27 поступает.новый номер избранного блока 29 памяти и такая же информация записывается в него. Процесс подх отовки адресов заканчивается после записи адресной ни - 15 переводящий блоки 5 памяти в режим

формации во все блоки 29 памяти.

Затем производится запись в блоки 5 памяти информации об алгоритме рабо ты устройства управления. Для этого сигнал с входа 30 устанавливает блоки 29 памяти в режим считывания, а сигнал с входа 31 устанавливает блоки 5 памяти в режим записи. Далее происходит процесс, аналогичный записи информации в блоки 29 памяти.

Дешифратор 26 в соответствии с кодом на входах 27 устройства выбирает один из блоков 29 памяти для считывания информации и один из блоков 5 памяти для записи. Генератор 1, счетчик 2, дешифратор 3 и триггеры 7 и 32 управляют записью адреса в регистр 11, считыванием числа из блока 29 памяти и записью информации с шин устройства 10,.,,Юм в блок 5 памяти. По сигналу с дешифратора 3 в регистр 11 записывается адрес с входов 16 и 17 устройства,-который дешифруется дешифратором 28 и выбирает в блоке 29 памяти ячейку; из которой считывается число. При этом L старших разрядов адреса подаются на группу входов дешифратора 4, Затем по сигналу дешифратора 3 срабатывает триггер 32 и на блоки 29 памяти поступает сигнал обращения. При этом из блока 29 памяти считывается число от О до (), представляющее собой младшие разряды адреса ячейки в блоке 5 памяти, которые подаются на вторую группу входов дешифратора 4. Последний дешифрует адрес и выбирает ячейку в блоке 5 памяти. По сигналу дешифратора 3 срабатывает триггер 7, вследствие чего на блоки 5 памяти подается сигнал обращения и в избранную.ячейку блока 5 памяти записывается информа20

30

35

считывания, а сигнал с входа 30 пер ключает блоки 29 памяти в режим зап си. После этого в блоки 29 памяти записываются кодированные обозначен наборов входных переменных, анализи руемых в каждом а -м состоянии устр ства управления. Процесс записи ана логичен описанной выше записи адрес ных констант в блоки 29 памяти и уп

25 равляется генератором 1, счетчиком 2, дешифраторами 3, 26 и 28, тригге ром 32, По окончании записи блоки 2 памяти переключаются в режим считывания сигналом с входа 30, а сигнал логической единицы, поступающий на вход 18 устройства, переводит его в режим считывания.

При этом коммутаторы 13 и 25 ком мутируют выходы регистра 12, ключев элементы И 6 отключены от магистрал а выходы мультиплексоров 20 подключ ны к группе входов регистра 11, Затем подается импульсный сигнал логи ческого нуля на вход 9 устройства,пр водящий счетчик 2, триггеры 7 и 32 и регистр 12 в исходное состояние.

Процесс считывания информации из блоков 5 и 29 памяти аналогичен про цессу записи алгоритма работы устро ства в блоки 5 памяти и управляется генератором 1, счетчиком 2, дешифра торами 3, 4, 26 и 28, триггерами 7 32, При этом адреса считывания из б ков 29 памяти определяются совокупностью сигналов на третьей и четвер той группах выходов регистра 12 и соответствующих входах 24 устройств которые коммутируются в данном состоянии на вход регистра 11, Адреса считывания из блоков 5 памяти опре55 деляются совокупностью сигналов на третьей и четвертой группах выходов регистра 12 и соотвествующим числом (номером набора), считанных из блок

40

45

50

ция с шин 10,,., тем триггеры 7 и

10ц устройства. За- 32, а всед за ними

счетчик 2 приводятся в исходное состояние, выставляется новая информация на шинах 10 и новый адрес на входах 16 и 17 и процесс повторяется. Так происходит до заполнения избранного блока 5 памяти ,после чего на входы 27 подается новый код, избирающий новую пару блоков 5 и 29 памяти, и процесс повторяется. Он заканчивается после занесения информации об алгоритме работы устройства управления во все блоки 5 памяти;

Затем с входа 31 поступает сигнал.

0

5

считывания, а сигнал с входа 30 переключает блоки 29 памяти в режим записи. После этого в блоки 29 памяти записываются кодированные обозначения наборов входных переменных, анализируемых в каждом а -м состоянии устройства управления. Процесс записи аналогичен описанной выше записи адресных констант в блоки 29 памяти и уп5 равляется генератором 1, счетчиком 2, дешифраторами 3, 26 и 28, триггером 32, По окончании записи блоки 29 памяти переключаются в режим считывания сигналом с входа 30, а сигнал логической единицы, поступающий на вход 18 устройства, переводит его в режим считывания.

При этом коммутаторы 13 и 25 коммутируют выходы регистра 12, ключевые элементы И 6 отключены от магистрали, а выходы мультиплексоров 20 подключены к группе входов регистра 11, Затем подается импульсный сигнал логического нуля на вход 9 устройства,приводящий счетчик 2, триггеры 7 и 32 и регистр 12 в исходное состояние.

Процесс считывания информации из блоков 5 и 29 памяти аналогичен процессу записи алгоритма работы устройства в блоки 5 памяти и управляется генератором 1, счетчиком 2, дешифраторами 3, 4, 26 и 28, триггерами 7 и 32, При этом адреса считывания из блоков 29 памяти определяются совокупностью сигналов на третьей и четвертой группах выходов регистра 12 и соответствующих входах 24 устройства, которые коммутируются в данном состоянии на вход регистра 11, Адреса считывания из блоков 5 памяти опре5 деляются совокупностью сигналов на третьей и четвертой группах выходов регистра 12 и соотвествующим числом (номером набора), считанных из блока

0

5

0

БП

29 памяти. Номер пары блоков 5 и 9 памяти, из которых производятся г.чи- тьшанне, определяется совокупностью сигналов из пятой группы выходов ре- гистра 12 и соответственно сигналом с дешифратора 26. Это обеспечивает возможность наращивания памяти устройства до необходимой размерности решаемых задач. Мультиплексоры 20 коммутируют на вход регистра 11 в каждом q -м состоянии не более К вхо ных сигналов, С четвертой группы выходов регистра 12 снимаются функции доопределения состояний. Они служат для объединения состояний устройства в которых анализируется незначительн число входньсх переменных и позволяют экономить память устройства управления ,

В выходных сигналах блоков 29 па- закодированы номера наборов вхоных переменных, являющиеся младшей частью адресного слова блоков 5 памяти. В выходных сигналах блоков 5 памяти, поступающих на входы дешифратора 21, закодированы выходные функ- дйи устройства управления. При этом подгруппы выходных сигналов, посту, пающих на входы соответствую1цих деши раторов, выбраны так, что внутри их каждый из сигналов принимает истинное значение в моменты времени, не совпадающие с другими сигналами подгруппы. Это группа выходов 23 устройства. Выходные сигналы, для которых кодирование провести невозможно, выведены непосредственно на выход устройства.(группа выходов 22).

Формула изобретения

Программное устройство управления содержащее.генератор импульсов, счетчик, первый и второй дешифраторы, блок памяти, первую и вторую группы коммутаторов, первый триггер, элемент И, элемент задержки, регистр адреса, выходной регистра, группу мультиплексоров, группу дешифраторов причем вход управления режимом уст- ройства соединен с управляюшлми входами коммутаторов первой и второй групп, выходы первой группы коммутаторов соединены с первой группой информационных входов регистра адреса, первая группа выходов которого соединена с первой группой входов первого де1иифратора, выходы которого соединены с адресными входами блока па

5 0

5

о

0

5 0 5

5

58

мяти, пыхолм которого с(.)едииены соответственнее ( информационными входами выходного регистра, перная группа выходов KOTopoi O соединена с соответствующими входами дешифраторов группы, выходы которых соединены с первой группой Р5ьгходов устройства, вторая группа выходов выходного регистра соединена с второй группой выходов устройства, выход генератора соединен с первым входом элемента И, вход пуска устройства соединен с вторым элемента И, выход которого соединен с счетным входом счетчика, выходы которого соединены с входами второго дешифратора, первый выход которого соединен с входом разрешения записи регистра адреса, второй выход второго дешифратора соединен с входом установки в 1 первого триггера, третий выход второго дешифратора соединен с входом разрешения записи выходного регистра, вход сброса устройства соединен с входом сброса выходного регистра,. с первым входом сброса счетчика и с первым входом установки в О первого триггера, четвертый выход второго дешифратора соединен с вторым входом установки в .О первого триггера, с входом элемента задержки и с выходом признака конца работы устройства, выход элемента задержки соединен с вторым входом сброса счетчика, выход первого триггера соединен с входом разрешения обращения блока памяти, группа информационных входов устройства соединена с группой входов данных блока памяти, третья группа выходов вы - ходного регистра соединена соответственно с первыми информационными входами коммутаторов первой группы и с группой управляющих входов мультиплексоров группы, первая и вторая группы входов логических условий устройства соединены соответственно с вторыми информационными входами коммутаторов первой и второй групп, третья группа входов логических условий устройства соединена с первой группой информационных входов мультиплексоров группы, четвертая группа выходов выходного регистра соединена с второй группой информационных входов мультиплексоров группы, отличающееся тем, что, с целью экономии оборудования, устройство содержит группу элементов И, второй

713

триггер, первую и вторую группы блоков памяти, третий и четвертый дешифраторы, причем четвертая группа входов логических условий устройства соединена с первыми входами элементов И группы, выходы которых соединены о второй группой информационных входов регистра адреса, вход выбора режима устройства соединен с вторыми входами элементов И г руппы и с входами разрешения работы мультиплексоров группы, выходы которых соединены с второй группой информационных входов регистра адреса, первая и вторая груп пы выходов которого соединены с входами третьего дешифратора, выходы которого соединены соответственно с адресными входами блоков памяти первой группы, выходы которых соединены Ъ второй группой входов первого дешифратора, выходы которого соединены с адресными входами блоков памяти второй группы, выходы которых соединены с группой информационных входов выходного регистра, пятая группа выходов которого соединена соответственно с первыми информацион

8

ными входами коммутаторов iJTOpofi i-pyn- пы, выходы которых соединен с входами четвертого дешифратора, выходы торого соединены с входами разрешения работы соответствующих блоков памяти первой и второй групп, первый вход разрешения записи устройства соединен с входами разрешения записи блоков памяти первой группы, второй вход разрешения записи устройства соединен с входами разрешения записи блоков памяти второй группы, группа информационных входов устройства соединена с входами данных блоков памяти первой и второй групп, вход сброса устройства соединен с первым входом установки в О второго триггера, выход которого соединен с входами разрешения работы блоков памяти первой группы, выход первого триггера соединен с входами разрешения работы блоков памяти второй группы, четвертый выход второго дешифратора соединен с вторым входом установки в О второго триггера, пятый выход дешифратора соединен с входом установки в 1 второго триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентом | 1985 |

|

SU1287170A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1278869A1 |

| Программное устройство управления | 1983 |

|

SU1173414A1 |

| Программное устройство управления | 1985 |

|

SU1264171A2 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1982 |

|

SU1072036A1 |

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1986 |

|

SU1396147A1 |

| Многоканальное устройство для контроля систем управления | 1985 |

|

SU1345200A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

Изобретение.относится к вычислительной технике и может быть использовано для построения управляющих автоматов и автоматов обработки дискретной информации. Цель изобретения- сокращение аппаратурных затрат за счет экономии объема памяти автомата путем применения принципа двойного кодирования. Устройство содержит генератор, счетчик, четьфе дешифратора, два регистра, два триггера, элемент задержки, элемент И, две группы блоков памяти, две группы коммутаторов, группу ключевых элементов, группу мультиплексоров и группу дешифраторов. Цель достигается с помощью указанной совокупности признаков. 2 ил.

гч

ц 10/: 10,

П

j

в

-11

Qu

5,

7OV

. 3и

з;

к

л. м- но- пСоставитель А.Михайлов Редактор Е.Папп Техред М.ДВДЬККорректор Г.Решетник

Заказ 4223/39 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Ш

25,

26

г

2f

2

h-7-

k

.

23

22;

2Zp

7Dt

Фиг. 2

| Устройство для отделения твердой фазы из газового потока | 1984 |

|

SU1214171A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Программное устройство управления | 1983 |

|

SU1173414A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-23—Публикация

1986-05-28—Подача