ства, вход разрешения внешнего обмена блока управления обменом является одноименным входом устройства, вторая группа информационных входов-выходов выходного коммутатора соединена с группой выходов постоянной памяти команд, с группой информационных входов счетчика адреса, блока счетчиков, регистра косвенного адреса, группой входов кода адресации блока управления обменом, первой группой информационных входов второго коммутатора адреса, а также с группой информационных входов-выходов оперативного запоминающего блока контролера и первой группой информационных входов-выходов выходного коммутатора соответственно, первая группа выходов блока управления обменом соединена с группой управляющих входов блока счетчиков, первая группа выходов которого соединена с первой группой Входов блока управления обменом, вторая группа выходов блока управления обменом соединена с группой входов управления обменом блоков хранения сообщений группы, выход первого разряда третьей группы управляющих выходов блока управления обменом соединен с разрешающими входами блока магистральных элементов, первого, второго и третьего магистральных элементов, выходы второго и третьего разрядов третьей группы выходов блока управления обменом соединены соответственно со счетным и синхронизирующим входами счетчика адреса, третья группа выходов блока управления обменом соединена соответственно с информационным входом первого магистрального элемента, выходом запроса непосредственного доступа устройства, информационными входами второго и третьего магистральных элементов и с группой управляющих входов входного коммутатора, четвертая группа выходовблока управления обменом соединена с группой информационных входов коммутатора записи, пятая группа выходов блока управления обменом соединена соответственно с синхронизирующим входом регистра косвенного адреса, управлякяцим входом второго коммутатора адреса, синхронизирующим входом регистра исполнительного адреса, входами записи и обращения блока буферной памяти, шестая группа выходов блока управления обменом соединена с соответствующими управляющими входами записи блоков хранения сообщений группы, первьй управляюш 1Й выход блока управления обменом соединен с вторым управляющим входом коммутатора записи, второй управляющий выход блока управления обменом соединен с вторым управляющим входом коммутатора обращения, седьмая группа управляющих вькодов блока управления обменом соединена соответственно с первым и вторым управляющими входами выходного коммутатора, входами обращения и записи оперативного запоминающего блока контролле{ а и входом обращения постоянной памяти команд, вторая и третья группы выходов блока счетчиков соединены с второй и третьей группами входов блока управления обменом, выход управляющего разряда третьей группы выходов блока счетчиков соединен с третьими управляющими входами коммутатора записи, коммутатора обращения и- управляющим входом первого коммутатора адреса, четвертая группа выходов блока счетчиков соединена с второй группой информационных входов первого коммутатора адреса, пятая группа вькодов блока счетчиков соединена с груплой адресных входов оперативного запоминающего блока контроллера, выходы младщих разрядов пятой группы выходов блока счетчиков соединены с четвертой группой входов блока управления обменом, шестая группа выходов блока счетчиков соединена с группой адресных входов постоянной памяти команд, вход внешней записи блока управления обменом соединен с первым входом коммутатора записи, выходы регистра косвенного адреса соединены с первой группой входов сумматора, выходы которого соединены с второй группой информационных входов второго коммутатора адреса, выходы которого соединены с группой информационных входов регистра исполнительного адреса, выходы которого соединены с второй группой входов сумматора и с уруппой адресных входов блока буферной памяти, группа информационных входоввыходов блока буферной памяти соедииа с первой группой информационных входов-выходов выходного коммутатора, выходы всех разрядов счетчика адреса, кроме младшего, соединены с соответствующими информационными входами блока магистральных элемен-тов, группа информационных входоввыходов центрального оперативного запоминающего блока соединена с второй и третьей группами входов-выходов входного коммутатора, причем блок управления обменом содерзкит память микрокоманд, узел дещифраторов управления счетчиками, узел коммутлции внешних запоминающих блоков, регистр адреса, регистр микрокоманд коммутатор адреса, коммутатор управляющих сигналов, мультиплексор, дешифратор записи, дешифратор управления- обращением, генератор тактовых импульсов, триггер пуска, пять элементов И, при этом группа информационных входов дешифратора управления обращением соединена с группой одноименных входов дешифратора записи и образует первую Группу входов блока управления обменом, группа информационных входов мультиплексора образует вторую группу входов блока управления обменом, группа входов коммутатора управляющих сигналов образует третью группу входов блока управления обменом, первая группа информационных входов узла коммутации внешних запоминающих.блоков обра зует четвертую группу входов блока управления обменом, первый управляю щий вход коммутатора управляющих сиг налов является входом внешней записи блока управления обменом, единичный вход триггера пуска является входом пуска блока управления обменом, первый информационный вход мультиплексо ра является входом разрешения внешнего обмена блока управления обменом первая группа информационных входов коммутатора -адреса образует группу одноименных входов блока управления обменом, груйпа выходов узла дешифраторов управления счетчиками обра зует первую группу выходов блока управления обменом, группа выходов коммутатора управляющих сигналов образует вторую группу выходов блока управления обменом, группа выходов узла коммутации внешних запоминающих блоков образует третью группу выходов блока управления обменом группа выходов дешифратора записи образует четвертую группу выходов блока управления обменом, выход пер 143 вого элемента И, второй разряд первой группы выходов регистра микрокоманд, выходы второго и третьего элементов И и пятый разряд первой группы выходов регистра микрокоманд образуют пятую группу выходов блока управления обменом, группа выходов дешифратора управления обращением образует шестую группу выходов блока управления обменом, первый и четвертый разряды второй группы выходов регистра микрокоманд и выход четт вертого элемента И образуют седьмую группу выходов блока управления обменом, второй выход генератора тактовых импульсов соединен с первым входом первого элемента И и является первым управляющим выходом блока управления обменом, выход микрооперации разрешения обмена регистра микрокоманд является BTopbtM управляющим выходом блока, при этом в блоке управления обменом выход микрооперации конца команды регистра микрокоманд соединен с первым и вторым управляющими входами коммутатора адреса, вторая группа информационных входов которого соединена с выходом мультиплексора и группой немодифицируемьпс разрядов адресного выхода памяти микрокоманд, модифицируемый разряд адресного выхода которого соединен с вторым информационным входом мультиплексора, группа адресных входов которого соединена с группой выходов кодов логических условий памяти микрокоманд, операционная часть выходов которой соединена с группой информационных входов регистра микрокоманд, выход микрооперации конца работы блока которого соединен с первым входом пятого элемента И, выход которого соединен с нулевым входом триггера пуска, выход которого сое- динен с входом генератора тактовых импульсов, первый выход которого соединен с синхровходом регистра адреса, группа входов которого соединена с группой выходов коммутатора адреса, а группа выходов - с группой входов памяти микрокоманд, третий выход генератора тактовых им пульсов соединен с первым управляющим входом узла коммутации внешних запоминающих блоков и узла дешифраторов управления счетчиками, а также с первыми входами третьего и четвертого элементов И и вторым

управляющим вхадом дешифратора запи си, первый управляющий вход которого соединен с вторым управляющим входом коммутатора управляющих сигналов и с выходом микрооперации разрешения записи регистра микрокоманд, синхровход которого соединен с вторым входом пятого элемента И, с вторыми управляющими входами узла коммутации внешних запоминающих блоков и узла дешифраторов управления счетчиками, с первым входом второго элемента И .и с четвертым входом генератора тактовых импульсов, выход микрооперации управления обращением регистра микрокоманд соединен с управляющим

входом дешифратора управления обращением, первый, третий и четвертьй разряды первой группы выходов регистра микрокоманд соединены с вторыми входами первого, второго и третьего элементов И соответственно, пятый разряд второй группы выходов регистра микрокоманд соединен с вторым входом четвертого элемента И, третья и четвертая группы выходов регистра микрокоманд соединены соответственно с группами информационных входов узла дешифратора управления счетчиками и узла коммутации внешних запоминающих блоков.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Многоканальное микропрограммное устройство ввода-вывода | 1983 |

|

SU1104500A1 |

| Устройство для управления и обмена данными | 1986 |

|

SU1319042A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

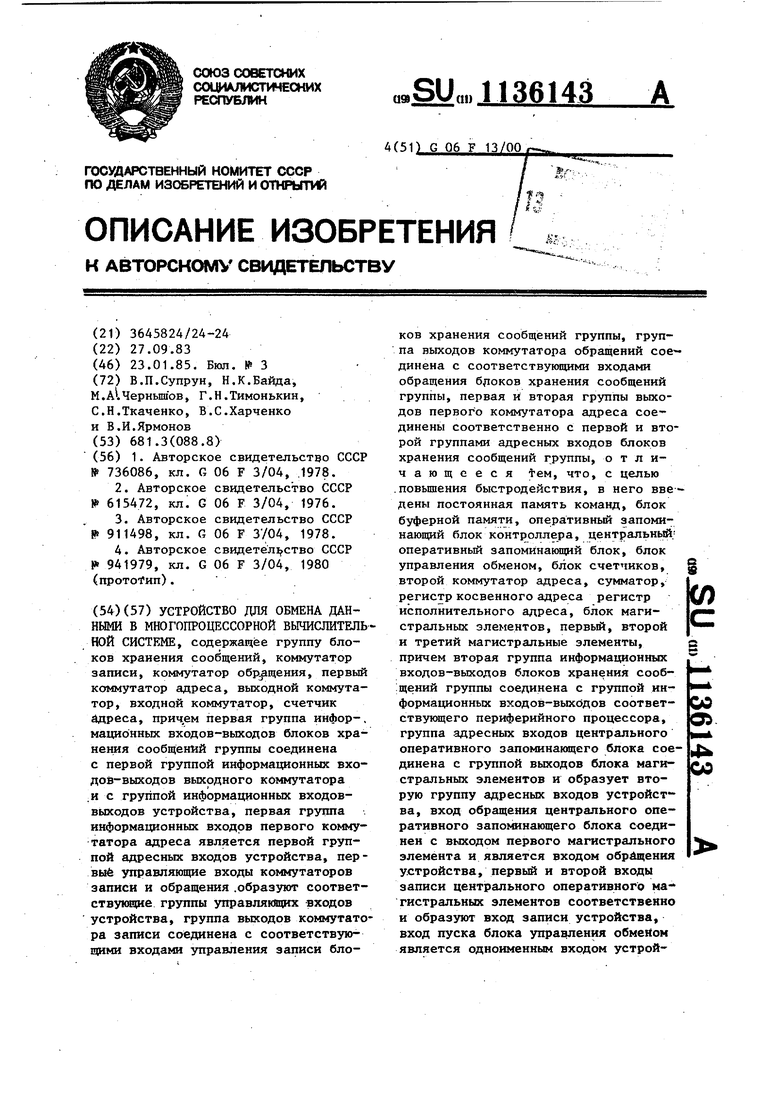

УСТРОЙСТВО ДЛЯ ОБМЕНА ДАННЫМИ В МНОГОПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ, содержащее группу блоков хранения сообщений, коммутатор записи, коммутатор обр.щения, первый коммутатор адреса, выходной коммутатор, входной коммутатор, счетчик реса, прич.ем первая группа инфор-, мационных входов-выходов блоков хранения сообщений группы соединена с первой группой информационных входов-выходов выходного коммутатора .и с группой информационных входоввыходов устройства, первая группа информационных входов первого коммутатора адреса является первой группой адресных входов устройства, первые управляющие входы коммутаторов записи и обращения .образуют соответствукяцие группы управлякзацих входов устройства, группа выходов коммутатора записи соединена с соответствующими входами управления записи блоков хранения сообщений группы, группа выходов коммутатора обращений сое динена с соответствующими входами обращения б токов хранения сообщений группы, первая и вторая группы выходов первого коммутатора адреса соединены соответственно С первой и второй группами адресных входов блоков хранения сообщений группы, отличающееся teM, что, с целью .повышения быстродействия, в него введены постоянная память команд, блок буферной памяти, оперативный запоминающий блок контроллера, центральный,оперативный запоминающий блок, блок управления обменом, блок счетчиков, второй коммутатор адреса, сумматор, (Л регистр косвенного адреса регистр исполнительного адреса, блок магистральных элементов, первый, второй и третий магистральные элементы, причем вторая группа информационных входов-выходов блоков хранения сооб:щений группы соединена с группой ин00 Од формационных входов-выходов соответствующего периферийного процессора, группа адресных входов центрального оперативного запоминающего блока сое4 динена с группой выходов блока магиСО стральных элементов и образует вторую группу адресных входов устройства, вход обращения центрального оперативного запо5в1нающего блока соединен с выходом первого магистрального элемента и является входом обращения устройства, первый и второй входы записи центрального оперативного магистральных элементов соответственно и образуют вход записи устройства, вход пуска блока управления обменом является одноименным входом устрой

Изобретение относится к вычислительной технике и может быть использовано В;многопроцессорных .вычислительных системах в качестве устройства специального процессора для организации обмена данными.

Известно устройство для сопряжения, содержащее блок синхронизации, блок управления обменом, коммутатор информации Cll.

Недостатками устройства- являются низкое быстродействие и большой объем оборудования.

Известно также многоканальное устройство для сопряжения источников сообщений с цифровой вычислительной машиной, содержащее блок синхронизации, блоки хранения сообщений, блоки дешифрации, коммутатор записи, коммутатор считывания 2.

Недостатками данного устройства являются низкое быстродействие и узкая область применения.

известно также многопрограммное устройство сопряжения, содержащее адаптер связи с каналом, адаптер связи с внешним устройством, регистр адреса, регистр данных, ре- гистр команды, блок управления, генератор, регистр микрокоманд, дешифратор микрокоманд, блок выработки адреса микрокоманд, блок коммутации сигнала выборки З.

Недостатками указанного устройства являются низкое быстродействие и ограниченная область применения.

Наиболее близким по технической сущности и достигаемому эффекту является многоканальное устройство для сопряжения.источников сообщения с цифровой вычислительной машиной, .содержащее генератор импульсов, блок дешифрации, первый -h -и каналы, содержащие блоки хранения сообщений, элемент ИЛИ, реверсивный счетчик, коммутатор записи и коммутатор считывания , коммутатор входов, коммутатор выходов, блок сравнения, блок дешифрации, содержащий первый - п-й элементы И и дешифратор, блок дешифрации числа заявок в канале, причем выход генератора импульсов соединен с входом блока дешифрации, группа входов устройства соединена с группой информационных входов коммутатора входов, группа выходов которого соединена с кодовыми входами коммутаторов записи каналов и входами элементов ИЛИ каналов, выходы которых соединены с управляющими входами коммутаторов записи каналов и суммирующими входами реверсивных счетчиков каналов, выходы которых соединены с группой входов дешифратора блока дешифрации и с группой входов блока дешифрации числа заявок в каналах, группа выходов которого соединена с группой входов блока сравнения, первая группа выходов которого соединена с группой адресных входов ком мутатора входов; а вторая группа выходов - с группой входов коммутато ра выходов, с первы№1 входами первого - h -го элементов. И, первый выход которого соединен с вторым входом коммутатора входов, а второй выход образует выход устройства, выходы коммутаторов записи каналов соединены .с кодовыми входами блоков хранени сообщений каналов, выходы которых соединены с группой информационных входов коммутатора выхода, группа выходов дешифратора блока дешифрации соединена с вторыми входами первого п-го элементов И блока дешифрации, выходы которых соединены с управляющими входами коммутаторов считывания каналов и вычитающими входами (Реверсивных счетчиков каналов, выходы коммутаторов считывания каналов соединены с управляющими входами блоков хранения сообщений каналов С . Недостатками, известного устройства являются низкое быстродействие и узкая область использования. Низкое быстродействие обусловлено тем, что в устройстве используетсяп параллельно работающих каналов, содержащих блоки хранения сообщений. В каждьй момент времени в блоке хранения сообщений каналов может производиться либо запись сообщения, либо считывание. Это приводит к тому, что общее время обмена сообщениями увели чивается. . Суммарное среднее время одного цикла работы j-ro канала (,h) Твычисляется по формуле: , 1 где t. , . - среднее время записи и считьгаания из i-ro блока хранения сообще НИИ соответственно; т. - число блоков хранения : Сообщений . канала устройства.. Из выражения (1)следует, что среднее время одного цикла работы j-канала увеличивается за счет невозможности совмещения процессов я писи и считывания сообщений из блоков хранения сообщений для одного и того же канала, это обусловлено заданием жесткого порядка работы канала по записи, а затем считыванию сообщений. Узкая область применения известного устройства обусловлена невозможностью обмена сообщениями по гибкому алгоритму. Это связано с тем, что в устройстве предопределен последовательный порядок записи и считывания сообщений в каналы и, кроме того, устройство не позволяет обмениваться сообщениями. Цель изобретения - повышение быстродействия и расширение области применения устройства путем организации параллельной записи и считывания информации. Поставленная цель достигается тем, что в -устройство для обмена данными в многопроцессорной вычислительной системе, содержащее группу блоков хранения- сообщений, коммутатор записи, коммутатор обращения, первый коммутатор адреса, выходной коммутатор, входной коммутатор, счетчик адреса, причем первая группа информационных входов-выходов блоков хранения сообщений группы соединена с первой группой информационных входов-выходов выходного коммутатора и с группой информационных входов-выходов устройства, первая группа информационных входов первого коммутатора адреса является первой группой адресных входов устройства, первые управляющие входы коммутаторов записи и обращения образуют соответствующие группы управляющих входов устройства, группа выходов коммутатора записи соединена с соответствующими входами управления записи хранения сообщений группы, группа выходов коммутатора обращений соединена с соответствующими входами обращения блоков хранения сообщений группы, первая и вторая группы выходов первого коммутатора адреса соединены соответственно с первой и второй группами адресных входов блоков хранения сообщений группы, введены постоянная память (ПП) команд, блок буферной памяти, оперативный запоминающий блок (ОЗБ) контроллера, центральный оперативный запоминающий блок, блок управления обменом, блок 5 счетчиков, второй коммутатор адреса сумматор, регистр косвенного адреса регистр исполнительного адреса, бло магистраильных элементов, первый, второй и третий магистральные элеме ты, причем вторая группа информационных входов-вькодов блоков хранения сообщений группы соединена с группой информационных входов-выходов соответствующего периферийного процессора, группа адресных входов центрального ОЗБ соединена с группой выходов блока магистральных элементов и образует вторую группу адресных входов устройства, вход обращения центрального ОЗБ соединен с выходом первого магистрального элемен та и является входом обращения устройства, первый и второй входы записи центрального ОЗБ соединены с выходами второго и третьего магистраль ных элементов соответственно и образуют вход записи устройства, вход пуска блока управления обменом является .одноименным входом устройства, вход разрешения внешнего обмена блока управления обменом является одноименным входом устройства, вторая группа информационных входов-выходов выходного коммутатора соединена с группой выходов ПП команд, с группой информационных входов счетчика адреса, блока счетчиков, регистра косвенного адреса, группой входов (Кода адресации блока управления обменом, первой группой информационных входов второго коммутатора адреса, а также с группой информационных входов-выходов ОЗБ контроллера и первой группой информационных входов-выходов выходного коммутатора соответственно, первая группа выходов блока управления обменом соедине на с группой управляющих входов блока счетчиков, первая группа выходов которого соединена с первой группой входов блока управления обменом, вторая группа выходов блока управления обменом соединена с группой входов управления обменом блоков хранения сообщений группы, выход первого разряда третьей группы управляющих выходов блока управления обменом соединен с разрешающими входами блока магистральных элементов, первого второго и третьего магистральных элементов, выходы второго и третьего разрядов третьей группы выходов 3 блока управления обменом соединены соответственно со счетным и синхронизирующим входами счетчика адреса, третья группа выходов блока управления обменом соединена соответственно с информационным входом первого магистрального элемента, выходом запроса непосредственного доступа устройства, информационными входами второго и третьего магистральных элементов и с группой управляющих входов входного коммутатора, четвертая группа выходов блока управления обменом соединена с группой информационных входов коммутатора записи, пятая группа выходов блока управления обменом соединена соответственно с синхронизируюш;им входом регистра косвенного адреса управляющим входом второго коммутатора адреса, синхронизирующим входом регистра исполнительного адреса, входами записи и обращения блока буферной памяти, шестая группа выходов блока управления обменом соединена с соответствующими управляющими входами записи блоков хранения сообщений группы, первый управляющий выход блока управления обменом соединен с вторым управляющим входом коммутатора записи, второй управляющий выход блока управления обменом соединен t вторым управляющим входом коммутатора обращения, седьмая группа управляющих выходов блока управления обменом соединена соответственно с первым и вторым управляющими рходами выходного коммутатора, входами обращения и записи ОЗБ контроллера и входом обращения.1Ш команд, вторая и третья группы выходов блока счетчиков соединены с второй и третьей группами входов блока управления обменом, выход управляющего разряда третьей группы выходов блока счетчиков соединен с третьими управляющими входами коммутатора записи, коммутатора обращения и управляющим входом первого коммутатора адреса, четвертая группа выходов блока счетчиков соедине.на с второй группой информационных входов первого коммутатора адреса, пятая группа выходов блока счетчиков соединена с группой адресных входов ОЗБ контроллера, выходы младщих разрядов пятой группы выходов блока счетчиков соединены с четвертой группой 7 входов блока управления обменом, шестая группа вькодов блока счетчиков соединена с группой адресных входов ПП кокганд, вход внешней записи блока управления обменом соединен с первьм входом коммутатора записи, выходы регистра косвенного адреса соединены с первой группой входов сумматора, выходы которого соединены с второй группой информационных входов второго коммутатора адреса, выходы которого соединены с группой информационных входов регистра исполнительного адреса, выходы которого соединены с второй группой входов сумматора и с группой адресных входов блока буферной памяти группа входов-выходов блока буферной памяти соединена с первой группой информационных входов-выходов выходного коммутатора, выходы всех разрядов счетчика адреса, кроме младшего соединены с соответствующими информационными входами блока магистральных элементов, группа информационных входов-выходов центрального ОЗБ соединена с второй и третьей группа ми входов-выходов входного коммутатора, причем блок управления обменом содержит память микрокоманд, узел дешифраторов управления счетчиками, узел коммутации внешних запоминающих блоков, регистр адреса, регистр микрокоманд, коммутатор адреса, ком мутатор управляющих сигналов, мульти плексор, дешифратор записи, дешифра тор управления обращением, генератор тактовых импульсов, триггер пуска, пять элементов И, при этом группа информационных входов дешифратора управления обращением боединена с группой одноименных входов дешифратора записи и образует первую группу входов блока управления обме ном, группа информационных входов мультиплексора образует вторую группу входов блока управления обменом, группа входов коммутатора управляющих сигналов образует третью группу входов блока управления обме ном, первая группа информационных входов узла коммутации внешних запо минающих блоков образует четвертую группу входов блока управления обменом, первый управляющий вход коммутатора управляющих сигналов являе ся входом внешней записи блока упра ления обменом, единичный вход триг143гера пуска является входом пуска блока управления обменом, первый информационный вход мультиплексора является входом разрешения внешнего обмена блока управления обменом, первая группа информационных входов коммутатора адреса образует группу одноименных входов блока управления обменом, группа выходов узла дешифраторов управления счетчиками образует первую группу выходов блока управления обменом, группа выходов коммутатора управляющих сигналов образует вторую группу выходов блока управления обменом, группа выходов узла коммутации внешних запоминающих блоков образует третью груп- , пу выходов блока управления обменом,, группа выходов дешифратора записи образует четвертую группу выходов блока управления обменом, выход первого элемента И, второй разряд первой группы выходов регистра микрокоманд, выходы второго и третьего элементов И и пятый разряд первой группы выходов регистра микрокоманд образуют пятую группу выходов блока управления обменом, группа выходов дешифратора управления обращением образует ;иестую группу выходов блока управления обменом, первый и четвертый разряды второй группы выходов регистра микрокоманд и выход четвертого элемента И образуют седьмую группу выходов блока управления обменом, второй выход генератора тактовых импульсов соединен с первым входом первого элемента И и является первым управляющим выходом блока управления обменом, выход микрооперации разрешения обмена регистра микрокоманд является вторым управляющим выходом блока управления обменом, при этом в блоке управления обменом выход микрооперации конца команды регистра микрокоманд соеди|Нен с первым и вторым управляющими |входами коммутатора адреса, вторая группа информационных входов которого соединена с выходом мультиплексора и группой немодифицируемых разрядов адресного выхода памяти микрокоманд, модифицируемый разряд адресного выхода которого соединен с вторым информационным входом мультиплексора, группа адресных входов которого соединена с группой выходов кодов логических условий памяти 9 микрокоманд, операционная часть выходов которой соединена с группой информационных входов регистра микрокоманд, выход микрооперации конца работы блока которого соединен с пер вым входом пятого элемента И, выход которого соединен с нулевым входом триггера пуска, выход которого соединен с входом генератора тактовых импульсов, первый выход которого сое динен с синхровходом р-егистра адреса группа входов которого соединена с группой выходов коммутатора адреса, а группа выходов - с группой входов памяти микрокоманд, третий выход генератора тактовых импульсов . соединен с первым управляющим входом узла коммутации внешних запоминающих блоков и узла дешифраторов управления счетчиками, а также с первыми входами третьего и четвертого элементов И и вторым управляющим входом дешифратора записи, первый управляющий вход которого соединен с вторым управляющим входом коммутатора управ ляющих сигналов и с выходами микрооперации разрешения записи регистра микрокоманд, синхровход которого соединен с вторым входом пятого элемента И, с вторыми управляющими входами узла коммутации внешних запоминающих блоков и узла дешифраторов управления счетчиками, с первым входом второго элемента И и с четвертым выходомгенератора тактовых импульсов, выход микрооперации управления обращением регистра микрокоманд соединен с управляющим входом дешифратора управления обращением, первый, третий, и четвертый разряды первой группы выходов регистра микрокоманд соединены с вторыми входами первого, второго и третьего . элементов И соответственно, пятый разряд второй группы выходов регистра микрокоманд соединен с вторым входом четвертого элемента И, третья и четвертая группы выходов регистра микрокоманд соединены соответственно с группами информационных входов узла дешифраторов управления счетчиками и узла коммутации внешних запоминающих блоков. Повьш1ение быстродействия достигается совмещением во времени процес сов записи и считывания сообщений в блоки приема сообщений путем введения новых элементов и связей. 4310 : Расимрение области применения устройства осуществляется введением новьк элементови связей, обеспечивающих произвольную дисциплину обмена сообщениями между источниками с использованием микропрограммного принципа управления записью и считыванием сообщений. Кроме того, введенные новые элементы и связи, обеспечивающие устранение недостатков известного устройства,позволяют повысить надежность функционирования устройства. Это связано с тем, что для хранения программ функционирования устройства может использоваться не только ГШ команд, но и ОЗБ контроллера. Гибкость дисциплин обмена сообщениями достигается за счет возможности задания программы обмена сообщениями внешними источниками.. Введение ГШ команд позволяет расширить область применения устройства за счет возможности црограммирования дисциплин обмена сообщениями. Введение блока буферной памяти и соответствзгющих связей обеспечивает повьшение быстродействия и расширение области применения устройства за счет согласования быстродействия процессоров разных уровней управлейия вычислительной системы, которые являются источниками (приемниками) сообщений. При этом блок буферной памяти используется для промежуточного хранения сообщений. Введение центрального ОЗБ и соответствующих связей, а также блока магистральных элементов и магистраль-. ных элементов позволяет повысить быстродействие устройства и системы вцелом и расширить область применения устройства за счет возможности совмещения во времени процессов обмена сообщениями источниками и приемниками различных уровней. Например, возможно совмещение процессов обмена сообщениями блока буферной памяти с блоками хранения сообщений и центрального ОЗБ с процессором верхнего уровня. Введение ОЗБ контроллера и соответствующих связей позволяет повысить быстродействие и расширить область применения устройства за счет использования этого блока для промежуточного хранения сообщений при обмене между блоками хранения

сообщений и центральным ОЗБ и возможности задания программы обмена сообщениями с внешней системой лутеМ записи программы обмена в ОЗБ . контроллера .

Введение блока управления обменом блока счетчиков и соответствующих связей позволяет обеспечить реализацию алгоритмов обмена сообщениями устройством,

Введение регистров косвенного и исполнительного адресов, сумматора второго коммутатора адреса и соответствующих связей обеспечивает возможность применения расширенных способов адресации блока буферной памяти, что позволяет сокращать время выборки сообщений из этого блока.

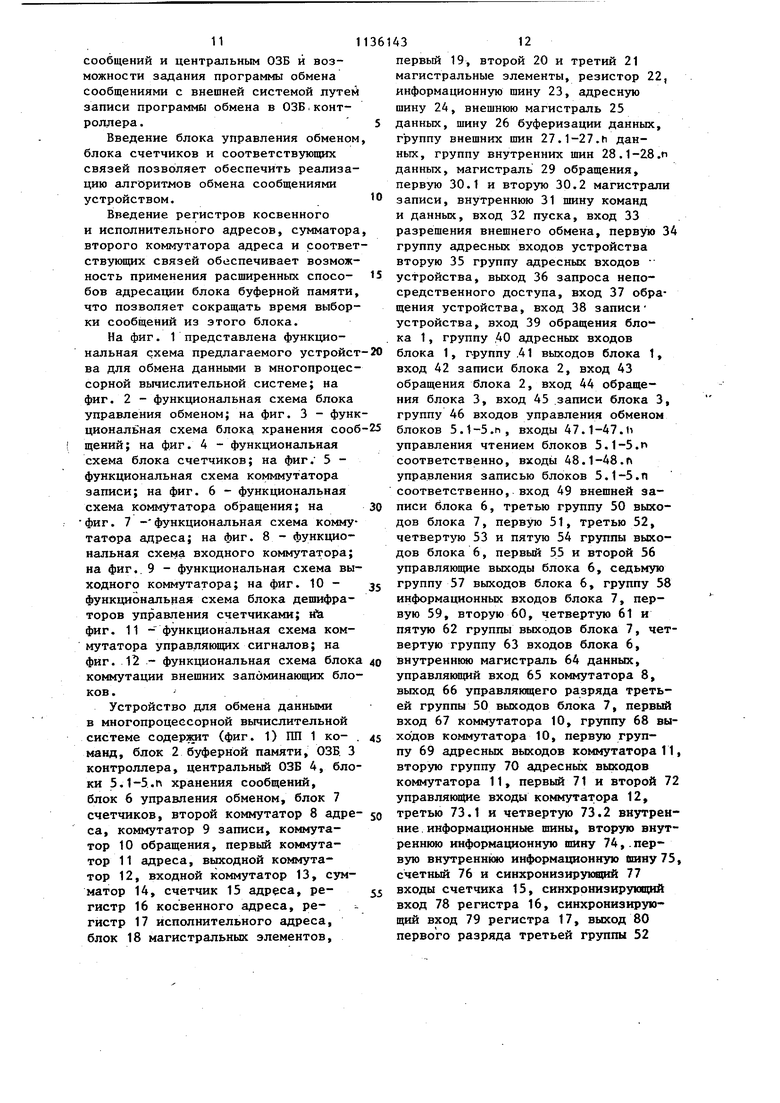

На фиг. 1 представлена функциональная схема предлагаемого устройст ва для обмена данными в многопроцессорной вычислительной системе; на фиг. 2 - функциональная схема блока управления обменом; на фиг. 3 - функциональная схема блокд хранения сооб щений; на фиг. 4 - функциональная схема блока счетчиков; на фиг. 5 функциональная схема комммутатора записи; на фиг. 6 - функциональная схема коммутатора обращения; на фиг. 7 -функциональная схема коммутатора адреса; на фиг. 8 - функциональная схема входного коммутатора; на фиг.. 9 - функциональная схема выходного коммутатора; на фиг. 10 функциональная схема блока дешифраторов управления счетчиками; Hfei фиг. 11 -функциональная схема коммутатора управляющих сигналов; на фиг. 12 - функциональная схема блока коммутации внешних запоминающих блоков.

Устройство для обмена данными в многопроцессорной вычислительной системе содерлшт (фиг. 1) ГШ 1 ко- . манд, блок 2 буферной памяти, ОЗБ. 3 контроллера, центральный ОЗБ 4, блоки 5.1-5.п хранения сообщений, блок 6 управления обменом, блок 7 счетчиков, второй коммутатор 8 адреса, коммутатор 9 записи, коммутатор 10 обращения, первый коммутатор 11 адреса, выходной коммутатор 12, входной коммутатор 13, сумматор 14, счетчик 15 адреса, регистр 16 косвенного адреса, регистр 17 исполнительного адреса, блок 18 магистральных элементов.

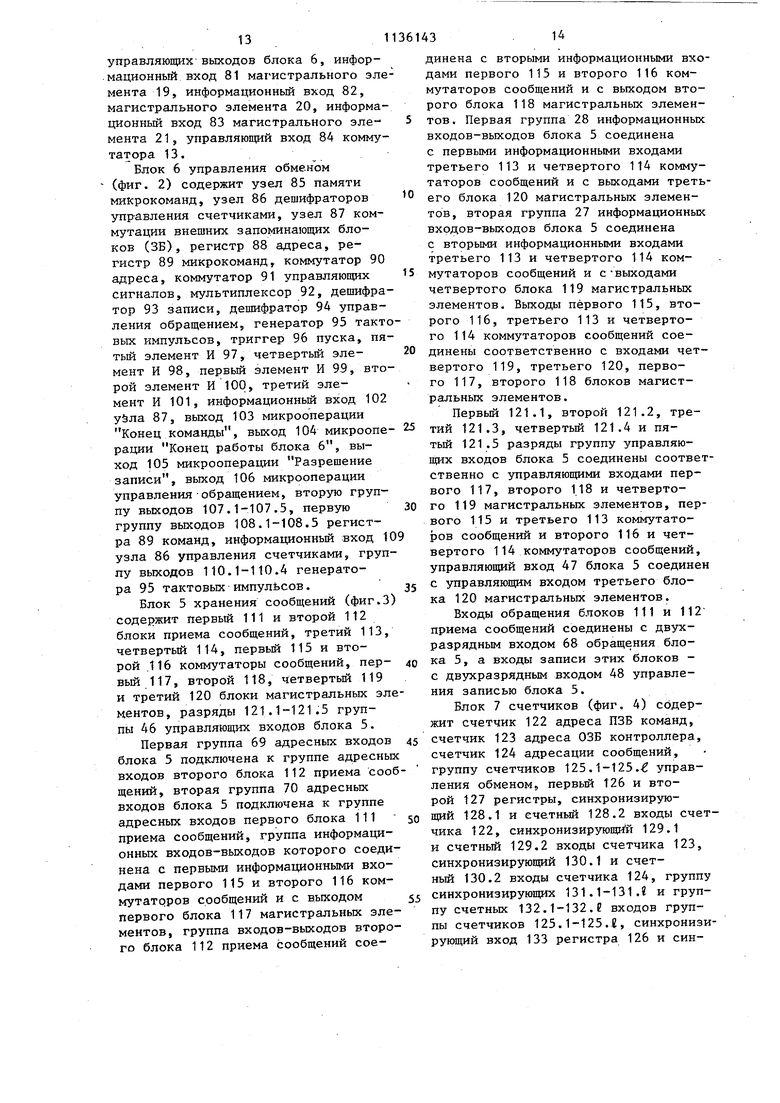

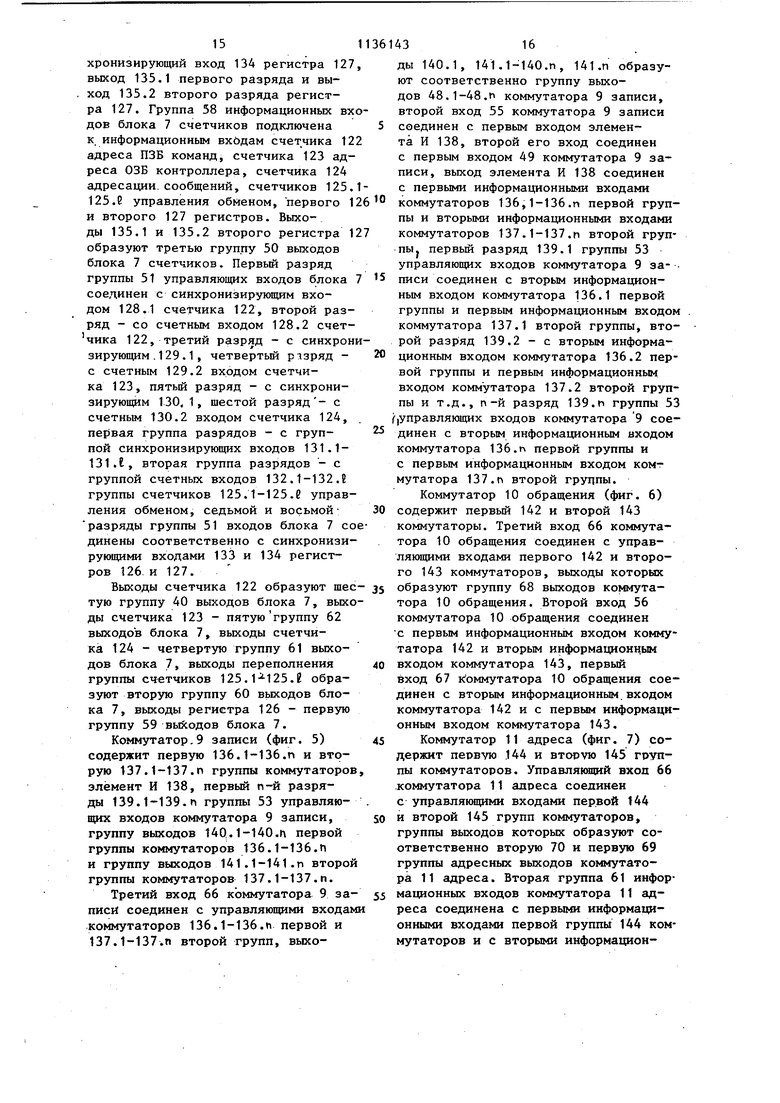

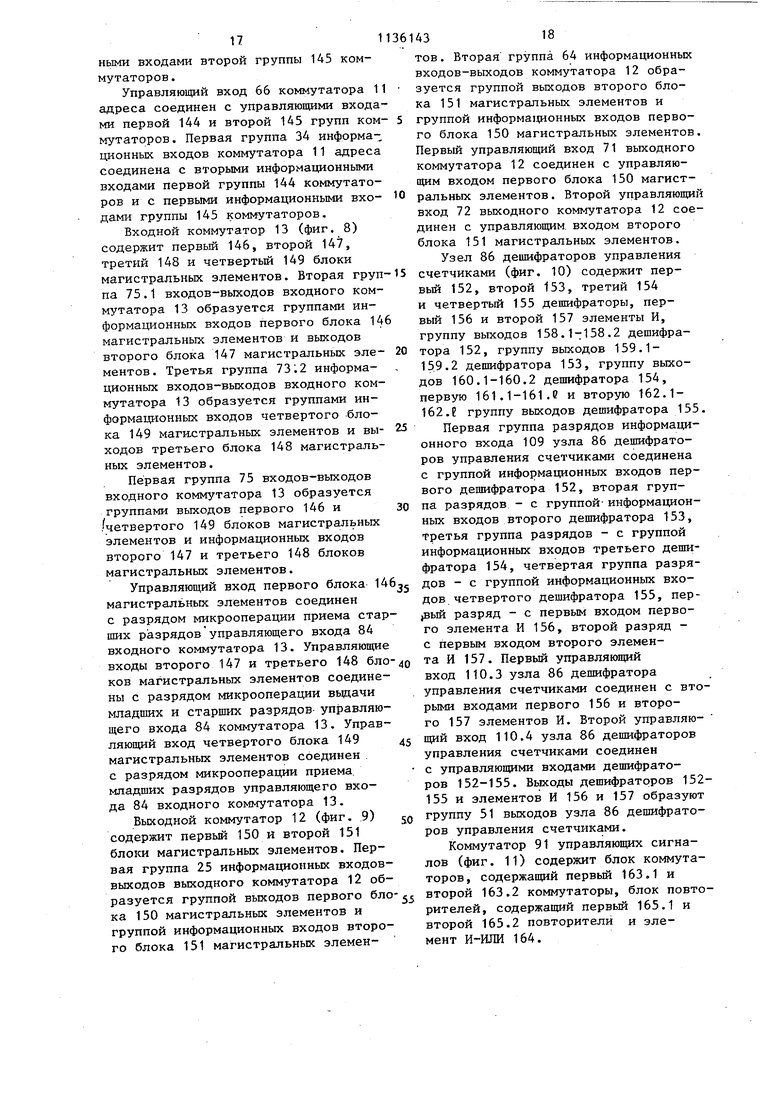

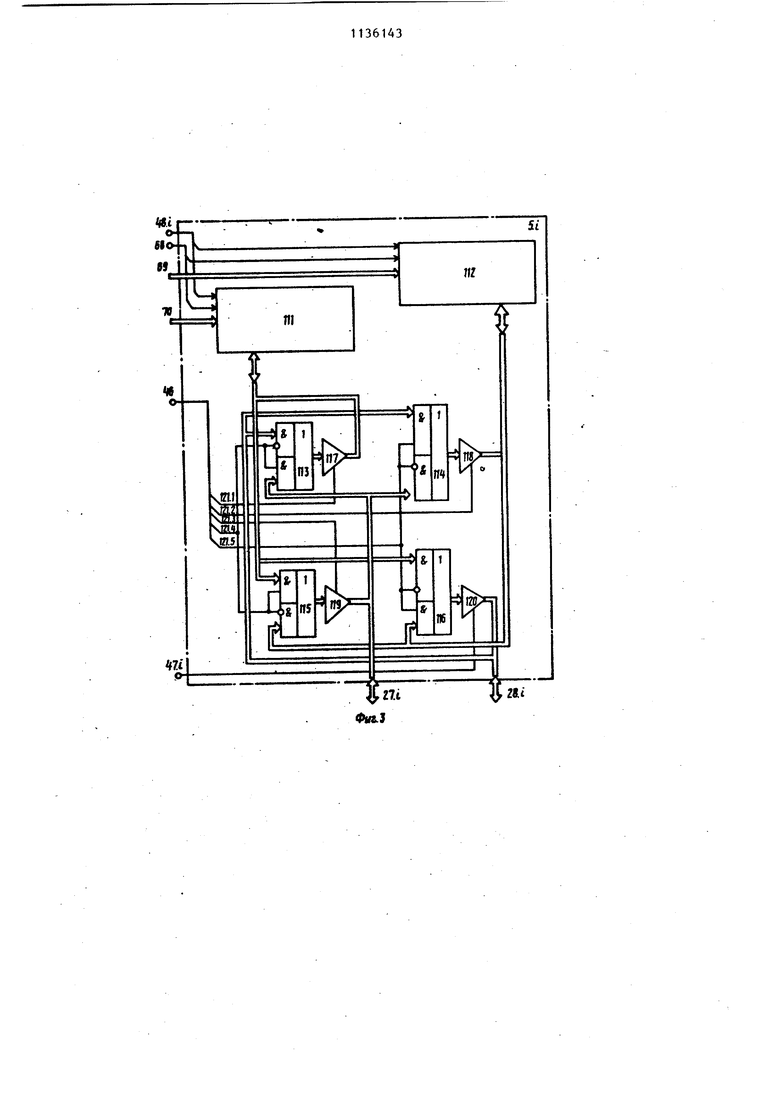

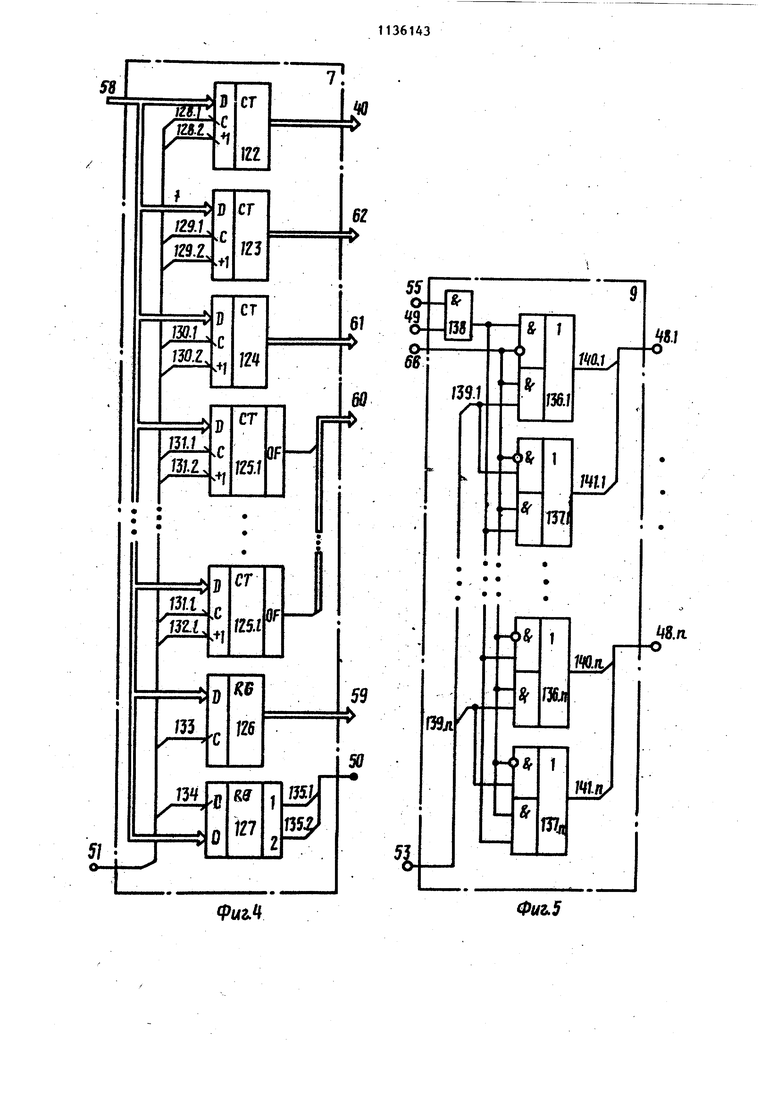

первый 19, второй 20 и третий 21 магистральные элементы, резистор 22, информационную шину 23, адресную шину 24, внешнюю магистраль 25 данных, шину 26 буферизации данных, группу внешних шин 27.1-27.h данньтх, группу внутренних шин 28.1-28.п данных, магистраль 29 обращения, первую 30.1 и вторую 30.2 магистрали записи, внутреннюю 31 шину команд и данных, вход 32 пуска, вход 33 разрешения внешнего обмена, первую 34 группу адресных входов устройства вторую 35 группу адресных входов устройства, выход 36 запроса непосредственного доступа, вход 37 обращения устройства, вход 38 записи устройства, вход 39 обращения блока 1, группу 40 адресных входов блока 1, г-руппу ,41 выходов блока 1, вход 42 записи блока 2, вход 43 обращения блока 2, вход 44 обращения блока 3, вход 45 записи блока 3, группу 46 входов управления обменом блоков 5.1-5.П, входы 47.1-47.1 управления чтением блоков 5.1-5.г соответственно, входы 48.1-48.г управления записью блоков 5.1-5.П соответственно, вход 49 внешней записи блока 6, третью группу 50 выходов блока 7, первую 51, третью 52, четвертую 53 и пятую 54 группы выходов блока 6, первый 55 и второй 56 управляюш;ие выходы блока 6, седьмую группу 57 выходов блока 6, группу 58 информационных входов блока 7, первую 59, вторую 60, четвертую 61 и пятую 62 группы выходов блока 7, четвертую группу 63 входов блока 6, внутреннюю магистраль 64 данных, управлякмций вход 65 коммутатора 8, выход 66 управляющего разряда третьей группы 50 выходов блока 7, первый вход 67 коммутатора 10, группу 68 выходов коммутатора 10, первую группу 69 адресных выходов коммутатора 11, вторую группу 70 адресньк выходов коммутатора 11, первый 71 и второй 72 управляющие входы коммутатора 12, третью 73.1 и четвертую 73.2 внутренние . информационные шины, вторую внутреннюю информационную шину 74,.первую внутреннюю информационную шину 75, счетный 76 и синхронизирукш{ий 77 входы счетчика 15, синхронизирующий вход 78 регистра 16, синхронизирующий вход 79 регистра 17, выход 80 первого разряда третьей группы 52 управляющих выходов блока 6, информационный вход 81 магистрального элемента 19, информационный вход 82, магистрального элемента 20, информационный вход 83 магистрального элемента 21, управляющий вход 84 коммутатора 13, Блок 6 управления обменом - (фиг. 2) содержит узел 85 памяти микрокоманд, узел 86 дешифраторов управления счетчиками, узел 87 коммутации внешних запоминающих блоков (ЗБ), регистр 88 адреса, регистр 89 микрокоманд, коммутатор 90 адреса, коммутатор 91 управляющих сигналов, мультиплексор 92, дешифратор 93 записи, депшфратср 94 управления обращением, генератор 95 такто вых импульсов, триггер 96 пуска, пяTbrii элемент И 97, четвертый элемент И 98, первый элемент И 99, второй элемент И 100, третий элемент И 101, информационный вход 102 уела 87, выход 103 микрооперации Конец команды, выход 104 микрооперации Конец работы блока 6, выход 105 микрооперации Разрешение записи, выход 106 микрооперации управления-обращением, вторую группу выходов 107,1-107,5, первую группу выходов 108.1-108,5 регистра 89 команд, информационный вход 10 узла 86 управления счетчиками, группу выходов 110,1-110,4 генератора 95 тактовых импульсов, Блок 5 хранения сообщений (фиг,3) содержит первый 111 и второй 112 блоки приема сообщений, третий 113, четвертьй 114, первый 115 и второй .116 коммутаторы сообщений, первый 117, второй 118, четвертый 119 и третий 120 блоки магистральных эле ментов, разряды 121,1-121,5 группы 46 управляющих входов блока 5. Первая группа 69 адресных входов блока 5 подключена к группе адресных входов второго блока 112 приема сооб щений, вторая группа 70 адресных входов блока 5 подключена к группе адресных входов первого блока 111 приема сообщений, группа информационных входов-выходов которого соедииена с первыми информационными входами первого 115 и второго 116 коммутаторов сообщений и с выходом первого блока 117 магистральных элементов, группа входов-выходов второго блока 112 приема сообщений соединена с вторыми информационными входами первого 115 и второго 116 коммутаторов сообщений и с выходом второго блока 118 магистральных элементов. Первая группа 28 информационных входов-выходов блока 5 соединена с первыми информационными входами третьего 113 и четвертого 114 коммутаторов сообщений и с выходами третьего блока 120 магистральных элементов, вторая группа 27 информационных входов-выходов блока 5 соединена с вторыми информационными входами третьего 113 и четвертого 114 коммутаторов сообщений и свыходами четвертого блока 119 магистральных элементов. Выходы первого 115, второго 116, третьего 113 и четвертого 114 коммутаторов сообщений соединены соответственно с входами четвертого 119, третьего 120, первого 117, второго 118 блоков магистральных элементов. Первый 121.1, второй 121.2, третий 121,3, четвертый 121.4 и пятый 121 ,5 разряды группу управляющих входов блока 5 соединены соответственно с управляющими входами первого 117, второго 118 и четвертого 119 магистральных элементов, первого 115 и третьего 113 коммутаторов сообщений и второго 116 и четвертого 114 коммутаторов сообщений, управляющий вход 47 блока 5 соединен с управляющим входом третьего блока 120 магистральных элементов. Входы обращения блоков 111 и 112 приема сообщений соединены с двухразрядным входом 68 обращения блока 5 , а входы записи этих блоков с двухразрядным входом 48 управления записью блока 5, Блок 7 счетчиков (фиг. 4) содержит счетчик 122 адреса ИЗБ команд. счетчик 123 адреса ОЗБ контроллера, счетчик 124 адресации сообщений, группу счетчиков 125,1-125,€ управления обменом, первый 126 и второй 127 регистры, синхронизируюЧ й 128,1 и счетный 128.2 входы счетчика 122, синхронизирующими 129.1 и счетный 129,2 входы счетчика 123, синхронизирующий 130,1 и счетный 130,2 входы счетчика 124, группу синхронизирующих 131,1-131.« и группу счетных 132,1-132.2 входов группы счетчиков 125,1-125.2, синхронизирующий вход 133 регистра 126 и синхронизирующий вход 134 регистра 127 выход 135.1 первого разряда и вы. ход 135.2 второго разряда регистра 127. Группа 58 информационных вх дов блока 7 счетчиков подключена к. информационным входам счетчика 12 адреса ПЗБ команд, счетчика 123 адреса ОЗБ контроллера, счетчика 124 адресации, сообщений, счетчиков 125 125.С управления обменом, первого и второго 127 регистров. Выходы 135.1 и 135.2 второго регистра образуют третью группу 50 выходов блока 7 счетчиков. Первый разряд группы 51 управляющих входов блока соединен с синхронизирующим входом 128.1 счетчика 122, второй разряд - со счетным входом 128.2 счетчика 122, третий разряд - с синхрон зирующим . 129. 1 , четвертый рязряд с счетным 129.2 входом счетчика 123, пятый разряд - с синхрониЗИРУЮ1ЦИМ 130, 1, шестой разряд- с счетным 130.2 входом счетчика 124, первая группа разрядов - с группой синхронизирующих входов 131.1131.Е, вторая группа разрядов - с группой счетных входов 132.1-132.8 группы счетчиков 125.1-125.6 управ ления обменом, седьмой и восьмой разряды группы 51 входов блока 7 с динены соответственно с синхронизи рующими входами 133 и 134 регистров 126. и 127. Выходы счетчика 122 образуют ше тую группу 40 выходов блока 7, вых ды счетчика 123 - пятуюгруппу 62 выходов блока 7, выходы счетчика 124 - четвертую группу 61 выходов блока 7 выходы переполнения группы счетчиков 125.1 425. образуют вторую группу 60 вькодов блока 7, выходы регистра 126 - первую группу 59 вы&одов блока 7. Коммутатор.9 записи (фиг. 5) содержит первую 136.1-136.п и вторую 137.1-137.п группы коммутаторо элемент И 138, первый п-й разряды 139.1-139. группы 53 управляющих входов коммутатора 9 записи, группу выходов 140,. 1-140.ГА первой группы коммутаторов 136.1-136.М и группу выходов 141.1-141.п второ группы коммутаторов 137.1-137.п. Третий вход 66 коммутатора 9 за пней соединен с управляющими входа коммутаторов 136.1-136.П первой и 137.1-137.п второй групп, выхо4316ды 140.1, 141.1-140.п, 141.П образуют соответственно группу выходов 48.1-48.11 коммутатора 9 записи, второй вход 55 коммутатора 9 записи соединен с первым входом элемента И 138, второй его вход соединен с первым входом 49 коммутатора 9 записи, выход элемента И 138 соединен с первыми информационными входами коммутаторов 136,1-136.п первой группы и вторыми информационными входами коммутаторов 137.1-137.п второй группы первый разряд 139.1 группы 53 управляющих входов коммутатора 9 за- . писи соединен с вторым информационным входом коммутатора 136.1 первой группы и первым информационным входом коммутатора 137.1 второй группы, второй разряд 139.2 - с вторым информационным входом коммутатора 136.2 первой группы и первым информационным входом коммутатора 137.2 второй группы и т.д., п-й разряд 139.h группы 53 Управляющих входов коммутатора 9 соединен с вторым информационным входом коммутатора 136.г первой группы и с первым информационным входом коммутатора 137.п второй грулпы. Коммутатор 10 обращения (фиг. 6) содержит первьш 142 и второй 143 коммутаторы. Третий вход 66 коммутатора 10 обращения соединен с управляющими входами первого 142 и второго 143 коммутаторов, выходы которых образуют группу 68 выходов коммутатора 10 обращения. Второй вход 56 коммутатора 10 обращения соединен с первым информационным входом коммутатора 142 и вторым информационным входом коммутатора 143, первый вход 67 1 оммутатора 10 обращения соединен с вторым информационным.входом коммутатора 142 и с первым информационным входом коммутатора 143. Коммутатор 11 адреса (фиг. 7) содержит первую 144 и ВТОРУЮ 145 группы коммутаторов. Управляющий вход 66 .коммутатора 11 адреса соединен с управляющими входами первой 144 и второй 145 групп коммутаторов, группы выходов которых образуют соответственно вторую 70 и первую 69 группы адресных выходов коммутатора 1 1 адреса. Вторая группа 61 информационных входов коммутатора 11 адреса соединена с первыми информационными входами первой группы 144 коммутаторов и с вторыми информационными входами второй группы 145 коммутаторов.

Управляющий вход 66 коммутатора 11 адреса соединен с управляющими входами первой 144 и второй 145 групп коммутаторов. Первая группа 34 информационных входов коммутатора 11 адреса соединена с вторыми информационными входами первой группы 144 коммутаторов и с первыми информационными входами группы 145 коммутаторов.

Входной коммутатор 13 (фиг. 8) содержит первый 146, второй 147, третий 148 и четвертый 149 блоки магистральных элементов. Вторая группа 75.1 входов-выходов входного коммутатора 13 образуется группами информационных входов первого блока 146 магистральных элементов и выходов второго блока 147 магистральных элементов. Третья группа 73L2 информационных входов-выходов входного коммутатора 13 образуется группами информационных входов четвертого блока 149 маги-стральных элементов и выходов третьего блока 148 магистральных элементов.

Первая группа 75 входов-выходов входного коммутатора 13 образуется группами выходов первого 146 и /четвертого 149 блоков магистральных элементов и информационных входов второго 147 и третьего 148 блоков магистральных элементов.

Управляющий вход первого блока l магистральных элементов соединен с разрядом микрооперации приема старших разрядовуправляющего входа 84 входного коммутатора 13. Управляющие входы второго 147 и третьего 148 блоков магистральных элементов соединены с разрядом микрооперации вьщачи младших и старших разрядов управляющего входа 84 коммутатора 13. Управляющий вход четвертого блока 149 магистральных элементов соединен с разрядом микрооперации приема, младших разрядов управляющего входа 84 входного коммутатора 13.

Выходной коммутатор 12 (фиг. 9) содержит первый 150 и второй 151 блоки магистральных элементов. Первая группа 25 информационных входоввыходов выходного коммутатора 12 образуется группой выходов первого блока 150 магистральных элементов и группой информационных входов второго блока 151 магистральных элементов . Вторая группа 64 информационных входов-выходов коммутатора 12 образуется группой вькодов второго блока 151 магистральных элементов и группой информационных входов первого блока 150 магистральных элементов Первый управляющий вход 71 выходного коммутатора 12 соединен с управляюпщм входом первого блока 150 магистральных элементов. Второй управляющи вход 72 выходного коммутатора 12 соединен с управляющим, входом второго блока 151 магистральных элементов.

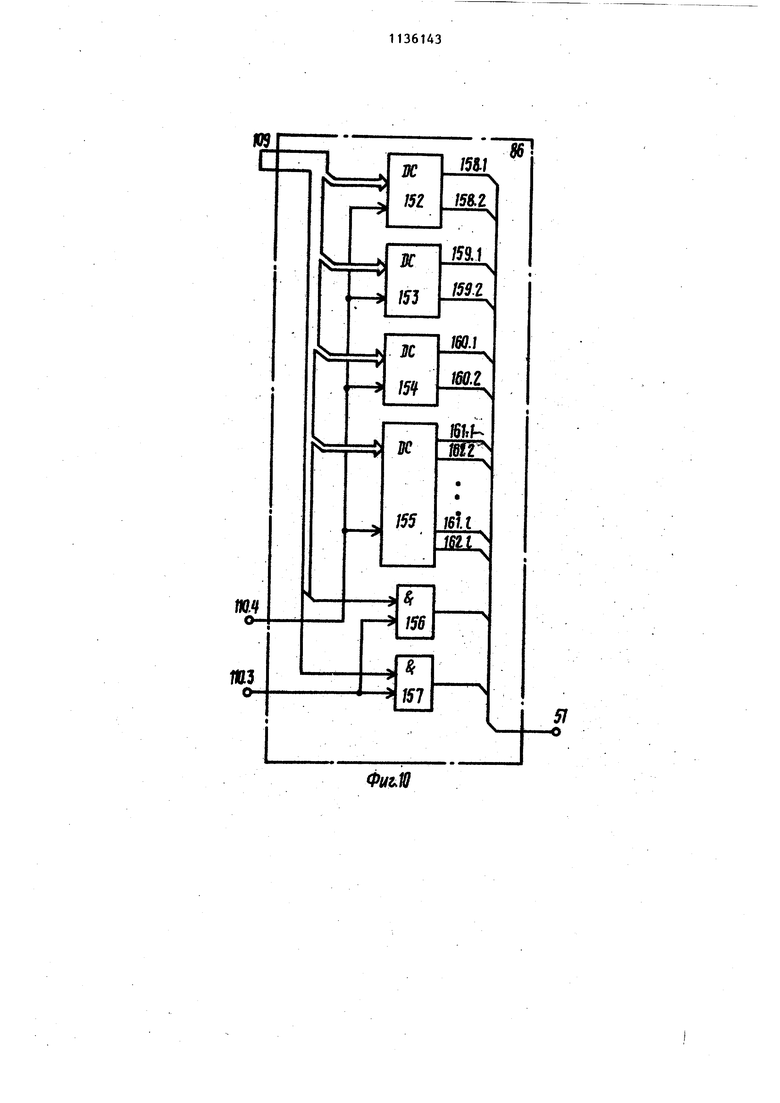

Узел 86 дешифраторов управления счетчиками (фиг. 10) содержит первый 152, второй 153, третий 154 и четвертый 155 дешифраторы, первый 156 и второй 157 элементы И, группу выходов 158.1-158.2 дешифратора 152, группу выходов 159.115.9.2 дешифратора 153, группу выходов 160.1-160.2 дешифратора 154, первую 161.1-161.е и вторую 162.1162.С группу выходов дешифратора 155

Первая группа разрядов информационного входа 109 узла 86 дешифраторов управления счетчиками соединена с группой информационных входов первого дешифратора 152, вторая группа разрядов - с группой- информационных входов второго дешифратора 153, третья группа разрядов - с группой информационных входов третьего дешифратора 154, четвертая группа разрядов - с группой информационных входов четвертого дешифратора 155, разряд - с первым входом первого элемента И 156, второй разряд с первым входом второго элемента И 157. Первый управляющий вход 110.3 узла 86 дешифратора управления счетчиками соединен с вторыми входами первого 156 и второго 157 элементов И. Второй управляющий вход 110.4 узла 86 дешифраторов управления счетчиками соединен с управляющими входами дешифраторов 152-155. Вькоды дешифраторов 152155 и элементов И 156 и 157 образуют группу 51 выходов узла 86 дешифраторов управления счетчиками.

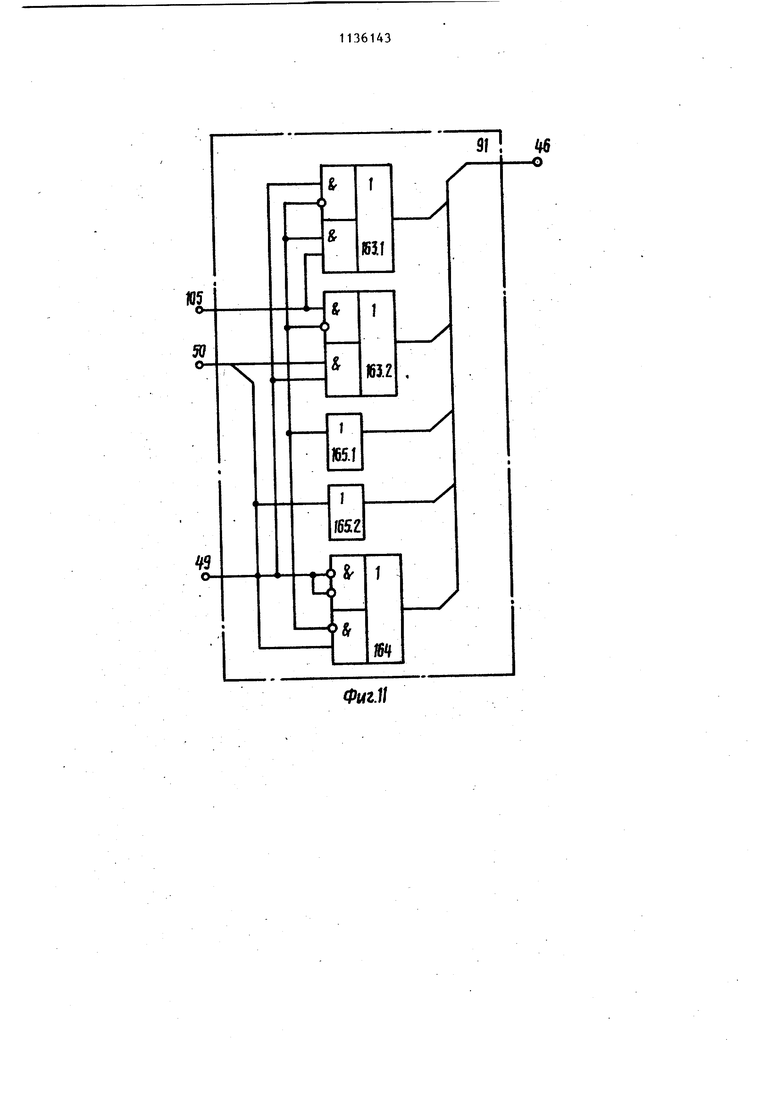

Коммутатор 91 управляюш ге сигналов (фиг. 11) содержит блок коммутаторов, содержащий первый 163.1 и второй 163.2 коммутаторы, блок повторителей, содержащий первый 165.1 и второй 165.2 повторители и элемент И-ИЖ 164.

191

Первый вход 105 коммутатора 91 управляющих сигналов соединен с первым информационным входом первого коммутатора 163.1 и вторым информационным входом второго коммутатора 163.2, третий вход 49 коммутатора 91 управляющих сигналов соединен с вторым информационным входом первого 163.1, первым информационным входом второго 163.2 коммутаторов и инверсным входом первого вентиля элемента И-ИЛИ 164. Первьш разряд второго входа 50 коммутатора 91 управляющих сигналов соединен с управляющими входами коммутаторов 163.1 и 163.2 блока коммутаторов, с входом первого повторителя 165.1 блока повторителей и с инверсным входом второго вентиля элемента И-ИЛИ 164. Второй разряд второго входа 50 коммутатора 91 управляющих сигналов соединен с входом второго повторителя 165.2 блока повторителей и-прямым входом второго вентиля элемента И-ШШ 164. Выходы элементов коммутатора 91 управляющих сигналов образуют группу 46 выходов коммутатора 91.

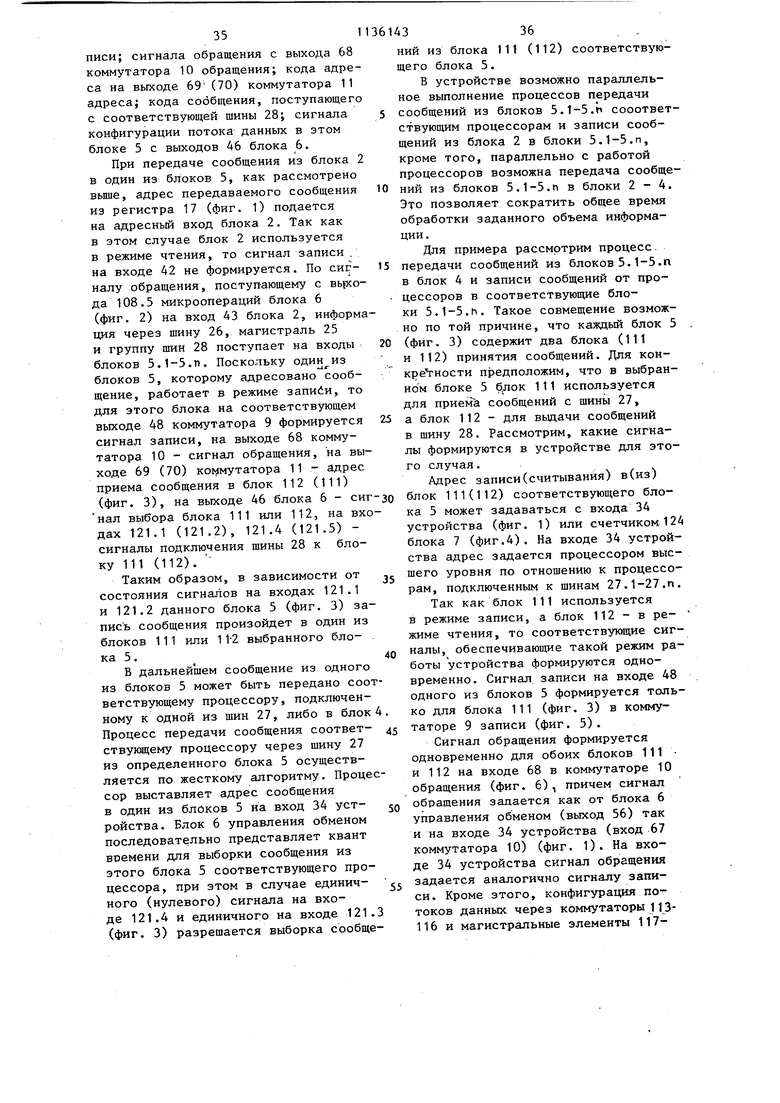

Функционирование коммутатора 91 управляющих сигналов (фиг. 11) описывается табл. 1.

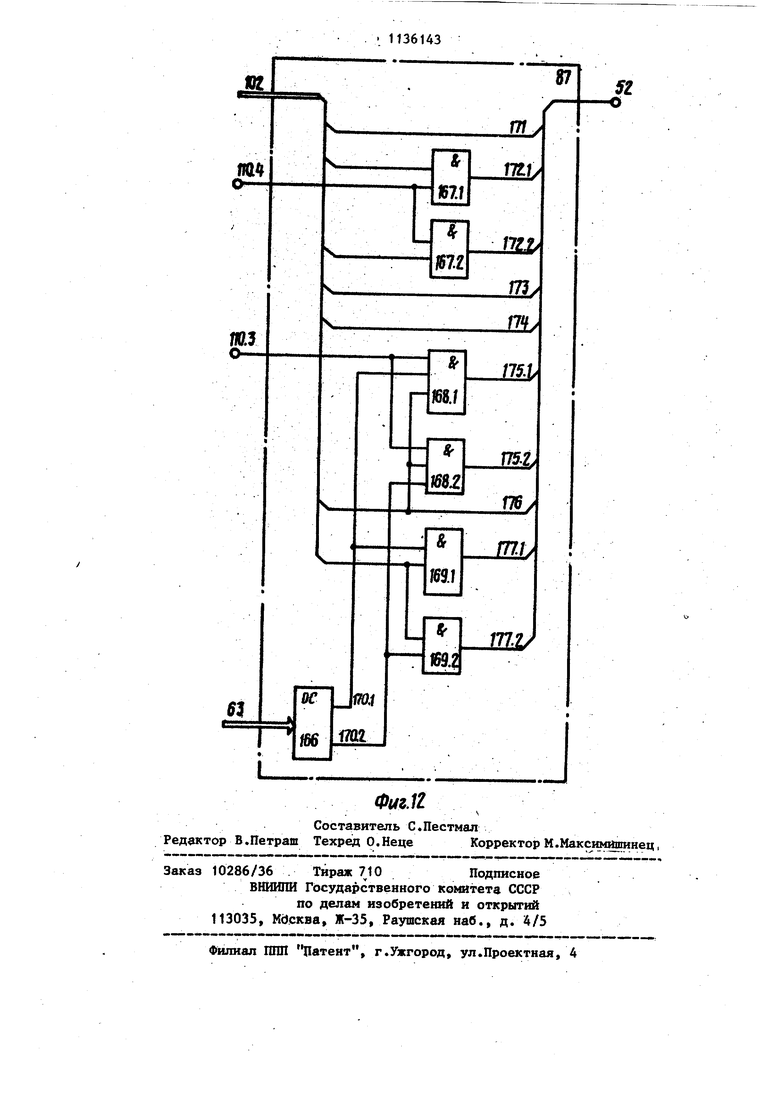

Узел 87 коммутации внешних ЗБ (фиг. 12) содержит дешифратор 166, первый блок элементов И, содержащий первый 167.1 и второй 167.2 элементы И, второй блок элементов И, содержащий первый 168.1 и второй 168.2 элементы И, третий блок элементов И,- содержащий первый 169.1 и второй 169.2 элементы И первый 170.1 и второй 170.2 выходы дешифратора 166, первый разряд 171 группы входов 102 -узла 87 коммутации внешних ЗБ, группу выходов первого блока элементов И, причем вькод 172.1 является выходом первого 167.1 элемента И, а выход 172.2 выходом второго 167.2 элемента И первого блока элементов И, четвертый разряд 173 и пятый разряд 174 группы 102 входов узла 87 коммутации внешних ЗБ, группу выходов второго блока элементов И 168, содержащую выход 175.t первого 168.1 и выход 175.2 второго 1б8.2 элементов И шестой разряд 176 группы 102 входов узла 87 коммутации внешних ЗБ, группу выходов третьей группы элемен3614:

20

тов и 169, содержащую выход 177.1 первого 169.1 и выход 177.2 второго 169.2 элементов И.

Первый 171, четвертый 173, пятый 174, шестой 176 разряды группы 102 входов узла 87 коммутации внешних ЗБ совместно с выходами 172.1, 172.2, 175.1, 175.2, 177.1 и 177.2 соответственно элементов И 167.1,

разряды группы 102 входов узла 87

коммутации внешних ЗБ соединены соот- ветственно с первым выходом первого элемента И 167.1 первого блока элементов И, с первым входом второго

элемента И 167.2 первого блрка элементов И, с первыми входами первого 168.1 и второго 168.2 элементов И второго блока элементов И, с первыми входами первого 169.1 и

второго 169.2 элементов И третьего блока элементов И.

Адресный вход 6-3 узла 87 коммутации внешних ЗБ соединенс входом дешифратора 166, первый выход 170.1

которого соединен с вторыми входами первого элемента И 168.1 второго блока элементов И и первого элемента И 169.1 третьего блока элементов И, второй выход 170.2 дешифрато-

ра 166 соединен с вторыми входами

второго элемента И 168.2 второго блока элементов И и второго элемента И 169.2 третьего блока элементов И. Второй управляющий вход 110.4

узла 87 коммутации внешних ЗБ соединен с вторыми входами первого 167.1 и второго 167.2 элементов И первого блока элементов И.

Первый управляющий вход 110.3 узла 87 коммутации внешних ЗБ соединен с третьими входами первого 168.1 и второго 168.2 элементов И второго блока элементов И.

Следует отметить, что в данном устройстве вход (группа входов) 63 является одноразрядным, представляющим младпшй разряд пятой группы 62 выходов блока 7 счетчиков и являющимся адресным входом ОЗБ 3 контроллера. Поэтому дешифратор 166 узла 87 управления внешними ЗБ является дешифратором из одного в два, т.е.

расшифровывает одно из двух состояний входа 63 - О или 1.

Функциональное назначение элементов и связей устройства.

Блок 1 предназначен для хранения команд, конста;нт, начальных адресов подпрограмм управления обменом сооб.щений. Блок 1 представляет собой статистический блок памяти и может быть построен на типовых интегральных элементах, например типа 556 РТ5, Вход 39 блока 1 предназначен для подачи сигнала управления обращением с выхода 107.3 второй группы (фиг. 2) выходов регистра 89, образующих седь-15 для му1о группу 57 выходов блока 6. При отсутствии сигнала на входе 39 блока 1 на его выходах 41 уста навливается состояние высокого импеданса. На группу входов 40 блока 1 с выхода счетчика 122 команд блока 6 (фиг. 4) поступает код адреса. С выхода 41 блока 1 (фиг. 1) при наличии сигнала обращения на его входе 39 информацияпередается на внутреннюю шину 64, откуда информация может передаваться через выходной коммутатор 12 (фиг. 9) во внешнюю магистраль 25 данных, а с нее в блок.2 буферной памяти через шину 26 буфериза ции данных или.в блоки 5.1-5.ti хране ния сообщений (фиг. 1) через труппу внутренних шин 28.1-28.П данных. Кроме того, с выхода 41 блока (фиг. 1) в блок 7 (фиг. 4) может поступать следующая информация: в счет чик 1.22 - код номера команды, в счетчик 123 - адрес информации в блок 3, в счетчик 124 - адрес информации в блок 3, в счетчик 124 адрес информации в одном из заданных блоков 5 хранения сообщений, в счетчики 125.1-125. - коды дополнения числа циклов до переполнения соответ ствующих счетчиков, в регистр 126 код номера канала (код номера одного из блоков 5) и, наконец, в регистр 127 - код управления работой одного из блоков 5 как через коммута тор буферизации 91 (фиг 2 и 11), та и через коммутаторы 9,10 и 11 соответственно записи, обращения и адреса (фиг. 1,5,6 и 7). Дополнительно с выхода 41 блока 1 в счетчик 15 адреса поступает адрес сообщений в блоке 4 в случае обращения (записи) к этому блоку, в блок 6 управления обменом - коды операций

управления обменом (.фиг. 2) , реализуемые устройством, в регистр 16 адреса - косвенный адрес сообщений блока 2 буферной памяти, на коммутатор 8 - исполнительный адрес при работе с блоком 2 буферной памяти.

Блок 2 буферной памяти представляет собой запоминающее устройство статического типа, емкость которого существенно превосходит емкость всех других блоков памяти устройства, и может быть построен на типовых интегральных элементах, например типа 541 РУ 1. Блок 2 предназначен промежуточного хранения сообщений, подлежащих перемещению между процессорами разныхуровней иерархии вычислительной системы, согласование которых обеспечивает-предлагаемое устройство. Применение блока 2 в предлагаемом устройстве позволяет компенсировать несоответствие скорости обмена процессоров разных уровней и, тем самым, обеспечивает повышение коэффициента их использования. На вход 42 блока 2 с выхода элемента И 101 блока 6 (фиг. 2) поступает сигнал управления записью, на вход 43 блока 2 (фиг. 1) с выхода 108.5 группы 108 выходов регистра 89 (фиг. 2) сигнал управления обращением. С выхода регистра 17 исполнительного адреса на адресный вход блока 2 поступает исполнительный адрес для записи (считывания) сообщений по сигналу 43 блока 2. Через шину 26 буферизации данных (фиг. 1) блок 2 сообщается с внешней магистралью 25 данных . Блоки 5.1-5.п хранения сообщений i предназначены для временного хранения сообщений, в обмене которыми участвует предлагаемое устройство. Сообщение блоков 5.1-5.П осуществляется через группу 28 внутренних шин данных, магистраль 25 и шину 26 с блоком 2, а через группу 27 внешних шин данньк - с внеЩними устройствами, например процессорами. Управление группами 27 и 28 шин данных осуществляется сигналами с выхода блока 6 (фиг. 2) через коммутаторы 113-116 и блоки 117-120 магистральных элементов (фиг. 3). Для хранения сообщений в блоках 5.1-5.П использзпотся блоки 111 и 112 приема сообщений, которые могут быть выполнены на типовых интегральньк элементах типа 541 РУ 1. Обращение к блокам 5.1-5.П производится по адресу, поступающему с выходов 69 и 70 коммутатора 11 адреса (фиг. 1 и 7), причем по адресу, поступающему с выходов 69 коммутатора 1 1 , производится обращение к блоку 112 приема сообщений (фиг. 3), а по адресу с выхода 70 - к блоку 11 приема сообщений соответствующего блока 5 хранения сообщений. На вход 68 одного из блоков 5 поступают сигналы обращения с одноименного выхода коммутатора 10 (фиг. 6).

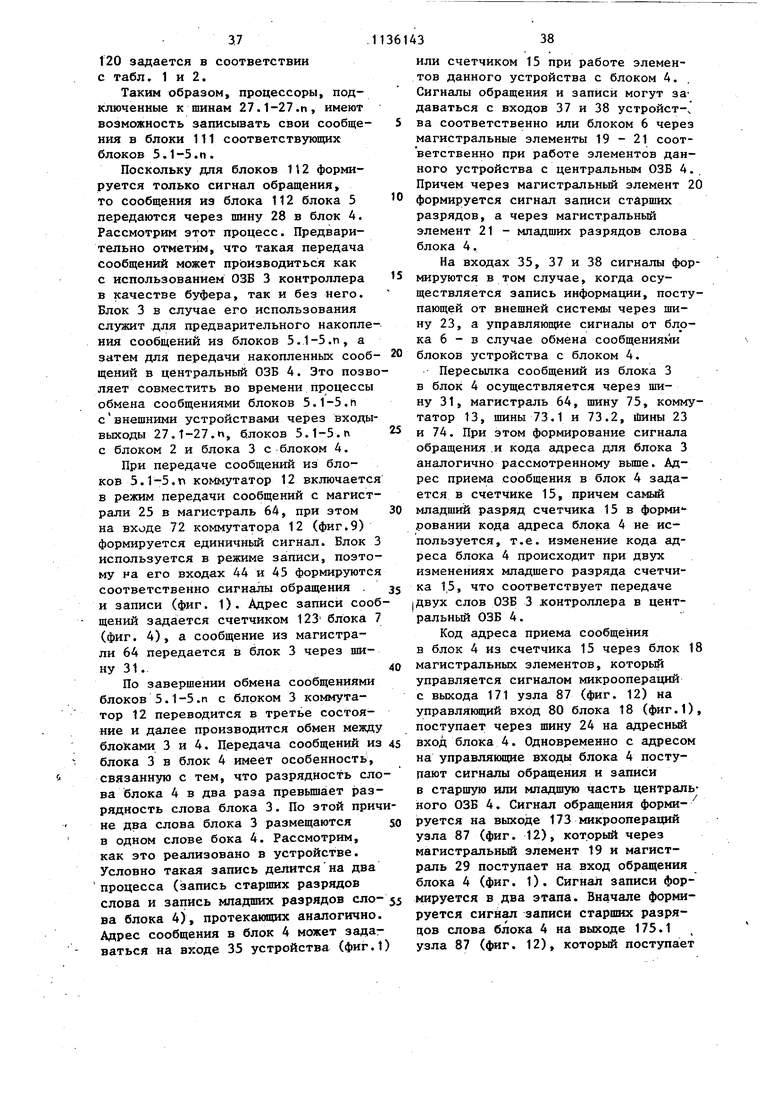

На один из входов 48 одного из блоков 5 поступают сигналы записи с одноименного выхода коммутатора 9 (фиг. 5). При наличии сигнала обращения и отсутствии сигнала записи происходит чтение информации, а при наличии сигналов обращения и записи происходит запись информации в соответствующие блоки 111 (112) приема сообщений блока 5 хране1гая сообщений (фиг. 3). Выбор соответствующего блока 5 в режиме чтения информации осуществляется управлякмцим сигналом на одноименном входе 47, которьй формируется в блоке 6 (фиг. 2) дешифратором 94. ПО этому сигналу открывается магистральный элемент 120, чем обеспечивается вьодача сообщений в одну из шин 28. В дальнейшем это сообщение может быть направлено, например, в блок 2 или 3. Коммутаторы 113-116 блока 5 (фиг. 3) служат для образования трактов двухсторОнней передачи информации между блоками 111 и 112 приема сообщений и внеш (НИМИ (через шины 27.1-27.п) и внутренними (через щины 28. 1-28.п) источниками и приемниками сообщений. Алгоритм функционирования коммутационной части любого блока 5 описывается табл. 2, в которой задан полный набор кодов, для всех возможных конфигураций коммутаций.

Блок 6 управления обменом (фиг. 2 предназначен для управления работой блоков и узлов устройства. В узле 85 хранятся микропрограммы работы устройства. Считывание информации из узла 85 осуществляется по адресу, заданному в регистре 88.

Адресная часть микрокоманды или начальный адрес микропрограммы с выхода коммутатора 90 по импульсу с выхода 110.1 генератора 95 заносится

в регистр 88. При нулевом значении выхода 103 микрооперации Конец команды регистра 89 немодифицируемые разряды адресной части микрокоманды пос гупают на первую группу информационных входов коммутатора 90, модифицируемый разряд адреса подается на информационный вход мультиплексора 92 логических условий, который формирует истинное значение модифицируемого разряда адреса, поступающего также на один из входов первой группы информационных входов коммутатора 90. Код проверяемых логических условий с выхода блока 85 поступает на адресный вход мультиплексора 92. На вторую группу информационных входов коммутатора 90 подается код операции с выхода 41 (фиг. 1) блока 1 памяти команд через внутреннюю шину 64 в конце команды при единичном значении сигнала на выходе 103 регистра 89 (фиг. 2).

Мультиплексор 92 реализует следующую логическую функцию

a+x Zo+X2Z + ... ZeV где Xp - код, определяющий прохождение на выход значения модифицируемого разряда адреса О без изменений ii--iXg - коды, предопределяющие прохождение на выход мультиплексора 92 соответствующего сигнала на входе 33 устройства, а также Zj,z,...,z логического условия (переполнения) с выхода переполнения счетчиков 125.1-125. группы выходов 60 счетчиков 125.1-125.2 блока 7 (фиг. 4).

Коммутатор 90 управляет поступлением адресной информации в регистр 88 (фиг. 2). При наличии сигнала на выходе 103 регистра 89 адреса микрокоманды определяется кодом реализуемой операции, поступающим с входа 64 блока 6 (выхода 41 блока 1). При вьтолнении микрокоманд заданной микропрограммы адрес очередной микрокоманды определяется по адресу, считываемому из узла 85 и с выхода мультиплексора 92, при этом на выходе 103 сигнал равен нулю.

Регистр 89 предназначен для хранения операционных частей микрокоманд. С выхода 104 на элемент -И 97 поступает сигнал окончания работы, по которому в момент появления сигнала на выходе 110.4 генератора 95 триггер 96 устанавливается в нулевое сос тояние и запрещается 1 ормирование так товых импульсов на выходах группы 11 генератора 95. В исходном состоянии триггер 96 находится в нулевом состоянии, и нулевым сигналом на его единичном выхо де запрещается формирование тактовых импульсов генератором 95. В единичное состояние триггер 96 устанавливается по сигналу пуска, поступающему на вход 32 блока 6. Генератор 95 тактовых импульсов формирует на своих выходах 110.1-110.4 четьфе последовательности сдвинутых один относительно другого импульсов только при наличии единичного сигнала на его управляющем входе. Элемент И 9 служит для формирования сигнала на нулевой вход триггера 96 после поступления управляющего сигнала Конец работы с выхода 104 регистра 89 Дешифратор 93 обеспечивает работу устройства в режиме записи сообщений в блоки 5.1-5.п ,вырабатывая сигналы записи, поступающие в один из блоков 5 через коммутатор 9 записи, в соответствии с кодом этого блока на первой группе 59 входов блока 6 при наличии микрооперации Разрешение записи на выходе 105 регистра 89 и при наличии сигнала на выходе 110.3 генератора 95 (фиг. 2). Дешифратор 94 в соответствии с указанным кодом одного из блоков 5 при наличии микрооперации на выходе 106 регистра 89 разрешает вьщачу этим блоком 5 информации через его входвыход 28 на шину 25. Элемент И 98 обеспечивает выработку сигнала записи в блок 3 ОЗБ контроллера, подавае мого на его вход 45 при наличии микрооперации на выходе 107,5 регист ра 89 и сигнала на. выходе 110.3 гене ратора 95. Элемент И 99 обеспечивает выработку синхросигнала записи в регистр 16, подаваемого на его синхровход 78 в момент выработки сигнала на выходе 110.2 генератора 95 и микрооперации на выходе 108.1 регистра 89. Элемент И 100 обеспечивает выработку синхросигнала записи в регистр 17, подаваемого на его синхровход 79 в момент вьфаботки сигнала на выходе 110.4 генератора 95 и микрооперации на выходе 108.3 регйст1326 ра 89. Элемент И 101 обеспечивает вьфаботку сигнала записи в блок 2, подаваемого на его вход 42 записи при наличии микрооперации на выходе 108.4 регистра 89 и сигнала на вьгходе 110.3 генератора 95. Коммутатор 91 управляющих сигналов (фиг. 2 и 11) вьфабатывает сигналы в соответствии с табл. 1, осуществляя коммутацию потоков информации в блоках 5.1-5.П в соответствии с табл. 2, при этом привязка выходов элементов коммутатора 91 управляющих сигналов (фиг. 11) к соответствующим разрядам группы 46 входов каждого блока 5 (фиг. 3) приведенав табл. 1. Узел 86 дешифраторов управления счетчиками служит для вьфаботки сигналов записи и счета для соответствующих счетчиков и регистров блока 7 счетчиков. Причем выработка сигналов записи и счета для каждого иэ счетчиков 122 - 1.24 и группы счетчиков 125.1-125. (фиг. 4) несовместима, так как для каждого из них предусмотрен дешифратор, управляемый сигналом с выхода 110.4 генератора 95 и позволяющий выработку сигнала только на одном из выходов. Так как для каждого из дешифраторов 152155 (фиг. 10) предусмотрена отдельная группа разрядов с выхода 109 регистра 89, то обеспечивается одновременная выработка на одном из выходов сигналов для всех дешифраторов 152-155 или различных их сочетаний. При подаче сигналов микроопераций с выхода 109 регистра 89 (фиг. 2 10) на входы элементов И 156 и 157 В момент выработки сигнала генератором 95 на его выходе 110.3 элементы И 156 и 157 вырабатывают сигналы, поступающие на синхровходы 133 и 134 соответственно регистров 126 и 127 (фиг. 4). Узел 8/ коммутации внешних ЗБ служит для разрешения вьщачи сигналов обращения, записи и адреса.на выходы магистральных элементов 19, 20 и 21 и блока 18 магистральных элементов при выработке сигнала микрооперации на вьгходе 171 группы выхоДов 102 регистра 89 (выход 80 группы 52 выходов узла 87); вьфаботки сигнала счета для счетчика 15 на его выходе 76 с выхода 172.1 элемента И 167.1 при наличии микрооперации на втором разряде группы выходов 102 регистра 89; выработки синхросигнала записи на входе 77 счетчика 15 с выхода 172.2 элемента И 167.2 при наличии микрооперации на третьем разряде группы выхо,дов 102 регистра 89; выработки сигнала обращения к центральному ОЗБ 4 выдаваемого с четвертого разряда 17 группы выходов 102 регистра 89 на информационный вход 81 магистрального элемента 19; выработки сигнала запроса непосредственного доступа к центральному ОЗБ 4, вьщаваемого с пятого разряда 174 группы выходов 102 регистра 89 на выход 36 уст ройства; выработки сигнала записи старшей части блока 4, выдаваемого с выхода 175.1 элемента И 168.1 на магистрального элемента 20, и младшей части блока 4, выдаваемого с выхода 175.2 элемента И 168.2 на вход 83 магистрального элемента 21, причем выработка си налов элементами И 168.1 и 168.2 производится при наличии микроопера ции на шестом разряде 176 группы выходов 102 регистра 89 и сигнала на выходе 110.3 генератора 95 таким образом, что при нулевом значении младшего разряда 63 пятой группы вы ходов 62 блока 7 сигнал вырабатывае ся на выходе 170.1 дешифратора 166 и сигнал записи поступает на выходе 170.1 дешифратора 166 и сигнал записи пос.тупает только на выход 175.1 элемента И 168.1, а при единичном значении младшего разряда 63 (вход 63 дешифратора 166) адр са с выхода 62 блока 7 сигнал выраб тывается на выходе 170.2 дешифратора 166 и, соответственно, на выходе 175.2 элемента И 168.2; выработк сигнала на шестом разряде 176 групп выходов 102 регистра 89 для подачи его через группу входов 84 блока 13 (фиг. 8) на управляющие входы блоков 147 и 148 магистральных (фиг. 8 на управляющие входы блоков 147 и 148 магистральных элементов, что обеспечивает передачу через них информации с входа-выхода 75 блока 13 на его входы-выходы 73.1 и 73.2; выработки сигнала на выходе 177.1 элемента И 169.1 при поступлении микрооперации на седьмой разряд гру пы выходов 102 регистра 89 и нулев значении входа 63 дешифратора 166; данный сигнал, поступая через группу входов 84 блока 13 (фиг. 8) на управляюпщй вход блока 146 магистральных элементов, обеспечивает передачу информации с группы входоввыходов 73.1 блока 13 через блок 146 магистральных элементов на группу входов-выходов 75 блока 13; выработки сигнала на выходе 177.2 элемента И 169.2 при поступлении микрооперации на седьмой разряд группы выходов 102 регистра 89 и единичном значении входа 63 дешифратора 166; данный сигнал, поступая через группу входов 84 блока 13 (фиг. 8) на управляющий вход блока 149 магистральных элементов, обеспечивает передачу информации с группы входов-выходов 73.2 блока 13 через блок 149 магистральных элементов на группу входов-вьгходов 75 блока 13. Блок 7 счетчиков предназначен для обеспечения адресации блоков 1,3 и 5, а также для организации циклов выполнения микропрограмм управления обменом и необходимых переключений при адресации блоков 5.1-5.п. При этом счетчик 122 адреса команд обеспечивает адресацию хранящихся в ПП 1 команд и кодов, являющихся частью этих команд, при выполнении команд в определенном режиме. Счетчик 123 адреса данных осуществляет адресацию данных, расположенных в ОЗБ 3 контроллераi причем, если в ходе выполнения команд программы обрабатывается массив данных, храним 1Х в ОЗБ 3 контроллера для исключения потерь времени и сокращения объема памяти ПП 1 команд уяел 123 выполнен не в виде регистра, а в виде счетчика, содержимое которого автоматически увеличивается на единицу при выборе очередного слова данных из соответствующего массива ОЗБ 3 контроллера. При этом при перемещении данных мкжду ОЗБ 3 контроллера и центральным ОЗБ 4, имеющим формат слова, равный двойному формату слова ОЗБ 3 контроллера, младший разряд 63 адреса ОЗБ 3 контроллера при передаче данных блока 3 в блок 4 обеспечивает выдачу сигнала записи только в старшую часть центрального ОЗБ 4 при нулевом значении младшего разряда 63 адреса либо только в младшую часть блока 4. В противном случае, при передаче данныз из блока 4 в блок 3 младший разряд 63 адреса обеспечивает передачу данных только со старшей части блока 4 через его входы-выходы 74, информацион ную шину 23, входы-выходы 73 (73.1) рходного коммутатора 13, входной ком мутатор 13, его входы-выходы 75, внутреннюю шину 64, шину 31 на входы-выходы ОЗВ 3 контроллера, либо только с младшей части блока 4 на входы-выходы блока 3. Счетчик 124 адреса обеспечивает адресацию блоков 111 и 112 во всех блоках 5 при обрашении к ним от данного устройства по микрооперации обращения , вырабатываемой на выходе 56 блока 6. Счетчики 125.1-125.12 обеспечивают возможность организации программных циклов, причем максимальная глубина вложения циклов в циклах равна 1. Выход из цикла или продолжение его в олнения осуществляется проверкой логического условия переполнения продвинутого одного из счетчиков 125 на мультиплексоре 92 в блоке 6, при этом осуществляется ветвле ние микропрограммы по альтернативным ветвям, организующим этот выход из цикла или продолжение его выполнения . Регистр 126 задает код номера одного из блоков 5, в который поступит сигнал записи или сигнал по его входу 47 на выдачу данных из этого блока 5 через его внутреннюю шину 28 данных на внешнюю магистраль 25 данных . Регистр 127 своим выходом 135.1 обеспечивает коммутацию трансляции сигналов обращения, записи и адресов через соответствующие коммутаторы 10,9 и 11 как от самого устройства, так и извне, поступающих по входу 34 устройства. Выходы 135.1 и 135.2 регистра 127 через коммутатор 91 буферизации осуществляют управление потоками данных внутри одного из блоков 5 в соответствии с табл. 1 и 2. Коммутатор 8 обеспечивает возможность адресации блока 2 как с модификацией, так и без модификации адре са. При работе без модификации адрес сообщения в блоке 2 задается считыванием этого адреса из блока 1 или 2 на внутреннюю шину 64 и далее через коммутатор 8 на вход регистра 17. В случае модификации адрес формируется на сумматоре 14 из адреса преды дущего сообщения, записанного в регистре 17, и косвенного адреса, занесенного в регистр 16. Коммутатор 9 записи (фиг. 5) предназначен для формирования сигнала записи в блоки 5.1-5.п. Выбор одного из блоков 5 осуществляется по сигналам, поступающим с выходов 53 блока 6 управления обменом (фиг. 2 и 5). Для управления записью в блоки 5.1-5.П используются две группы коммутаторов 136.1, 137.1-136.Л, 137.t (фиг.5), причем коммутаторы 136 группы обеспечивают формирование сигнала записи в блоки 112 группы (фиг. 3), а коммутаторы 137 группы - в блоки 111. Перекличение групп коммутаторов 136 и-137 осуществляется сигналом на входе 66 блока 9 (фиг. 5), который, формируется в регистре 127 (фиг. 4) блока 7 . Элемент И 138 обеспечивает стробирование сигнала разрешения записи в случае управления записью внешней системой. Сигнал разрешения записи поступает на вход 49 блока 9 с входа 34 устройства, а стробирующий сигнал - на вход 55 с выхода 110.2 генератора 95 блока 6 (фиг. 2). . Сигналы записи на одном- из разрядов выходов 48.1-48.п блока 9 формируются одновременно при появлении сигнала на выходе элемента И 138 (наличие сигналов на входах 55 и 49 коммутатора 9 записи), а на другом из разрядов появляется сигнал только на одном из выходов 48, поступающий с группы выходов 53 блока 6 в зависимости от его кода в регистре 126 блока 7. Нулевое (единичное) значение сигнала на входе 66 (выход 135.1 регистра 127.блока 7) осуществляет коммутацию сигналов записи на его первые 140 и вторые 141 разряды выходов 48 коммутатора 9 записи (фиг.5) с выхода элемента И 138 и разряда 139 группы входов 53 соответственно (с разряда 139 группы входов 53 и с выхода элемента И 138 соответственно) . Коммутатор 10 обращения (фиг. 6) предназначен для коммутации сигнала обращения., поступающего с выхода 56 блока 6 (фиг. 2) или с разряда обращения группы 34 входов устройства, поступающего на вход 67 коммутатора 10. Выбор блоков 111 или 112 в блоках 5.1-5.П для вьщачи сигнала обращения осуществляется управляющим сигналом, который поступает с выхода 135.1 первого разряда регистра 12 (фиг.4) на управляющий вход 66 в ком мутаторе 10 и обеспечивает выдачу на вход коммутатора 142 (143) (фиг. 6) сигнала с входа 56 (57) или 67 (56). Коммутатор 11 адреса (фиг. 7) предназначен для коммутации адреса блоков 5.1-5.П хранения сообщений, который может поступать с внешнего адресного входа 34 устройства или с выхода 61 блока 7 счетчиков (фиг.4 Выбор блоков 111 и 112 в блоках 5.1З.п для вьщачи адресов на блоки 111 и 112 (фиг. 3) осуществляется аналогично описанному для коммутатора 10. Выходной коммутатор 12 (фиг. 9) предназначен для коммутации передачи информации между внешней магистралью 25 данных (фиг. 1) и внутренней магистралью 64 данных. При наличии сигнала на входе 71 коммутатора 12 (сигнал на входе 72 коммутатора 12 отсутствует) осуществляется передача информации с внутренней магистрали 64 во внешнюю магистраль 25. При наличии сигнала на входе 72 сигнал на входе 71 отсутствует - информация из магистрали 25 передается в магистраль 64. В случае отсутствия сигналов на входах 71 и 72 коммутатора магистральные элементы 150 и 151 (фиг. 9) находятся в высокоимпедансном состоянии. Управ ляющие сигналы на входы 71 и 72 коммутатора 12 поступают с выходов 107.1 и 107.2 группы регистра 89 микрокоманд (фиг. 2) и одновременно выработаться не могут. Срабатывание блоков 146-149 магистральных элементов во входном комму таторе 13 (фиг. 8) осуществляется от сигналов на их управляющих входах аналогично блокам 150 и 151 магистральных элементов в выходном коммута торе 12. Выработка сигналов на группе входов 84 входного коммутатора 13 показана при описании назначения блока 87 управления внешними ЗБ. Устройство работает следующим образом. Фуйкционирование устройства рассмотрено в следующих основных режимах; передача сообщений из(в) бло14332 ка 2 в(из) блок 5; передача сообщений из(в) блока 5 в(из) блок 4. Передача сообп1ений из блока 2 в блоки 5.1-5.П имеет целью обеспечить данными работу процессоров, подключенных к шинам 27.1-27.п. Б режиме передачи сообщений из блока 2 в блоки 5.1-5.П сообщение передается по шине 26 (фиг. 1) в магистраль 25 и далее по шинам 28.1-28.П в блоки 5.1-5 .п. Из блоков 5.1-5.tj процессоры, подключенные к шинам 27.1-27.я, под управлением своих управляющих устройств и программ осуществляют выборку данных из соответствующих блоков 5.1-5.п. Программы управления обменом сообщениями для различных режимов хранятся в ПП 1 команд. В исходном состоянии все регистровые (в том числе счетчики и триггер 96) элементы памяти, за исключением оговоренных ниже разрядов регистра 89, находятся в нулевом состоянии. По сигналу пуска, поступающему н.а вход 32 устройства (фиг. 1), в блоке 6 (фиг. 2) триггер 96 переводится в единичное состояние и включает генератор 95, который на выходах 110.1-110.4 формирует тактовую сетку импульсов, синхронизирующих работу устройства. В счетчике 122 команд (фиг. 4) задан адрес первой (нулевой) команды программы управления обменом, хранящейся в блоке 1 (фиг. 1). В исходном состоянии на выходе 107.3 регистра 89 (фиг. 2) присутствует единичный потенциал, который через выходы 57 блока 6 поступает на вход 39 управления обращением блока 1 (фиг. 2 и 1) и разрешает тем самым считывание из блока 1 команды по адресу, поступающему на выходы 40 блока 1 (фиг. 1) из счетчика 122 блока 7 (Фиг. 4). С выхода 41 блока 1 (фиг. 1) считывается первая команда программы работы устройства, код операции которой поступает на входы 64 блока 6 (фиг. 2) и записывается через коммутатор 90 по тактовому импульсу с выхода 110.1 генератора 95 в регистр 88, содержимое которого задает адрес первой микрокоманды выполнения операции обмена в блоке 85 памяти микропрограмм. В зависимости от типа выполняемой операции обмена (режи33..

ма обмена) в последующих микрокомандах может задаваться считывание из блока 1 и запись соответствующих кон стант в счетчик 15 и регистры 16 и 17, а также счетчики и регистры блока 7 (фиг. 4). При этом адрес считываемой информации из ПП 1 задается счетчиком 122 блока 7 (фиг. 4), а считывание разрешается сигналом микрооперации с выхода 107.3 блока 6 (фиг. 2) и поступает на вход 40 блока 1 (фиг. 1). Адресат определяется сигналом микрооперации с выходов 158.1, 159.1, 160.1, 161.1 161., выходов элементов И 156 и 157 узла 86, а также выход 172.2 элемента 167.2 узла 87 (фиг. 2 и 12) и выходов элементов И 99 и 100 (фиг. 2), поступающим на один из соответствующих выходов блока 7 (фиг. 4): 128.1 - запись адреса команды

в счетчик 122; 129.1 - запись адреса сообщения

(данных) в блоке 3 в счетчик 123;

в счетчики циклов 125.1125.8;

133- запись кода номера канала в регистр 126;

134- запись кода выбора блока 111 или 112 (фиг. 3) в канале регистра 127 или поступающих на входы 77 - 79 соответственно счетчика 15 и регистра 1 6 и 1 7 .

Приращение значений счетчиков 122-125 блока 7 (фиг. 4) осуществляется по сигналам микроопераций, поступающим с выходов 158.2 159.2, 160.2, 162.1 - 162.г узла 86 (фиг. 2 и 10) на соответствующие входы 128.2, 129.2, 130.2, 132.1-132.8 блока 7 (фиг. 4), а приращение значения счетчика 15 осуществляется сигналом, поступающим с выхода 172.1 элемента И 167.1 на его вход 76. ,

Таким образом, рассмотрены принципы адресации блоков 1 - 3 и управления их работой. Для пояснения процессов, протекающих в устройстве при обмене сообщениями между блоками 2

34

136143

И 5.1-5.п, рассмотрим адресацию блока 2. Считанная информация из блока 1 может опредять адрес обращения к блоку 2, который с выхода 41 блока 1 поступает на вход 64 коммутатора 8 и записывается в регистр 17. При этом коммутатор 8 открывается сигналом, поступающим с выхода 108i2 регистра 89 (фиг. 2), а регистр 17 управляется импульсом, формируемым на выходе элемента И 100 по сигналу с выхода 110.4 генератора 95.

Кроме того, считанная информация из блока 1 может определить константу, которая записывается в регистр 16 (фиг. 1) и обеспечивает модификацию адреса обращения к блоку 2. Управляющий импульс записью в регистр 16 формируется на выходе элемента И 99

0 (фиг 2) по такту с выхода 110.2 генератора 95.

Модификация адреса осуществляется сумматором 14 (фиг. 1) путем сложения значения константы из регистра 16 со значением адреса, поступающего на другой вход сумматора 14 регистра 17.

Такой способ адресации блока 2 позволяет реализовать гибкие алгоритмы обращения к ячейкам 2, т.е. ячейки блока 2 могут выбираться последовательно с постоянным шагом выборки (значение регистра 16 не изменяется) либо с переменным шагом

5 (значение регистра 16 изменяется по заданному закону).

Таким образом, адрес обращения к блоку 2 поступает с выхода регистра 17. Сигнал обращения поступает

0 на вход 43 блока 2 с выхода 108.5 регистра 89 (фиг. 2).

Считывание информации из блока 2 осуществляется под управлением микропрограммы блока 6, группа 54 выходов которого определяет сигналы микрооперации управления записью в регистры 16 и 17 (выходы 78 и 79 соответственно), управления.коммутатором 8 (вход 65), обращения

O к блоку 2 (вход 43). Труппа 57 выходов блока 6 определяет сигналы обращения к блоку 1 (вход 39) и блоку 3 (вход 44).

Запись сообщения в соответствующий

5 блок 5 производится при наличии -на его входах следующей информации (фиг. 1): сигнгша записи с соответствующего выхода 48 коммутатора 9

писи; сигнала обращения с выхода 68 коммутатора 10 обращения; кода адреса на выходе 69 (70) коммутатора 11 адреса; кода сообщения, поступающего с соответствующей шины 28; сигнала конфигурации потока данных в этом блоке 5 с выходов 46 блока 6.

При передаче сообщения из блока 2 в один из блоков 5, как рассмотрено выше, адрес передаваемого сообщения из регистра 17 (фиг. 1) подается на адресный вход блока 2. Так как в этом случае блок 2 используется в режиме чтения, то сигнал записи . на входе 42 не формируется. По сигналу обращения, поступающему с вьрсода 108.5 микроопераций блока 6 (фиг. 2) на вход 43 блока 2, информация через шину 26, магистраль 25 и группу шин 28 поступает на входы блоков 5.1-5.п. Поскольку блоков 5, которому адресовано сообщение, работает в режиме записи, то для этого блока на соответствующем выходе 48 коммутатора 9 формируется сигнал записи, на выходе 68 коммутатора 10 - сигнал обращения, на выходе 69 (70) ко1 1мутатора 11 - адрес приема сообщения в блок 112 (111) (фиг. 3), на выходе 46 блока 6 - си нал выбора блока 111 или 112, на вхдах 121.1 (121.2), 121.4 (121.5) сигналы подключения шины 28 к блоку 111 (112).

Таким образом, в зависимости от состояния сигналов на входах 121.1 и 121.2 данного блока 5 (фиг. 3) запись сообщения произойдет в один из блоков 111 или 11-2 выбранного блока 5.

Б дальнейшем сообщение из одного из блоков 5 может быть передано сооветствующему процессору, подключенному к одной из шин 27, либо в блок Процесс передачи сообщения соответствующему процессору через шину 27 из определенного блока 5 осуществляется по жесткому алгоритму. Процесор выставляет адрес сообщения в один из блоков 5 на вход 34 устройства. Блок 6 управления обменом последовательно представляет квант времени для выборки сообщения из этого блока 5 соответствующего процессора, при этом в случае единичного (нулевого) сигнала на входе 121.4 и единичного на входе 121. (фиг. 3) разрешается выборка сообще336

НИИ из блока 111 (112) соответствующего блока 5.

В устройстве возможно параллельное выполнение процессов передачи сообщений из блоков 5.1-5.и сооответствующим процессорам и записи сообщений из блока 2 в блоки 5.1-5.П, кроме того, параллельно с работой процессоров возможна передача сообщений из блоков 5.1-5.П в блоки 2-4. Это позволяет сократить общее время обработки заданного объема информации.

Для примера рассмотрим процесс. передачи сообщений из блоков 5.1-5.п в блок 4 и записи сообщений от процессоров в соответствующие блоки 5.1-5.h. Такое совмещение возможно по той причине, что каждый блок 5 (фиг. 3) содержит два блока (111 и 112) принятия сообщений. Для конкре гности предположим, что в выбранном блоке 5 блок 111 используется для приема сообщений с шины 27, а блок 112 - для выдачи сообщений в шину 28. Рассмотрим, какие сигналы формируются в устройстве для этого случая.

Адрес записи(считывания) в(из) блок 111(112) соответствующего блока 5 может задаваться с входа 34 устройства (фиг. 1) или счетчиком 124 блока 7 (фиг.4). На входе 34 устройства адрес задается процессором высшего уровня по отношению к процессорам, подключенным к шинам 27.1-27.п.