Изобретение относится к контрольно-измерительной технике и может быть Использовано при проверке цифровых устройств.

Целью изобретения является расширение функциональных возможностей, попьппение быстродействия за счет

блока 15 сравнения напряжений соединен с первым входом логического преобразователя 20, четвертый вход которого подключен к входу 7 теста на- г рузки, второй вход соединен с выходом блока 2 сравнения напряжений, а третий вход подключен к выходу блока 5 сравнения напряжений. Выходы

контроля высокоимпедансного состояния и применения форсированного режи- IQ логического преобразователя 20 соеди- ма разряда паразитных емкостей. нет. с входами индикатора 21 и с логическими выходами 22 зонда.

На фиг.2 представлен один из возможных вариантов блока 9 нагрузки, 15 выполняющий операции, требующиеся для работы устройства. Блок 9 нагрузки состоит из шести резисторов, диода транзистора и инвертора с открытым

На фиг.1 представлена функциональная схема зонда, состоящего из первого регулируемого источника 1 опорного напряжения, выходом соединенного с первым входом первого блока 2 сравнения напряжений, второй вход которого подключен к второму входу блока 3 сравнения напряжений, к щупу Дик первому входу блока 5 сравнения напряжений, второй вход которого соединен с выходом второго регулируемого Источника 6 опорного напряжения. Вход 7 теста нагрузки соединен с первым входом логического преобразователя 8 и с первым входом блока 9 нагрузки. Второй и третий входы логического преобразователя 8 соединены соответственно с прямым и инверсным выходами блока 3 сравнения напряжений, а четвертьм вход логического преобразователя В подключен к второму выходу блока 9 нагрузки. Щуп А соединен через резистор 10 с выходом первого электронного ключа 11, непосредственно подключен к первому выводу резистора 12 и к входу второго электронно г-о ключа 13, выход которого через резистор 14 соединен с вторым выводом резистора 12, с входом первого электронного ключа 11,с первым выходом блока 9 нагрузки, второй вход которого подключен к входу управления первого электронного ключа 1 1 и к перколлектором 23, входом соединенного

20 с первым входом блока 9 нагрузки, а выходом подключенного к второму выходу блока ,9 нагрузки непосредственно, а через резистор 24 - к первому выходу блока 9 нагрузки и к коллекто25 ру транзистора 25, база которого через резистор 26 соединена с третьим нходом блока 9 нагрузки. Эмиттер транзистора 25 через резистор 27 соединен с шиной питания, которая через

30 резистор 28 подключена к первому вы- ходу блока 9 нагрузки, который, в свою очередь, через резистор 29 подключен к общей шине, а непосредственно соединен с анодом диода 30, катод

2(- которого через резистор 31 соединен с вторым входом блока 9 нагрузки.

На фиг.З представлен пример реализации логического преобразователя 8, состоящего из элемента И-НЕ 32, пер40 вым входом соединенного с четвертым нходом логического преобразователя 8, вторым входом подключенного к второму входу логического преобрйзо- вателя 8, а выходом соединенного с

Бому выходу логического преобразовате- 45 ервым выходом логического преобраля 8. TpBTHi i вход блока 9 нагрузки соединен с входом управления второго электронного ключа 13 и с вторым выходом логического преобразователя 8. Вход второго электронного ключа 13 соединен с перв;)1м входом блока 15 сравнения напряжений, второй вход которого через резистор 16 подключен к первому выходу блока 9 нагрузки, а через резистор 17 - к первому входу блока 3 сравнения напряжений, которьш в свою очередь через резистор 18 подключен к шине питания, а через резистор 19 соединен с общей шиной. Выход

блока 15 сравнения напряжений соединен с первым входом логического преобразователя 20, четвертый вход которого подключен к входу 7 теста на- г рузки, второй вход соединен с выходом блока 2 сравнения напряжений, а третий вход подключен к выходу блока 5 сравнения напряжений. Выходы

логического преобразователя 20 соеди- нет. с входами индикатора 21 и с логическими выходами 22 зонда.

коллектором 23, входом соединенного

с первым входом блока 9 нагрузки, а выходом подключенного к второму выходу блока ,9 нагрузки непосредственно, а через резистор 24 - к первому выходу блока 9 нагрузки и к коллектору транзистора 25, база которого через резистор 26 соединена с третьим нходом блока 9 нагрузки. Эмиттер транзистора 25 через резистор 27 соединен с шиной питания, которая через

резистор 28 подключена к первому вы- ходу блока 9 нагрузки, который, в свою очередь, через резистор 29 подключен к общей шине, а непосредственно соединен с анодом диода 30, катод

которого через резистор 31 соединен с вторым входом блока 9 нагрузки.

На фиг.З представлен пример реализации логического преобразователя 8, состоящего из элемента И-НЕ 32, первым входом соединенного с четвертым нходом логического преобразователя 8, вторым входом подключенного к второму входу логического преобрйзо- вателя 8, а выходом соединенного с

зователя 8, и элемента И-НЕ 33, первым входом соединенного с первым входом логического преобразователя 8, вторым входом подключенного к треть 50 му входу логического преобразователя 8, а выходом соединенного с вторым выходом логического преобразователя 8.

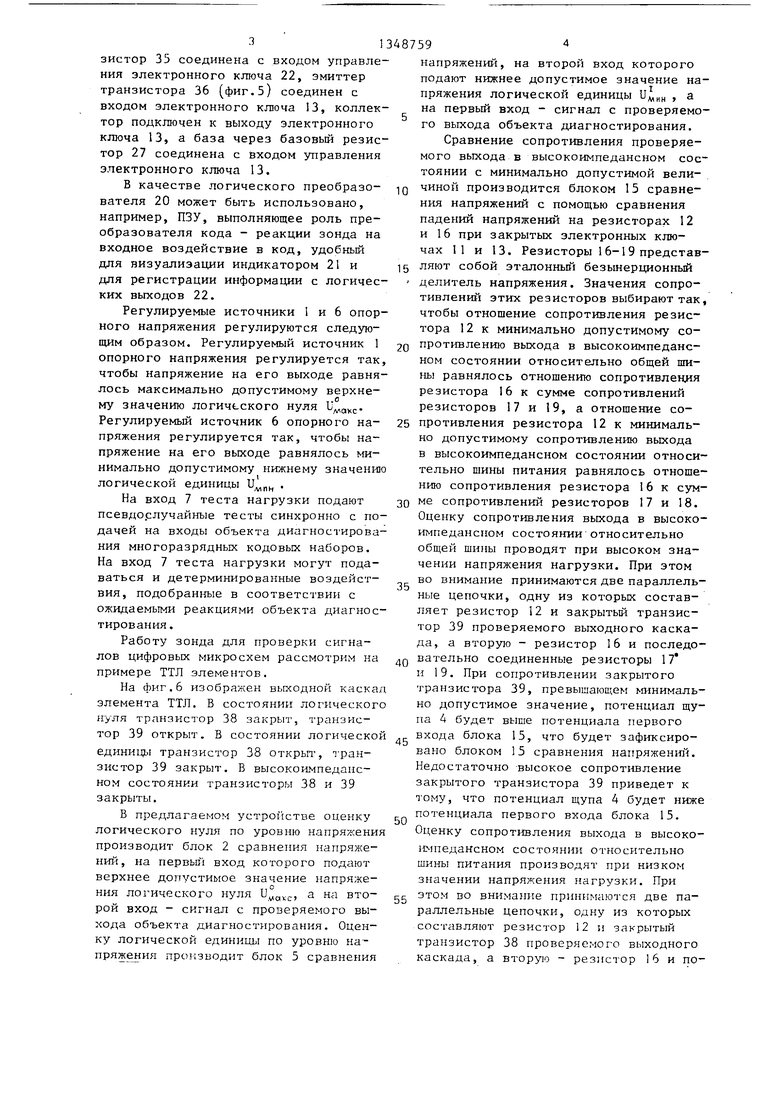

В качестве электронных ключей 11 и 13 могут быть использованы, напри55 мер, транзисторы р-п-р типа, при этом коллектор транзистора 34 (фиг.4) соединен с выходом электронного ключа 11, эмиттер подключен к входу электронного ключа 11, а база через базовый резистор 35 соединена с входом управления электронного ключа 22, эмиттер транзистора 36 (фиг.5) соединен с входом электронного ключа 13, коллектор подключен к выходу электронного ключа 13, а баэа через базовый резистор 27 соединена с входом управления электронного ключа 13.

В качестве логического преобразователя 20 может быть использовано, например, ПЗУ, выполняющее роль преобразователя кода - реакции зонда на входное воздействие в код, удобньш для визуализации индикатором 21 и для регистрации информации с логических выходов 22.

Регулируемые источники 1 и 6 опорного напряжения регулируются следующим образом. Регулируемый источник 1 опорного напряжения регулируется так чтобы напряжение на его выходе равнялось максимально допустимому верхнему значению логического нуля U. Регулируемый источник 6 опорного напряжения регулируется так, чтобы напряжение на его выходе равнялось минимально допустимому нижнему значению

-,1 логической единицы .

На вход 7 теста нагрузки подают псевдослучайные тесты синхронно с подачей на входы объекта диагностирования многоразрядных кодовых наборов. На вход 7 теста нагрузки могут подаваться и детерминированные воздействия, подобранные в соответствии с ожидаемыми реакциями объекта диагностирования .

Работу зонда для проверки сигналов цифровых микросхем рассмотрим на примере ТТЛ элементов.

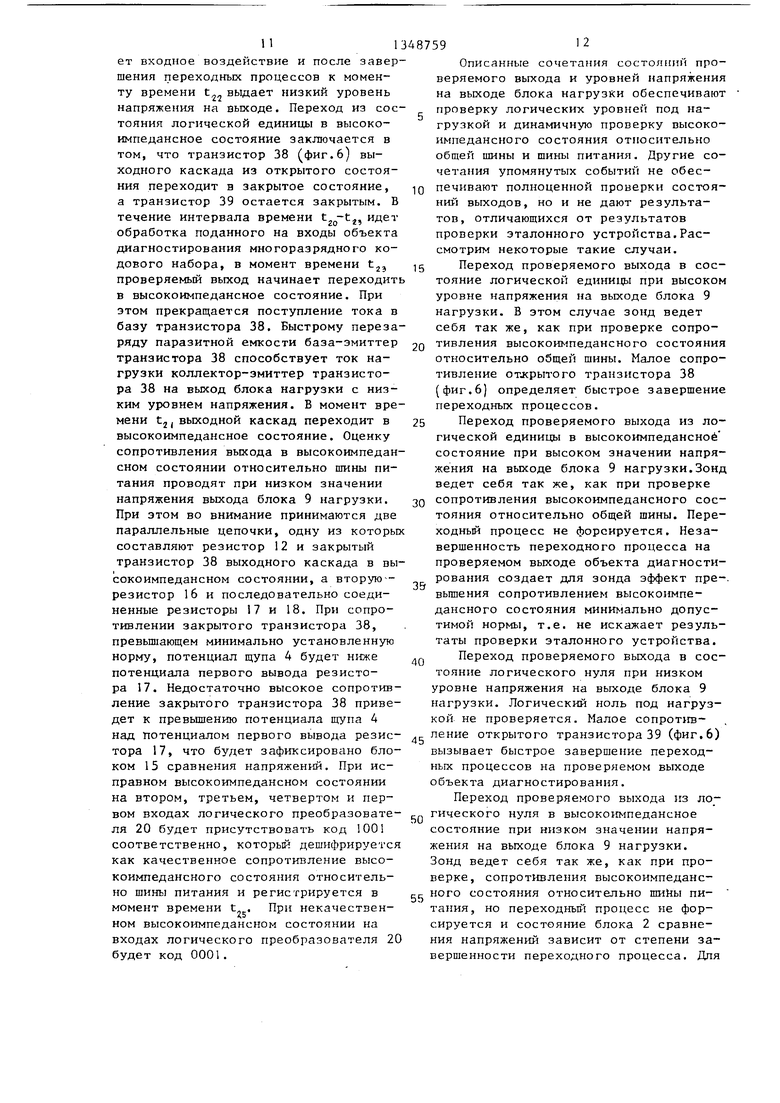

На фиг.6 изображен выходной каска элемента ТТЛ. В состоянии логическог нуля транзистор 38 закрыт, транзистор 39 открыт. В состоянии логическо единицы транзистор 38 открьп , транзистор 39 закрыт. В высокоимпеданс- ном состоянии транзисторы 38 и 39 закрыты.

В предлагаемом устрот гстве оценку логического нуля по уровню напряжени производит блок 2 сравнения напряжений, на первьп вход которого подгиот верхнее допустимое значение напряжения логического нуля U.,g(,, а на второй вход - сигнал с проверяемого выхода объекта диагностирования. Оценку логической единицы по уровню напряжения производит блок 5 сравнения

5

0

напряжений, на второй вход которого подают нижнее допустимое значение напряжения логической единицы U , а на первый вход - сигнал с проверяемого выхода объекта диагностирования.

Сравнение сопротивления проверяемого выхода в высокоимпедансном состоянии с минимально допустимой величиной производится блоком 15 сравнения напряжений с помощью сравнения падений напряжений на резисторах 12 и 16 при закрытых электронных ключах 11 и 13. Резисторы 1 6-1 9 представляют собой эталонный безьшерционный делитель напряжения. Значения сопротивлений этих резисторов выбирают так, чтобы отношение сопротивления резистора 12 к минимально допустимому сопротивлению выхода в высокоимпедансном состоянии относительно общей тины равнялось отношению сопротивления резистора 16 к сумме сопротивлений резисторов 17 и 19, а отношение со- 5 противления резистора 12 к минимально допустимому сопротивлению выхода в высокоимпедансном состоянии относительно шины питания равнялось отношению сопротивления резистора 16 к сум- 0 ме сопротивлений резисторов 17 и 18. Оценку сопротивления выхода в высокоимпедансном состоянии относительно общей шины проводят при высоком значении напряжения нагрузки. При этом во внимание принимаются две параллельные цепочки, одну из которых составляет резистор 12 и закрытьй транзистор 39 проверяемого выходного каскада, а вторую - резистор 16 и последовательно соединенные резисторы 17 и 19. При сопротивлении закрытого транзистора 39, превышающем минимально допустимое значение, потенциал щупа 4 будет выше потенциала первого входа блока 15, что будет зафиксировано блоком 15 сравнения напряжений. Недостаточно высокое сопротивление закрытого транзистора 39 приведет к тому, что потенциал щупа 4 будет ниже потенциала первого входа блока 15. Оценку сопротивления выхода в высокоимпедансном состоянии относительно шины питания производят при низком значении напряжения нагрузки. При этом во внимание принимаются две параллельные цепочки, одну из которых составляют резистор 12 и закрытый транзистор 38 проверяемого выходного каскада, а вторую - резистор 16 и по5

0

5

0

5

следовательно соединенные peзиcтo- ры 17 н 18. При сопротивлении закрытого транзистора 38, превышающем минимально допустимое значение, потенциал щуна 4 будет ниже потенциала первого входа блока 15, что будет за фиксировацо блоком 15 сравнения напряжений. Недостаточно высокое сопротивление закрытого транзистора 38 приведет к тому, что потенциал щупа А будет выше потенциала первого входа блока 15.

В существующих устройствах точность измерения сопрот1шления высоко импедансного состояния находится в противоречии с быстродействием. При фиксированной чувствительности блока 15 сравнения напряжений повысить точность измерения можно увеличением до некоторой степени сопротивления резистора 12, но при этом затрудняется перезаряд паразитных емкостей выходного каскада объекта диагностирования, что приводит к понижению быстродействия. Для уменьшения упомянутого противоречия приняты меры по форсированному перезаряду паразитных eMKOcTei t, которые осуществляются с помощью блока 3 сравнения напряжений логичес кого преобразователя 8, бло- ка 9 нагрузки, резисторов 10, 14 и 17, электронных ключей 11 и 13.

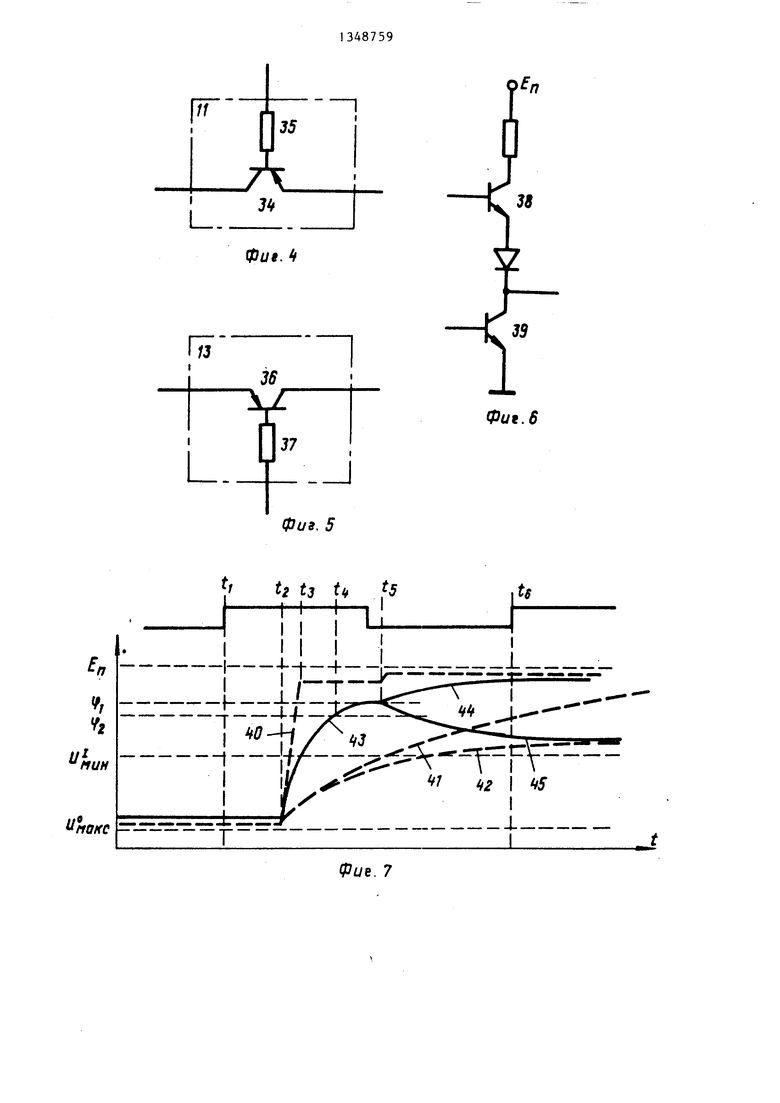

Предположим в исходном состоянии проверяемый выход находится в высоко импедансном состоянии, при котором транзисторы 38 и 39 закрыты, а блок 9 нагрузки выдает низкий уровень напряжения на выходе (фиг.7). Допустим в момент времени t, на входы объекта диагностирования подают многоразряд- Hbrfi кодовый набор, реакцией проверяемого вЕзГкода }ia которьй также является высокоимпендансное состояние. Од- ноБ11емепно на вход 7 теста нагрузки подают воздействие, которое создаст на зыходе блока 9 нагрузки высокий уровень напряжения. В течение интервала времени t, -t,, блок 9 нагрузки обрабатывает входное воздействие и после завершения переходных процессов к моменту времени t. выдает высоКИ11 уровень напряжения на выходе (кривая АО на фиг.7). При отсутствии формирующих цепеГ, которые составляют резисторы 10 и 14 и электронные ключи 1 1 и 13, перезаряд паразитных емкостей проверяемого выхода объекта диагностирон..ния происходит через

10

15

20

25

3487596

резистор 12 с постоянной времени, определяемой величиной этого резистора и собственными цепями разряда (кривые 4 и 42 для исправного и неисправного высокоимпедансного состояния соответственно ).

Работа форсирующих цепей происходит следующим образом. Одновременно с переходными процессами на выходе блока 9 нагрузки, завершаются переходные процессы на резисторе 17 безынерционного эталона высокоимпедансного состояния. В момент времени t устанавливается критический потенциал t|| на первом выводе резистора 17. На несколько процентов ниже устанавливается потенциал ср на втором выводе резистора 17. При незавершенньсх переходных процессах на проверяемом выходе объекта диагностирования по- тенциал щупа 4 ни7;се потенциала второго вывода резистора 17, отчего блок 3 сравнения напряжений с прямого выхода выдает логическую единицу на второй вход логического преобразовате- ля В, которая совместно с логической единицей на четвертом входе логичес- р;ого преобразователя 8 создает на первом выходе логический ноль, который по входу управления открывает электронный ключ П. Одновременно по второму входу блока 9 нагрузки логи- ческ1ш ноль обеспечивает ток через резистор 28, диод 30, резистор 31, шу1ггирующее действие которого снижает на заданную величину высокий уро- ве}1Ь напряжения на первом выходе блока нагрузки. Снижение высокого уровня напряжения на выходе блока 9 нагрузки происходит до такой степени, чтобы при минимально допустимом значении сопротивления высокоимпедансного состояния и открытом электронном ключе 11 на щупе установился потенци- ;ш, приближающийся, но не достигаю- ци}т критического потенциала первого иывода резистора 17. При этом происходит форсированньш перезаряд паразитных емкостей проверяемого выхода объекта диагностирования с постоянной времени, определяемой сопрот1шлением резистора 12, параллельно подключенному ему резистора 10 с открытым электронным ключем 1I и собственньми це- пями разряда (кривая 43 на фиг.7). В момент времени t. потенциал щупа 4 сравнивается с потенциалом второго вывода резистора 17 и затем начинает

30

35.

40

45

50

55

71

его превосходить. Блок 3 сравнения напряжений логическую единицу на прямом выходе изменяет на ноль, вследствие чего логической единицей с первого выхода логического преобразователя 8 закрывается электроиньй ключ 11 и одновременно повышается напряжение на выходе блока 9 нагрузки. Отрезок времени равен времени срабаты- вания блока 3 сравнения напряжен, логического преобразователя 8, блока 9 нагрузки и электронного ключа 11. После момента времени tg начинается завершающая стадия переходного процесса с постоянной времени, опре- деляемой величиной сопротивления резистора 12 и собственными цепями разряда выходного каскада. Кривая 4А ха- рактеризует переход1 Ой процесс ис- правного высокоимпедансного состояния, а кривая 45 - неисправного (фиг,7). В момент времени tg регистрируют результат анализа зондом состояния проверяемого выхода. Выше рас- смотрена работа форсируюш,их цепей при оценке сопротивления высокоимпедансного состояния относительно общей шины. Аналогично происходит работа цепей форсирования переходных про- цессов. при оценке сопротивления высокоимпедансного состояния относительно шины питания (фиг.8).

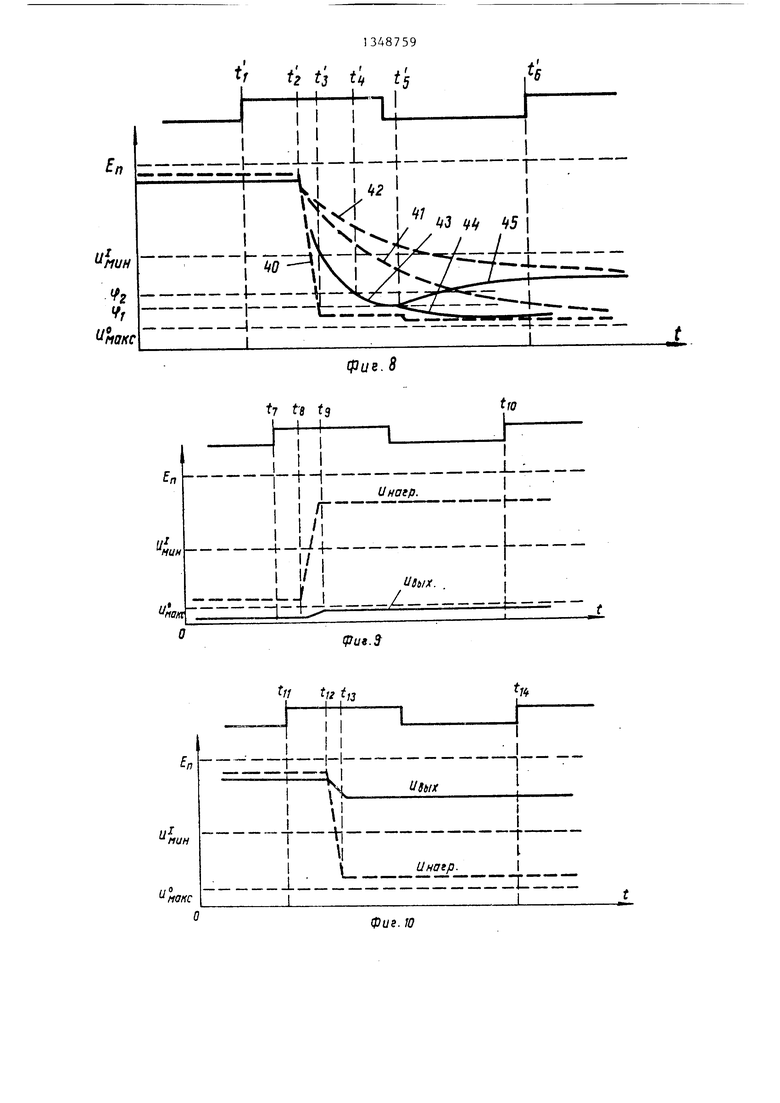

Проверка логического нуля. Предположим в исходньп момент времени про- веряемый выход объекта диагностирования находится в состоянии логического нуля, а блок нагрузки выдает низкий уровень напряжения.

Допустим в момент времени t (фиг.9) на входы объекта диагностирования подают многоразрядный кодовый набор, который создаст на прореряе- мом выходе состоя}п- е логического нуля. Одновременно на вход 7 теста на- грузки подают воздействие, которое создаст на выходе блока 9 нагрузки высокий уровень напряжения. В течение интервала времени блок нагрузки обрабатывает поступиви:ее воз- действие и после завершения переходных процессов к моменту времени t, выдает высокое значение напряжения нагрузки, при котором открытый транзистор 39 (фиг.6) проверяемого выход- кого каскада нагружается максимально допустимым током по цепи: первый выход блока 9 нагрузки, откр1 1тый элект- pOHHbrii ключ П, резистор 10, частич

В

5 0 5 0

о 5 Q g

но через резистор 12, щуп 4, откры- Tboi транзистор 39, обшая шина. В данной ситуации электрониьп ключ 1 1 открыт логическим нулем с выхода первого логического преобразопател; 8, В момент времени t,, на щупе присутствует низкий уровень напряжения, вызванный логическим нулем на проверяемом выходе, а на втором выводе резистора 17 имеет место высокий потенциал, вызванньй высоким уровнем напряжения на выходе блока 9 нагрузки. Такое сочетание рассматривается блоком 3 сравнения напряжений и логическим преобразователем 8 как пезавершенньп переходньп процесс, которые принимают меры для форсированного перезаряда паразитных емкостей. Но в данном случае это состояние стабильно и упомя- ну1Ъ1е вьше меры нагружают выходной каскад максимально разрешенным током. В момент времени под воздействием максимальной нагрузки уровень сигнала проверяемого выхода несколько повышается, но для Исправного выхода он не

О

должен превьш1ать ч ° определяет блок 2 сравнения напряжений. На втором, третьем, четвертом и первом входах логического преобразователя 20 будет присутствовать кодовый набор 1100 соответственно, что депшфрирует- ся как качественный логическш ноль, проверенный под нагрузкой и регистрируется в момент времени t..

Проверка логической единицы. Предположим в исходньй момент времени проверяемы выход объекта диагностирования находится в состоянии логической единицы, а блок 9 нагрузки выдает высокий уровень напряженш.

Допуст гм в момент времени t,, (фиг.10) на входы объекта диагностирования подают многоразряд}1ьш кодовый набор, который создаст нл проверяемом выходе состояние логической единицы. Одновременно на вход 7 теста нагрузки подают воздействие, которое создаст на выходе блока 9 нагрузки низкий уровень напряжения. В течение интервала времени t,,-t, блок нагрузки обрабатьшает входное воздействие и после за-верщения переходных процессов к моменту времени t ,. выдает низкое значение напряжения }1агруяки, при котором открытьв транзистор 38 проверяемого выходного каскпдл нагружается максимально разреглеши гм током по цепи: источник питания об текта диагностировання, открытый транзистор 38, выход объекта диагностирования, щуп 4, Открытый электронный . ключ 13, резистор 14, частично через резистор 12, выход блока нагрузки, общая шина. В момент времени на

ческого нуля в высокоимпедансное сос- тояние заключается в том, что транзистор 39 (фиг.6) из открытого состояния пефеходит в закрытое состояние, а транзистор 38 остается закрытым. В течение интервала времени t,5.-t,g идет обработка поданного на входы объекта диагностирования многоразрядного

щупе присутствует высокий уровень напряжения, вызванный логической единицей на проверяемом выходе, а на Q втором выводе резистора 17 имеет место низкий потенциал, вызванный низким уровнем напряжения на выходе блока 9 нагрузки. Такое сочетание потенциалов рассматривается блоком 3 срав- g ряду емкости база-эмиттер транзисто- нения напряжений и логическим преоб- ра 39 способствует ток нагрузки кол- разователем 8 как незавершенный переходный процесс, в результате чего на первом и втором выходах логического

дового набора и в момент времени t проверяемый выход начинает переходит в высокоимпедансное состояние. При этом прекращается поступление тока в базу транзистора 39. Быстрому переза

лектор-эмиттер транзистора 39 от блока нагрузки с высоким уровнем напряжения на выходе. Этим достигается

преобразователя 8 присутствует код 10,2о быстрый переход транзистора 39 в закоторый открывает электронный ключ 13 и закрьгаает электронный ключ II. В момент времени t,, под воздействием максимально допустимого тока нагрузки уровень сигнала проверяемого выхода несколько понижается, но для исправного выхода он не должен опуститься ниже , т.е. ниже уровня, который регистрирует блок 5 сравнения напряжений. На втором, третьем, четвертом, и первом входах логического преобразователя 20 будет присутствовать код ООП, что дешифрируется как качественная логическая единица, проверенная под нагрузкой, и регистрируется в момент времени t,4 Проверка сопротивления выхода в высокоимпедансном состоянии относительно общей шины. Предположим в исходный момент времени проверяемый выход находится в состоянии логического нуля, при котором транзистор 38 закрыт, а транзистор 39 открыт (фиг.6), блок нагрузки выдает низкий уровень напряжения (фиг.11). Допустим в момент времени t, на входы объекта диагностирования подают многоразрядный кодовый набор, которьй создаст на проверяемом выходе высокоимпедансное состояние. Одновременно на вход 7 теста нагрузки подают воздействие, которое создаст на выходе блока нагрузки высокий уровень напряжения. В течение интервала времени блок нагрузки обрабатывает поданное воздействие и после завершения переходных процессов к моменту времени t,, выдает высокий уровень напряжения на выходе. Переход из состояния логи4875910

ческого нуля в высокоимпедансное сос- тояние заключается в том, что транзистор 39 (фиг.6) из открытого состояния пефеходит в закрытое состояние, а транзистор 38 остается закрытым. В течение интервала времени t,5.-t,g идет обработка поданного на входы объекта диагностирования многоразрядного g ряду емкости база-эмиттер транзисто- ра 39 способствует ток нагрузки кол-

в

ряду емкости база-эмиттер транзисто- ра 39 способствует ток нагрузки кол-

дового набора и в момент времени t проверяемый выход начинает переходить в высокоимпедансное состояние. При этом прекращается поступление тока в базу транзистора 39. Быстрому перезаряду емкости база-эмиттер транзисто- ра 39 способствует ток нагрузки кол-

лектор-эмиттер транзистора 39 от блока нагрузки с высоким уровнем напряжения на выходе. Этим достигается

5

0

5

0

5

0

5

крытое состояние и, как следствие, повьшение быстродействия при проверке вьпсодов с тремя устойчивыми состояниями. После завершения переходных процессов потенциал щупа 4 при исправном высокоимпедансном состоянии будет выше потенциала первого вывода резистора 17, что фиксирует блок 15 сравнения напряжений. На втором, третьем, четвертом и первом входах логического преобразователя 20 будет присутствовать код 0010 соответственно, что дешифрируется как качественное сопротивление высокоимпе- i дансного состояния относительно об- щеЛ шины и регистрируется в момент времени t,,. При некачественном высокоимпедансном состоянии на входах логического преобразователя 20 будет код 1010.

Проверка сопротивления выхода в высокоимпедансном состоянии относительно шины питания. Предположим в исходном состоянии проверяемый выход находится в логической единице, при которой транзистор 38 (фиг.6) открыт, транзистор 39 закрыт, а блок 9 нагрузки вьщает на выходе высокий уровень напряжения (фиг.12).

Допустим в момент времени t на входы объекта диагностирования подают многоразрядный кодовый набор, который создаст на проверяемом выходе высокоимпедансное состояние. Одновременно на вход 7 теста нагрузки подают воздействие, которое создаст на выходе блока 9 нагрузки низкий уровень напряжения. В течение интервала времени блок 9 нагрузки обрабатываП1348759

т входное воздействие и после заверения переходных процессов к моменвена пр гр им об че пе ни то пр см

ту времени t вьщает низкий уровень напряжения на выходе. Переход из состояния логической единицы в высоко- импедансное состояние заключается в том, что транзистор 38 (фиг.б) выходного каскада из открытого состояния переходит в закрытое состояние, а транзистор 39 остается закрытым. В течение интервала времени , идет обработка поданного на входы объекта диагностирования многоразрядного кодового набора, в момент времени проверяемый выход начинает переходит в высокоимпедансное состояние. При этом прекращается поступление тока в базу транзистора 38. Быстрому перезаряду паразитной емкости база-эмиттер транзистора 38 способствует ток нагрузки коллектор-змиттер транзистора 38 на выход блока нагрузки с низким уровнем напряжения. В момент времени tj J выходной каскад переходит в высокоимпедансное состояние. Оценку сопротивления выхода в высокоимпедан сном состоянии относительно шины питания проводят при низком значении напряжения выхода блока 9 нагрузки. При этом во внимание принимаются две параллельные цепочки, одну из которы составляют резистор 12 и закрытый транзистор 38 выходного каскада в вы сокоимпедансном состоянии, а вторую-- резистор 16 и последовательно соединенные резисторы 17 и 18. При сопротивлении закрытого транзистора 38, превьш1ающем минимально установленную норму, потенциал щупа 4 будет ниже потенциала первого вывода резистора 17. Недостаточно высокое сопротивление закрытого транзистора 38 приведет к превышению потенциала щупа 4 над ттотенциалом первого вывода резистора 17, что будет зафиксировано блоком 15 сравнения напряжений. При исправном высокоимпедансном состоянии на втором, третьем, четвертом и первом входах логического преобразователя 20 будет присутствовать код 100 соответственно, который дешифрируется как качественное сопротивление высо- коимпедансного состояния относительно шины питания и регистрируется в

момент времени t

as

При некачественном высокоимпедансном состоянии на входах логического преобразователя 20 будет код 0001.

12

0

5

0

5

0

5

0

5

O

5

Описанные сочетания состояний проверяемого выхода и уровней напряжения на выходе блока нагрузки обеспечивают проверку логических уровней под нагрузкой и динамичную проверку высоко- импедансного состояния относительно общей шины и шины питания. Другие сочетания упомянутых событий не обеспечивают полноценной проверки состояний выходов, но и не дают результатов, отличающихся от результатов проверки эталонного устройства.Рассмотрим некоторые такие случаи.

Переход проверяемого выхода в состояние логической единицы при высоком уровне напряжения на выходе блока 9 нагрузки. В этом случае зонд ведет себя так же, как при проверке сопротивления высокош.{педансного состояния относительно общей шины. Малое сопротивление открытого транзистора 38 (фиг.6) определяет быстрое завершение переходных процессов.

Переход проверяемого выхода из логической единицы в высокоимпедансное состояние при высоком значении напряжения на выходе блока 9 нагрузки.Зонд ведет себя так же, как при проверке сопротивления высокоимпедансного состояния относительно общей шины. Переходный процесс не форсируется. Незавершенность переходного процесса на проверяемом выходе объекта диагностирования создает для зонда эффект пре-. вьшения сопротивлением высокоимпедансного состояния минимально допустимой нормы, т.е. не искажает результаты проверки эталонного устройства.

Переход проверяемого выхода в состояние логического нуля при низком уровне напряжения на выходе блока 9 нагрузки. Логический ноль под нагрузкой не проверяется. Малое сопротугв- ление открытого транзистора 39 (фиг.6) вызывает быстрое завершение переходных процессов на проверяемом выходе объекта диагностирования.

Переход проверяемого выхода из логического нуля в высокоимпедансное состояние при низком значении напряжения на выходе блока 9 нагрузки. Зонд ведет себя так же, как при проверке, сопротивления высокоимпедансного состояния относительно шийы пи- тания, но переходный процесс не форсируется и состояние блока 2 сравнения напряжений зависит от степени завершенности переходного процесса. Для

13

устранения неоднозначности реакции зонда предназначено соединение входа 7 теста нагрузки с первым входом логического преобразователя 20, которое блокирует в преобразователе 20 сигнал блока 2 сравнения напряжений при низком значении напряжения на выходе блока 9 нагрузки. Незавершенность переходного процесса на проверяемом выходе объекта диагностирования создает для зонда эффект превышения сопротивлением высокоимпеданс- ного состояния минимально допустимой нормы, т.е. не искажает результаты проверки эталонного устройства.

Формула изобретения

Зонд для проверки сигналов цифровых микросхем, содержащий первый резистор, индикатор, щуп, первый логический преобразователь, три блока сравнения напряжений, два регулируемых источника опорного напряжения, первый из которых соединен выходом с первым входом первого блока сравнения напряжений, второй вход которого соединен со щупом и первым входом второго блока сравнения напряжений, с первым входом третьего блока сравнения напряжений, второй вход которого соединен с выходом второго регилуремого источника опорного напряжения, первый вьшод первого резистора соединен с клеммой для подключения источника напряжения, первый логический преобразователь соединен первым входом с выходом второго блока сравнения на- пряженн}, вторым входом - с выходом первого блока сравнения напряжений, третьим входом - с выходом третьего блока сравнения напряжений, выходы первого логического преобразователя соед гаены с входами индикатора, отличающийся тем, что, с целью расширения функциональных возможностей и повышения быстродействия, в него введены второй, третий, чет3А8759

вертый.

14

10

15

20

25

30

40

455

пятыи, шестой и седьмои резисторы, два электронных ключа, блок нагрузки, четвертый блок сравнения напряжений, второй логический преобразователь, вход теста нагрузки зонда, соединенный с первым входом второго логического преобразователя,с четвертым входом первого логического пр еобразователя, с первым входом блока нагрузки, первый выход которого соединен с входом первого электронного ключа, с первым выводом второго резистора, с первым выводом третьего резистора, с первым выводом четвертого резистора, второй вывод третьего ре;зистора соединен с вторым входом второго блока сравнения напряжений и с первым выводом пятого резистора, второй вывод которого через шестой резистор соединен с общей шиной, че- Р€;З первый резистор соединен с шиной питания, а непосредственно соединен с первым входом четвертого блока г сравнения напряжений, второй вход которого соединен со щупом, а прямой и инверсный выходы соединены соответственно с вторым и третьим входами второго логического преобразователя, четвертьш вход которого соединен с вторым выходом блока нагрузки, второй вход которого соединен с первым выходом второго логического преобразователя и с входом управления первого электронного ключа, третий вход блока нагрузки соединен с вторым выходом второго логического преобразователя и с входом управления второго электронного ключа, выход которого соединен с вторым выводом четвертого резистора, вход второго электронного ключа через седьмой резистор соединен с выходом первого электронного ключа, а непосредственно соединен с первым входом второго блока сравнения напряжений, логические выходы зонда соединены с выходами первого логического преобразователя, второй вывод второго резистора соединен со щупом.

Фиг. 3

фаз. 2

J(

F

|.

Фив.

п

Фиг. 6

Фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ поиска дефектов в цифровых блоках и устройство для его осуществления | 1985 |

|

SU1260884A1 |

| Зонд для проверки сигналов цифровых микросхем | 1984 |

|

SU1228055A1 |

| Преобразователь логических уровней | 1990 |

|

SU1812634A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1619208A1 |

| Устройство для контроля исправности силовых тиристоров вентильного преобразователя | 1989 |

|

SU1758760A1 |

| УСТРОЙСТВО КОНТРОЛЯ | 1996 |

|

RU2109300C1 |

| Трехстабильный аналоговый коммутатор | 1990 |

|

SU1725384A1 |

| Трехфазный преобразователь напряжения для питания гистерезисного двигателя | 1983 |

|

SU1119154A1 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С УПРАВЛЯЕМОЙ ДВУНАПРАВЛЕННОЙ ВНЕШНЕЙ ФОРСИРОВКОЙ | 2021 |

|

RU2781107C1 |

| Устройство для контроля сопротивления | 1988 |

|

SU1615639A1 |

Изобретение позволяет расширить функциональные возможности устройства и повысить его быстродействие. Устройство содержит регулируемые источники 1 и 6 опорного напряжения, блоки 2, 3 и 5 сравнения напряжений, логический преобразователь 8, резистор 10 и индикатор 21. Введение блока 9 нагрузки, электронных ключей 11 и 13, блока 15 сравнения напряжений, логического преобразователя 20 и резисторов 12, 14, 16-19 позволяет контролировать высокоимпедансное состояние и применить форсированньй режим разряда паразитных емкостей. 12 ил. i (Л OQ 4 00 СЛ Фие

п

noffc

tf

Фие. 7

г t3 t , t s

I I I I j

t .

I I

..

-J-i 1 I

I 2

T

1-JU-

Г- - l

j

I I I

rz--jiz--4t l:3

T

t7 f-e t3

с.1

C/7I

f// f7

0

«pi/e. 5

tfO

;j

f

Фиг. Ю

5 trs ii7 tfa -f

f/7

HUH

/5

Фи.11

tx f1 t22 t23

n

tf.

AfOAT

tlS

Фиг. 12

Редактор Ю.Середа

Составитель А. Коробков Техред Л.Сердюкова

Заказ 5186/45 Тираж 729Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Л.Патан

| Зонд для проверки сигналов цифровых микросхем | 1984 |

|

SU1228055A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Зонд для проверки сигналов цифровых микросхем | 1974 |

|

SU513330A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-10-30—Публикация

1986-06-19—Подача