Изобретение относится к контрольно-измерительной технике и может быть использовано в многоканальных системах контроля цифровых узлов.

Цель изобретения - расширение функциональных возможностей устройства за счет возможности контроля входного тока объекта контроля.

ливаются уровни логической 1, а на третьем и четвертом выходах - уровни логического О. Указанное состояние , выходов блока 26 режима приводит ключи 7 и 8 в проводящее состояние, а ключи 9 и 10 - в непроводящее, при этом операционные усилители 27 и 28 работают как повторители напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых схем | 1986 |

|

SU1522130A1 |

| Устройство для контроля электронных схем | 1985 |

|

SU1270732A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Устройство для контроля электронных схем | 1984 |

|

SU1302870A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Устройство для разбраковки полупроводниковых диодов | 1983 |

|

SU1164636A1 |

| Электронный коммутатор системы зажигания | 1990 |

|

SU1774060A1 |

| Устройство для времятоковой защиты электродвигателей переменного тока | 1985 |

|

SU1350740A1 |

Изобретение относится к контрольно-измерительной технике. Цель изобретения - расширение функциональных возможностей устройства за счет возможности контроля входного тока объекта контроля - достигается введением блока 26 управления, ключей 7 - 12, операционных усилителей 27 и 28, клеммы 25 режима и диодов 29 и 30. Устройство содержит также формирователь 3 импульсов, управляемый источник 4 тока, схему 5 сравнения, ключ 6, линию 13 передачи. В описании изобретения даны также структурные схемы формирователя импульсов и блока управления. 2 з.п. ф-лы, 3 ил.

На фиг.1 приведена схема устройст- JQ На клеммы 23 и 24 должны подаваться

ва; на фиг.2 - схема формирователя импульсов; на фиг.З - схема блока управления.

Устройство для контроля цифрового узла 1 с контактом 2 содержит форми- рователь 3 импульсов, управляемый источник 4 тока, схему 5 сравнения, - первый 6, второй 7, третий 8, четвертый 9, пятьй 10, шестой 11, седьмой 12 ключи, линию 13 передачи, клемму 20 14 тестовой последовательности, клемму 15 блокировки, клемму 16 для задания тока, первую 17 и вторую 18 клеммы для задания уровня контроля, первую 19 и вторую 20 клеммы стробирова-25 ния, первую 21 и вторую 22 клеммы контроля, первую 23 и вторую 24 клеммы для задания напряжения, клемму 25 режима, блок 26 управления, первый 27 „и второй 28 операционные усилители, on первый 29 и второй 30 диоды с соответствующими связями.

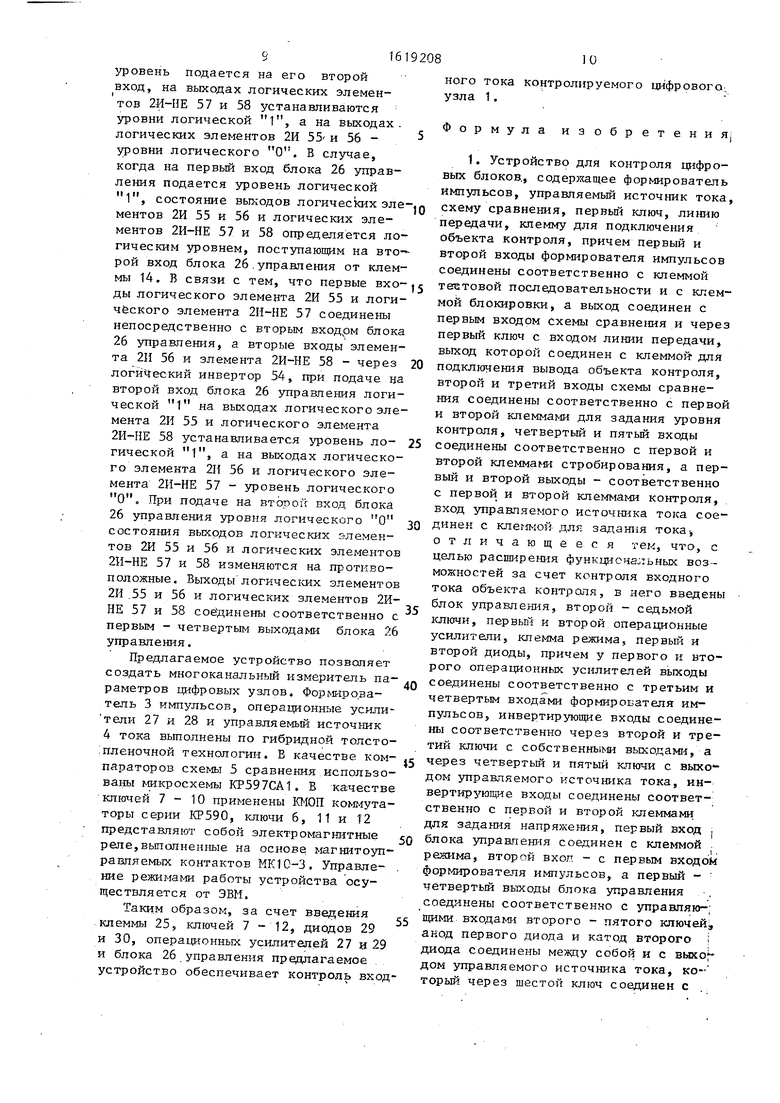

Формирователь 3 импульсов содержит первый 31, второй 32, третий 33, четвертый 34, пятый 35, шестой 36 и седьмой 37 транзисторы, третий 38, четвертый 39, пятый 40 и шестой 41 диоды, ключ 42, первый 43 и второй 44 конденсаторы, первый 45, второй 46, третий 47, четвертый 48, пятый 49, шестой 50, седьмой 51, восьмой 52, девятый 53 резисторы с соответствующими связями.

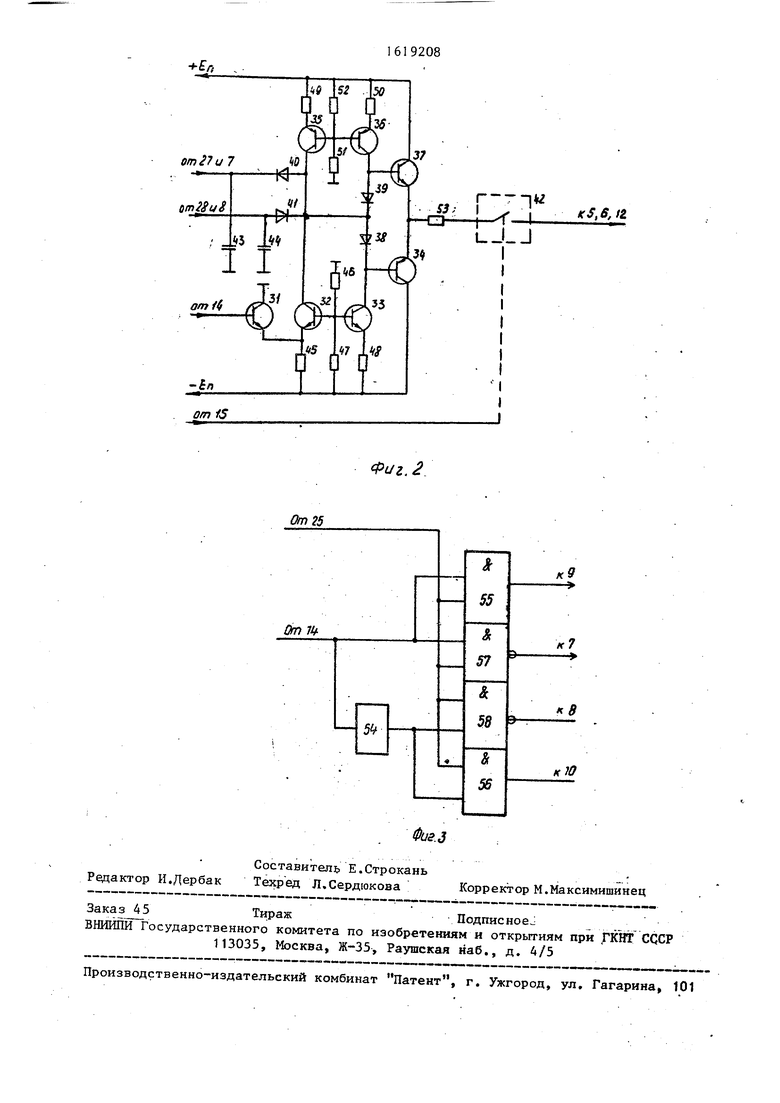

Блок 26 управления содержит логический инвертор 54, первый 55 и вто- 45 рой 56 логический элементы 2И, первый 57 и второй 58 логические элементы 2И-НЕ.

Устройство работает следующим образом.

Для приведения устройства в состояние, соответствующее функциональному контролю проверяемого цифрового уэла 1, ключ 6 должен быть замкнут, ключ 12 разомкнут, а ключ 11 - в любом состоянии. На клемму 25 подается уровень логического О, под воздействием которого на первом и втором выходах блока 26 управления устанав35

40

50

55

напряжения постоянного тока, которые передаваясь через операционные усили тели 27 и 28, поступают на третий и четвертый входы формирователя 3 импульсов, определяя соответственно вы сокий и низкий уровни его выходного напряжения, на клемму 14 должна пода ваться последовательность импульсов с уровнями, соответствующими логичес кому О и логической 1.

При подаче на клемму 15 уровня ло гической 1 на выходе формирователя 3 импульсов вырабатывается импульсна последовательность, которая через ключ 6 и линию 13 передачи поступает на контакт 2 в качестве входного воз действия для контролируемого цифрово го узла 1. Для неискаженной передачи импульсного напряжения должно быть обеспечено согласование выходного со противления формирователя 3 импуль сов с волновым сопротивлением линии 13 передачи, входной ток контролируе мого цифрового узла 1, являясь одновременно выходным током формирователя 3 импульсов, создает на его выход ном сопротивлении падение напряжения которое приводит к погрешности, проявляющейся в несоответствии значений высокого и низкого уровней выходного напряжения формирователя 3 импульсов напряжения постоянного тока, задавае мым на клеммы 23 и 24.

Для перевода устройства в ние Формирования импульсного напряже ния с компенсацией падения напряже ния на выходном сопротивлении формир вателя 3 импульсов ключ 1 1 должен быть замкнут, на клемму 25 подается уровень логической 1. В этом случа при подаче на клемму 14, а следовательно, и на второй вход блока 26 уп равления уровня логической 1 на втором и третьем выходах последнего появляются уровни логической 1, а на первом и четвертом - уровни логического О. Выходными сигналами бло ка 26 управления ключи 8 и 9 устанав ливаются в проводящее состояние, а

; 0 5 n

5

5

0

0

5

напряжения постоянного тока, которые, передаваясь через операционные усилители 27 и 28, поступают на третий и четвертый входы формирователя 3 импульсов, определяя соответственно высокий и низкий уровни его выходного напряжения, на клемму 14 должна подаваться последовательность импульсов с уровнями, соответствующими логическому О и логической 1.

При подаче на клемму 15 уровня логической 1 на выходе формирователя 3 импульсов вырабатывается импульсная последовательность, которая через ключ 6 и линию 13 передачи поступает на контакт 2 в качестве входного воздействия для контролируемого цифрового узла 1. Для неискаженной передачи импульсного напряжения должно быть обеспечено согласование выходного сопротивления формирователя 3 импульсов с волновым сопротивлением линии 13 передачи, входной ток контролируемого цифрового узла 1, являясь одновременно выходным током формирователя 3 импульсов, создает на его выходном сопротивлении падение напряжения, которое приводит к погрешности, проявляющейся в несоответствии значений высокого и низкого уровней выходного напряжения формирователя 3 импульсов напряжения постоянного тока, задаваемым на клеммы 23 и 24.

Для перевода устройства в ние Формирования импульсного напряжения с компенсацией падения напряжения на выходном сопротивлении формирователя 3 импульсов ключ 1 1 должен быть замкнут, на клемму 25 подается уровень логической 1. В этом случае при подаче на клемму 14, а следовательно, и на второй вход блока 26 управления уровня логической 1 на втором и третьем выходах последнего появляются уровни логической 1, а на первом и четвертом - уровни логического О. Выходными сигналами бло- ка 26 управления ключи 8 и 9 устанавливаются в проводящее состояние, а

ключи 7 и 10 - в непро водящее. Под действием отрицательной обратной связи, образованной ключами 9 и 11 выходное напряжение операционного усилителя 27, воздействуя на третий вход формирователя 3 импульсов, устанавливает в точке соединения ключа 11 с входом линии 13. передачи напряжение высокого уровня, равное напряжению постоянного тока на клемме 23, соединенной с нейнвертирующим входом операционного усилителя 27, ключ 8 в этом случае предотвращает насыщение операционного усилителя 28.

При подаче на клемму 14 уровня логического О на втором и третьем выходах блока 26 появляются уровни логического О, а на первом и четвертом - уровни логической 1, при этом ключи 8 и 9 устанавливаются в непро- водящее состояние, а ключи 7 и 10 - в проводящее. Отрицательная обратная связь, образованная ключами 10 и 11, устанавливает выходное напряжение операционного усилителя 28 таким, при котором низкий уров.ень выходного напряжения формирователя 3 импульсов в точке соединения ключа 11 с входом линии 13 передачи соответствует напряжению постоянного тока на клемме 24. Ключ 7 предотвращает насыщение операционного усилителя 27.

При функциональном контроле цифровых узлов с шинной структурой для отключения выходного напряжения формирователя 3 импульсов от контролируемого узла 1 (перевода выхода формирователя 3 импульсов в высокоим- педанское третье состояние) на клемму 15 подается уровень логического О. На клемму 16 подается напряжение, определяющее полярность и значение выходного тока управляемого ис

точника 4 тока, который, протекая через ключ 11 и линию 13 передачи, создает необходимую нагрузку для контакта 2, который в этом случае является выходом контролируемого цифрового узла 1. Выходное напряжение контролируемого цифрового узла 1 от контакта 2 через линию 13 передачи, ключ 6 поступает на первый вход схемы 5 сравнения, на второй и третий входы которой от клемм 17 и 18 поступают напря- ;жения постоянного тока, определяющие границы разбраковки соответственно высокого и низкого уровней напряжения, В момент подачи стробирующих им0

5

5

20

30

5

0

5

0

пульсов на клеммы 19 и 20 и соответственно на четвертый и пятый входы , схемы 5 сравнения на выходах последней и соответственно на клеммах 21 и 22 устанавливаются уровни логического О или логической 1 в зависимости от результата разбраковки.

Для контроля входного тока контролируемого узла 1 ключ 6 должен быть разомкнут, а ключ 12 замкнут. На клемму 15 должен быть подан уровень логической 1. Вследствие того, что ключ 6 разомкнут, выходное напряжение фор- мир-рвателя 3 импульсов поступает на контакт 2 через ключ 12, диод 29 или диод 30, ключ 11 и линию 13 передачи. Погрешность задания напряжения при этом отсутствует, так как дополнительное падение напряжения на диоде 29 или диоде 30 вместе с падением напряжения на выходном сопротивлении формирователя 3 импульсов компенсируется действием отрицательных обратных 5 связей, образуемых ключами 9-11, аналогично тому, как описано для случая формирования импульсного напряже - ния с компенсацией падения напряжения на выходнЪм сопротивлении формирова- теля 3 импульсов.

На клемму 16 подается напряжение постоянного тока, которое ьядает выходной ток управляемого источника 4 тока, равный граничному значению разбраковки тока через клемму 2 для подключения вывода контролируемого узла

1,являющегося в этом случае входом. На клеммы 17 и 18 подаются напряжения постоянного тока, равные значениям ; соответственно высокого и низкого уровней, импульсного напряжения на контакте 2.

Пусть на контакте 2 устанавлйвает|- ся высокий уровень напряжения. Если входной ток контролируемого узла 1 меньше граничного значения (случай годности контролируемого цифрового узла 1), то з соответствии с вторым законом Кирхгофа ток,равный разности между выходным током упраапяемого источника 4 .тока и током через контакт

2,протекает через один из диодов 29 и 30, например через диод 29, создавая на нем падение напряжения. В этом случае напряжение на первом входе схемы 5 сравнения меньше, чем на ее втором входе, причем разница определяется падением напряжения на диоде 29, так как его катод через ключ 12 сое5

динен с первым входом схемы 5 сравнения, а анод через ключ 11 и линию 13 передачи - с контактом 2, напряжение на котором равно напряжению на втором входе схемы 5 сравнения, поступающему от клеммы 17. В момент поступления стробирующего импульса от клеммы 19 на первом выходе схемы 5 сравнения и соответственно на клемме 21 устанав- ливается уровень логического О, ко- iорый в этом случае является признаком годности контролируемого узла 1 по входному току высокого уровня.

Если входной ток контролируембго цифрового узла 1 превышает граничное значение разбраковки (случаи брака контролируемого цифрового узла 1), разностный ток имеет направление, обратное по сравнению с рассмотренным случаем, при этом открывается диод 30. Напряжение на первом входе схемы 5 сравнения устанавливается более высоким, чем на втором входе схемы 5 сравнения. Разница определяется падением напряжения на диоде 30. При подаче стробирующего импульса на первом выходе схемы 5 сравнения и соответственно на клемме 21 устанавливается уровень логической 1 - признак бра- ка контролируемого цифрового узла 1 по входному току высокого уровня.

При низком уровне напряжения на контакте 2 контроль входного тока контролируемого цифрового узла 1 осуществляется по выходным сигналам схе- мы 5 сравнения, поступающим на клемму 22 при подаче стробирующего импульса на клемму 20.

Формирователь 3 импульсов содержит дифференциальный каскад на транзисторах 31 и 32 с несимметричной нагрузкой, ток которого задается резистором 45. Базы транзисторов 31 и 32 соединены соответственно с первым входом формирователя 3 импульсов и со средней точкой делителя напряжения, образованного резисторами 46 и 47, к которому подключена также база транзистора 33. Транзистор 33 вместе с токозадающим резистором 48 образуют генератор тока, являющийся нагрузкой дифференциального каскада. Делитель напряжения, образованный резисторами 51 и 52, обеспечивает напряжение на базах транзисторов 35 и 36, соответ- (ствующим выбором номиналов резисторов 45 и 49 ток дифференциального каскада устанавливается в два раза больше, чем ток транзистора 35. При подаче на

5

Q

5Q

92088

базу транзистора 31 уровня логической 1 транзистор 31 открывается, закрывая транзистор 32. Па коллекторе транзистора 32 формируется фронт импульсного напряжения, которое фиксируется диодом 40 на высоком уровне, определяемом постоянным напряжением, поступающим на катод диода 40 от третьего входа формирователя 3 импульсов. Конденсатор 43 осуществляет фильтрацию высокочастотных составляющих импульсного напряжения, предотвращая попадание их на третий в::од формирователя 3 импульсов.

Подача на базу транзистора 31 уровня логического О приводит к закрыванию транзистора 31 и, следова0

5 Q

5

0

5

0

тельно, открыванию транзистора 32, Вследствие того, нто ток транзистора 32 превышает ток транзистора 35, формируется срез импульсного напряжения, которое в этом случае фиксируется диодом 41 на низком уровне, определяемом напряжением постоянного тока, , поступающим на анод диода i. 1 от чет- i вертого входа формирователя 3 импульсов. Назначение конденсатора 44 аналогично конденсатору 43.

Транзисторы 33 и 36 вместе с токо- чацающими резисторами 48 и 50 образуют генераторы тока, обеспечивающие прямое смещение диодов 38 и 39, которые в свою очередь определяют начальный ток выходных повторителей на транзисторах 34 и 37. Импульсное напряжение с эмиттеров транзисторов 34 и 37 через резистор 53 и ключ 42 поступает на выход формирователя 3 импульсов. Резистор 53 в сумме с выходным сопротивлением повторителей напряжения на транзисторах 34 к 37 и сопротивлением ключа 42, находяцегося в проводящем состоянии, определяет выходное сопротивление формирователя 3 импульсов и служит для обеспечения согласования с волновым сопротивлением линии 13 передачи. Ключ 42 переводится в непроводящее состояние уровнем логического О, поступающим на его управляющий вход от второго входа формирователя 3 импульсов, чем обеспечивается выключение последнего, т.е. перевод в высокоимпедансное третье состояние.

Блок 26 управления предназначен для управления работой ключей 7 - 10. -При подаче уровня логического О на первый вход блока 26 управления, не- зависимо от того, какай логический

о1619

уровень подается на его второй вход, на выходах логических элементов 2И-НЕ 57 и 58 устанавливаются уровни логической 1, а на выходах, логических элементов 2И 55 и 56 -

уровни логического О. В случае, когда на первый вход блока 26 управления подается уровень логической 1, состояние выходов логических элементов 2И 55 и 56 и логических элементов 2И-НЕ 57 и 58 определяется логическим уровнем, поступающим на второй вход блока 26 управления от клеммы 14. В связи с тем, что первые BXOды логического элемента 2И 55 и логического элемента 2И-НЕ 57 соединены непосредственно с вторым входрм блока 26 управления, а вторые входы элемента 2И 56 и элемента 2И-НЕ 58 - через логический инвертор 54, при подаче на второй вход блока 26 управления логической 1 на выходах логического элемента 2И 55 и логического элемента 2И-НЕ 58 устанавливается уровень ло- гической 1, а на выходах логического элемента 2И 56 и логического элемента 2И-НЕ 57 - уровень логического О. При подаче на вход блока 26 управления уровня логического О состояния выходов логических элементов 2И 55 и 56 и логических элементов 2И-НЕ 57 и 58 изменяются на противоположные. Выходы логических элементов 2И 55 и 56 и логических элементов 2И- НЕ 57 и 58 соединены соответственно с первым - четвертым выходами блока 26 управления.

Предлагаемое устройство позволяет создать многоканальный измеритель параметров цифровых узлов. Формирователь 3 импульсов, операционные усили- тели 27 и 28 и управляемый источник 4 тока выполнены по гибридной толстопленочной технологии. В качестве компараторов схемы 5 сравнения использованы микросхемы КР597СА1. В качестве ключей 7-10 применены КМОП коммутаторы серии КР590, ключи 6, 11 и 12 представляют собой электромагнитные реле,выполненные на основе магнитоуп- равляемых контактов МК10-3. Управление режимами работы устройства осуществляется от ЭВМ.

Таким образом, за счет введения клеммы 25, ключей 7-12, диодов 29 и 30, операционных усилителей 27 и 29 и блока 26 управления предлагаемое устройство обеспечивает контроль вход

Q J 20 25 JQ

Q

40

i5

5

10

ного тока контролируемого цифрового узла 1.

Формула изобретения,

входом линии передачи, катод первого диода соединен с анодом второго дио- др, который через седьмой ключ соединен,с выходом формирователя импульсов.

5

0

5

0

5

0

ры четвертого и седьмого транзисто- ров соединены между собой и с первым выводом ( девятого резистора, второй | вывоД которого через ключ соединен с выходом фррмирователя импульсов, анод третьего и катод четвертого диодов соединены между собой, с коллекторами второго и пятого транзисторов, с ано- дом пятого и катодом шестого диодов, а катод пятого и анод шестого диодов соединены соответственно с первыми выводами первого и второго конденсаторов, вторые выводы которых соединены с общей шиной формирователя импульсов, базы первого транзистора, управляющий вход восьмого ключа, катод пятого и анод шестого диодов соединены соответственно с первым - четвертым входами фopjмиpoвaтeля импульсов.

| Устройство контроля больших интегральных схем | 1983 |

|

SU1193608A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| . | |||

Авторы

Даты

1991-01-07—Публикация

1988-01-11—Подача